### OKI

# MSM9552/9553 IC for FM Multiplex Broadcast Reception User's Manual

Ver. 1.0 ISSUE DATE: Mar., 1998

#### **IMPORTANT NOTICE**

DARC (DAta Radio Channel), an FM multiplex broadcast technology, has been developed by NHK (Japan Broadcasting Corporation). DARC is a registered trademark of NHK Engineering Service (NHK-ES).

Any manufacturer who intends to manufacture/sell products that utilize DARC technology needs to be licensed by NHK-ES.

For detailed information on licenses, please contact: NHK Engineering Service Phone: (+81) 3-3417-4840

#### NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents cotained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 1998 Oki Electric Industry Co., Ltd.

### TABLE OF CONTENTS

| 1. | GEN        | IERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                           | 1-1                                                                              |

|----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2. | BLO        | CK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                  | 2-1                                                                              |

| 3. | 3.1        | INFORMATION<br>PIN CONFIGURATION (TOP VIEW)<br>PIN DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                             | 3-1                                                                              |

| 4. | 4.1<br>4.2 | CTRICAL CHARACTERISTICS<br>MSM9552 ELECTRICAL CHARACTERISTICS<br>4.1.1 Absolute Maximum Ratings<br>4.1.2 Recommended Operating Conditions<br>4.1.3 DC Characteristics<br>4.1.4 AC Characteristics<br>4.1.5 Filter Characteristics<br>MSM9553 ELECTRICAL CHARACTERISTICS<br>4.2.1 Absolute Maximum Ratings<br>4.2.2 Recommended Operating Conditions<br>4.2.3 DC Characteristics<br>4.2.4 AC Characteristics | 4-1<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-5<br>4-5<br>4-5<br>4-5<br>4-7<br>4-8 |

|    | 4.3        | TIMING DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                              | 4-9                                                                              |

| 5. |            | ITROL REGISTERS<br>INTERRUPT REGISTERS<br>5.1.1 Interrupt Source<br>5.1.2 INT Mask                                                                                                                                                                                                                                                                                                                          | 5-1<br>5-1                                                                       |

|    | 5.2        | <ul> <li>RECEIVE DATA REGISTERS</li> <li>5.2.1 Receive Block Status</li> <li>5.2.2 Receive Data RAM Port</li> <li>5.2.3 Receive RAM, Data Accumulation Condition, and Address Clear</li> <li>5.2.4 BIC Monitor</li> </ul>                                                                                                                                                                                   | 5-4<br>5-6<br>5-6                                                                |

|    | 5.3        | CLOCK REGENERATION REGISTERS                                                                                                                                                                                                                                                                                                                                                                                | 5-10<br>5-10<br>5-12<br>5-13                                                     |

|    | 5.4        | <ul> <li>5.3.4 Phase Correction Step</li></ul>                                                                                                                                                                                                                                                                                                                                                              | 5-15<br>5-15<br>5-16<br>5-16<br>5-17                                             |

|    |            | <ul> <li>5.4.6 Block Synchronization Clear</li></ul>                                                                                                                                                                                                                                                                                                                                                        | 5-18                                                                             |

|    | 5.5   | FRAM    | E SYNCHRONIZATION REGISTERS                               | .5-19       |

|----|-------|---------|-----------------------------------------------------------|-------------|

|    |       | 5.5.1   | Number of Frame Synchronization Backward Protection Steps | .5-19       |

|    |       |         | Number of Frame Synchronization Forward Protection Steps  |             |

|    |       | 5.5.3   | Frame Synchronization Monitor                             | .5-20       |

|    |       | 5.5.4   | Frame Synchronization Set                                 |             |

|    |       | 5.5.5   | Frame Synchronization Clear                               | .5-21       |

|    |       | 5.5.6   | Block Number Monitor                                      | .5-21       |

|    |       | 5.5.7   | Frame Format Specification                                | .5-23       |

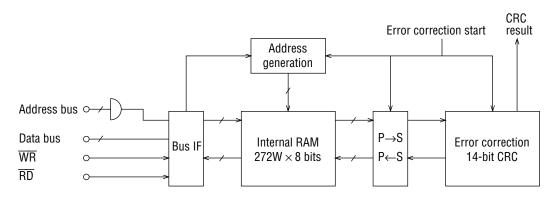

|    | 5.6   | ERRO    | R CORRECTION REGISTERS                                    | .5-24       |

|    |       | 5.6.1   | Internal Memory Address Counter Clear                     | .5-24       |

|    |       | 5.6.2   | Data Transfer Port for Error Correction                   | .5-24       |

|    |       | 5.6.3   | Error Correction Start Signal                             | .5-25       |

|    |       |         | CRC Result Indication                                     |             |

|    |       | 5.6.5   | Error Correction Result Indication                        | .5-26       |

|    |       | 5.6.6   | Majority Logic Threshold Value                            | .5-27       |

|    |       | 5.6.7   | Internal Address Monitor                                  | .5-27       |

|    | 5.7   | LAYEF   | R 4 CRC REGISTERS                                         |             |

|    |       | 5.7.1   | Layer 4 CRC Register Clear                                |             |

|    |       | 5.7.2   | Layer 4 CRC Data Buffer                                   | .5-31       |

|    |       | 5.7.3   | Layer 4 CRC Result Indication                             | .5-31       |

|    |       | 5.7.4   | Layer 4 CRC Register                                      | .5-32       |

|    | 5.8   | ANAL    | OG SECTION CONTROL/MONITOR REGISTER                       | .5-34       |

|    |       |         | R DOWN CONTROL REGISTER                                   |             |

|    | 5.10  |         | CONTROL REGISTERS                                         |             |

|    |       | 5.10.1  | Test Control 0                                            | .5-39       |

|    |       | 5.10.2  | Test Control 1                                            | .5-39       |

|    |       |         | DRESS REGISTER                                            |             |

|    | 5.12  | EXTEN   | NDED PORT REGISTER                                        | .5-43       |

| 6. | EXT   | ERNAL   | CONNECTION EXAMPLE                                        | .6-1        |

| 7  | م م ۸ |         | ON CIRCUIT                                                | 7_1         |

| 1. |       | LIGATI  |                                                           |             |

| AP | PEN   | DIX: IN | TERNATIONAL FRAME FORMAT                                  | .Appendix-1 |

## **Chapter 1**

# **GENERAL DESCRIPTION**

#### 1. GENERAL DESCRIPTION

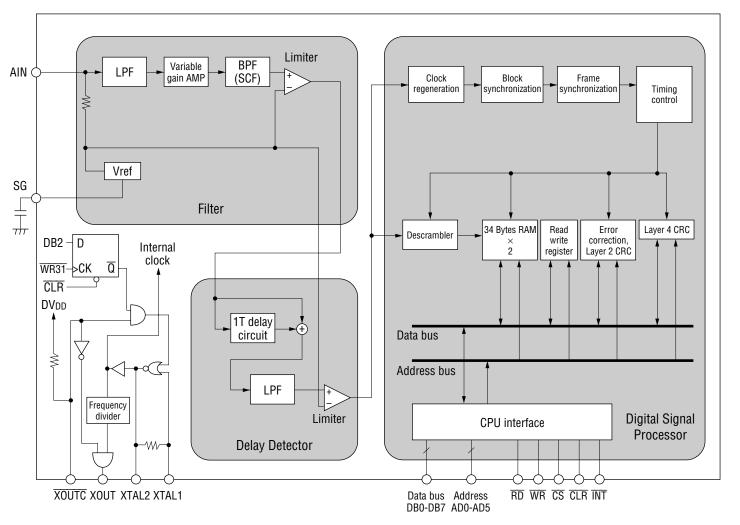

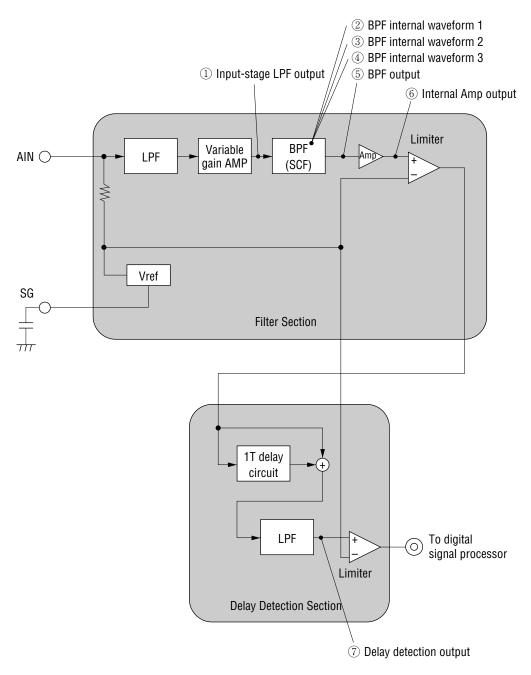

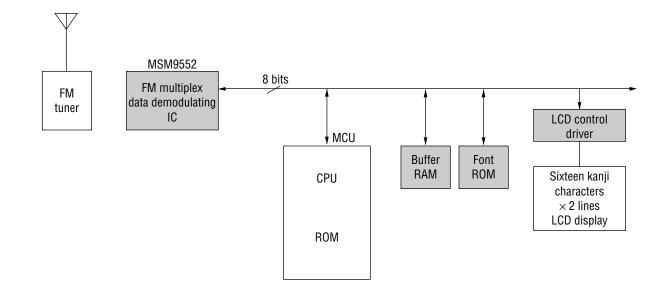

The MSM9552 and MSM9553 are LSI devices which demodulate FM character multiplex signals in the DARC (DAta Radio Channel) format to acquire digital data. These devices operate on 5 V and 3 V, respectively. In the DARC format, baseband signals at ordinary FM broadcasting frequencies are multiplexed with 16 kbps digital data which are L-MSK-modulated at 76 kHz.

Each device has a bandpass filter consisting of SCF, frame synchronization circuit, and error correction circuit, on a single chip.

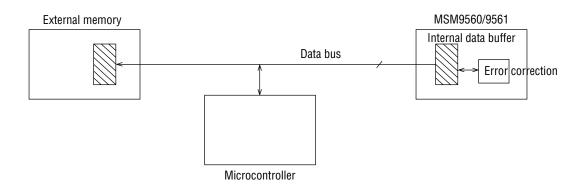

They allow a system for acquisition of digital data to be easily constructed by externally mounting an FM receiver tuner, microcontroller for control, and memory for temporary storage of data.

The MSM9552 and MSM9553 have a simple configuration, and are equipped with only necessary functions. By making changes to software for the external microcontroller, the MSM9552 and MSM9553 meet the various requirements of FM multiplex broadcasting services to be offered in future.

These devices are best suited for radio sets and information devices using FM character multiplex broadcasting, which began in Japan in October 1994. The MSM9553 is especially suitable for portable units.

#### Features

- Built-in Bandpass Filter (SCF)

- Built-in Block Synchronization Circuit and Frame Synchronization Circuit

- Setting of Synchronization Protecting Stage number

- Regeneration of Data Clocks by Digital PLL

- 1T Delay Detection

- Built-in Error Correcting Circuit

- Built-in Layer 4 and Layer 2 CRC Processing Circuit

- International Frame Formats A (supporting a real time block), B, and C available

- Microcontroller Parallel Interface

- Clock Output for External Devices (64 kHz to 8.192 MHz selectable)

- Power Source: 5 V (MSM9552), 3 V (MSM9553)

- Package: 44-pin plastic QFP (QFP44-P-910-0.80-2K) (Product name: MSM9552GS-2K,

MSM9553GS-2K)

## Chapter 2

## **BLOCK DIAGRAM**

**BLOCK DIAGRAM**

Ņ

## **Chapter 3**

# **PIN INFORMATION**

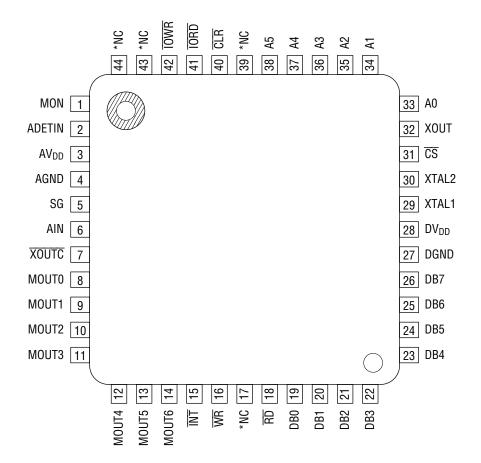

#### 3. PIN INFORMATION

#### 3.1 PIN CONFIGURATION (TOP VIEW)

44-Pin Plastic QFP

Figure 3.1 Pin Layout

\* Leave the NC pins (17, 39, 43, and 44) open.

#### 3.2 PIN DESCRIPTIONS

| Function                              | Symbol           | Pin   | Туре | Description                                            |

|---------------------------------------|------------------|-------|------|--------------------------------------------------------|

| Microcontroller                       | WR               | 16    | I    | Write signal to internal register.                     |

| interface                             | RD               | 18    | I    | Read signal to internal register.                      |

|                                       | ĪNT              | 15    | 0    | Interrupt signal to microcontroller. When set to       |

|                                       |                  |       |      | "L", an interrupt is generated.                        |

|                                       | CS               | 31    | I    | Chip select signal. When set to "L", the read, write   |

|                                       |                  |       |      | and data bus signals become effective.                 |

|                                       | CLR              | 40    | I    | When set to "L", the internal register is initialized, |

|                                       |                  |       |      | and the IC enters power down mode.                     |

|                                       | A0-A5            | 33-38 | I    | Address signal to internal register.                   |

| · · · · · · · · · · · · · · · · · · · | DB0-DB7          | 19-26 | I/O  | Data bus signal to internal register.                  |

| Tuner interface                       | AIN              | 6     | I    | FM multiple signal input.                              |

|                                       | SG               | 5     | 0    | Analog reference voltage pin. Connect a                |

|                                       |                  |       |      | capacitor between this pin and the analog ground       |

|                                       |                  |       |      | pin to prevent noise.                                  |

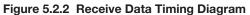

| Analog section                        | MON              | 1     | 0    | Analog section waveform monitoring pin. The            |

| est                                   |                  |       |      | mode setting for the blocks in the analog section      |

|                                       |                  |       |      | is specified by the analog section control register.   |

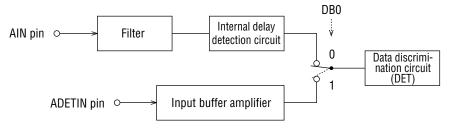

|                                       | ADETIN           | 2     | I    | Analog signal input pin for testing.                   |

| Digital section                       | IORD             | 41,   | I    | Digital section test signal input pins (pulled up      |

| test                                  | IOWR             | 42    |      | internally).                                           |

|                                       | MOUT0-           | 8-14  | 0    | Digital section test signal and monitor output         |

|                                       | MOUT6            |       |      | pins.                                                  |

| Clock                                 | XTAL1            | 29    | I    | 8.192 MHz crystal connection.                          |

|                                       | XTAL2            | 30    | 0    | 8.192 MHz crystal connection.                          |

|                                       | XOUT             | 32    | 0    | Pin to supply variable clock (64 kHz to 8.192 MHz)     |

|                                       |                  |       |      | to external devices.                                   |

|                                       | XOUTC            | 7     | I    | XOUT control. "L" sets XOUT output,                    |

|                                       |                  |       |      | "H" sets XOUT output inhibit. This pin is pulled up    |

|                                       |                  |       |      | internally.                                            |

| Power supply                          | AV <sub>DD</sub> | 3     |      | Analog power supply.                                   |

|                                       | AGND             | 4     |      | Analog ground.                                         |

|                                       | $DV_DD$          | 28    |      | Digital power supply.                                  |

|                                       | DGND             | 27    |      | Digital ground.                                        |

#### Table 3.1 Pin Description

### **Chapter 4**

# ELECTRICAL CHARACTERISTICS

#### 4. ELECTRICAL CHARACTERISTICS

#### 4.1 MSM9552 ELECTRICAL CHARACTERISTICS

#### 4.1.1 Absolute Maximum Ratings

| No. | Parameter            | Symbol           | Condition              | Rating                         | Unit  |

|-----|----------------------|------------------|------------------------|--------------------------------|-------|

| 4   | Dower oupply veltage | AV <sub>DD</sub> |                        | -0.3 to +7.0                   |       |

| I   | Power supply voltage | DV <sub>DD</sub> | $AV_{DD} = DV_{DD}$    | -0.3 10 +7.0                   | v     |

| 0   | Input voltage        | VI               | Ta = 25°C              | -0.3 to AV <sub>DD</sub> + 0.3 |       |

| 2   | Output voltage       | V <sub>0</sub>   |                        | -0.3 to DV <sub>DD</sub> + 0.3 |       |

| 3   | Maximum power        | п                | Ta = 25°C, per package | 400                            | mW    |

| 3   | dissipation          | PD               | Ta = 25°C, per output  | 50                             | 11100 |

| 4   | Storage temperature  | T <sub>STG</sub> | —                      | -55 to +150                    | °C    |

#### 4.1.2 Recommended Operating Conditions

| No. | Parameter             | Symbol            | Condition                           | Range               | Unit             | Applied Pin      |

|-----|-----------------------|-------------------|-------------------------------------|---------------------|------------------|------------------|

| 4   | Power supply voltage  | $AV_{DD}$         | AV <sub>DD</sub> = DV <sub>DD</sub> | 4.5 to 5.5          | V                | AV <sub>DD</sub> |

|     |                       | $DV_{DD}$         | AvDD = DvDD                         | 4.5 10 5.5          | v                | DV <sub>DD</sub> |

| 2   | Crystal oscillation   | f <sub>XTAL</sub> |                                     | 9 100 MUz . 100 ppm |                  | XTAL1,           |

| 2   | frequency             |                   |                                     | 8.192 MHz ±100 ppm  |                  | XTAL2            |

| 0   | FM multiplex signal   | M                 | Composite signal in-                | 0 E to 0*           |                  | A 1 N I          |

| 3   | input voltage         | V <sub>AIN</sub>  | cluding multiplex signal            | 0.5 to 2*           | V <sub>P-P</sub> | AIN              |

| 4   | Operating temperature | Та                |                                     | -40 to +85          | °C               | —                |

\* The gain of the variable gain amplifier (VGain): × 1, × 1.5, × 2, or × 3. The VGain should be adjusted to satisfy the equation:  $V_{AIN} \times VGain = 1.5$  V to 2.0 V.

### 4.1.3 DC Characteristics

$(DV_{DD} = AV_{DD} = 5 V \pm 10\%, DGND = AGND = 0 V, Ta = -40 to +85°C)$

| No. | Parameter          | Symbol            | Condition                                                        | Min.                       | Тур. | Max.                 | Unit | Applied Pin                                                               |

|-----|--------------------|-------------------|------------------------------------------------------------------|----------------------------|------|----------------------|------|---------------------------------------------------------------------------|

|     | Input voltage      | V <sub>IH</sub>   |                                                                  | 0.8 	imes DV <sub>DD</sub> |      |                      | V    | WR, RD,<br>XOUTC,<br>DB0 to DB7,                                          |

| 1   | input voltage      | V <sub>IL</sub>   |                                                                  | _                          |      | $0.2 \times DV_{DD}$ | V    | XTAL1, <u>CS</u> ,<br>A0 to A5, <u>CLR</u> ,<br><u>IORD</u> , <u>IOWR</u> |

| 2   | Output voltage     | V <sub>OH</sub>   | I <sub>0H</sub> = -1 mA                                          | DV <sub>DD</sub><br>-0.5   |      | _                    | V    | MOUT0 to<br>MOUT6, ĪNT,                                                   |

|     | Output voltage     | V <sub>OL</sub>   | I <sub>0L</sub> = 2 mA                                           |                            |      | 0.45                 | v    | DB0 to DB7,<br>XOUT                                                       |

| 3   | Input current 1    | I <sub>IH1</sub>  | V <sub>IH</sub> = DV <sub>DD</sub>                               |                            |      | 2                    | μΑ   | WR, RD, CS,<br>DB0 to DB7,                                                |

|     |                    | I <sub>IL1</sub>  | V <sub>IL</sub> = DGND                                           | -2                         |      | _                    |      | A0 to A5,<br>CLR                                                          |

| 4   | Input current 2    | I <sub>IH2</sub>  | $V_{IH} = AV_{DD}$                                               |                            |      | 2                    | μA   | ADETIN                                                                    |

|     |                    | I <sub>IL2</sub>  | V <sub>IL</sub> = AGND                                           | -2                         |      | _                    | μΑ   |                                                                           |

| 5   | Input current 3    | I <sub>IH3</sub>  | $V_{IH} = DV_{DD}$                                               | —                          |      | 2                    | μA   | XOUTC,                                                                    |

| 6   | Pull-up current    | I <sub>pull</sub> | DV <sub>DD</sub> = 5 V,<br>V <sub>IL</sub> = DGND                | 8                          | 35   | 110                  | μA   | IORD, IOWR                                                                |

| 7   | Output off-leakage | I <sub>ОН</sub>   | V <sub>OH</sub> = AV <sub>DD</sub><br>During nonmonitoring (Hiz) | —                          |      | 2                    |      | MON                                                                       |

| -   | current            | I <sub>OL</sub>   | V <sub>OL</sub> = AGND<br>During nonmonitoring (Hiz)             | -2                         | _    | _                    | μA   | WON                                                                       |

| 8   | Supply current     |                   | During operation, no load<br>f = 8.192 MHz                       |                            | 16   | 32                   | mA   |                                                                           |

| 0   |                    | I <sub>DD</sub>   | During power down,<br>no load                                    |                            |      | 20                   | μA   | AV <sub>DD</sub> , DV <sub>DD</sub>                                       |

#### 4.1.4 AC Characteristics

| No. | Parameter              | Symbol*              | Condition                  | Min.                                 | Тур.             | Max.    | Unit    | Applied Pin                     |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|-----|------------------------|----------------------|----------------------------|--------------------------------------|------------------|---------|---------|---------------------------------|-----|----|---------------------|---------------------|---------|---------|---------|---------|---------|---------|---------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-------------|-----|---|---|----|----|

|     |                        | t <sub>SWR1</sub>    | _                          | 10                                   | _                | _       |         | $\overline{WR}, \overline{CS},$ |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 1   | Write setup time       | -000111              |                            |                                      |                  |         | ns      | A0 to A5,                       |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     |                        | t <sub>SWR2</sub>    | —                          | 60                                   | _                | _       |         | DB0 to DB7                      |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     |                        |                      |                            |                                      |                  |         |         | $\overline{WR}, \overline{CS},$ |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 2   | Write hold time        | t <sub>HWR</sub>     | —                          | 10                                   | _                | _       | ns      | A0 to A5,                       |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     |                        |                      |                            |                                      |                  |         |         | DB0 to DB7                      |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 3   | Write pulse width      | t <sub>WWR</sub>     | —                          | 65                                   | _                | —       | ns      | WR                              |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 4   | Read setup time        | t <sub>SRD</sub>     |                            | 10                                   |                  |         | ns      | RD, CS,                         |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     |                        | <sup>I</sup> SRD     | —                          | 10                                   |                  |         | 115     | A0 to A5                        |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 5   | Read hold time         | t <sub>HRD</sub>     |                            | 10                                   |                  |         | ns      | $\overline{RD}, \overline{CS},$ |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 5   | neau noiu time         | чнкр                 | —                          | 10                                   |                  |         | 115     | A0 to A5                        |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 6   | Read pulse width       | t <sub>WRD</sub>     | —                          | 105                                  |                  |         | ns      | RD                              |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     | Interval between error |                      |                            |                                      |                  |         |         |                                 |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

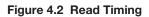

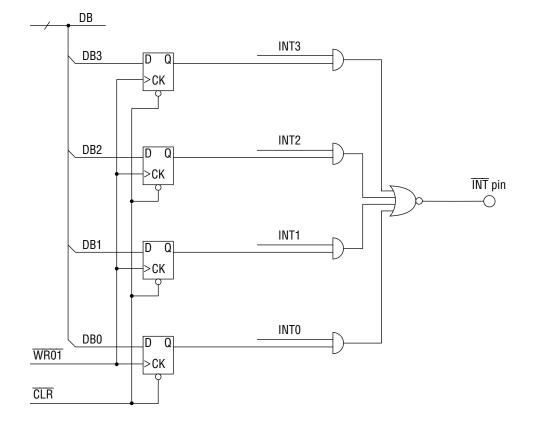

| 7   | correction data write  | t <sub>IWRWRE</sub>  | Error correction           | 250                                  | _                | -       | ns      | WR                              |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     | and write              |                      |                            |                                      |                  |         |         |                                 |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     | Interval between error |                      |                            |                                      |                  |         |         |                                 |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 8   | correction data read   | t <sub>IRDRDE</sub>  | t <sub>IRDRDE</sub>        | Error correction                     | 250              | _       | -       | ns                              | RD  |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     | and read               |                      |                            |                                      |                  |         |         |                                 |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     | Interval between error |                      |                            |                                      |                  |         | WR,     |                                 |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 9   | correction data write  |                      | t <sub>IWRRDE</sub>        | t <sub>IWRRDE</sub> Error correction | Error correction | 100     | -       | -                               | ns  | RD |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     | and read               |                      |                            |                                      |                  |         |         |                                 |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

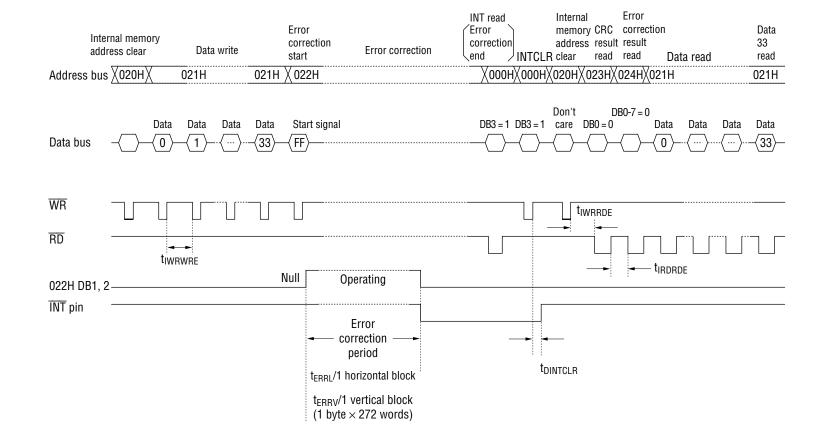

| 10  | Interval between layer | t <sub>ICLRWR4</sub> | Layer 4 CRC                | 100                                  | _                |         | ns      | WR                              |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     | 4 data clear and write | 40LNWN4              |                            | 100                                  |                  |         | 110     |                                 |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 11  | Interval between layer | timemea              |                            |                                      | tiwewe/          | tiwewe4 | tiwowoa |                                 |     |    | t <sub>IWRWR4</sub> | t <sub>IWRWR4</sub> | tiwewea | tiwewea | tiwewea | tiwowda | tiwowoa | tiwewea | tiwewe4 | t <sub>IWRWR4</sub> | Layer 4 CRC | 4.5 | _ | _ | μs | WR |

|     | 4 data write and write | -1001100114          | Layor Forto                |                                      |                  |         | μο      |                                 |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 12  | Interval between layer | t <sub>IWRRD4</sub>  | Layer 4 CRC                | 4.5                                  | _                | _       | μs      | WR,                             |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     | 4 data write and read  | -100111104           | Layor Forto                |                                      |                  |         | μο      | RD                              |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 13  | Read data output       | t <sub>DRD1</sub>    | _                          | _                                    | _                | 95      | ns      | RD,                             |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     | delay (1)              |                      |                            |                                      |                  |         | -       | DB0 to DB7                      |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 14  | Read data output       | t <sub>DRD2</sub>    | _                          | _                                    | _                | 80      | ns      | RD,                             |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     | delay (2)              | DIIDE                |                            |                                      |                  |         | -       | DB0 to DB7                      |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 15  | Interrupt CLR delay    | t <sub>DINTCLR</sub> | Step out interrupt         | 250                                  | _                | _       | ns      | INT,                            |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     |                        | -DINTOLIT            | Error correction interrupt |                                      |                  |         |         | WR                              |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

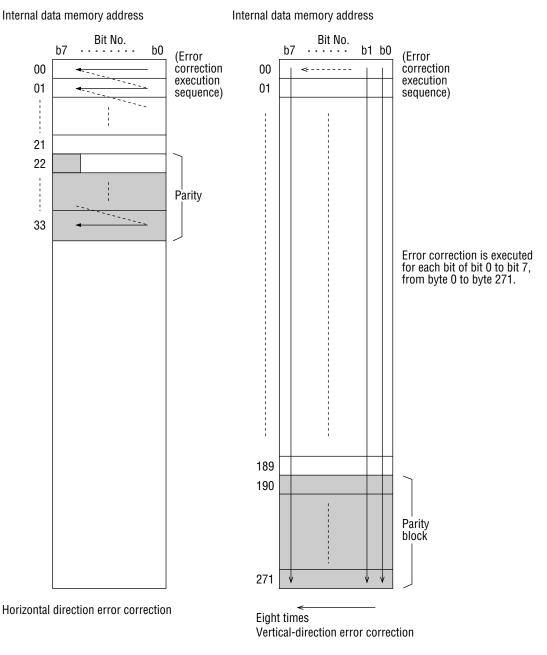

| 16  | Error correction time  | terr                 | _                          |                                      | _                | 274     | μs      | INT,                            |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     | (Horizontal direction) | <sup>I</sup> ERRL    | t <sub>ERRL</sub> —        |                                      |                  |         | 2/4     | μο                              | DBO |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 17  | Error correction time  | tropy                | t <sub>ERRV</sub> —        |                                      | _                | 2178    | μs      | INT,                            |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

|     | (Vertical direction)   |                      |                            |                                      |                  |         | μο      | DBO                             |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

| 18  | CLR pulse width        | t <sub>WCLR</sub>    | —                          | 200                                  |                  | —       | ns      | CLR                             |     |    |                     |                     |         |         |         |         |         |         |         |                     |                     |                     |                     |                     |                     |                     |                     |                     |                     |             |     |   |   |    |    |

\* See section 4.3, "TIMING DIAGRAM".

#### 4.1.5 Filter Characteristics

| No. | Parameter                      | Symbol | Condition                                               | Min. | Тур. | Max. | Unit | Applied Pin |

|-----|--------------------------------|--------|---------------------------------------------------------|------|------|------|------|-------------|

| 1   | BPF pass band attenuation      | GAIN1  | 72 to 80 kHz<br>Variable gain amplifier<br>gain: 0 dB   |      |      | 3.0  | dB   | MON         |

| 2   | BPF block band attenuation (1) | GAIN2  | 0 to 53 kHz<br>Variable gain amplifier<br>gain: 0 dB    | 50   |      |      | dB   | MON         |

| 3   | BPF block band attenuation (2) | GAIN3  | 100 to 500 kHz<br>Variable gain amplifier<br>gain: 0 dB | 50   |      |      | dB   | MON         |

#### 4.2 **MSM9553 ELECTRICAL CHARACTERISTICS**

| No. | Parameter            | Symbol           | Condition              | Rating                         | Unit |

|-----|----------------------|------------------|------------------------|--------------------------------|------|

| 4   | Dower oupply voltage | AV <sub>DD</sub> |                        | -0.3 to +7.0                   |      |

| 1   | Power supply voltage | DV <sub>DD</sub> | $AV_{DD} = DV_{DD}$    | -0.3 10 +7.0                   | v    |

| 0   | Input voltage        | VI               | Ta = 25°C              | -0.3 to AV <sub>DD</sub> + 0.3 |      |

| 2   | Output voltage       | V <sub>0</sub>   |                        | -0.3 to DV <sub>DD</sub> + 0.3 |      |

|     | Maximum power        | Р                | Ta = 25°C, per package | 400                            |      |

| 3   | dissipation          | PD               | Ta = 25°C, per output  | 50                             | mW   |

| 4   | Storage temperature  | T <sub>STG</sub> | —                      | -55 to +150                    | °C   |

#### 4.2.1 Absolute Maximum Ratings

#### **Recommended Operating Conditions** 4.2.2

| No.   | Parameter             | Symbol           | Condition                | Range               | Unit             | Applied Pin      |

|-------|-----------------------|------------------|--------------------------|---------------------|------------------|------------------|

| 4     | Power supply voltage  | $AV_{DD}$        |                          | 0.7 to 0.0          | v                | AV <sub>DD</sub> |

| I<br> |                       | DV <sub>DD</sub> | $AV_{DD} = DV_{DD}$      | 2.7 to 3.3          | v                | DV <sub>DD</sub> |

| 2     | Crystal oscillation   | f                |                          | 9 100 MHz , 100 ppm |                  | XTAL1,           |

| Z     | frequency             | TXTAL            |                          | 8.192 MHz ±100 ppm  |                  | XTAL2            |

|       | FM multiplex signal   | M                | Composite signal in-     | 0.0 += 0.0*         | V <sub>P-P</sub> | A 1 N I          |

| 3     | input voltage         | V <sub>AIN</sub> | cluding multiplex signal | 0.2 to 0.9*         |                  | AIN              |

| 4     | Operating temperature | Та               | _                        | -20 to +75          | °C               | _                |

\* The gain of the variable gain amplifier (VGain):  $\times$  1,  $\times$  1.5,  $\times$  2, or  $\times$  3. The VGain should be adjusted to satisfy the equation: V<sub>AIN</sub> × VGain = 0.6 V to 0.9 V.

### 4.2.3 DC Characteristics

(DV<sub>DD</sub> = AV<sub>DD</sub> = 3 V  $\pm$ 10%, DGND = AGND = 0 V, Ta = -20 to +75°C)

| No. | Parameter          | Symbol            | Condition                                                        | Min.                       | Тур. | Max.                 | Unit | Applied Pin                                |

|-----|--------------------|-------------------|------------------------------------------------------------------|----------------------------|------|----------------------|------|--------------------------------------------|

| 4   | Input voltage      | VIH               |                                                                  | 0.8 	imes DV <sub>DD</sub> |      |                      | V    | WR, RD,<br>XOUTC,<br>DB0 to DB7,           |

| 1   | input voltago      | VIL               |                                                                  | _                          |      | $0.2 \times DV_{DD}$ | V    | XTAL1, CS,<br>A0 to A5, CLR,<br>IORD, IOWR |

| 2   |                    | V <sub>OH</sub>   | I <sub>0H</sub> = -1 mA                                          | DV <sub>DD</sub><br>-0.5   |      | _                    | - V  | MOUTO to<br>MOUT6, INT,                    |

|     | Output voltage     | V <sub>OL</sub>   | I <sub>OL</sub> = 2 mA                                           | _                          |      | 0.45                 |      | DB0 to DB7,<br>XOUT                        |

| 3   | Input current 1    | lih1              | $V_{IH} = DV_{DD}$                                               | _                          |      | 2                    | μA   | WR, RD, CS,<br>DB0 to DB7,                 |

| 0   |                    | I <sub>IL1</sub>  | V <sub>IL</sub> = DGND                                           | -2                         |      | _                    | μι   | A0 to A5,<br>CLR                           |

| 4   | Input current 2    | I <sub>IH2</sub>  | $V_{IH} = AV_{DD}$                                               | —                          |      | 2                    | ıΔ   | ADETIN                                     |

|     |                    | I <sub>IL2</sub>  | V <sub>IL</sub> = AGND                                           | -2                         |      | _                    | μA   | ADETIN                                     |

| 5   | Input current 3    | I <sub>IH3</sub>  | $V_{IH} = DV_{DD}$                                               | —                          | —    | 2                    | μA   | XOUTC,                                     |

| 6   | Pull-up current    | I <sub>pull</sub> | DV <sub>DD</sub> = 3 V,<br>V <sub>IL</sub> = DGND                | 3                          | 13   | 50                   | μA   | IORD, IOWR                                 |

| 7   | Output off-leakage | I <sub>ОН</sub>   | V <sub>OH</sub> = AV <sub>DD</sub><br>During nonmonitoring (Hiz) | —                          | _    | 2                    | ۸    | MON                                        |

| I   | current            | I <sub>OL</sub>   | V <sub>OL</sub> = AGND<br>During nonmonitoring (Hiz)             | -2                         | _    | _                    | μA   |                                            |

| 8   | Supply current     |                   | During operation, no load<br>f = 8.192 MHz                       | _                          | 13   | 22                   | mA   |                                            |

| 0   |                    | I <sub>DD</sub>   | During power down,<br>no load                                    |                            |      | 10                   | μA   | AV <sub>DD</sub> , DV <sub>DD</sub>        |

### 4.2.4 AC Characteristics

| No. | Parameter              | Symbol*                              | Condition                            | Min.                                 | Тур. | Max. | Unit | Applied Pin                     |    |

|-----|------------------------|--------------------------------------|--------------------------------------|--------------------------------------|------|------|------|---------------------------------|----|

|     |                        | t <sub>SWR1</sub>                    |                                      | 10                                   |      | _    |      | $\overline{WR}, \overline{CS},$ |    |

| 1   | Write setup time       | -01111                               |                                      |                                      |      |      | ns   | A0 to A5,                       |    |

|     |                        | t <sub>SWR2</sub>                    | —                                    | 120                                  | _    | _    |      | DB0 to DB7                      |    |

|     |                        |                                      |                                      |                                      |      |      |      | $\overline{WR}, \overline{CS},$ |    |

| 2   | Write hold time        | t <sub>HWR</sub>                     | —                                    | 10                                   | _    | _    | ns   | A0 to A5,                       |    |

|     |                        |                                      |                                      |                                      |      |      |      | DB0 to DB7                      |    |

| 3   | Write pulse width      | t <sub>WWR</sub>                     | —                                    | 130                                  |      |      | ns   | WR                              |    |

| 4   | Dood opture time       | +                                    |                                      | 10                                   |      |      | 20   | RD, CS,                         |    |

| 4   | Read setup time        | t <sub>SRD</sub>                     | —                                    | 10                                   |      |      | ns   | A0 to A5                        |    |

| 5   | Dood hold time         | tupp                                 |                                      | 10                                   |      |      | 20   | RD, CS,                         |    |

| 5   | Read hold time         | t <sub>HRD</sub>                     | —                                    | 10                                   |      | _    | ns   | A0 to A5                        |    |

| 6   | Read pulse width       | t <sub>WRD</sub>                     | —                                    | 160                                  |      |      | ns   | RD                              |    |

|     | Interval between error |                                      |                                      |                                      |      |      |      |                                 |    |

| 7   | correction data write  | t <sub>IWRWRE</sub>                  | Error correction                     | 250                                  | _    | _    | ns   | WR                              |    |

|     | and write              |                                      |                                      |                                      |      |      |      |                                 |    |

|     | Interval between error |                                      |                                      |                                      |      |      |      |                                 |    |

| 8   | correction data read   | t <sub>IRDRDE</sub>                  | t <sub>IRDRDE</sub>                  | Error correction                     | 250  | -    | -    | ns                              | RD |

|     | and read               |                                      |                                      |                                      |      |      |      |                                 |    |

|     | Interval between error | t <sub>IWRRDE</sub> Error correction |                                      |                                      |      |      | WR,  |                                 |    |

| 9   | correction data write  |                                      | t <sub>IWRRDE</sub> Error correction | t <sub>IWRRDE</sub> Error correction | 100  | _    | -    | ns                              | RD |

|     | and read               |                                      |                                      |                                      |      |      |      |                                 |    |

| 10  | Interval between layer | tion prove (                         | Layer 4 CRC                          | 100                                  |      |      | ns   | WR                              |    |

|     | 4 data clear and write | t <sub>ICLRWR4</sub>                 | Layer 4 Ono                          | 100                                  |      |      | 115  |                                 |    |

| 11  | Interval between layer | tuvovo                               | Layer 4 CRC                          | 4.5                                  |      |      | μs   | WR                              |    |

|     | 4 data write and write | t <sub>IWRWR4</sub>                  |                                      | 4.5                                  |      |      | μο   |                                 |    |

| 12  | Interval between layer | twopport                             | Layer 4 CRC                          | 4.5                                  |      |      |      | WR,                             |    |

| 12  | 4 data write and read  | t <sub>IWRRD4</sub>                  | Layer 4 0h0                          | 4.5                                  |      |      | μs   | RD                              |    |

| 13  | Read data output       | t <sub>DRD1</sub>                    |                                      | _                                    |      | 160  | ns   | RD,                             |    |

|     | delay (1)              | URDI                                 |                                      |                                      |      | 100  | 115  | DB0 to DB7                      |    |

| 14  | Read data output       | toppo                                |                                      | _                                    | _    | 160  | ns   | RD,                             |    |

| 14  | delay (2)              | t <sub>DRD2</sub>                    | —                                    |                                      |      | 100  | 115  | DB0 to DB7                      |    |

| 15  | Interrupt CLR delay    | touroup                              | Step out interrupt                   | 250                                  |      |      | ne   | ĪNT,                            |    |

| 15  |                        | tdintclr                             | Error correction interrupt           | 230                                  |      |      | ns   | WR                              |    |

| 16  | Error correction time  | teres                                |                                      |                                      |      | 271  | 110  | ĪNT,                            |    |

| 10  | (Horizontal direction) | t <sub>ERRL</sub>                    | _                                    | —                                    |      | 274  | μs   | DBO                             |    |

| 17  | Error correction time  | tesev                                |                                      | _                                    |      | 2178 | 110  | ĪNT,                            |    |

| 17  | (Vertical direction)   | t <sub>ERRV</sub>                    | —                                    |                                      |      | 21/0 | μs   | DBO                             |    |

| 18  | CLR pulse width        | t <sub>WCLR</sub>                    | —                                    | 200                                  | _    | —    | ns   | CLR                             |    |

\* See section 4.3, "TIMING DIAGRAM".

#### 4.2.5 Filter Characteristics

| No. | Parameter                      | Symbol | Condition                                               | Min. | Тур. | Max. | Unit | Applied Pin |

|-----|--------------------------------|--------|---------------------------------------------------------|------|------|------|------|-------------|

| 1   | BPF pass band attenuation      | GAIN1  | 72 to 80 kHz<br>Variable gain amplifier<br>gain: 0 dB   |      |      | 3.0  | dB   | MON         |

| 2   | BPF block band attenuation (1) | GAIN2  | 0 to 53 kHz<br>Variable gain amplifier<br>gain: 0 dB    | 50   | _    |      | dB   | MON         |

| 3   | BPF block band attenuation (2) | GAIN3  | 100 to 500 kHz<br>Variable gain amplifier<br>gain: 0 dB | 50   |      |      | dB   | MON         |

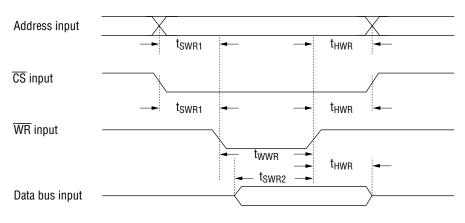

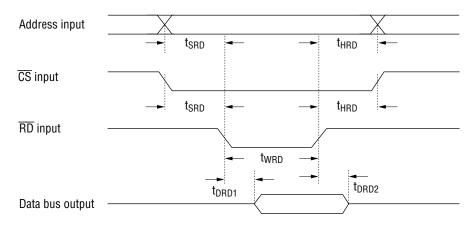

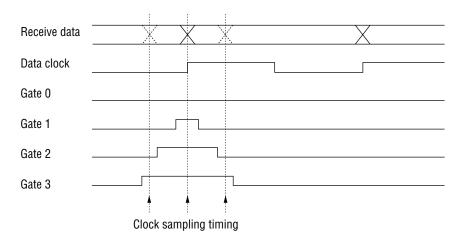

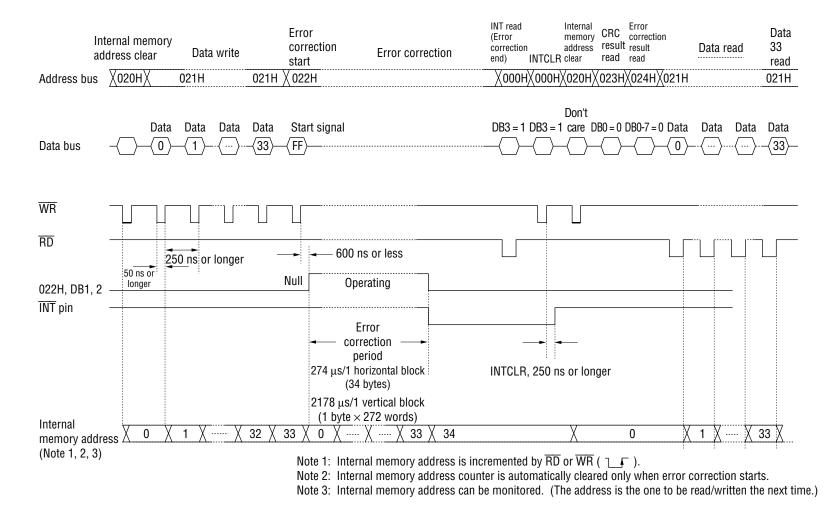

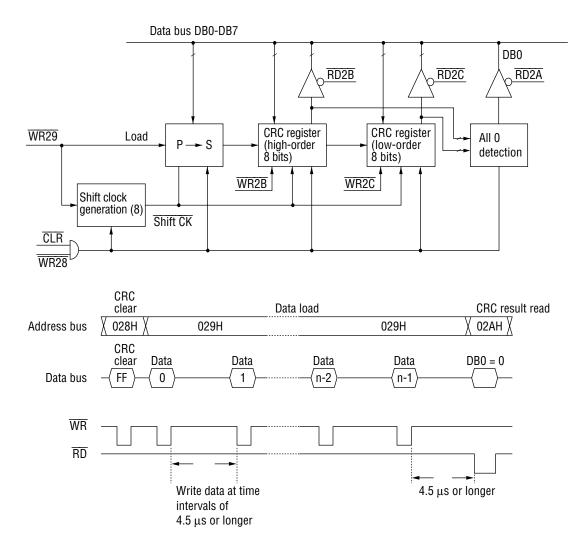

#### 4.3 TIMING DIAGRAM

Figure 4.1 Write Timing

| Address signal input     | Х 000Н Х   |

|--------------------------|------------|

| Data signal input        | XXXX01XX > |

| WR input (INTCLR signal) |            |

| INT output               |            |

Figure 4.3 Interrupt CLR Timing

Figure 4.4 Error Correction Timing Diagram

Figure 4.5 Layer 4 CRC Timing Diagram

## Chapter 5

## CONTROL REGISTERS

#### 5. CONTROL REGISTERS

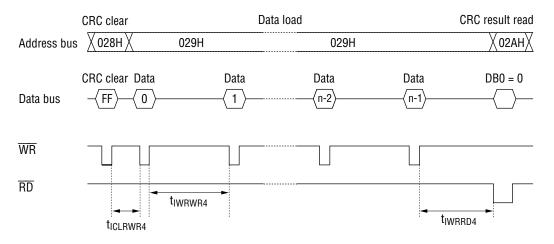

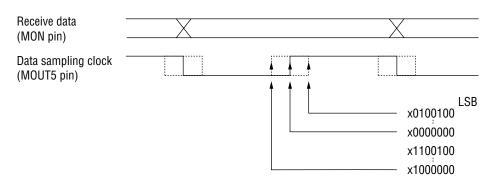

#### 5.1 INTERRUPT REGISTERS

#### 5.1.1 Interrupt source

These registers indicate the four types of interrupt factors: (1) receive interrupt, (2) 1st horizontal error correction completion, (3) out of sync., and (4) vertical error correction/2nd horizontal error correction completion. When an interrupt occurs, "1" is written. The registers must be externally cleared after reading, however clear conditions are different for each interrupt factor. For details see Table 5.1.1.

|         |             |     |     |     |     | (4)   | (3)   | (2)   | (1)   |

|---------|-------------|-----|-----|-----|-----|-------|-------|-------|-------|

| Address |             | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1   | DB0   |

|         | Reset value | —   | —   | _   | _   | 0     | 0     | 0     | 0     |

| 000H    | Read/write  | —   | —   | —   | —   | Read/ | Read/ | Read/ | Read/ |

|         | (Note)      |     |     |     |     | write | write | write | write |

(Note) Write is used to clear the interrupt. Write = "1" : clear Write = "0" : none

| Туре                               | Generation Condition                | Generation Cycle                                                                                                                         | Clear Condition           |

|------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| INT0                               | At the time one block is            | Every time 34 bytes are                                                                                                                  | 1. Write DB0 = "1" to INT |

| Receive interrupt                  | received in a frame/block           | received (18 ms).                                                                                                                        | (000H).                   |

| (000H, DB0)                        | synchronization state.              |                                                                                                                                          | 2. Clear the CLR pin.     |

|                                    | (Data is received only in a         |                                                                                                                                          | (Initial setting)         |

|                                    | synchronized status; not            |                                                                                                                                          |                           |

|                                    | received in an out-of-sync. state.) |                                                                                                                                          |                           |

| INT1                               | At the time1st horizontal error     | 0.274 ms after 1st error                                                                                                                 | 1. Write DB1 = "1" to INT |

| 1st horizontal error               | correction is completed.            | correction start signal is                                                                                                               | (000H).                   |

| correction completion              |                                     | written.                                                                                                                                 | 2. Clear the CLR pin.     |

| (000H, DB1)                        |                                     |                                                                                                                                          | (Initial setting)         |

| INT2                               | When frame is out of                | $\left(\frac{1}{270/4}\right)$ (number of forward)+123 $\left(\frac{1}{2000}\right)$                                                     | 1. Write DB2 = "1" to INT |

| Out of synchronization             | synchronization.                    | $\left(272/4 \times \left(\begin{array}{c} number of forward \\ protection steps \end{array}\right)^{+123} \times 18 \text{ ms} \right)$ | (000H).                   |

| (000H, DB2)                        |                                     | This comes out at 10 to 12                                                                                                               | 2. Clear the CLR pin.     |

|                                    |                                     | seconds when the number of                                                                                                               | (Initial setting)         |

|                                    |                                     | forward protection steps is 8.                                                                                                           |                           |

| INT3                               | At the time error correction is     | When the time shown in the                                                                                                               | 1. Write DB3 = "1" to INT |

| Vertical/horizontal                | completed.                          | table below has elapsed after                                                                                                            | (000H).                   |

| 2nd error correction<br>completion |                                     | an error correction start signal                                                                                                         | 2. Clear the CLR pin.     |

| (000H, DB3)                        |                                     | is written (see table below).                                                                                                            | (Initial setting)         |

| Table 5.1.1 | Interrupt | Sources |

|-------------|-----------|---------|

|             | mitoriapt | 0001000 |

|                     | Error | Time     | Data        |

|---------------------|-------|----------|-------------|

| I I a sila a sata I | No*   | 0.138 ms | 0.4 hudaa   |

| Horizontal          | Yes   | 0.274 ms | 34 bytes    |

| Manthaal            | No*   | 1.090 ms | 070 history |

| Vertical            | Yes   | 2.178 ms | 272 bytes   |

\*Error correction is skipped when there is no error.

#### 5.1.2 INT Mask

This register controls interrupt generation.

|         | - 3        |       | (1) |     |     |     |     |     |     |     |

|---------|------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| Address | Read/write | Reset | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

| 001H    | Write      | value |     |     | —   | —   | 0   | 0   | 0   | 0   |

(1) DB0-DB3:

0: INT0-INT3 interrupt disabled

1: INT0-INT3 interrupt enabled

INTO: Receive interrupt

INT1: 1st horizontal error correction completion interrupt

- INT2: Out-of-sync interrupt

- INT3: Vertical/2nd horizontal error correction completion interrupt

Figure 5.1.1 INT Mask Register

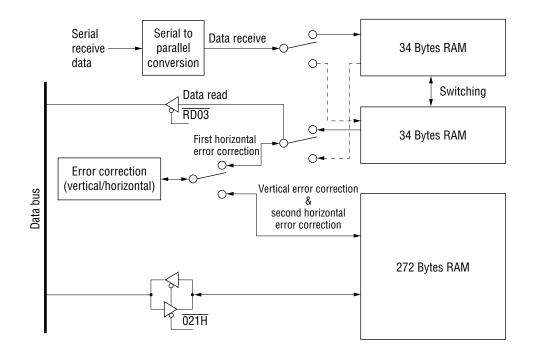

#### 5.2 RECEIVE DATA REGISTERS

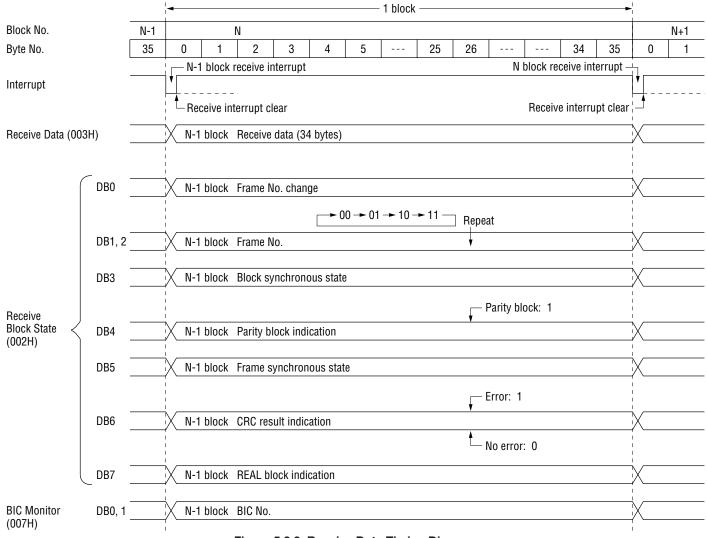

#### 5.2.1 Receive Block Status

This register indicates the status of the received block data, which consists of the following: (1) Frame Number Change, (2) Frame Number, (3) Block Synchronization Status, (4) Parity Block Indication, (5) Frame Synchronization Status, (6) Layer 2 CRC Result, and (7) Real Time Block Indication

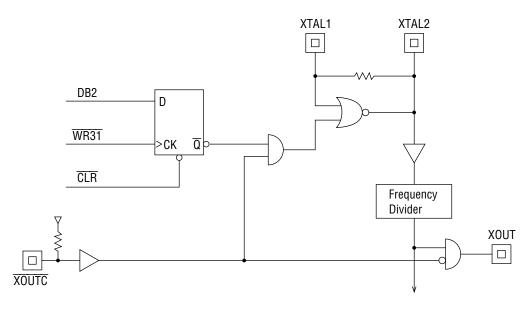

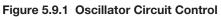

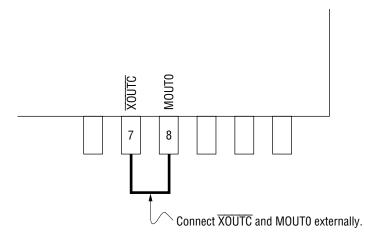

| - (7) - (6) - (6) - (4) - (3) - (2) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1) - (1 |            |       |     |     |     |     |     |     |     |     |  |  |