FET INPUT POWER OPERATIONAL AMPLIFIERS

# PA07 • PA07A

HTTP://WWW.APEXMICROTECH.COM (800) 546-APEX (800) 546-2739

# **FEATURES**

- LOW BIAS CURRENT FET Input

- PROTECTED OUTPUT STAGE Thermal Shutoff

- EXCELLENT LINEARITY Class A/B Output

- WIDE SUPPLY RANGE ±12V TO ±50V

- HIGH OUTPUT CURRENT ±5A Peak

# **APPLICATIONS**

- MOTOR, VALVE AND ACTUATOR CONTROL

- MAGNETIC DEFLECTION CIRCUITS UP TO 4A

- POWER TRANSDUCERS UP TO 100kHz

- TEMPERATURE CONTROL UP TO 180W

- PROGRAMMABLE POWER SUPPLIES UP TO 90V

- AUDIO AMPLIFIERS UP TO 60W RMS

## DESCRIPTION

The PA07 is a high voltage, high output current operational amplifier designed to drive resistive, inductive and capacitive loads. For optimum linearity, especially at low levels, the output stage is biased for class A/B operation using a thermistor compensated base-emitter voltage multiplier circuit. A thermal shutoff circuit protects against overheating and minimizes heatsink requirements for abnormal operating conditions. The safe operating area (SOA) can be observed for all operating conditions by selection of user programmable current limiting resistors. Both amplifiers are internally compensated for all gain settings. For continuous operation under load, a heatsink of proper rating is recommended.

This hybrid circuit utilizes thick film (cermet) resistors, ceramic capacitors and semiconductor chips to maximize reliability, minimize size and give top performance. Ultrasonically bonded aluminum wires provide reliable interconnections at all operating temperatures. The 8-pin TO-3 package is hermetically sealed and electrically isolated. The use of compressible washers and/or improper mounting torque will void the product warranty. Please see "General Operating Considerations".

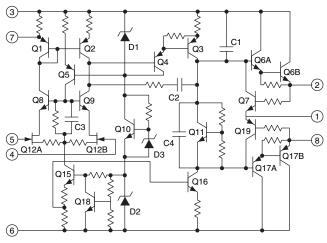

# **EQUIVALENT SCHEMATIC**

8-PIN TO-3 PACKAGE STYLE CE

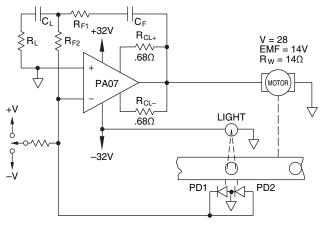

### **TYPICAL APPLICATION**

#### Negates optoelectronic instabilities Lead network minimizes overshoot SEQUENTIAL POSITION CONTROL

Position is sensed by the differentially connected photo diodes, a method that negates the time and temperature variations of the optical components. Off center positions produce an error current which is integrated by the op amp circuit, driving the system back to center position. A momentary switch contact forces the system out of lock and then the integrating capacitor holds drive level while both diodes are in a dark state. When the next index point arrives, the lead network of C1 and R1 optimize system response by reducing overshoot. The very low bias current of the PA07 augments performance of the integrator circuit.

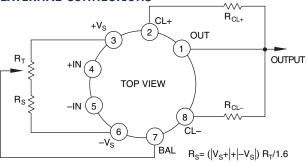

#### **EXTERNAL CONNECTIONS**

NOTE: Input offset voltage trim optional.  $R_{\tau} = 10K\Omega$  MAX

100V

5A

67W

±50V

200°C

-65 to +150°C

-55 to +125°C

±V<sub>c</sub> 300°C

#### **ABSOLUTE MAXIMUM RATINGS**

SUPPLY VOLTAGE, +V<sub>s</sub> to -V<sub>s</sub> OUTPUT CURRENT, within SOA POWER DISSIPATION, internal<sup>1</sup> INPUT VOLTAGE, differential INPUT VOLTAGE, common mode TEMPERATURE, pin solder - 10s TEMPERATURE, junction<sup>1</sup> **TEMPERATURE RANGE**, storage OPERATING TEMPERATURE RANGE, case

## **SPECIFICATIONS**

| SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                    |                                                                     |                                                                 |                      |             |                                                 |                       |                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------|----------------------|-------------|-------------------------------------------------|-----------------------|---------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                           | TEST CONDITIONS <sup>2</sup>                                                                                                                                                                                                                                                                                                                                       | MIN                                                                 | PA07<br>TYP                                                     | МАХ                  | MIN         | PA07A<br>TYP                                    | MAX                   | UNITS                                                         |

| INPUT<br>OFFSET VOLTAGE, initial<br>OFFSET VOLTAGE, vs. temperature<br>OFFSET VOLTAGE, vs. supply<br>OFFSET VOLTAGE, vs. power<br>BIAS CURRENT, initial <sup>3</sup><br>BIAS CURRENT, initial <sup>3</sup><br>BIAS CURRENT, initial <sup>3</sup><br>INPUT IMPEDANCE, DC<br>INPUT CAPACITANCE<br>COMMON MODE VOLTAGE RANGE <sup>4</sup><br>COMMON MODE REJECTION, DC | $\begin{array}{l} T_c = 25^{\circ}C \\ Full temperature range \\ T_c = 25^{\circ}C \\ Full temperature range \\ T_c = 25^{\circ}C \\ Full temperature range \\ Full temperature range \\ Full temperature range \\ Full temperature range \\ \end{array}$ | ±V <sub>s</sub> -10                                                 | .5<br>10<br>8<br>20<br>5<br>.01<br>2.5<br>10 <sup>11</sup><br>4 | ±2<br>30<br>50<br>50 | *           | ±.25<br>5<br>*<br>10<br>3<br>*<br>1.5<br>*<br>* | ±.5<br>10<br>10<br>10 | mV<br>μV/°C<br>μV/V<br>pA<br>pA/V<br>pA<br>Ω<br>pF<br>V<br>dB |

| GAIN<br>OPEN LOOP GAIN at 15Hz<br>GAIN BANDWIDTH PRODUCT @ 1MHz<br>POWER BANDWIDTH<br>PHASE MARGIN                                                                                                                                                                                                                                                                  | $T_{c} = 25^{\circ}C, R_{L} = 15\Omega$<br>$T_{c} = 25^{\circ}C, R_{L} = 15\Omega$<br>$T_{c} = 25^{\circ}C, R_{L} = 15\Omega$<br>Full temperature range, $R_{L} = 15\Omega$                                                                                                                                                                                        | 89                                                                  | 95<br>1.3<br>18<br>70                                           |                      | *           | *<br>*<br>*                                     |                       | dB<br>MHz<br>kHz<br>°                                         |

| OUTPUT<br>VOLTAGE SWING <sup>4</sup><br>VOLTAGE SWING <sup>4</sup><br>VOLTAGE SWING <sup>4</sup><br>CURRENT, peak<br>SETTLING TIME to .1%<br>SLEW RATE<br>CAPACITIVE LOAD, unity gain<br>CAPACITIVE LOAD, gain>4                                                                                                                                                    | Full temp. range, $I_o = 5A$<br>Full temp. range, $I_o = 2A$<br>Full temp. range, $I_o = 90mA$<br>$T_c = 25^{\circ}C$<br>$T_c = 25^{\circ}C$ , 2V step<br>$T_c = 25^{\circ}C$<br>Full temperature range<br>Full temperature range                                                                                                                                  | ±V <sub>s</sub> −5<br>±V <sub>s</sub> −5<br>±V <sub>s</sub> −5<br>5 | 1.5<br>5                                                        | 1<br>SOA             | *<br>*<br>* | *                                               | *<br>*                | V<br>V<br>Α<br>μs<br>V/μs<br>nF                               |

| POWER SUPPLY<br>VOLTAGE<br>CURRENT, quiescent                                                                                                                                                                                                                                                                                                                       | Full temperature range $T_c = 25^{\circ}C$                                                                                                                                                                                                                                                                                                                         | ±12                                                                 | ±35<br>18                                                       | ±50<br>30            | *           | *                                               | *                     | V<br>mA                                                       |

| THERMAL<br>RESISTANCE, AC, junction to case <sup>5</sup><br>RESISTANCE, DC, junction to case<br>RESISTANCE, junction to air<br>TEMPERATURE RANGE, case                                                                                                                                                                                                              | F>60Hz<br>F<60Hz<br>Meets full range specifications                                                                                                                                                                                                                                                                                                                | -25                                                                 | 1.9<br>2.4<br>30<br>25                                          | 2.1<br>2.6<br>+85    | *           | * * *                                           | *<br>*                | °C/W<br>°C/W<br>°C/W<br>°C                                    |

NOTES: \* The specification of PA07A is identical to the specification for PA07 in applicable column to the left.

1. Long term operation at the maximum junction temperature will result in reduced product life. Derate internal power dissipation to achieve high MTTF.

2. The power supply voltage for all specifications is the TYP rating unless otherwise noted as a test condition.

3. Doubles for every 10°C of temperature increase.

4.  $+V_s$  and  $-V_s$  denote the positive and negative supply rail respectively. Total V<sub>s</sub> is measured from  $+V_s$  to  $-V_s$ . 5. Rating applies if the output current alternates between both output transistors at a rate faster than 60Hz.

The internal substrate contains beryllia (BeO). Do not break the seal. If accidentally broken, do not crush, machine, or subject to temperatures in excess of 850°C to avoid generating toxic fumes.

# PA07 • PA07A

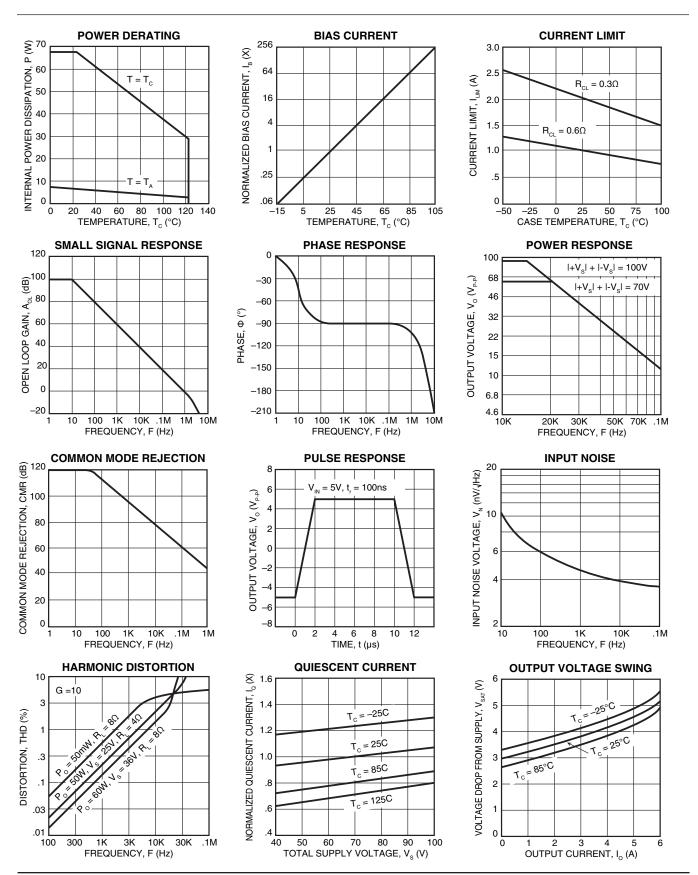

#### TYPICAL PERFORMANCE GRAPHS

APEX MICROTECHNOLOGY CORPORATION • TELEPHONE (520) 690-8600 • FAX (520) 888-3329 • ORDERS (520) 690-8601 • EMAIL prodlit@apexmicrotech.com

### OPERATING CONSIDERATIONS

## GENERAL

Please read Application Note 1 "General Operating Considerations" which covers stability, supplies, heat sinking, mounting, current limit, SOA interpretation, and specification interpretation. Visit www.apexmicrotech.com for design tools that help automate tasks such as calculations for stability, internal power dissipation, current limit; heat sink selection; Apex's complete Application Notes library; Technical Seminar Workbook; and Evaluation Kits.

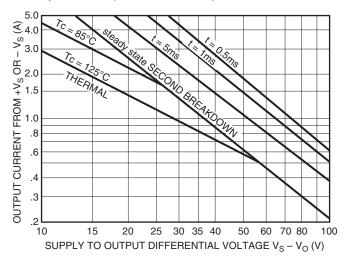

# SAFE OPERATING AREA (SOA)

The output stage of most power amplifiers has three distinct limitations:

- 1. The current handling capability of the wire bonds.

- 2. The second breakdown effect which occurs whenever the simultaneous collector current and collector-emitter voltage exceed specified limits.

- 3. The junction temperature of the output transistors.

# SAFE OPERATING AREA CURVES

The SOA curves combine the effect of these limits. For a given application, the direction and magnitude of the output current should be calculated or measured and checked against the SOA curves. This is simple for resistive loads but more complex for reactive and EMF generating loads. However, the following guidelines may save extensive analytical efforts.

1. For DC outputs, especially those resulting from fault conditions, check worst case stress levels against the new SOA graph.

For sine wave outputs, use Power Design<sup>1</sup> to plot a load line. Make sure the load line does not cross the 0.5ms limit and that excursions beyond any other second breakdown line do not exceed the time label, and have a duty cycle of no more than 10%.

For other waveform outputs, manual load line plotting is recommended. Applications Note 22, SOA AND LOAD LINES, will be helpful. A Spice type analysis can be very useful in that a hardware setup often calls for instruments or amplifiers with wide common mode rejection ranges. 2. The amplifier can handle any reactive or EMF generating load and short circuits to the supply rail or common if the current limits are set as follows at  $T_c = 85^{\circ}C$ :

| ±V <sub>s</sub> | SHORT TO ±V <sub>s</sub><br>C, L, OR EMF LOAD | SHORT TO<br>COMMON |

|-----------------|-----------------------------------------------|--------------------|

| 50V             | .21A                                          | .61A               |

| 40V             | .3A                                           | .87A               |

| 30V             | .46A                                          | 1.4A               |

| 20V             | .87A                                          | 2.5A               |

| 15V             | 1.4A                                          | 4.0A               |

These simplified limits may be exceeded with further analysis using the operating conditions for a specific application.

3. The output stage is protected against transient flyback. However, for protection against sustained, high energy flyback, external fast-recovery diodes should be used.

#### THERMAL SHUTDOWN PROTECTION

The thermal protection circuit shuts off the amplifier when the substrate temperature exceeds approximately 150°C. This allows heatsink selection to be based on normal operating conditions while protecting the amplifier against excessive junction temperature during temporary fault conditions.

Thermal protection is a fairly slow-acting circuit and therefore does not protect the amplifier against transient SOA violations (areas outside of the  $T_c = 25^{\circ}$ C boundary). It is designed to protect against short-term fault conditions that result in high power dissipation within the amplifier. If the conditions that cause thermal shutdown are not removed, the amplifier will oscillate in and out of shutdown. This will result in high power stresses, will destroy signal integrity and reduce the reliability of the device.

### **CURRENT LIMIT**

Proper operation requires the use of two current limit resistors, connected as shown in the external connections diagram. The minimum value for R<sub>CL</sub> is .12 $\Omega$ , however, for optimum reliability it should be set as high as possible. Refer to the "General Operating Considerations" section of the handbook for current limit adjust details.

<sup>1</sup> Note 1. Power Design is a self-extracting Excel spreadsheet available free from www.apexmicrotech.com