# Thermal Stability of MOSFETs

Prepared by: Alan Ball

ON Semiconductor

Application Engineering Manager

http://onsemi.com

A variety of applications use hot-swap controllers, often to increase the reliability of a system. However, a failure in the hot-swap circuit would defeat that purpose. When you use MOSFETs in their active region to control current, such as you would for a controller that operates in a constant-current mode of operation, they have an inherent failure mechanism. In this mode, the MOSFET can get hot spots and fail, long before the device exceeds its Safe Operating Area (SOA) ratings.

Engineers have long understood that MOSFETs are positive temperature coefficient devices. Therefore, as the temperature of the device increases, the resistance increases. In other words, higher temperatures result in lower currents. This fact is important if you want to operate MOSFETs in parallel. With a good thermal path between devices, the positive temperature coefficient reduces the current in the hottest device and forces more of it to flow in the cooler device, thereby avoiding thermal runaway.

Engineers often think of a MOSFET as a single power transistor, but it is a collection of thousands of tiny power FET cells connected in parallel. In terms of sharing current,

As the current density of a small group of cells increases, those cells heat up, increasing the resistivity of those cells and forcing current to flow in neighboring cells, which minimizes the thermal gradient and avoids hot spots. This process is an essential physical tenet that allows the parallel array of cells to function reliably.

If the MOSFET exhibits a negative thermal coefficient, today's parallel cell structure would cause serious reliability issues. In fact, in some modes of operation, the thermal coefficient goes negative. You can easily understand this phenomenon by looking at the transconductance curves for a FET device (refer to Reference 1).

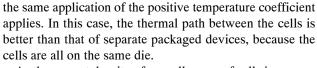

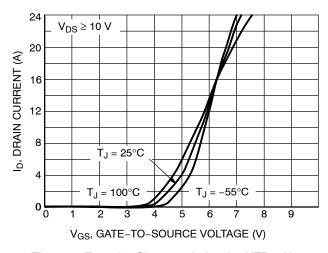

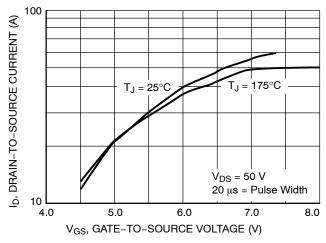

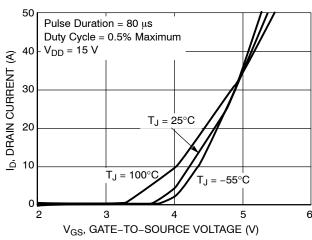

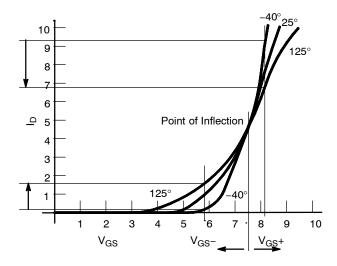

A typical set of transconductance curves clearly demonstrates this effect as shown by Figure 1. Below are curves from three typical devices used in hot swap applications.

Figure 1. Transfer Characteristics for NTD12N10

Figure 2. International Rectifier IRF530

Figure 3. Fairchild HUF75631SK8

All three devices shown have one thing in common: a point of inflection at which the temperature coefficient is zero. At greater gate—to—source voltages, the coefficient is positive, and, at lower gate—to—source voltages it is negative.

Figure 4 illustrates the change from negative to positive. At a gate–to–source voltage greater than that of the inflection point ( $V_{GS}$ +), a positive temperature coefficient exists. At this gate voltage, the drain conducts more than 9.0 A of current. However, at 125°C the drain current reduces to less than 7.0 A. The arrow at the left of Figure 4, which shows the current decreasing due to an increase in temperature, indicates this drop.

At a gate–to–source voltage below the inflection point ( $V_{GS}$ –) a negative temperature coefficient exists. At –40°C, the drain current is close to zero. However, at 125°C, the drain current is more than 1.0 A. A second arrow at the left of Figure 4 indicates this relationship, and the current rises due to an increase in temperature.

The implication is that when you are controlling the FET with a gate-to-source voltage below the inflection point, thermal runaway can occur. When one cell or a small group of cells becomes hotter than the surrounding cells, they tend to conduct more current. This situation, in turn, creates more heat, which allows more current to flow. These cells can pull a large amount of current and, if not limited in time, can cause the device to fail.

This situation is similar to the well-known phenomenon of secondary breakdown that occurs in bipolar transistors except that a bipolar junction transistor is a single device, and you can take steps to avoid its destruction. A power MOSFET contains thousands of parallel devices that are internal to the die, and you cannot individually protect them. If hot spots occur, the SOA characteristics of the heavily conducting cells differ greatly from those of the marginally conducting cells.

Figure 4. Typical Transconductance Curve

The thermal–runaway situation occurs when you use large devices at low current–limit settings. Even though it would appear to be desirable to use a very large MOSFET for an application such as a hot swap and limit it to a low current, it may be an inappropriate approach. Use of a very–low–on–resistance device offers low losses for steady–state operation but may cause the device to fail during a short circuit or an overload.

One way to overcome this problem is to directly sense the die temperature of the MOSFET by integrating the MOSFET with the controller using a monolithic approach. ON Semiconductor takes this approach with its new line of hot–swap ICs. In this case, the temperature can be sensed directly on the FET die. The location of the sense element on the die is critical for ensured protection of the device. If a hot spot occurs too far from the sense location, the device may be unable to protect itself.

Discrete hot-swap controllers employ a number of protection schemes. Thermal instability is an issue only if the controller can go into a constant-current mode of operation. Some protection circuits simply shut off the MOSFET switch if a number of conditions indicate a dangerous area of operation. Controllers that use a constant-current method of protection can use timers or other schemes along with the current-limit circuit to reduce the risk of failure.

Because system efficiency is an important parameter, it is tempting to use the largest MOSFET possible to reduce losses. It is important to keep in mind, however, that this approach may require you to make a trade-off with the system reliability if you are not mindful of the possible thermal instability. You can reliably use a large power device at a low current limit level if you handle it properly.

## **AND8199**

### Reference

|    | 1.6.6.6.1.6.1                                                                                                                             |

|----|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | Thermal Instability of Low Voltage Power–MOSFET's. IEEE Transactions on Power Electronics, Vol. 15, No. 3, May 2000, Alfio Consoli et al. |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

|    |                                                                                                                                           |

#### AND8199

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 61312, Phoenix, Arizona 85082–1312 USA Phone: 480–829–7710 or 800–344–3860 Toll Free USA/Canada Fax: 480–829–7709 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.