## **PRODUCT SUMMARY**

#### INTRODUCTION

S5D2509 is a stand-alone OSD Processor, which is used to display monitor adjustment or status information as a certain character or symbol on screen. Its basic operation includes making the R/ G/ B signal for the character or symbol by controlling the internal memory, synchronizing it with the horizontal flyback signal, and mixing it with the main video signal in the video AMP IC. The font data for making the character or symbol is stored in the internal ROM. It is accessed and controlled by the control data, transmitted from the micro controller through the I<sup>2</sup>C bus. The chip contains internal PLL circuitry, so all timing control signals, including the system clock, are synchronized with the horizontal flyback signal.

## FEATURES

- Enough font to support multiple language : 448 Standard Fonts + 16 Multi-Color Fonts

- Wide Operating (Horizontal) Frequency Range : 30kHz 120kHz

- Four Selectable OSD Resolutions : 640, 800, 1024 and 1280 Dots/ Line

- Pixel Frequency provided by On-Chip PLL : 19.2MHz 153.6MHz

- General Font Matrix : 12 × 18

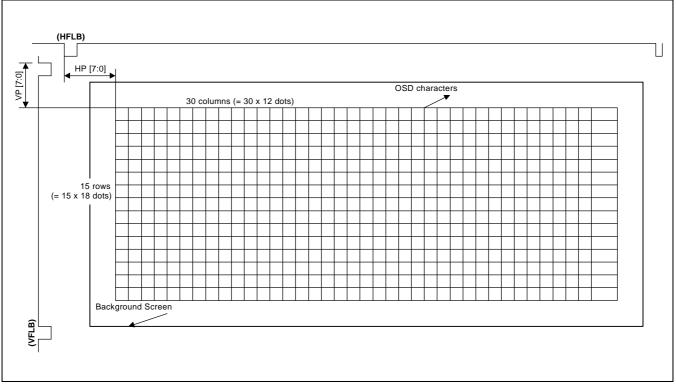

- Fully Programmable Display Area : 15 Rows × 30 Columns

- Popular MCU Interface : I<sup>2</sup>C Protocol

- Built in 1K-byte SRAM

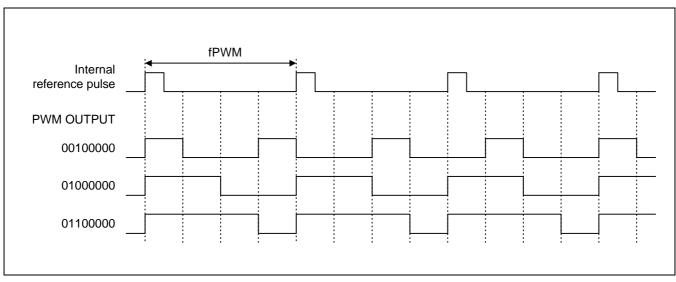

- PWM DAC Channels with 8 Bit Resolution : 8EA

- Selectable Character Color (Up to 16 Color) : Font basis

- Selectable Raster Color (Up to 16 Color) : Font basis

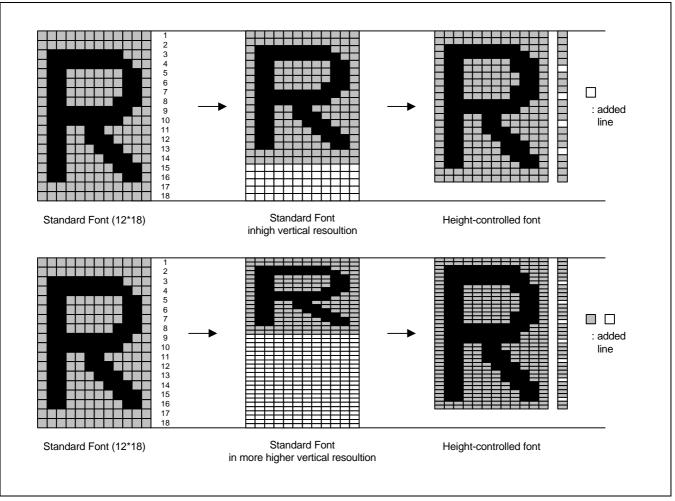

- Programmable and Auto-adjustable Vertical Height of Character : Range 18 63

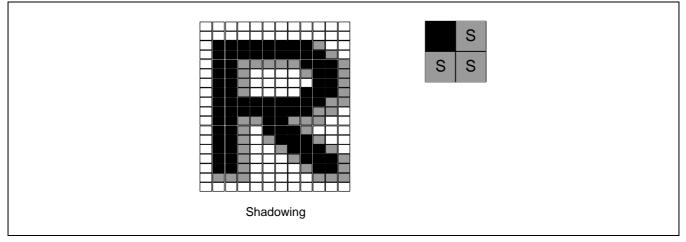

- Character Blinking and Shadowing : Font basis

- Programmable Symmetrical Row to Row Spacing : Range 0 31

- Horizontal Starting Position : 256 different positions (6 dots for each step)

- Vertical Starting Position : 256 different positions (4 scan line for each step)

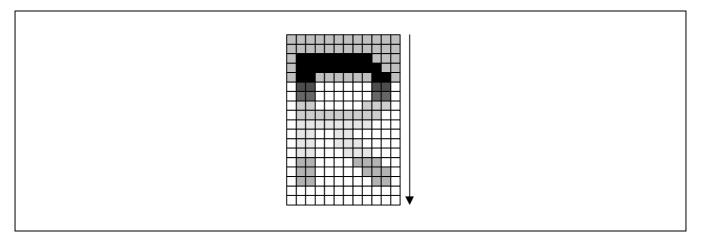

- Scrolling : Effect where 1 character line is scrolled up or down

- 4 Programmable Window Function and Window Priority Control

- Selectable Window Shadow Width : H/ V 2, 4, 6 and 8 Dots

- Supports Background Video Transparency : Font basis or Window basis

- Full White Pattern Generation for Manufacturing Mode

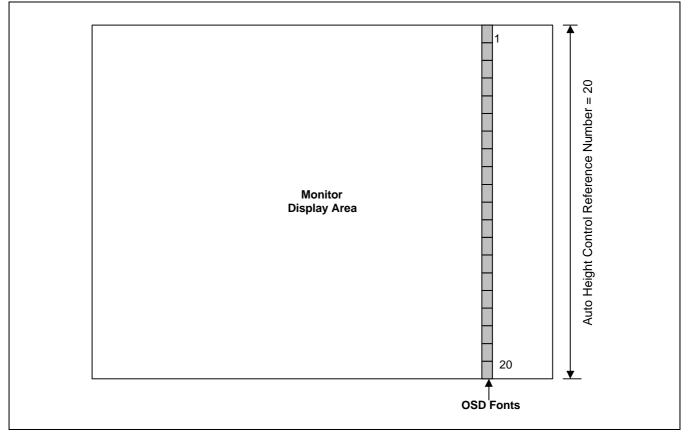

- Auto Character Height Control

- Full-Screen Display RAM Erasing

- OSD Vertical Bouncing Auto-Detecting & Correction

# **BLOCK DIAGRAM**

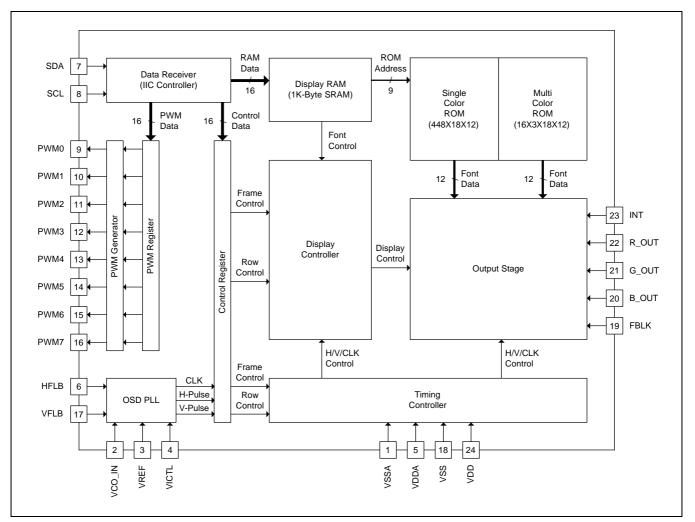

The OSD Processor consists of 8 blocks on the top level as shown "Figure 1: Functional block diagram".

There are 4 input signals for the OSD Processor, which are serial data (SDA), clock (SCL) form a micro controller and sync signals (HFLB and VFLB) from the H/ V sync processor. Through the serial data line, all information for the OSD operation are transferred. Here, the protocol is  $l^2C$  bus.

The data receiver block is a decoder for decoding the serial input data from a micro controller. The serial data is converted to a 16-bit parallel format at the data receiver block. The parallel data are transported to the RAM or registers by the bus line. The internal bus is a kind of star-bus type.

Control data comes from the data receiver is used to generate the control signals that control the character size, character position, blank mode, blink mode, background color, and etc, in timing controller and display unit block. All timing signals to read/ write data from/ to the internal RAM and ROM are also generated in the timing controller block. In the PLL block, the internal system clock that is synchronized with HFLB is generated, which is used as a timing reference signal for the OSD processor.

Figure 1. Functional Block Diagram

## **PIN CONFIGURATIONS**

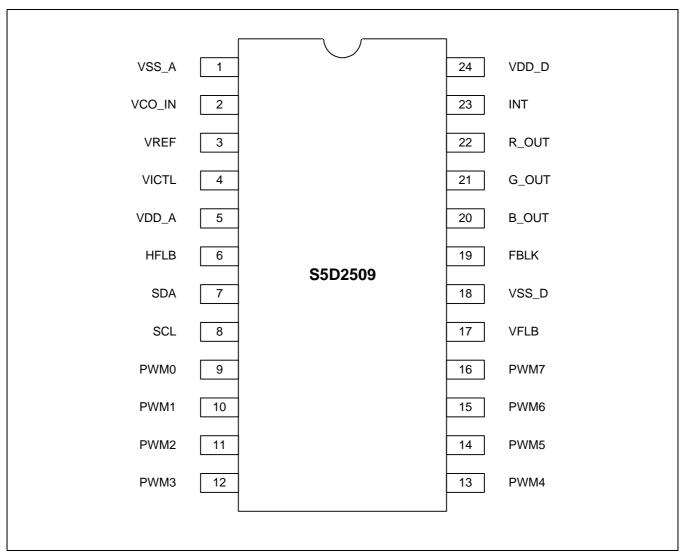

Package Type of the S5D2509 is 24-DIP-300.

Pin Configuration including PWM Port (9 — 16 Pin) 8 channels is shown in the figure bellow.

Figure 2. Pin configuration

# **PIN DESCRIPTIONS**

| Pin No. | Signal | Active | I/ O    | Description                                                                                                                                                                                                                                                                                                             |

|---------|--------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VSSA   | -      | -       | This pin provides the signal ground to the PLL circuit. We recommend that you separate the analog ground from the digital ground as shown in 'Figure 3 : S5D2509 Application Circuit' (6p) for optimum performance (S5D2509's built-in PLL is sensitive to noise due to wide range PLL characteristics).                |

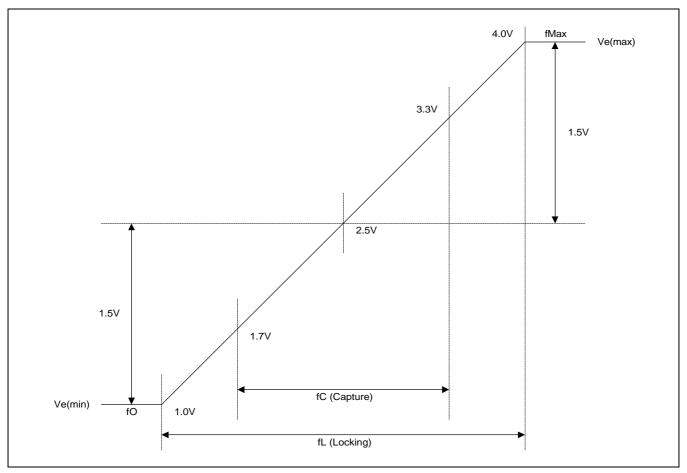

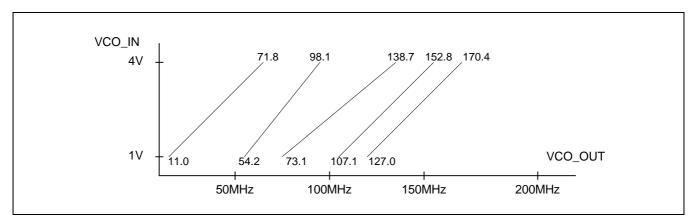

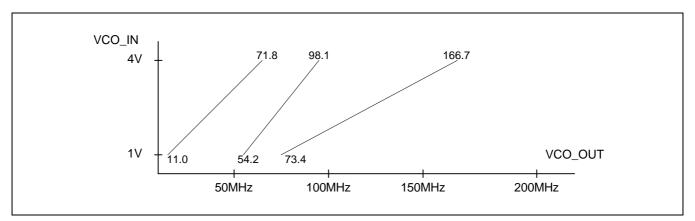

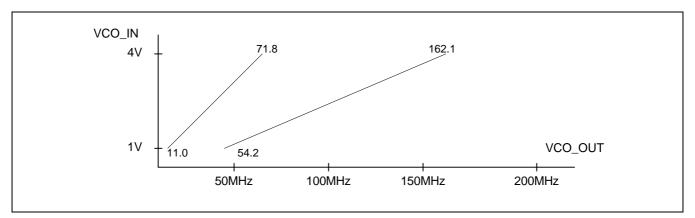

| 2       | VCO_IN | -      | -       | This voltage is made in an external loop filter and sent to VCO's input block. Operation voltage range is about 1 — 4V, and you can raise immunity against external noise if you want lower the VCO sensitivity by allowing the max operation voltage range possible at 5V power voltage. Refer to 'PLL Control' (30p). |

| 3       | VREF   | -      | -       | Connect to ground using resistance in order to make the reference current that need to operate internal PLL (PLL region control). Refer to 'PLL Control' (30p)'.                                                                                                                                                        |

| 4       | VICTL  | -      | -       | PLL gain controlled by controlling VCO Current.                                                                                                                                                                                                                                                                         |

| 5       | VDDA   | -      | -       | This pin supplies +5V supply voltage to the PLL circuit. We recommend that you divide the digital and analog power for PLL as you did in 'Figure 3 : S5D2509 Application Circuit (6p)' to prevent the influence of clock noise on the                                                                                   |

|         |        |        |         | digital block.                                                                                                                                                                                                                                                                                                          |

| 6       | HFLB   | LOW    | Input   | Horizontal Flyback : This pin is reference signal source of the internal PLL.                                                                                                                                                                                                                                           |

| 7       | SDA    | -      | In/ Out | Serial Data ( $I^2C$ ). We recommend that you use the serial resistor about 1/ 10 value of 5V pull-up resistor as $I^2C$ protocol.                                                                                                                                                                                      |

| 8       | SCL    | -      | In/ Out | Serial Clock ( $I^2C$ ). We recommend that you use the serial resistor about 1/ 10 value of 5V pull-up resistor as $I^2C$ protocol.                                                                                                                                                                                     |

| 9       | PWM0   | -      | Output  | PWM DAC0 Output for DC Control other Peripheral.                                                                                                                                                                                                                                                                        |

| 10      | PWM1   | -      | Output  | PWM DAC1 Output for DC Control other Peripheral.                                                                                                                                                                                                                                                                        |

| 11      | PWM2   | -      | Output  | PWM DAC2 Output for DC Control other Peripheral.                                                                                                                                                                                                                                                                        |

| 12      | PWM3   | -      | Output  | PWM DAC3 Output for DC Control other Peripheral.                                                                                                                                                                                                                                                                        |

| 13      | PWM4   | -      | Output  | PWM DAC4 Output for DC Control other Peripheral.                                                                                                                                                                                                                                                                        |

| 14      | PWM5   | -      | Output  | PWM DAC5 Output for DC Control other Peripheral.                                                                                                                                                                                                                                                                        |

| 15      | PWM6   | -      | Output  | PWM DAC6 Output for DC Control other Peripheral.                                                                                                                                                                                                                                                                        |

| 16      | PWM6   | -      | Output  | PWM DAC7 Output for DC Control other Peripheral.                                                                                                                                                                                                                                                                        |

| 17      | VFLB   | LOW    | Input   | Vertical Flyback signal : Similar to pin #6, this inputs the negative polarity vertical flyback signal for syncronizing the vertical control circuit.                                                                                                                                                                   |

### Table 1. Pin Description

| Pin No. | Signal | Active | I/ O   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18      | VSS    | -      | -      | Ground for Digital Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 19      | FBLK   | -      | Output | Fast Blank Signal : OSD R/ G/ B output is recognized in the Pre-<br>AMP only when this output pin is high. In other words, if FBLK is<br>low, the OSD R/ G/ B output is not selected in the Pre-AMP.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20      | B_OUT  | -      | Output | OSD Signal Output (B).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 21      | G_OUT  | -      | Output | OSD Signal Output (G)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 22      | R_OUT  | -      | Output | OSD Signal Output (R)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 23      | INT    | -      | Output | This output pin signifies the color intensity. If you set the intensity control bit to '1' (high) and use with the Pre-AMP supporting intensity function, this pin outputs logic high while the specified character or raster is being displayed. If this pin's output is high, the color level is reduced to half and shows a difference in color level from when it is low, allowing a 16-color choice when this intensity pin and R/ G/ B output are combined. For example, if R, G, B are all high, white is output. If you set the INT bit to '1' (high), the color level becomes reduced to half and outputs gray. |

| 24      | VDD    | -      | Output | +5V Supply Voltage for Digital Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 1. Pin Description (Continued)

\* In the table above, only HFLB and VFLB's active column is low. This means that HFLB and VFLB are set so that they are inputted as active low in default. For more information, please refer to 'Register Descriptions (13p)'.

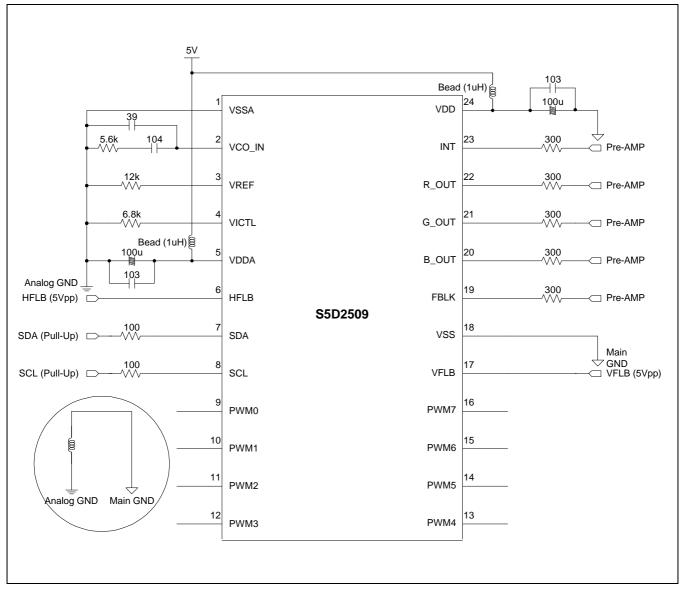

# **APPLICATION CIRCUIT**

- When you are doing PCB Art Work, separate analog VDD and digital VDD.

- Using PCB pattern, separate analog Ground and main ground, and then connect two ground with Bead as following figure.

- Because communication noise influences the operation of PLL, I<sup>2</sup>C communication line keep away from analog block (Pin #1 — #5) as possible as.

- You can improve the monitor's video characteristics (OSD ringing, OSD smear) and regulation characteristics by adding serial resistance to S5D2509's output pins (Pin #19 — Pin #23).

Figure 3 : S5D2509 Application Circuit

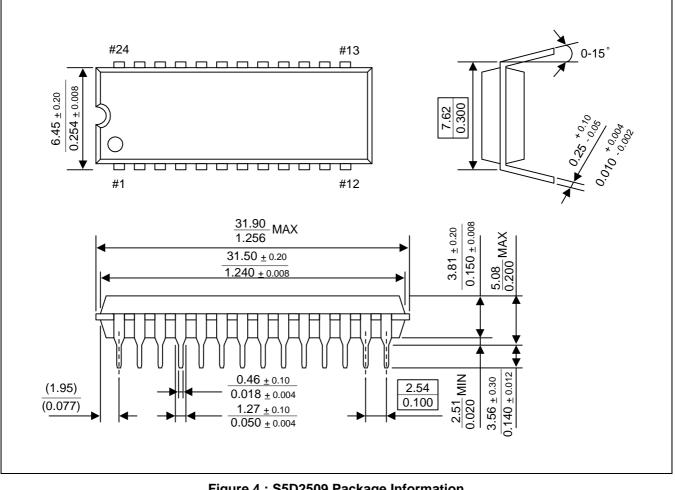

# **PACKAGE INFORMATION**

# SPECIFICATION

### ABSOLUTE MAXIMUM RATINGS

#### **Table 2. Absolute Maximum Ratings**

| Parameters                  | Symbol | Value     | Unit |

|-----------------------------|--------|-----------|------|

| Supply Voltage              | VDD    | 0 — 6.5   | V    |

| Input Voltage               | VI     | 0 — 5.25  | V    |

| Power Dissipation           | Pd     | 1200      | mW   |

| Operating Temperature Range | Topr   | -20 — 70  | °C   |

| Storage Temperature Range   | Tstg   | -40 — 125 | °C   |

♣ PKG Thermal Resistance : 64.2°C / W

### **ELECTRICAL CHARACTERISTICS**

### **DC Electrical Characteristics**

## **Table 3. DC Electrical Characteristics**

$(Ta = 25^{\circ}C, VDD_A = VDD_D = 5V)$

|                                        |        |        | ,    | , _     | _ ,  |

|----------------------------------------|--------|--------|------|---------|------|

| Parameters (Conditions)                | Symbol | Min.   | Тур. | Max.    | Unit |

| Supply Voltage                         | VDD    | 4.75   | 5.00 | 5.25    | V    |

| Supply Current (No load on any output) | IDD    | -      | -    | 25      | mA   |

| Input Voltage                          | VIH    | 0.8VDD | -    | -       | V    |

|                                        | VIL    | -      | -    | VSS+0.4 | V    |

| Output Voltage                         | VOH    | 0.8VDD | -    | -       | V    |

| $(lout = \pm 1mA)$                     | VOL    | -      | -    | VSS+0.4 | V    |

| Input Leakage Current                  | IIL    | -10    | -    | 10      | uA   |

| VCO Input Voltage                      | VVCO   | -      | 2.5  | -       | V    |

## **OPERATION TIMING**

#### OUTPUT SIGNAL R/ G/ B\_OUT, INT, FBLK

## Table 4: Rise/ Fall Time of Output Signal

(Ta = 25°C, VDDA = VDD=5V, CLOAD = 30pF)

| Parameters (Conditions) | Symbol | Min. | Тур. | Max. | Unit |

|-------------------------|--------|------|------|------|------|

| Rise Time               | tR     | -    | -    | 2    | nsec |

| Fall Time               | tF     | -    | -    | 2    | nsec |

#### Input Signal HFLB, VFLB

#### **Table 5: Frequency of Input Signal**

| Parameters(Conditions)              | Symbol | Min. | Тур. | Max. | Unit |

|-------------------------------------|--------|------|------|------|------|

| Horizontal Flyback Signal Frequency | fHFLB  | -    | -    | 120  | kHz  |

| Vertical Flyback Signal Frequency   | fVFLB  | -    | -    | 200  | Hz   |

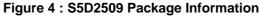

#### C Interface SDA, SCL

## Table 6: Operating Time of I<sup>2</sup>C Interface

| Parameters (Conditions)        | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------------|--------|------|------|------|------|

| SCL Clock Frequency            | fSCL   | -    | -    | 300  | kHz  |

| Hold Time for start condition  | ths    | 500  | -    | -    | ns   |

| Set Up Time for stop condition | tsus   | 500  | -    | -    | ns   |

| Low Duration of clock          | tlow   | 400  | -    | -    | ns   |

| High Duration of clock         | thigh  | 400  | -    | -    | ns   |

| Hold Time for data             | thd    | 0    | -    | -    | ns   |

| Set Up Time for data           | tsud   | 500  | -    | -    | ns   |

| Time between 2 access          | tss    | 500  | -    | -    | ns   |

| Fall Time of SDA               | tfSDA  | -    | -    | 20   | ns   |

| Rise Time of both SCL and SDA  | trSDA  | -    | -    | -    | ns   |

Figure 5 : Operation Timing - SDA and SCL

# FUNCTIONAL DESCRIPTIONS

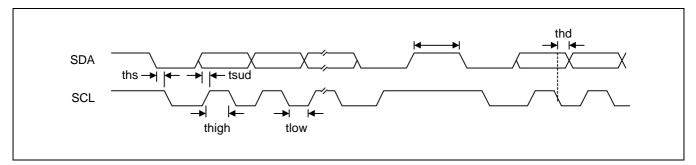

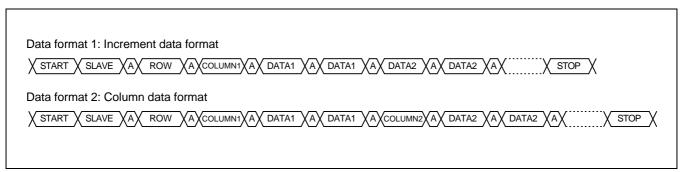

### DATA TRANSMISSION

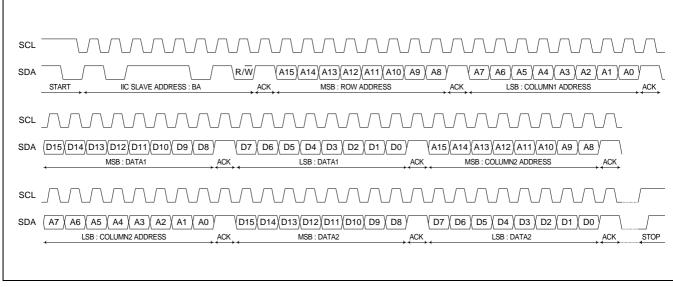

The communication interface between S5D2509 and MCU follows the I<sup>2</sup>C protocol. As shown in "Figure 6 : Data Transmission Format", It supports two formats to transmit 16-bits register values effectively. After the starting pulse, the transmission takes place in the following order: Slave address with R/W bit, each 1-byte row/ column address, 2-byte data, and stop condition. An acknowledge signal is received for each byte, excluding only the start/ stop condition. It assigns 8-bits out of 16-bits to font address for selecting character code, because attribute bits of the "Character & Attribute Registers" is composed of 8-bits for convenient adjustment with font unit. By the way, S5D2509 needs 9-bits for addressing 464-fonts by reason that it supports 464-fonts.

Therefore, the needed 1-bit is assigned to the RMSB of column address bit pattern as follows "Address Bit Pattern for Display Registers Data". For using the RMSB, it must be enabled the COLEN bit of row address bit pattern.

S5D2509's slave address is BAh. It is BBh in read mode, and BAh in write mode.

#### Address Bit Pattern for Display Registers Data

(a) Row Address Bit Pattern

R3 - R0 : Valid Data for Row Address

| A15   | A14                                | A13 | A12 | A11 | A10 | A9 | A8 |

|-------|------------------------------------|-----|-----|-----|-----|----|----|

| COLEN | Х                                  | Х   | C4  | R3  | R2  | R1 | R0 |

|       | 201 ENL Only a Data Franci Frankla |     |     |     |     |    |    |

COLEN : Column Data Format Enable

(b) Column Address Bit Pattern

C4 - C0 : Valid Data for Column Address

| A7                                              | A6 | A5 | A4 | A3 | A2            | A1 | A0 |

|-------------------------------------------------|----|----|----|----|---------------|----|----|

| RMSB                                            | Х  | Х  | C4 | C3 | C2            | C1 | C0 |

| RMSB : ROM Address MSB Bit 'X' : Don't care bit |    |    |    |    | on't care bit |    |    |

RMSB : ROM Address MSB Bit

#### **Data Transmission Format**

## **Figure 6: Data Transmission Formats**

## SDA / SCL Signal at Communication Data Format 1 : Auto Increment Data Format

Figure 7 : SDA/ SCL Timing Chart (Format 1)

## Data Format 2 : Column Data Format

Figure 8 : SDA/ SCL Timing Chart (Format 2)

\* As you can see the "Figure 7, 8 : SDA/ SCL Timing Chart", just the time when the SCL is low, the SDA can be occurred transition. Therefore, you must program MCU not to occur timing violation.

## **MEMORY MAP**

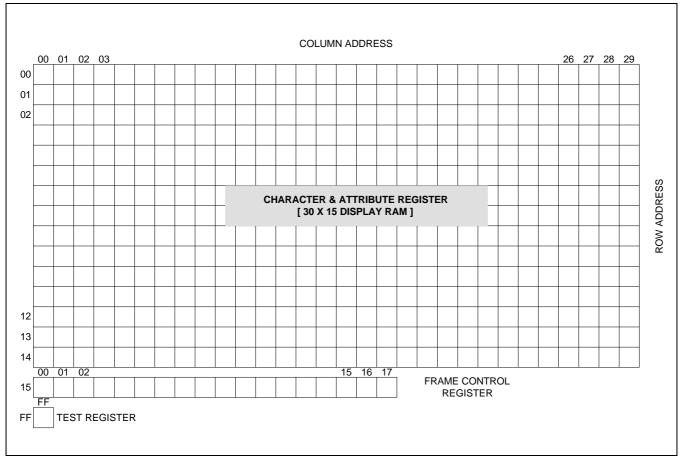

Figure 9: Memory Map of Display Registers

The display RAM's address of the row and column number are assigned in order. The display RAM is composed of 2 register groups (Character & Attribute Register, Frame Control Register).

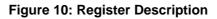

The display area in the monitor screen is 30 columns X 15 rows, so the related "Character & Attribute Registers" are also 30 columns X 15 rows. Each register has a character address and characteristics corresponding to the display location on the screen, and one register is composed of 16-buts. The lower 8-bits and the extended 1-bit (the MSB of row/ column address) are used for selecting a font out of 464 ROM fonts, and upper 8-bits are assigned to give a character attribute to a selected font.

"Frame Control Registers" are in the 15th row. "Frame Control Register 0 — 2" control with frame unit display position of the OSD, height of character, blinking, scrolling, and etc function. "Frame Control Register 3" select extended codes to control 'Blink', 'Shadow', 'Character intensity', and 'Raster intensity'. "Frame Control Register 4" specify the reference value for "Auto height control" and "Row to row space". "Frame Control Register 5 — 13" control in relation to 4-windows. "Frame Control Register 14 — 17" are registers for PWM control. Each PWM control register is composed of two channel with 8-bits resolution and control 8 PWM ports.

Each register's configurations shown in "Figure 10 : Register Description (13p) ". For more detailed information, refer to "Table 7 : Register Description (14p) ".

#### **REGISTER DESCRIPTION**

| Character & Attribute Register : Row 00 -              | 4. Column 00 - 29                     |                            |

|--------------------------------------------------------|---------------------------------------|----------------------------|

| F E D C B A                                            | 8 7 6 5 4 3                           | 2 1 0                      |

| Blink SHA RB RG RR CB C                                | CR C7 C6 C5 C4 C3                     | C2 C1 C0                   |

| CTL1 CTL0<br>Extended Code Raster Color Charact        | Color Character Code (256 Fo          | ont Address)               |

| Frame Control Register 0 : Row 15, Colu                | 00                                    |                            |

| F_E_D_C_B_A                                            | 8 7 6 5 4 3                           | 2 1 0                      |

|                                                        | I FullW ExEN BGEN ScrEN ScrT BliE     |                            |

|                                                        |                                       |                            |

| Frame Control Register 1 : Row 15, Colu                | 01                                    |                            |

| F E D C B A                                            | 8 7 6 5 4 3                           | 2 1 0                      |

|                                                        | DOTO HPOL VPOL CH5 CH4 CH3            |                            |

| PLL Control                                            | Polarity Character                    | Height Control             |

| Frame Control Register 2 : Row 15, Colu                |                                       | -                          |

| F E D C B A                                            | 8 7 6 5 4 3                           | 2 1 0                      |

| HP7 HP6 HP5 HP4 HP3 HP2 H                              |                                       |                            |

| Horizontal Start Position                              | Vertical Start Po                     | sition                     |

|                                                        |                                       |                            |

| Frame Control Register 3 : Row 15, Colu<br>F E D C B A |                                       | 2 1 0                      |

| F E D C B A<br>Blink SHA RINT CINT Blink SHA RI        |                                       |                            |

| CTL11 CTL10                                            | CTL01                                 | CTL00                      |

|                                                        |                                       | 01200                      |

| Frame Control Register 4 : Row 15, Colu                |                                       |                            |

| F E D C B A<br>AREF5 AREF4 AREF3 AREF2 AR              | <u>8 7 6 5 4 3</u><br>1 AREF0 RS4 RS3 | 2 1 0<br>3 RS2 RS1 RS0     |

| Auto Height CTL Reference                              |                                       | Row Space                  |

| Auto Height CTL Reference                              | 10                                    | Row Space                  |

| Frame Control Register 5, 7, 9, 11 : Row               | , Column 05, 07, 09, 11               |                            |

| F E D C B A<br>WIN_I WIN_BWIN_GWIN_RRSTR3RSTR2RS       | 8 7 6 5 4 3                           | 2 1 0<br>03REND2REND1REND0 |

|                                                        |                                       |                            |

| Window Color Window Start Ro                           | Address Shadow Width Wind             | dow End Row Address        |

| Frame Control Register 6, 8, 10,12 : Row               | 5, Column 06, 08, 10, 12              |                            |

| F E D C B A                                            | 8 7 6 5 4 3                           | 2 1 0<br>D3CEND2CEND1CEND0 |

|                                                        |                                       |                            |

| Window Start Column                                    | dress Window E                        | nd Column Address          |

| Frame Control Register 13 : Row 15, Col                | in 13                                 |                            |

| F E D C B A                                            | 8 7 6 5 4 3                           | 2 1 0                      |

| WPR31WPR30 WF                                          | 1WPR20 WPR11WPR10 -                   | - WPR01WPR00               |

| Window Priority 3 Window                               | Priority 2 Window Priority 1          | Window Priority 0          |

| Frame Control Register 14 ~ 17 : Row 15                | Column 14 ~ 17                        |                            |

| F E D C B A                                            | 8 7 6 5 4 3                           | 2 1 0                      |

|                                                        |                                       | 13 PWM2 PWM1 PWM0          |

| PWM1 / PWM3 / PWM5 / PWM7                              | PWM0 / PWM2 / PW                      | M4/ PWM6                   |

|                                                        |                                       |                            |

| Table 7: Register | Description |

|-------------------|-------------|

|-------------------|-------------|

| Registers                             | Bits                      | Description                                                                                                                                                                                                                                |

|---------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Character &<br>Attribute<br>Registers | Blink (Bit F)             | Character Blink<br>Set this bit to activate character blinking effect or use as 'CTL1' bit for selecting<br>"Extended code set".                                                                                                           |

| (Row 00 — 14,<br>Column               | SHA (Bit E)               | <b>Character Shadow</b><br>Set this bit to activate character shadowing effect or use as 'CTL0' bit for selecting "Extended code set".                                                                                                     |

| 00 — 29)                              | RB, RG ,RR<br>(Bit D — B) | Raster Color<br>A color out of 16-colors is selected by these 3-bits and 'RINT' bit in "Frame<br>Control Register 3" as raster color.                                                                                                      |

|                                       | CB, CG, CR<br>(Bit A — 8) | <b>Character Color</b><br>A color out of 16-colors is selected by these 3-bits and 'CINT' bit in "Frame<br>Control Register 3" as character color.                                                                                         |

|                                       | C7 — C0<br>(Bit 7 — 0)    | Character Code Address<br>These 8-bits is used for accessing 256 ROM fonts. If you access over 256<br>FOM fonts, Column data format must be used. Column address MSB 'RMSB'<br>bit is used for MSB of 9-bits ROM fonts address.            |

| Frame Control                         | Bit F — B                 | Reserved.                                                                                                                                                                                                                                  |

| Registers-0<br>(Row15,                | PFEN (Bit A)              | <b>Programmable Full White Pattern Enable</b><br>As size as you want, you can determine full white pattern by using "Window size" at 320 OSD resolution. On the other hand, 'FullW' bit is used automatic "Full white pattern generation". |

| Column00)                             | AutoH (Bit 9)             | Auto Adjustable Vertical Font Height Control<br>If this bit is high, height of font is sustained as 'AREF' Bits regardless of video<br>input mode.                                                                                         |

|                                       | FullW (Bit 8)             | Full White Pattern Generation<br>If this bit is set high, OSD outputs full white pattern automatically.                                                                                                                                    |

|                                       | ExEN (Bit 7)              | <b>Extended Code Enable</b><br>If this bit is set high, Bit F/ E in "Character & Attribute Registers" are used for<br>selecting extended code set 'CTL00 — CTL11'.                                                                         |

|                                       | BGEN (Bit 6)              | Back Ground Enable<br>If you set this bit to '1', black color of OSD raster area is transparent.<br>This control bit is aimed for round-type OSD window generation.                                                                        |

|                                       | Scrl (Bit 5)              | Scroll Enable Refer to 'Scrolling (28p)'.                                                                                                                                                                                                  |

|                                       | ScrT (Bit 4)              | Scroll Time Control If this bit is '1', the scroll time is 0.5sec, otherwise 1.0sec.                                                                                                                                                       |

|                                       | BliEN (Bit 3)             | Blink Enable If you set this bit to high, blink the font with 'Blink' attribute.                                                                                                                                                           |

|                                       | BliT (Bit 2)              | Blink Time Control If this bit is '1', the blink time is 0.5sec, otherwise 1.0sec.                                                                                                                                                         |

|                                       | Erase (Bit 1)             | RAM Erasing RAM data are erased by setting this bit. Refer to 'Display RAM (19p)'.                                                                                                                                                         |

|                                       | EN (Bit 0)                | OSD Enable The character display is controlled by this bit. If this bit is high,<br>OSD is enable. Otherwise, disable. When this bit is disabled, OSD isn't output<br>inspite of writing control data.                                     |

| Registers                               | Bits                     |                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                     |             | Desc                                             | ription   |     |           |                 |

|-----------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------|-----------|-----|-----------|-----------------|

| Frame Control<br>Registers-1<br>(Row15, | CP2 — CP0<br>(Bit F — D) | This is th                                                                                                                                                                                                                                                                                                                                                                                                 | e PLL b                                                                                                                                                                                                                                                                                                                             | lock's inte | urrent Contro<br>ernal phase d<br>ermined by the | etector   |     | tatus, co | nverted into    |

| Column01)                               |                          | CP2                                                                                                                                                                                                                                                                                                                                                                                                        | CP1                                                                                                                                                                                                                                                                                                                                 | CP0         | Current                                          | CP2       | CP1 | CP0       | Current         |

|                                         |                          | 0                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                   | 0           | 40μΑ                                             | 1         | 0   | 0         | 160µA           |

|                                         |                          | 0                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                   | 1           |                                                  | 1         | 0   | 1         | 200μΑ           |

|                                         |                          | 0                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                   | 0           | 80μΑ                                             | 1         | 1   | 0         | 240µA           |

|                                         |                          | 0                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                   | 1           | 120µA                                            | 1         | 1   | 1         | 280μΑ           |

|                                         | HF2 — HF0<br>(Bit C — A) | PLL's h<br>is relate<br>frequen<br>refer to                                                                                                                                                                                                                                                                                                                                                                | <b>Horizontal Frequency</b><br>PLL's horizontal frequency is decided by the combination of these 3-bits. This<br>is related to the selection of DOT[1:0], so you can't numerically express the<br>frequency range with only the HF[2:0] selection. For more information, please<br>refer to 'Separating region of frequency (31p)'. |             |                                                  |           |     |           |                 |

|                                         | DOT1, DOT0<br>(Bit 9,8)  | Resolution Control (Dots/ Line)                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                     |             |                                                  |           |     |           |                 |

|                                         |                          | Dot1         dot0         No. Of Dots           0         0         640 dots/line                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                     |             |                                                  |           |     |           |                 |

|                                         |                          | 0 1 800 dots/line                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                     |             |                                                  |           |     |           |                 |

|                                         |                          |                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                   | 0           | 1024 dots/line                                   |           |     |           |                 |

|                                         |                          |                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                   | 1           | 128                                              | 0 dots/li |     |           |                 |

|                                         |                          | As shown above, the number of dots per horizontal line is decided by combination of these two bits.                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                     |             |                                                  |           |     |           |                 |

|                                         | HPOL (Bit 7)             | <b>Polarity of Horizontal Fly Back Signal</b><br>If this bit is '1', HFLB's polarity is positive, and if '0', it is negative. In other<br>words, this bit is set to '1' if active high, and '0' if active low.                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                     |             |                                                  |           |     |           |                 |

|                                         | VPOL (Bit 6)             | Polarity of Vertical Fly Back Signal<br>If this bit is '1', VFLB's polarity is positive, and if '0', it is negative. In other<br>words, this bit is set to '1' if active high, and '0' if active low.                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                     |             |                                                  |           |     |           |                 |

|                                         | CH5 — CH0<br>(Bit 5 — 0) | <b>Character Height Control</b><br>The purpose of CH[5:0] is to output OSD of a uniform size even if the resolution changes. If you adjust the value in the range of CH = $18 - CH = 63$ each line's repeating number is decided (standard height CH = $18$ is the reference value), by which the line is repeated. For more information on repeating number selection, refer to 'Character Height (26p)'. |                                                                                                                                                                                                                                                                                                                                     |             |                                                  |           |     |           |                 |

| Frame Control<br>Registers-2            | VP7 — VP0                |                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                     |             | <b>Control</b> (= VI<br>ght from the V           |           | ,   | edge.     |                 |

| (Row15,<br>Column02)                    | HP7 — HP0                | Signifie                                                                                                                                                                                                                                                                                                                                                                                                   | s delay o                                                                                                                                                                                                                                                                                                                           |             |                                                  | -         | - , | nc refere | ence edge to th |

Table 7: Register Description (Continued)

\* The purpose of bits 'HPOL', and 'VPOL' is to provide flexibility when using the S5D2509 IC. No matter which polarity you choose for the input signal, the IC will handle them identically, so you can select active high or active low according to your convenience.

| Registers                                            | Bits                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frame Control<br>Registers-3<br>(Row15,<br>Column03) | CTL11<br>(Bit F — C) | <b>Extended Code Set 11</b><br>If 'ExEN' bit of "Frame Control Register 0" is set to high, when Bit F (CTL1) and<br>Bit E (CTL0) of "Character & Attribute Registers" are set to '11', these extended<br>code set is referred as the combination of 'Blink', 'SHA', 'RINT', and 'CINT'.<br>That is, you may set previously the combination that you want. and then select<br>the extended code set by 'CTL1' and 'CTL0' bits.                                                                                                                                                                                                                                                                                        |

|                                                      | CTL10<br>(Bit B — 8) | <b>Extended Code Set 10</b><br>If 'ExEN' bit of "Frame Control Register 0" is set to high, when Bit F (CTL1) and<br>Bit E (CTL0) of "Character & Attribute Registers" are set to '10', these extended<br>code set is referred as the combination of 'Blink', 'SHA', 'RINT', and 'CINT'.<br>That is, you may set previously the combination that you want. and then select<br>the extended code set by 'CTL1' and 'CTL0' bits.                                                                                                                                                                                                                                                                                        |

|                                                      | CTL01<br>(Bit 7 — 4) | <b>Extended Code Set 01</b><br>If 'ExEN' bit of "Frame Control Register 0" is set to high, when Bit F (CTL1) and<br>Bit E (CTL0) of "Character & Attribute Registers" are set to '01', these extended<br>code set is referred as the combination of 'Blink', 'SHA', 'RINT', and 'CINT'.<br>That is, you may set previously the combination that you want. and then select<br>the extended code set by 'CTL1' and 'CTL0' bits.                                                                                                                                                                                                                                                                                        |

|                                                      | (Bit 3 — 0)          | <b>Extended Code Set 00</b><br>If 'ExEN' bit of "Frame Control Register 0" is set to high, when Bit F (CTL1) and<br>Bit E (CTL0) of "Character & Attribute Registers" are set to '00', these<br>extended code set is referred as the combination of 'Blink', 'SHA', 'RINT', and<br>'CINT'. That is, you may set previously the combination that you want. and then<br>select the extended code set by 'CTL1' and 'CTL0' bits.                                                                                                                                                                                                                                                                                        |

|                                                      | Bit F — E            | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Frame Control<br>Registers-4<br>(Row15,<br>Column04) | AREF<br>(Bit D — 8)  | Auto Height Control<br>Reference Number If 'AutoH' bit of "Frame Control Register 0" is set to '1', must<br>set these AREF[5:0] from 1 to 63. These control bits means the number of font<br>that you want to display in direction of vertical monitor line. In this case, that is,<br>'AutoH' bit is set to '1' and AREF[5:0] bits is set, OSD fonts sustain constant<br>vertical height regardless of video input mode change. If calculated font height<br>is smaller than 18, font height is displayed by 18 lines. In other hands, if 'AutoH'<br>Bit is set to '0', this function is ignored and character height is determined by<br>CH[5:0] of "Frame Control Register 1". Refer to 'Character Height (26p)'. |

|                                                      | Bit 7 — 5            | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

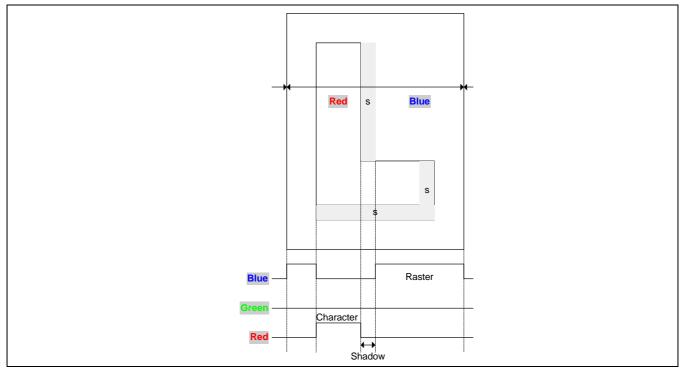

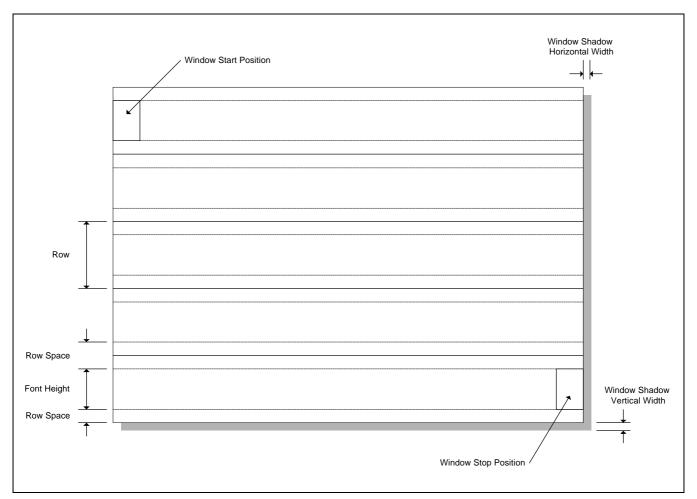

|                                                      | RS (Bit 4 — 0)       | <b>Row Space Number</b><br>It means the line number between a character row and the next row. The<br>default value is 0. For obtaining symmetrical row space, first and last line are<br>extended in each row. (line number for spacing = RS[4:0] 2) Refer to 'Figure<br>15 : OSD window area(24p)'.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Registers                                 | Bits                                             | Description                                                                                                                                                                                                                                                                                            |

|-------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frame Control<br>Registers-5,<br>7, 9, 11 | WIN_I,<br>WIN_B,<br>WIN_G,<br>WIN_R<br>(Bit F—C) | Window Raster Color Attribute The priority of raster color is determined by these bits is higher than raster color is determined by RB/ RG/ RR bits of "Character & Attribute Registers". 'WIN_I' bit may make 16-colors with the pre-AMP that support intensity function as like as 'CINT' or 'RINT'. |

| (Row15,<br>Column05, 07,<br>09, 11)       | RSTR3 —<br>RSTR0<br>(Bit B — 8)                  | Window Start Row Address : Range 0 — 15 It means the row address that window starts from. About actually start point, refer to 'III-6.3 Window Generation'(27p).                                                                                                                                       |

|                                           | HW1,HW0<br>(Bit 7 — 6)                           | Horizontal Width of Window Shadowing The horizontal width of window shadow is determined by these HW[1:0] bits setting as follows : (Horizontal Width = HW 2 Dots)                                                                                                                                     |

|                                           | VW1,VW0<br>(Bit 5 — 4)                           | Vertical Width of Window Shadowing The vertical width of window shadow is determined by these VW[1:0] bits setting as follows : (Vertical Width = VW $\times$ 2 Lines)                                                                                                                                 |

|                                           | REND3 —<br>REND0<br>(Bit 3 — 0)                  | Window End Row Address : Range 0 — 15 It means the row address that window stops on. About actually stop point, refer to 'III-6.3 Window Generation'(27p).                                                                                                                                             |

| Frame Control                             | WIN_EN (Bit F)                                   | Window Enable Set this bit to activate window.                                                                                                                                                                                                                                                         |

| Registers-6,                              | Bit E — D                                        | Reserved.                                                                                                                                                                                                                                                                                              |

| 8, 10, 12<br>(Row15,<br>Column06, 08,     | CSTR4 —<br>CSTR0<br>(Bit C — 8)                  | Window Start Column Address : Range 0 — 29 It means the column address that window starts from. About actually start point, refer to 'III-6.3 Window Generation'(27p).                                                                                                                                 |

| 10, 12)                                   | WSHA (Bit 7)                                     | Window Shadowing Enable If this bit is set '1', activate the area of window shadow as width as HW and VW.                                                                                                                                                                                              |

|                                           | Bit 6 — 5                                        | Reserved.                                                                                                                                                                                                                                                                                              |

|                                           | CEND4 —<br>CEND0 (Bit 3<br>— 0)                  | Window End Column Address : Range 0 — 29 It means the column address that window stops on. About actually stop point, refer to 'III-6.3 Window Generation'(27p).                                                                                                                                       |

Table 7: Register Description (Continued)

\* That "Frame Control Register 5" pair with "Frame Control Register 6" control the function about window. As like above, that the odd register pair with the even register in "Frame Control Register 7 — 12" control about each "Window 1 — 3".

| Registers                                        | Bits                           | Description                                                                                                                                                                      |

|--------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frame Control                                    | Bit F — E                      | Reserved.                                                                                                                                                                        |

| Registers-13<br>(Row15,<br>Column13)             | WPR31,<br>WPR30<br>(Bit D — C) | Window Priority 3 Determine a window out of 4 windows that has the lowest priority. The selected window area may be overlapped by a area of the window that has higher priority. |

|                                                  | Bit B — A                      | Reserved.                                                                                                                                                                        |

|                                                  | WPR21,<br>WPR20<br>(Bit 9 — 8) | Window Priority 2 Determine a window out of 4 windows that has the 3rd priority.                                                                                                 |

|                                                  | Bit 7 — 6                      | Reserved.                                                                                                                                                                        |

|                                                  | WPR11,<br>WPR10<br>(Bit 5 — 4) | Window Priority 1 Determine a window out of 4 windows that has the 3rd priority.                                                                                                 |

|                                                  | Bit 3 — 2                      | Reserved.                                                                                                                                                                        |

|                                                  | WPR01,<br>WPR00<br>(Bit 1 — 0) | Window Priority 0 Determine a window out of 4 windows that has the highest priority. The selected window area overlaps lower priority windows.                                   |

| Frame Control<br>Registers-14 —<br>17<br>(Row15, | PWM7 —<br>PWM0<br>(Bit F — 8)  | PWM Port Control (Odd) Decides channel 2/ 4/ 6/ 8 PWM's output duty cycle and waveform.                                                                                          |

| (100010,<br>Column14—17)                         | PWM7 —                         | N/M Port Control (Even) Decides channel 1/3/5/7 N/M/s output duty avela                                                                                                          |

| Column 14—17)                                    | PWM7 —<br>PWM0                 | PWM Port Control (Even) Decides channel 1/ 3/ 5/ 7 PWM's output duty cycle and waveform.                                                                                         |

|                                                  | (Bit 7 — 0)                    |                                                                                                                                                                                  |

Table 7: Register Description (Continued)

\* If you determine window priorities with "Frame Control Register 13", each window overlaps lower priority windows. So you can make pop-up window OSD. Refer to 'Transparency (23p)'.

## ADDRESSING

### DISPLAY RAM

1 k-Byte SRAM (512  $\times$  16 bits) is built in S5D2509. Registers are distributed within 16 rows  $\times$  30 columns. But, for facilitating internal caculation, addressing is done using exponents of 2, and the S5D2509 is composed of 16 rows  $\times$  32 columns RAM Cell.

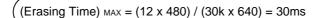

if 'Erase' Bit of "Frame Control Register 0" is enabled by setting '1' and erased RAM, 480 RAM cells are erased excepting only 16th row (Frame Control Registers). Therefore, the 'Erasing Time' is measured with 480 RAM cells as the standard.

\* Erasing Time

Erasing Time = RAM Clock x 480 (RAM Cell volume) RAM Clock = 12 dot clock Dot Clock = 1/ (dot frequency) Dot Frequency = Horizontal Frequency x Resolution (mode)

So, the maximum value of the 'Erasing Time' is as follows.

When you are programming with MCU, you have not to give the S5D2509 other operation or command during the (Erasing Time)MAX at a minimum, if you hope that timing violation isn't happened.

## **ROM FONTS**

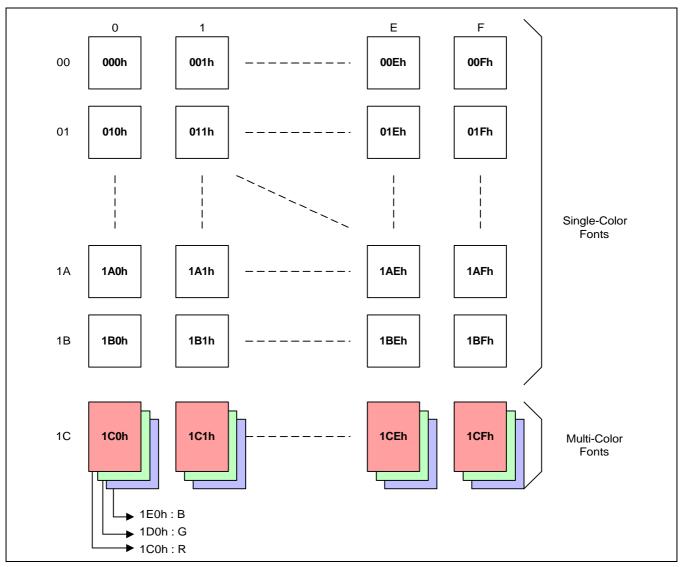

S5D2509 provides 464 ROM fonts for displaying OSD icons, which allows the use of multi-language OSD icons. Out of the 464 ROM fonts, 448 are standard fonts, and 16 are multi-color fonts. The standard font is placed at 000h address is reserved for blank data. Each multi-color font is composed of 4 color attribute ROM fonts are as shown "Figure III-4.2 : Composition of ROM Fonts".

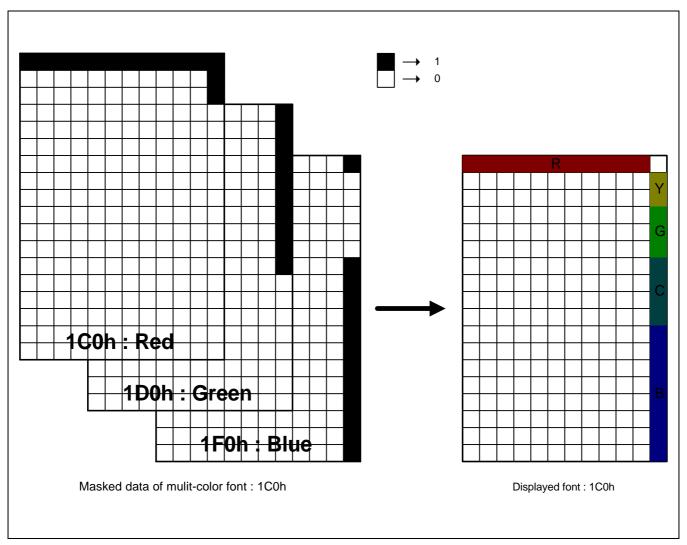

A multi-color font is made by 'OR operating with these 3 fonts. When you want to access this multi-color font, you may call the address of R-color attribute font. In example, the addresses of 1C0h, 1D0h and 1E0h mean respectively R, G, B color attribute fonts. and that the multi-color font is accessed by addressing 1C0h is made with 1C0h, 1D0h, and 1E0h through 'OR' operation.

To do addressing 464 ROM fonts, as explained at "Memory Map (12p)", the S5D2509 uses 9 bits added 1 extended bit which use the MSB of row/ column address and 8 bits for character code bits in "Character & Attribute Registers".

## Figure 11: Composition of ROM Fonts

## Notes for when making S5D2509 Fonts

Address 000h is appointed as blank data. RAM's initial values are all 0, and all bits are written as 0 when you erase the RAM, so blank data means the initial value. In other words, blank data means 'do nothing'. You don't need to write any data for the space font, except for 000h. It just needs to be an undotted area.

If you want to express a font image color the way you want according to the multi-color font characteristics, you must keep in mind that you are using a multi-color font when selecting the character or raster color. When you select a character or raster color, the color that was 'OR' operation to the original color is expressed. You should also consider the multi-color font's raster part. Since raster color is applied to '0' areas even with 'OR' operation, you can express many different background colors even with one multi-color font. The best thing to do is to set any part that you don't want to change color as the character part, and the changeable parts as the raster part when using a multi-color font.

# COLORING

If you have an intensity feature, the number of possible colors you can express becomes doubled. In other words, the number of colors you can represent with three colors blue, green, and red is 8 (=  $2^3$ ), but with the intensity feature, it is 16 (=  $2^4$ ).

## Character Color

Character Color is assigned for each font, and the 4 components for expressing a color are listed below.

| Blue      | CB bit [A] of "Character & Attribute Registers"                                                                                        |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------|

| Green     | CG bit [9] of "Character & Attribute Registers"                                                                                        |

| Red       | CR bit [8] of "Character & Attribute Registers"                                                                                        |

| Intensity | CINT bit of extended code set in "Frame Control Register 3" which is set by CTL1:CTL0 bits [F:E] in "Character & Attribute Registers". |

## **Raster Color**

| Blue      | RB bit [D] of "Character & Attribute Registers"                                                                                        |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------|

| Green     | RG bit [C] of "Character & Attribute Registers"                                                                                        |

| Red       | RR bit [B] of "Character & Attribute Registers"                                                                                        |

| Intensity | RINT bit of extended code set in "Frame Control Register 3" which is set by CTL1:CTL0 bits [F:E] in "Character & Attribute Registers". |

If the extended code is enabled by setting ExEN bit in "Frame Control Register 0" to '1', that the extended code is set in "Frame Control Register 3" is selected by [F:E] bits of "Character & Attribute Registers". So, you can select attribute with font unit by the various composition of Blink, Shadow, Raster Color Intensity, and Character Color Intensity. Otherwise, you can select just blink and shadow attributes with font base. Therefore, if you want to express 16 colors, you must enable ExEN bit and also set RINT and CINT bits of extended code set in "Frame Control Register 3" to '1'.

## **Multi-Color Font**

The multi-color fonts supported in S5D2509 is composed of 3 fonts (red, green, and blue) as the structure in "III-4.2 ROM Fonts" (21p) and can express 16 colors as single-color fonts is did 'OR' operation.