# PI7C7100 3-Port PCI Bridge

**Rev 1.1**

Pericom Semiconductor Corporation

### The Complete Interface Solution

2380 Bering Drive, San Jose, California 95131 Telephone: 1-877-PERICOM, (1-877-737-4266) Fax: (408) 435-1100, E-mail: nolimits@pericom.com

Internet: http://www.pericom.com

© 2000 Pericom Semiconductor Corporation

3-Port PCI Bridge

#### LIFESUPPORTPOLICY

Pericom Semiconductor Corporation's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of PSC.

- 1.Life support devices or systems are devices or systems which:

- a) are intended for surgical implant into the body or

- b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Pericom Semiconductor Corporation reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. Pericom Semiconductor does not assume any responsibility for use of any circuitry described other than the circuitry embodied in a Pericom Semiconductor product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Pericom Semiconductor Corporation.

ii

All other trademarks are of their respective companies.

### **Table of Contents**

| 1.          | DITC7100 Dlack Diagram                    |                                   |  |  |  |  |  |

|-------------|-------------------------------------------|-----------------------------------|--|--|--|--|--|

| 2.<br>3.    | PI7C7100 Block Diagram                    |                                   |  |  |  |  |  |

| <b>3.</b> 1 | Signal Types                              |                                   |  |  |  |  |  |

| 3.2         | Signals                                   |                                   |  |  |  |  |  |

| 3.2.1       | Primary Bus Interface Signals             |                                   |  |  |  |  |  |

| 3.2.2       | econdary Bus Interface Signals            |                                   |  |  |  |  |  |

| 3.2.3       | Clock Signals                             |                                   |  |  |  |  |  |

| 3.2.4       | Miscellaneous Signals                     | 8                                 |  |  |  |  |  |

| 3.2.5       | JTAG Boundary Scan Signals                | 9                                 |  |  |  |  |  |

| 3.2.6       | Power and Ground                          | 9                                 |  |  |  |  |  |

| 3.3         | PI7C7100 PBGA Pin Listing                 | 9                                 |  |  |  |  |  |

| 4.          | PCIBus Operation                          | 13                                |  |  |  |  |  |

| 4.1         | Types of Transactions                     | 13                                |  |  |  |  |  |

| 4.2         | Single Address Phase                      | 14                                |  |  |  |  |  |

| 4.3         | Device Select (DEVSEL#) Generation        | 14                                |  |  |  |  |  |

| 4.4         | Data Phase                                | 14                                |  |  |  |  |  |

| 4.5         | Write Transactions                        | 14                                |  |  |  |  |  |

| 4.5.1       | Posted Write Transactions                 | 14                                |  |  |  |  |  |

| 4.5.2       | Memory Write and Invalidate Transactions  | 15                                |  |  |  |  |  |

| 4.5.3       | Delayed Write Transactions                | 15                                |  |  |  |  |  |

| 4.5.4       | Write Transaction Address Boundaries      | 16                                |  |  |  |  |  |

| 4.5.5       | Buffering Multiple Write Transactions     | 16                                |  |  |  |  |  |

| 4.5.6       | Fast Back-to-Back Write Transactions      | 16                                |  |  |  |  |  |

| 4.6         | ead Transactions                          |                                   |  |  |  |  |  |

| 4.6.1       | Prefetchable Read Transactions            |                                   |  |  |  |  |  |

| 4.6.2       | Non-prefetchable Read Transactions        |                                   |  |  |  |  |  |

| 4.6.3       | Read Pre-fetch Address Boundaries         | Read Pre-fetch Address Boundaries |  |  |  |  |  |

| 4.6.4       | Delayed Read Requests                     | 18                                |  |  |  |  |  |

| 4.6.5       | Delayed Read Completion with Target       | 18                                |  |  |  |  |  |

| 4.6.6       | Delayed Read Completion on Initiator Bus  |                                   |  |  |  |  |  |

| 4.7         | Configuration Transactions                | 19                                |  |  |  |  |  |

| 4.7.1       | Type 0 Access to PI7C7100                 | 19                                |  |  |  |  |  |

| 4.7.2       | Type 1 to Type 0 Conversion               | 20                                |  |  |  |  |  |

| 4.7.3       | Type 1 to Type 1 Forwarding               | 21                                |  |  |  |  |  |

| 4.7.4       | Special Cycles                            | 22                                |  |  |  |  |  |

| 4.8         | Transaction Termination                   | 22                                |  |  |  |  |  |

| 4.8.1       | Master Termination Initiated by PI7C7100  | 23                                |  |  |  |  |  |

| 4.8.2       | Master Abort Received by PI7C7100         |                                   |  |  |  |  |  |

| 4.8.3       | Target Termination Received by PI7C7100   | 24                                |  |  |  |  |  |

| 4.8.3.1     | Delayed Write Target Termination Response | 24                                |  |  |  |  |  |

| 4.8.3.2     | Posted Write Target Termination Response  | 24                                |  |  |  |  |  |

| 4.8.3.3     | Delayed Read Target Termination Response  | 25                                |  |  |  |  |  |

| 4.8.4       | Target Termination Initiated by PI7C7100  |                                   |  |  |  |  |  |

| 4.8.4.1     | Target Retry                              | 26                                |  |  |  |  |  |

| 4.8.4.2     | Target Disconnect                         | 27                                |  |  |  |  |  |

| 4.8.4.3        | Target Abort                                                                                              | 2  |

|----------------|-----------------------------------------------------------------------------------------------------------|----|

| 4.9            | Concurrent Mode Operation                                                                                 | 2  |

| 5.             | Address Decoding                                                                                          |    |

| 5.1            | Address Ranges                                                                                            |    |

| 5.2            | I/O Address Decoding                                                                                      |    |

| -              | <u>c</u>                                                                                                  |    |

| 5.2.1          | I/O Base and Limit Address Registers                                                                      |    |

| 5.2.2          | ISA Mode                                                                                                  |    |

| 5.3            | Memory Address Decoding                                                                                   |    |

| 5.3.1          | Memory-Mapped I/O Base and Limit Address Registers                                                        | 30 |

| 5.3.2          | Prefetchable Memory Base and Limit Address Registers                                                      | 30 |

| 5.4            | VGA Support                                                                                               | 3  |

| 5.4.1          | VGA Mode                                                                                                  | 3  |

| 5.4.2          | VGA Snoop Mode                                                                                            | 3  |

| 6.             | Transaction Ordering                                                                                      |    |

| 6.1            | Transactions Governed by Ordering Rules                                                                   |    |

| 6.2            | General Ordering Guidelines                                                                               |    |

| 6.3            | Ordering Rules                                                                                            |    |

| 6.4            | Data Synchronization                                                                                      |    |

| 7.             | Error Handling                                                                                            |    |

| 7.1            | Address Parity Errors                                                                                     |    |

| 7.2            | Data Parity Errors                                                                                        | 3. |

| 7.2.1          | Configuration Write Transactions to Configuration Space                                                   | 3. |

| 7.2.2          | Read Transactions                                                                                         | 30 |

| 7.2.3          | Delayed Write Transactions                                                                                | 30 |

| 7.2.4          | Posted Write Transactions                                                                                 |    |

| 7.3            | Data Parity Error Reporting Summary                                                                       |    |

| 7.4            | System Error (SERR#) Reporting                                                                            |    |

| 8.             | Exclusive Access                                                                                          |    |

| 8.1            | Concurrent Locks                                                                                          |    |

| 8.2            | Acquiring Exclusive Access across PI7C7100                                                                |    |

| 8.3            | Ending Exclusive Access                                                                                   |    |

| 9.             | PCIBus Arbitration                                                                                        |    |

| 9.1            | Primary PCI Bus Arbitration                                                                               |    |

| 9.2            | Secondary PCI Bus Arbitration                                                                             |    |

| 9.2.1<br>9.2.2 | Secondary Bus Arbitration Using the Internal Arbiter  Secondary Bus Arbitration Using an External Arbiter |    |

| 9.2.2          | Bus Parking                                                                                               |    |

| 10.            | Clocks                                                                                                    |    |

| 10.1           | Primary Clock Inputs                                                                                      |    |

| 10.2           | Secondary Clock Outputs                                                                                   |    |

| 11.            | Reset                                                                                                     |    |

| 11.1           | Primary Interface Reset                                                                                   |    |

| 11.2           | Secondary Interface Reset                                                                                 |    |

| 11.3           | Chip Reset                                                                                                |    |

| 12.            | Supported Commands                                                                                        |    |

| 12.1           | Primary Interface                                                                                         | 52 |

| 12.2           | Secondary Interface                                                                                       |    |

| 13.            | Configuration Registers                                                                                   | 5. |

| 13.1    | Config Register 1                                                                                    | 55 |

|---------|------------------------------------------------------------------------------------------------------|----|

| 13.2    | Config Register 2                                                                                    | 56 |

| 13.2.1  | Config Register 1 or 2: Vendor ID Register (read only, bit 15-0; offset 00h)                         | 57 |

| 13.2.2  | Config Register 1: Device ID Register (read only, bit 31-16; offset 00h)                             | 57 |

| 13.2.3  | Config Register 2: Device ID Register (read only, bit 31-16; offset 00h)                             |    |

| 13.2.4  | Config Register 1: Command Register (bit 15-0; offset 04h)                                           |    |

| 13.2.5  | Config Register 2: Command Register (bit 15-0; offset 04h)                                           |    |

| 13.2.6  | Config Register 1 or 2: Status Register (for primary bus, bit 31-16; offset 04h)                     |    |

| 13.2.7  | Config Register 1 or 2: Revision ID Register (read only, bit 7-0; offset 08h)                        |    |

| 13.2.8  | Config Register 1 or 2: Class Code Register (read only, bit 31-8; offset 08h)                        |    |

| 13.2.9  | Config Register 1 or 2: Cache Line Size Register (read/write, bit 7-0; offset 0Ch)                   |    |

|         | Config Register 1: Primary Latency Timer Register (read/write, bit 15-8; offset 0Ch)                 |    |

| 13.2.11 | Config Register 2: Primary Latency Timer Register (read/write, bit 15-8; offset 0Ch)                 | 60 |

|         | Config Register 1: Header Type Register (read only, bit 23-16; offset 0Ch)                           |    |

|         | Config Register 2: Header Type Register (read only, bit 23-16; offset 0Ch)                           |    |

|         | Config Register 1: Primary Bus Number Register (read/write, bit 7-0; offset 18h)                     |    |

|         | Config Register 2: Primary Bus Number Register (read/write, bit 7-0; offset 18h)                     |    |

| 13.2.16 | Config Register 1 or 2: Secondary Bus Number Register (read/write, bit 15-8; offset 18h)             | 60 |

|         | Config Register 1 or 2: Subordinate Bus Number Register (read/write, bit 23-16; offset 18h)          |    |

|         | Config Register 1 or 2: Secondary Latency Timer (read/write, bit 31-24; offset 18h)                  |    |

|         | Config Register 1 or 2: I/O Base Register (read/write, bit 7-0; offset 1Ch)                          |    |

|         | Config Register 1 or 2: I/O Limit Register (read/write, bit 15-8; offset 1Ch)                        |    |

|         | Config Register 1 or 2: Secondary Status Register (bit 31-16; offset 1Ch)                            |    |

|         | Config Register 1 or 2: Memory Base Register (read/write, bit 15-0; offset 20h)                      |    |

|         | Config Register 1 or 2: Memory Limit Register (read/write, bit 31:16; offset 20h)                    |    |

|         | Config Register 1 or 2: Prefetchable Memory Base Register (read/write, bit 15-0;offset 24h)          |    |

|         | Config Register 1 or 2: Prefetchable Memory Limit Register (read/write, bit 31-16; offset 24h)       |    |

|         | Config Register 1 or 2: I/O Base Address Upper 16 Bits Register (read/write, bit 15-0; offset 30h)   |    |

|         | Config Register 1 or 2: I/O Limit Address Upper 16 Bits Register (read/write, bit 31-16; offset 30h) |    |

|         | Config Register 1 or 2: Subsystem Vendor ID (read/write, bit 15-0; offset 34h)                       |    |

|         | Config Register 1 or 2: Subsystem ID (read/write, bit 31-16; offset 34h)                             |    |

|         | Config Register 1 or 2: Interrupt Pin Register (read only, bit 15-8; offset 3Ch)                     |    |

|         | Config Register 1 or 2: Bridge Control Register (bit 31-16; offset 3Ch)                              |    |

|         | Config Register 1 or 2: Diagnostic/Chip Control Register (bit 15-0; offset 40h)                      |    |

|         | Config Register 1 or 2: Arbiter Control Register (bit 31-16; offset 40h)                             |    |

|         | Config Register 1: Primary Prefetchable Memory Base Register (Read/Write, bit 15-0; offset 44h)      |    |

|         | Config Register 2: Primary Prefetchable Memory Base Register (Read/Write, bit 15-0; offset 44h)      |    |

|         | Config Register 1: Primary Prefetchable Memory Limit Register (Read/Write, bit 31-16; offset 44h)    |    |

|         | Config Register 2: Primary Prefetchable Memory Limit Register (Read/Write, bit 31-16; offset 44h)    |    |

| 13.2.38 | Config Register 1 or 2: P_SERR# Event Disable Register (bit 7-0; offset 64h)                         | 65 |

| 13.2.39 | Config Register 1: Secondary Clock Control Register (bit 15-0; offset 68h)                           | 66 |

| 13.2.40 | Config Register 2: Secondary Clock Control Register (bit 15-0; offset 68h)                           | 66 |

| 13.2.41 | Config Register 1 or 2: Non-Posted Memory Base Register (read/write, bit 15-0; offset 70h)           | 67 |

| 13.2.42 | Config Register 1 or 2: Non-Posted Memory Limit Register (read/write, bit 31-16; offset 70h)         | 67 |

| 13.2.43 | Config Register 1: Port Option Register (bit 15-0; offset 74h)                                       | 67 |

|         | Config Register 2: Port Option Register (bit 15-0; offset 74h)                                       |    |

| 13.2.45 | Config Register 1 or 2: Master Timeout Counter Register (read/write, bit 31-16; offset 74h)          | 69 |

|         | Config Register 1 or 2: Retry Counter Register (read/write, bit 31-0; offset 78h)                    |    |

| 13.2.47 | Config Register 1 or 2: Sampling Timer Register (read/write, bit 31-0; offset 7Ch)                   | 69 |

| 13 2 48 | Config Register 1 or 2: Successful I/O Read Count Register (read/write bit 31-0; offset 80h)         | 69 |

| 13.2.49 | Config Register 1 or 2: Successful I/O Write Count Register (read/write, bit 31-0; offset 84h)       | 69 |

|---------|------------------------------------------------------------------------------------------------------|----|

| 13.2.50 | Config Register 1 or 2: Successful Memory Read Count Register (read/write, bit 31-0; offset 88h)     | 69 |

| 13.2.51 | Config Register 1 or 2: Successful Memory Write Count Register (read/write, bit 31-0; offset 8Ch)    | 69 |

|         | Config Register 1: Primary Successful I/O Read Count Register (read/write, bit 31-0; offset 90h)     |    |

|         | Config Register 1: Primary Successful I/O Write Count Register (read/write, bit 31-0; offset 94h)    |    |

|         | Config Register 1: Primary Successful Memory Read Count Register (read/write, bit 31-0; offset 98h)  |    |

|         | Config Register 1: Primary Successful Memory Write Count Register (read/write, bit 31-0; offset 9Ch) |    |

| 14.     | Bridge Behavior                                                                                      |    |

| 14.1    | Bridge Actions for Various Cycle Types                                                               |    |

| 14.2    | Transaction Ordering                                                                                 |    |

| 14.3    | Abnormal Termination (Initiated by Bridge Master)                                                    |    |

| 14.3.1  | Master Abort                                                                                         |    |

| 14.3.2  | Parity and Error Reporting                                                                           |    |

| 14.3.3  | Reporting Parity Errors                                                                              |    |

| 14.3.4  | Secondary IDSEL mapping                                                                              |    |

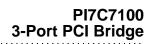

| 15.     | IEEE 1149.1 Compatible JTAG Controller                                                               |    |

| 15.1    | Boundary Scan Architecture                                                                           |    |

| 15.1.1  | TAP Pins                                                                                             |    |

| 15.1.2  | Instruction Register                                                                                 |    |

| 15.2    | Boundary Scan Instruction Set                                                                        |    |

| 15.3    | TAP Test Data Registers                                                                              |    |

| 15.4    | Bypass Register                                                                                      |    |

| 15.5    | Boundary-Scan Register                                                                               |    |

| 15.6    | TAPController                                                                                        |    |

| 16.     | Electrical and Timing Specifications                                                                 |    |

| 16.1    | Maximum Ratings                                                                                      | 79 |

| 16.2    | 3.3V DC Specifications                                                                               | 79 |

| 16.3    | 3.3V AC Specifications                                                                               | 80 |

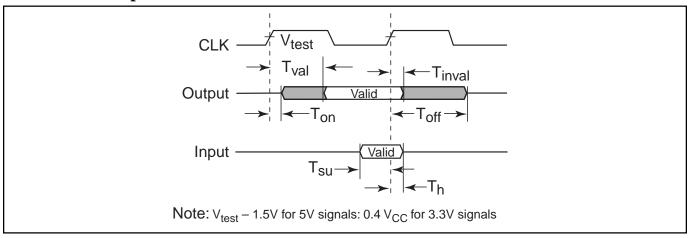

| 16.4    | Primary and Secondary buses at 33 MHz clock timing                                                   | 80 |

| 16.5    | Power Consumption                                                                                    | 80 |

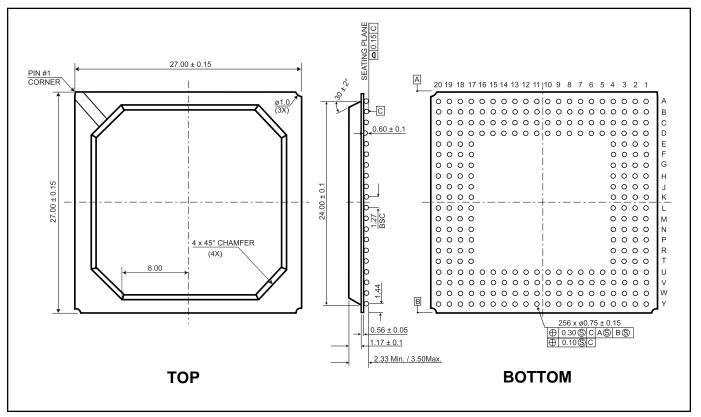

| 17.     | 256-Pin PBGA Package                                                                                 | 81 |

| 171     | Part Number Ordering Information                                                                     | Ω1 |

## **List of Figures**

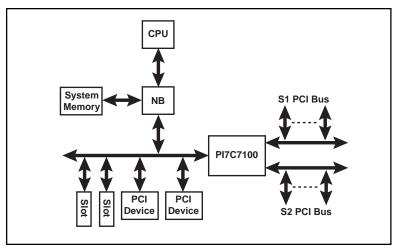

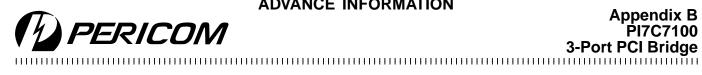

| 1-1.  | PI7C7100 on the System Board                              | 2  |

|-------|-----------------------------------------------------------|----|

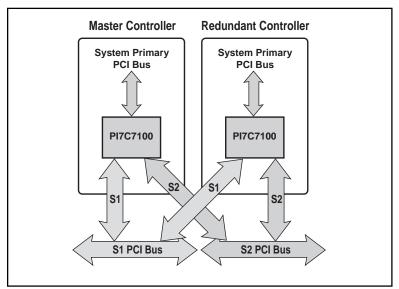

| 1-2.  | PI7C7100 in Redundant Applications                        | 2  |

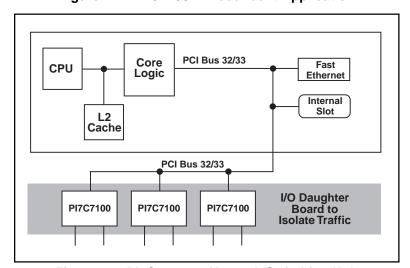

| 1-3.  | PI7C7100 on Network Switching Hub                         | 2  |

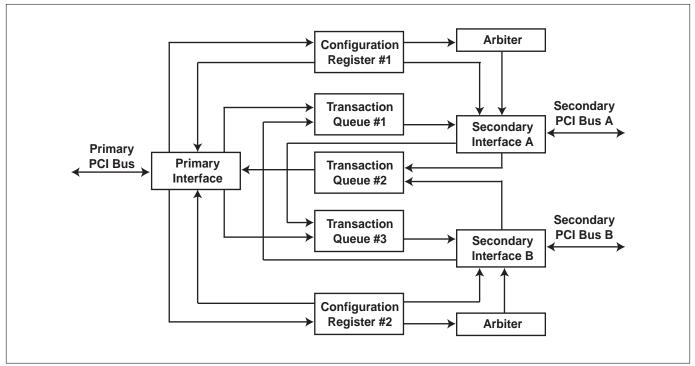

| 2-1.  | PI7C7100Block Diagram                                     | 3  |

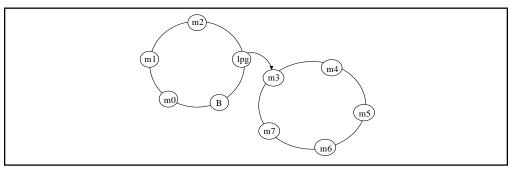

| 9-1.  | Secondary Arbiter Example                                 | 48 |

| 15-1. | Test Access Port Block Diagram                            | 72 |

| 16-1. | PCI Signal Timing Measurement Conditions                  | 80 |

| 17-1. | 256-Pin PBGA Package Drawing                              | 81 |

|       |                                                           |    |

|       | List of Tables                                            |    |

| 4-1.  | PCI Transaction                                           | 13 |

| 4-2.  | Write Transaction Forwarding                              | 14 |

| 4-3.  | Write Transaction Disconnect Address Boundaries           | 16 |

| 4-4.  | Read Pre-fetch Address Boundaries                         | 17 |

| 4-5.  | Read Transaction Pre-fetching                             | 18 |

| 4-6.  | Device Number to IDSEL S1_AD or S2_AD Pin Mapping         | 21 |

| 4-7.  | Delayed Write Target Termination Response                 | 24 |

| 4-8.  | Responses to Posted Write Target Termination              | 25 |

| 4-9.  | Responses to Delayed Read Target Termination              | 25 |

| 6-1.  | Summary of Tranaction Ordering                            |    |

| 7-1.  | Setting the Primary Interface Detected Parity Error Bit   | 39 |

| 7-2.  | Setting the Secondary Interface Detected Parity Error Bit |    |

| 7-3.  | Setting the Primary Interface Data Parity Detected Bit    | 40 |

| 7-4.  | Setting the Secondary InterfaceData Parity Detected Bit   | 41 |

| 7-5.  | Assertion of P_PERR#                                      | 42 |

| 7-6.  | Assertion of S_PERR#                                      |    |

| 7-7.  | Assertion of P_SERR# for Data Parity Errors               | 44 |

| 15-1. | TAP Pins                                                  | 73 |

| 15-2. | JTAG Boundary Register Order                              | 75 |

### **Appendix A - Timing Diagrams**

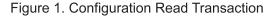

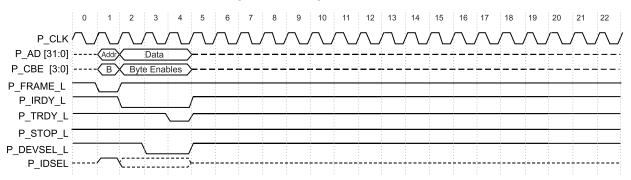

| 1.  | Configuration Read Transaction                                                        | A-3  |

|-----|---------------------------------------------------------------------------------------|------|

| 2.  | Configuration Write Transaction                                                       | A-3  |

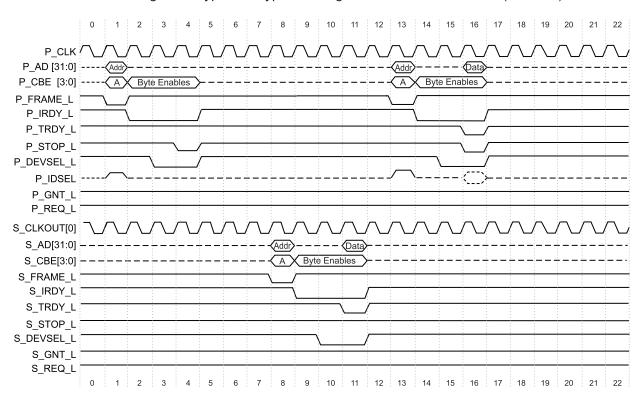

| 3.  | Type 1 to Type 0 Configuration Read Transaction (P→S)                                 | A-3  |

| 4.  | Type 1 to Type 0 Configuration Write Transaction (P →S)                               | A-4  |

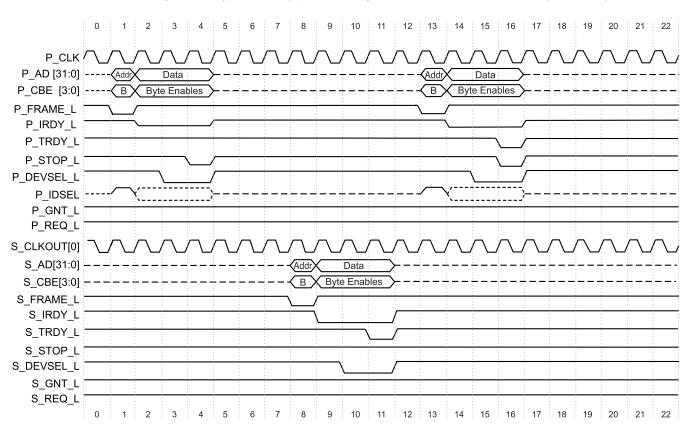

| 5.  | Upstream Type 1 to Special Cycle Transaction (S →P)                                   | A-4  |

| 6.  | Downstream Type 1 to Special Cycle Transaction (P →S)                                 | A-5  |

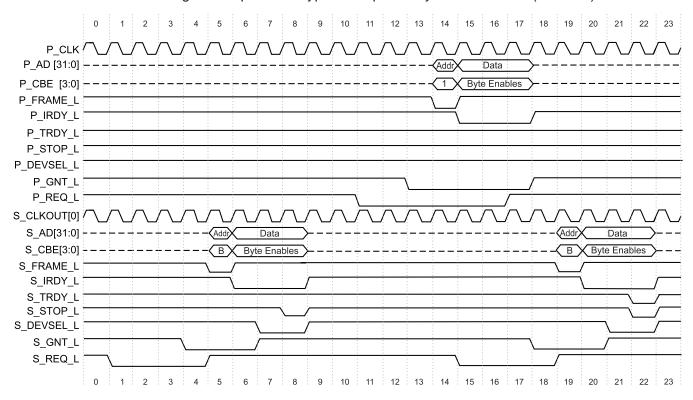

| 7.  | Downstream Type 1 to Type 1 Configuration Read Transaction (P →S)                     | A-5  |

| 8.  | Downstream Type 1 to Type 1 Configuration Write Transaction (P →S)                    |      |

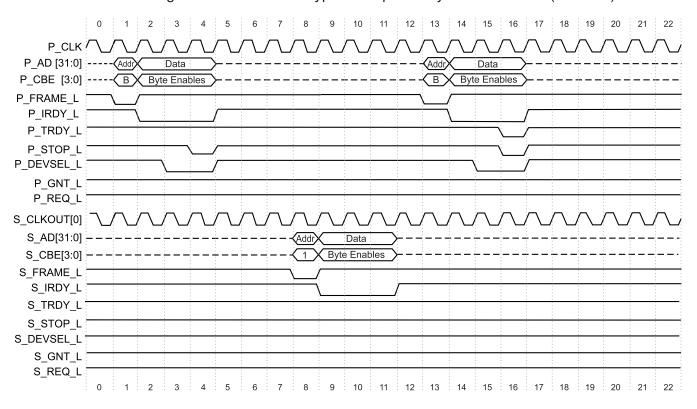

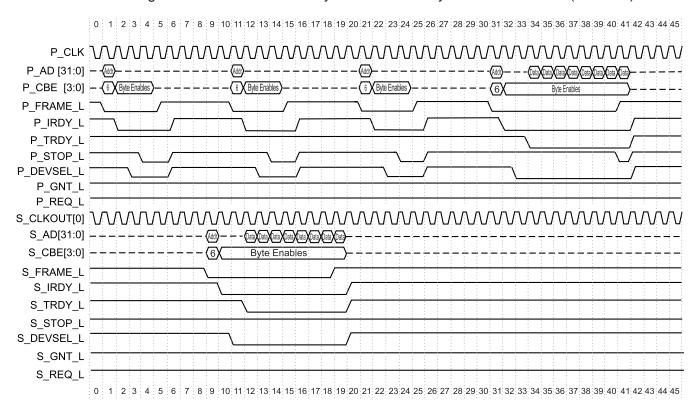

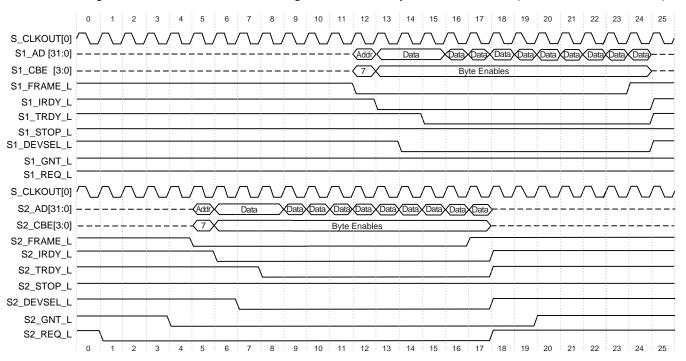

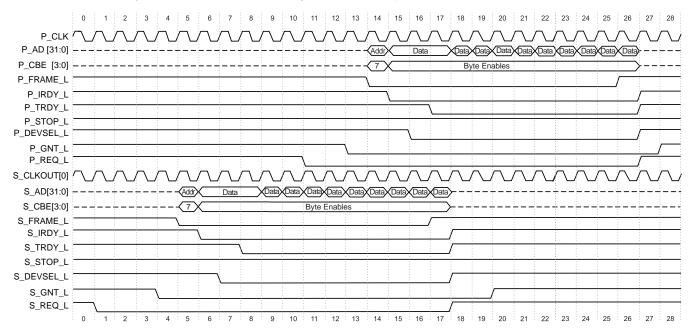

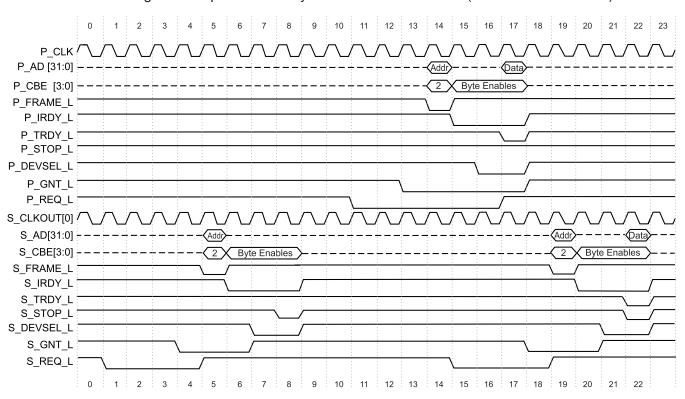

| 9.  | Upstream Delayed Burst Memory Read Transaction (S →P)                                 | A-6  |

| 10. | Downstream Delayed Burst Memory Read Transaction (P→S)                                | A-7  |

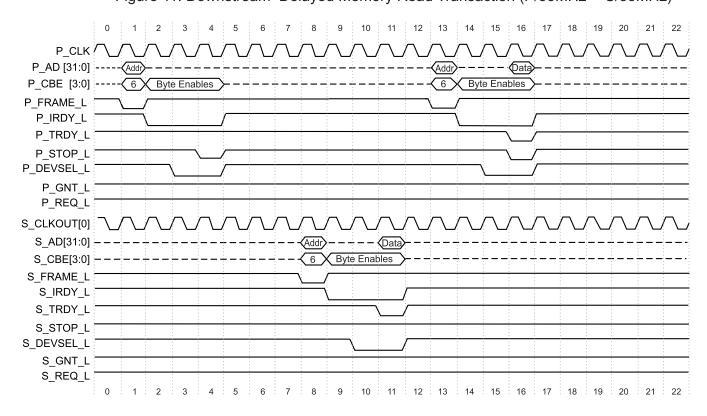

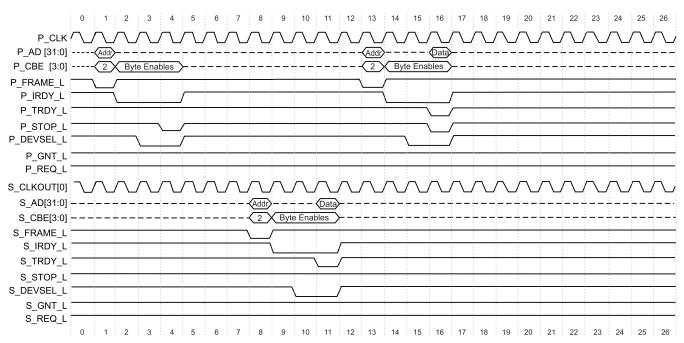

| 11. | Downstream Delayed Memory Read Transaction (P/33MHz →S/33MHz)                         | A-7  |

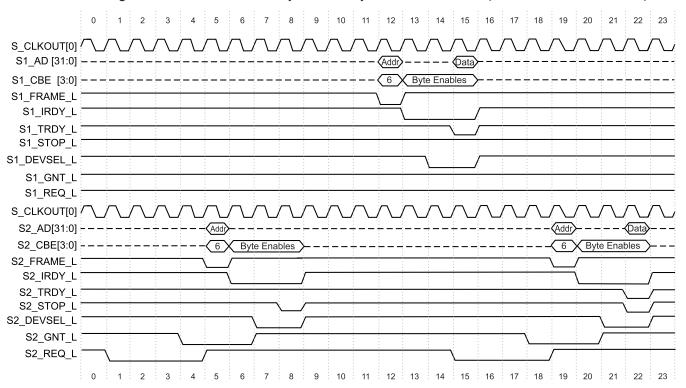

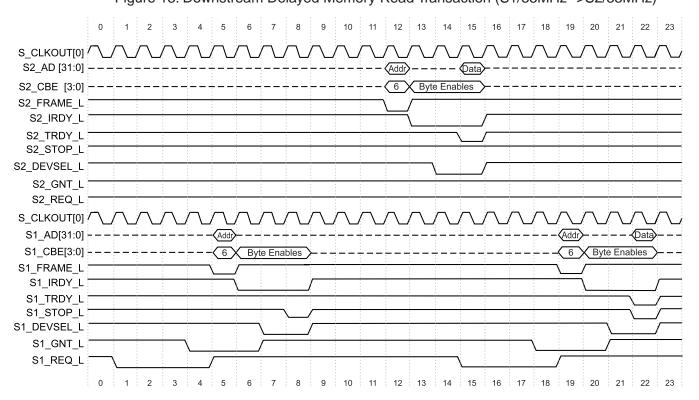

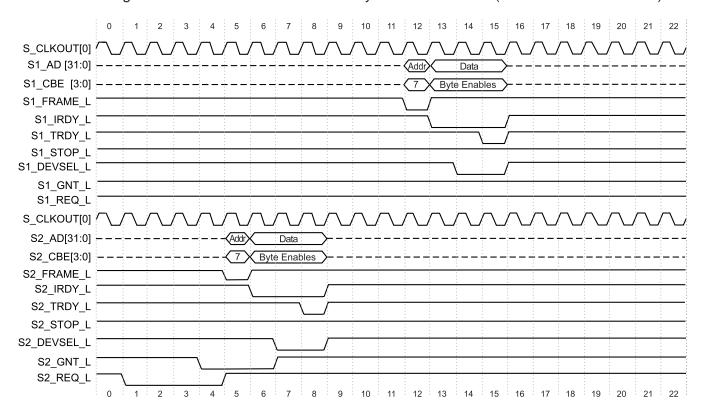

| 12. | Downstream Delayed Memory Read Transaction (S2/33MHz →S1/33MHz)                       | A-8  |

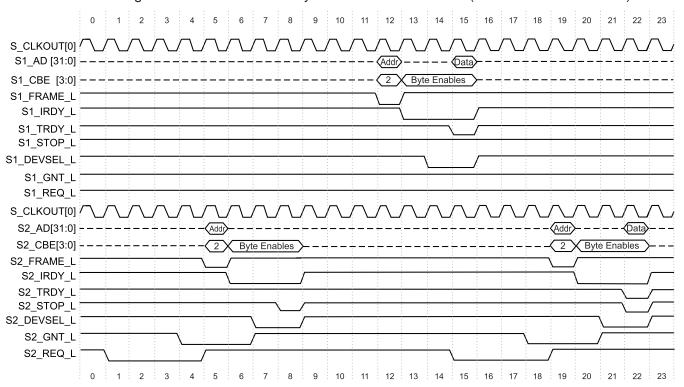

| 13. | Downstream Delayed Memory Read Transaction (S1/33MHz →S2/33MHz)                       | A-8  |

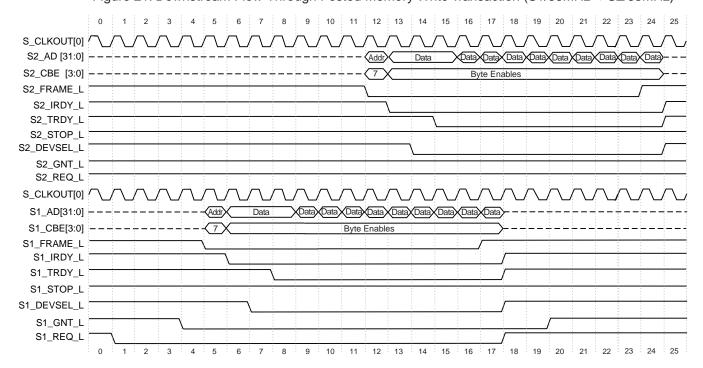

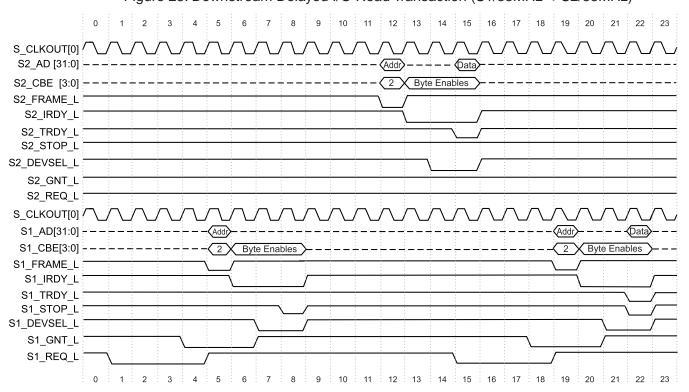

| 14. | Upstream Delayed Memory Read Transaction (S/33MHz →P/33MHz)                           | A-9  |

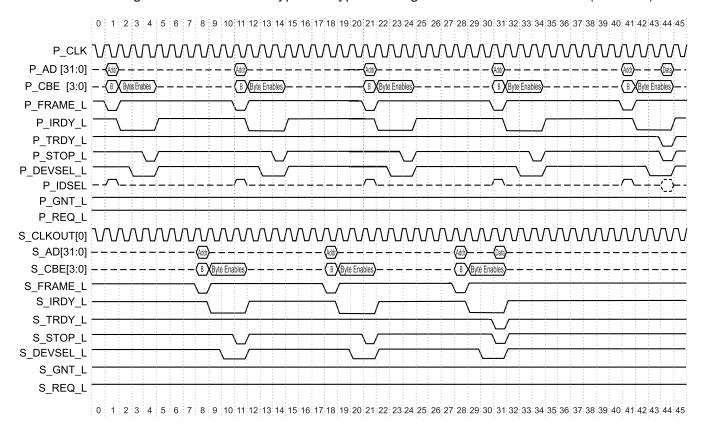

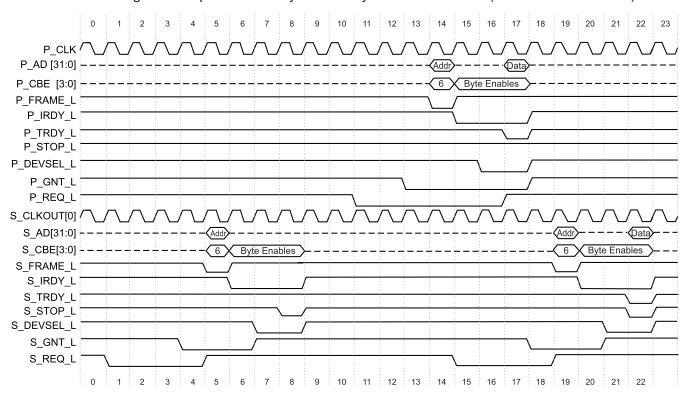

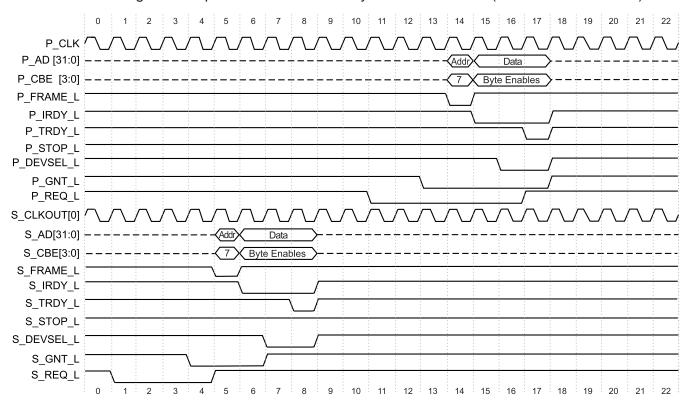

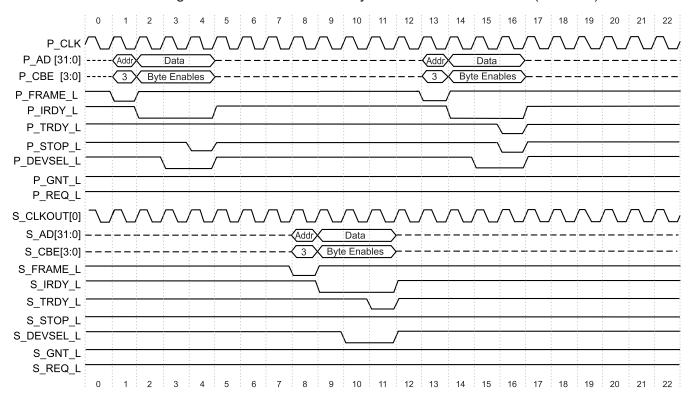

| 15. | Downstream Posted Memory Write Transaction (P/33MHz – S/33MHz)                        | A-9  |

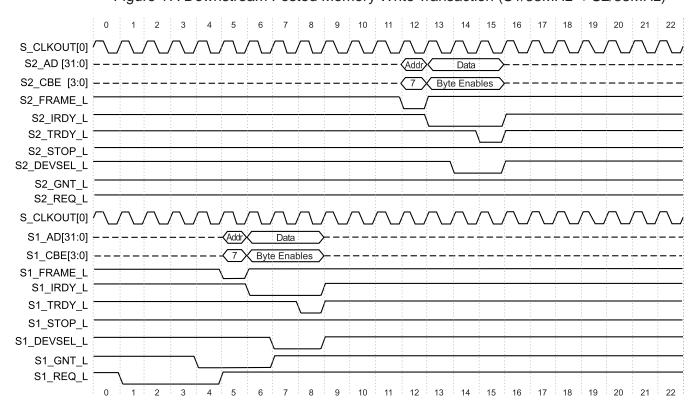

| 16. | Downstream Posted Memory Write Transaction (S2/33MHz →S1/33MHz)                       | A-10 |

| 17. | Downstream Posted Memory Write Transaction (S1/33MHz →S2/33MHz)                       | A-10 |

| 18. | Upstream Posted Memory Write Transaction (S/33MHz →P/33MHz)                           | A-11 |

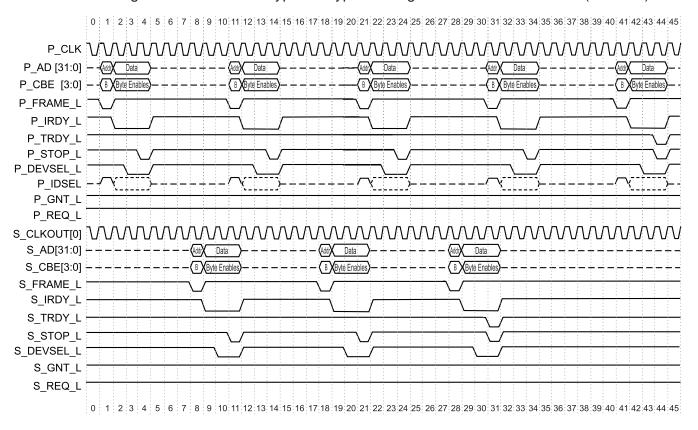

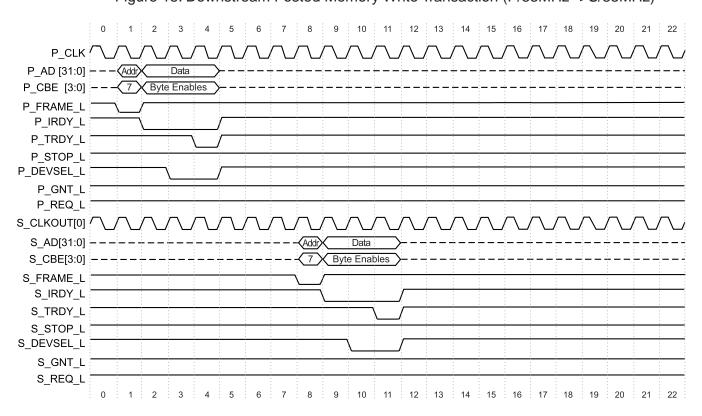

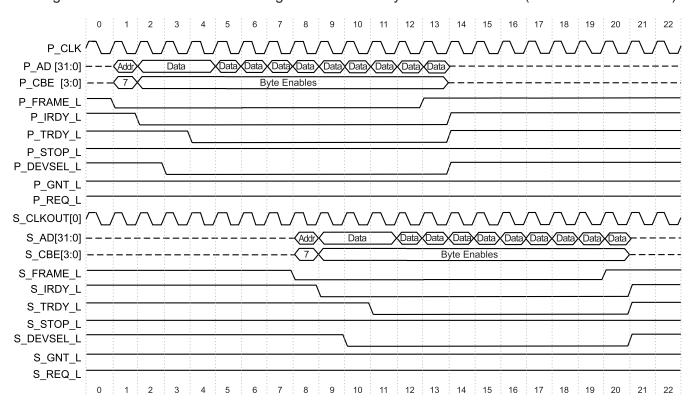

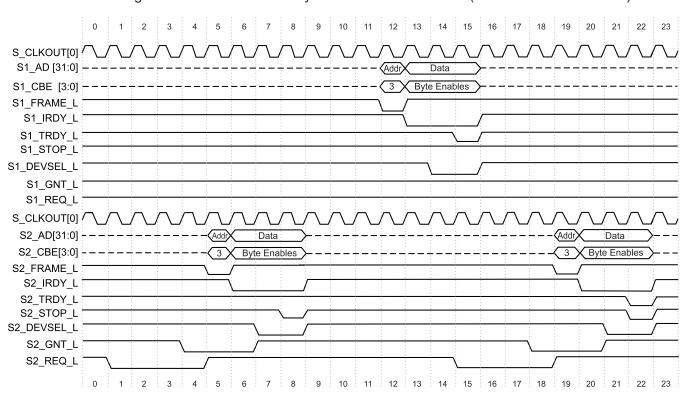

| 19. | Downstream Flow-Through Posted Memory Write Transaction (P/33MHz – \$\scrib{S}/33MHz) | A-11 |

| 20. | Downstream Flow-Through Posted Memory Write Transaction (S2/33MHz –\$1/33MHz)         | A-12 |

| 21. | Downstream Flow-Through Posted Memory Write Transaction (S1/33MHz – \$2/33MHz)        | A-12 |

| 22. | Upstream Flow-Through Posted Memory Write Transaction (S/33MHz –P/33MHz)              | A-13 |

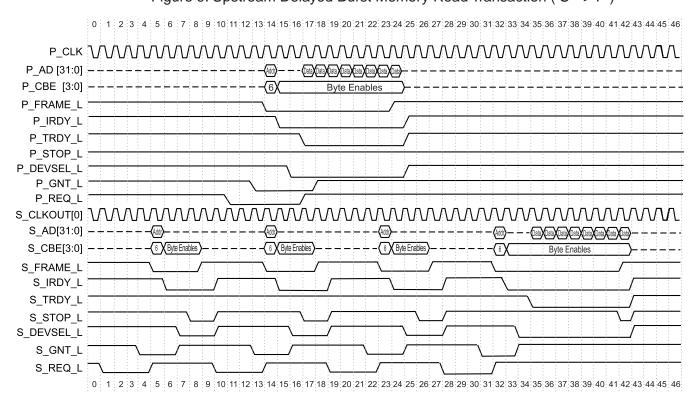

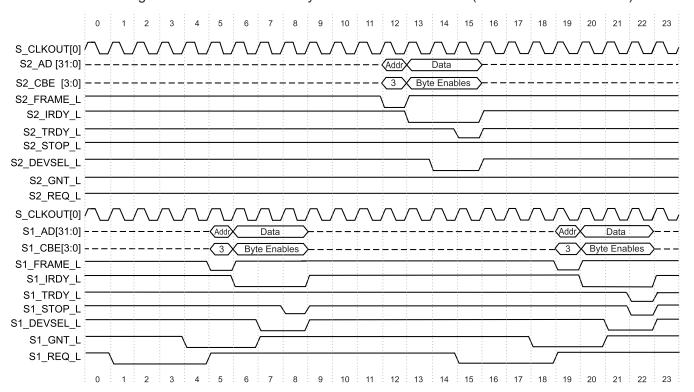

| 23. | Downstream Delayed I/O Read Transaction (P →S)                                        | A-13 |

| 24. | Downstream Delayed I/O Read Transaction (S2/33MHz — \$1/33MHz)                        | A-14 |

| 25. | Downstream Delayed I/O Read Transaction (S1/33MHz – \$2/33MHz)                        | A-14 |

| 26. | Downstream Delayed I/O Read Transaction (S/33MHz — P/33MHz)                           | A-15 |

| 27. | Downstream Delayed I/O Write Transaction (P →S)                                       | A-15 |

| 28. | Downstream Delayed I/O Write Transaction (S2/33MHz →S1/33MHz)                         | A-16 |

|     | Downstream Delayed I/O Write Transaction (S1/33MHz —S2/33MHz)                         |      |

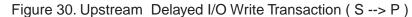

| 30. | Upstream Delayed I/O Write Transaction (S →P)                                         | A-17 |

|     | Appendix B - Evaluation Board User's Manual                                           |      |

| Ge  | eneral Information                                                                    | R-3  |

|     | equently Asked Questions                                                              |      |

|     | risked Questions                                                                      |      |

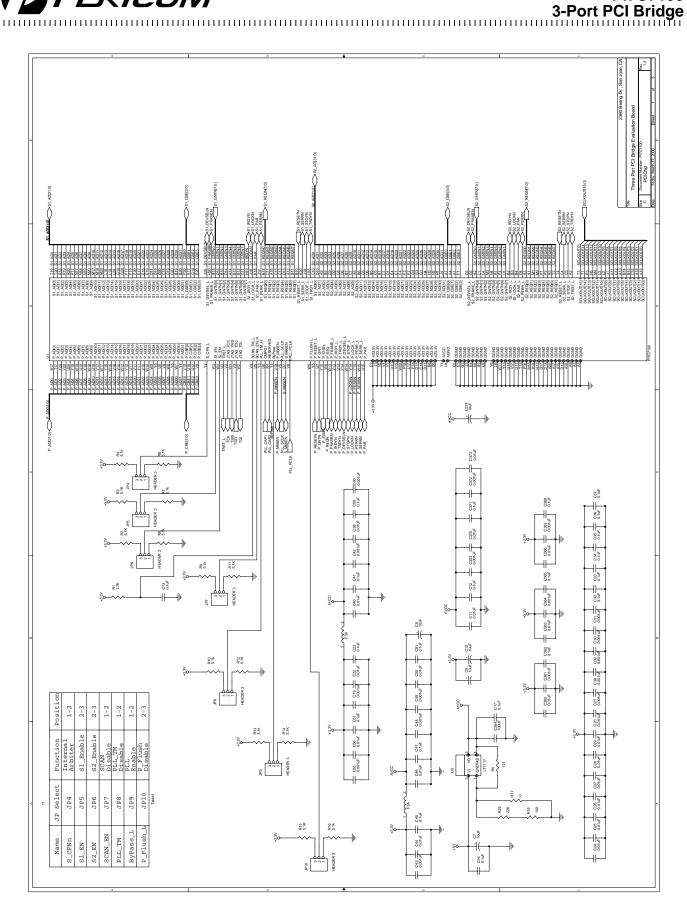

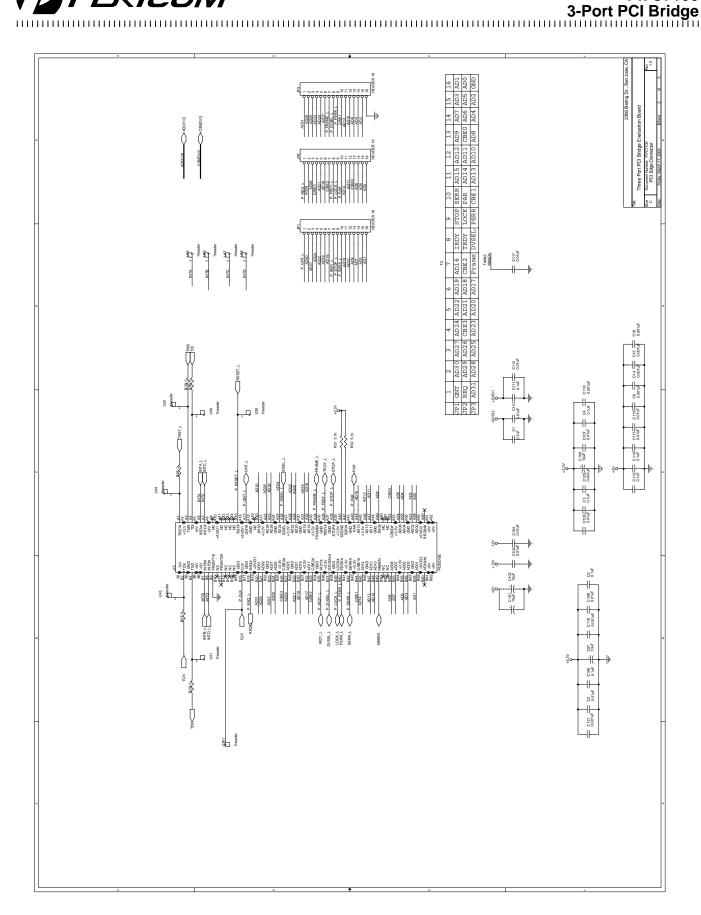

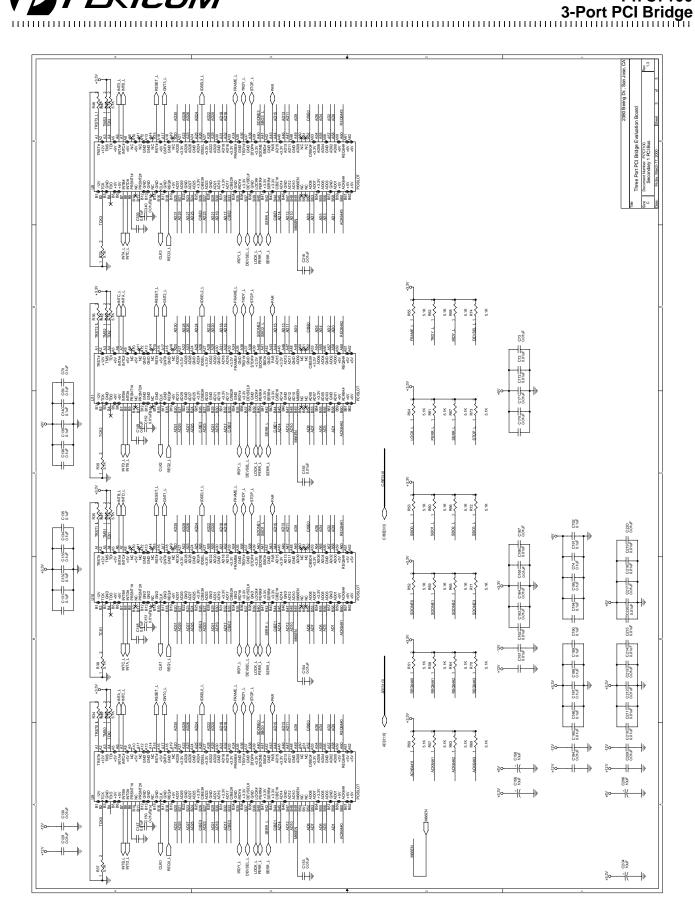

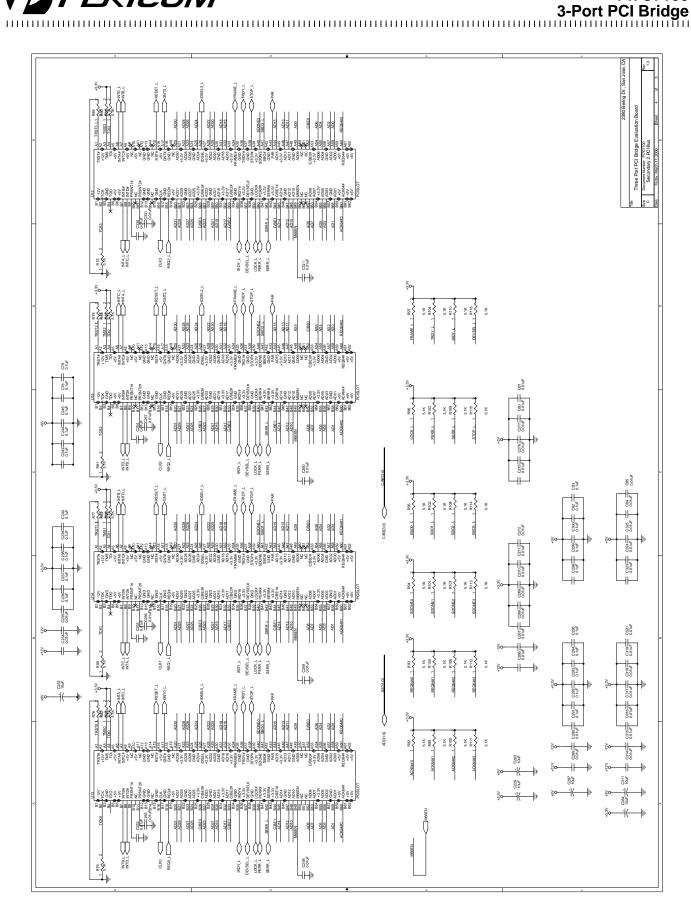

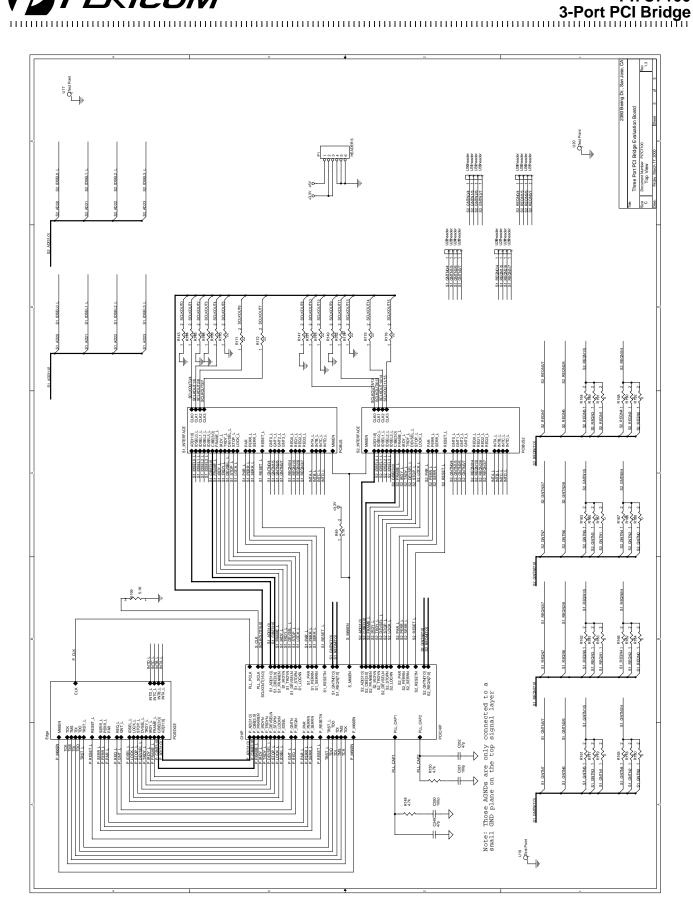

|     | Appendix C - Three-Port PCI Bridge Evaluation Board Schemat                           | tics |

| PC  | TChip                                                                                 | C-3  |

|     | I Edge Connector                                                                      |      |

| Sec | condary 1 PCI Bus                                                                     | C-5  |

| Sec | condary 2 PCI Bus                                                                     | C-6  |

| Top | p View                                                                                | C-7  |

### 1. Introduction

### **Product Description**

PI7C7100 is the first triple port PCI-to-PCI Bridge device designed to be fully compliant with the 32-bit, 33 MHz implementation of the *PCI Local Bus Specification, Revision 2.1*. PI7C7100 supports only synchronous bus transactions between devices on the primary 33 MHz bus and the secondary buses operating at 33 MHz. The primary and the secondary buses can also operate in concurrent mode, resulting in added increase in system performance. Concurrent bus operation off-loads and isolates unnecessary traffic from the primary bus; thereby enabling a master and a target device on the same secondary PCI bus to communicate even while the primary bus is busy.

### **Product Features**

- 32-bit Primary & two Secondary Ports run up to 33 MHz

- All three ports compliant with the PCI Local Bus Specification, Revision 2.1

- Compliant with PCI-to-PCI Bridge Architecture Specification, Revision 1.0.

- All I/O and memory commands

- Type 1 to Type 0 configuration conversion

- Type 1 to Type 1 configuration forwarding

- Type 1 configuration-write to special cycle conversion

- Concurrent primary to secondary bus operation and independent intra-secondary port channel to reduce traffic on the primary port

- · Provides internal arbitration for two sets of eight secondary bus masters

- Programmable 2-level priority arbiter

- Disable control for use of external arbiter

- · Supports posted write buffers on all directions

- Three 128 byte FIFOs for delay transactions

- Three 128 byte FIFOs for posted memory transactions

- · Enhanced address decoding

- 32-bit I/O address range

- 32-bit memory-mapped I/O address range

- VGA addressing and VGA palette snooping

- ISA-aware mode for legacy support in the first 64KB of I/O address range

- Interrupt Handling

- PCI interrupts are routed through an external interrupt concentrator

1

- · Supports system transaction ordering rules

- · Hot-plug support on secondary buses

- 3-State control of output buffers

- IEEE 1149.1 JTAG interface support

- 3.3V core; 3.3V PCI I/O interface with 5V I/O Tolerant

- · 256-pin plastic BGA package

Figure 1-1. PI7C7100 on the System Board

Figure 1-2. PI7C7100 in Redundant Application

Figure 1-3. PI7C7100 on Network Switching Hub

2

# 2. PI7C7100 Block Diagram

Figure 2-1. PI7C7100 Block Diagram

3

# 3. Signal Definitions

### 3.1 Signal Types

| Signal Type | Description                                                                                                                                                                  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PI          | PCI Input (3.3V, 5V tolerant)                                                                                                                                                |

| PIU         | PCI Input (3.3V, 5V tolerant) with weak pull-up                                                                                                                              |

| РВ          | PCI 3-state bidirectional (3.3V, 5V tolerant)                                                                                                                                |

| PO          | PCI Output (3.3V)                                                                                                                                                            |

| PSTS        | PCI Sustained 3-state bidirectional (Active LOW signal which must be driven inactive for one cycle before being 3-stated to ensure HIGH performance on a shared signal line) |

| PTS         | PCI 3-state Output                                                                                                                                                           |

| POD         | PCI Output which either drives LOW (active state) or 3-stated                                                                                                                |

| CI          | CMOS Input                                                                                                                                                                   |

| CIU         | CMOS Input with weak pull-up                                                                                                                                                 |

| CID         | CMOS Input with weak pull-down                                                                                                                                               |

| СТО         | CMOS 3-state Output                                                                                                                                                          |

### **3.2 Signals** (Note: Signal name that ends with character '#' is active LOW.)

### 3.2.1 Primary Bus Interface Signals

| Name       | Pin #                                                                                                                                                                       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P_AD[31:0] | Y7, W7, Y8, W8, V8,<br>U8, Y9, W9, W10,<br>V10, Y11, V11, U11,<br>Y12, W12, V12, V16,<br>W16, Y16, W17,<br>Y17, U18, W18, Y18,<br>U19, W19, Y19, U20,<br>V20, Y20, T17, R17 | РВ   | <b>Primary Address/Data.</b> Multiplexed address and data bus. Address is indicated by P_FRAME# assertion. Write data is stable and valid when P_IRDY# is asserted and read data is stable and valid when P_TRDY# is asserted. Data is transferred on rising clock edges when both P_IRDY# and P_TRDY# are asserted. During bus idle, PI7C7100 drives P_AD to a valid logic level when P_GNT# is asserted.                                                                                                                                                                                           |

| P_CBE[3:0] | V9, U12, U16, V19                                                                                                                                                           | РВ   | <b>Primary Command/Byte Enables.</b> Multiplexed command field and byte enable field. During address phase, the initiator drives the transaction type on these pins. After that the initiator drives the byte enables during data phases. During bus idle, PI7C7100 drives P_CBE[3:0] to a valid logic level when P_GNT# is asserted.                                                                                                                                                                                                                                                                |

| P_PAR      | U15                                                                                                                                                                         | РВ   | <b>Primary Parity.</b> Parity is even across P_AD[31:0], P_CBE[3:0], and P_PAR (i.e. an even number of '1's). P_PAR is an input and is valid and stable one cycle after the address phase (indicated by assertion of P_FRAME#) for address parity. For write data phases, P_PAR is an input and is valid one clock after P_IRDY# is asserted. For read data phase, P_PAR is an output and is valid one clock after P_TRDY# is asserted. Signal P_PAR is tri-stated one cycle after the PAD lines are 3-stated. During bus idle, PI7C7100 drives PPAR to a valid logic level when P_GNT# is asserted. |

| P_FRAME#   | W13                                                                                                                                                                         | PSTS | <b>Primary FRAME (Active LOW).</b> Driven by the initiator of a transaction to indicate the beginning and duration of an access. The de-assertion of P_FRAME# indicates the final data phase requested by the initiator. Before being 3-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                                                   |

### 3.2.1 Primary Bus Interface Signals (continued)

| Name      | Pin # | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|-----------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P_IRDY#   | V13   | PSTS | Primary IRDY (Active LOW). Driven by the initiator of a transaction to indicate its ability to complete current data phase on the primary side. Once asserted in a data phase, it is not de-asserted until end of data phase. Before being 3-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                            |  |  |  |  |

| P_TRDY#   | U13   | PSTS | Primary TRDY (Active LOW). Driven by the target of a transaction to indicate its ability to complete current data phase on the primary side. Once asserted in a data phase, it is not de-asserted until end of data phase. Before being 3-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                               |  |  |  |  |

| P_DEVSEL# | Y14   | PSTS | <b>Primary Device Select (Active LOW).</b> Asserted by the target indicating that the device is accepting the transaction. As a master, PI7C7100 waits for the assertion of this signal within 5 cycles of P_FRAME# assertion; otherwise, terminate with master abort. Before being 3-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                   |  |  |  |  |

| P_STOP#   | W14   | PSTS | <b>Primary STOP (Active LOW).</b> Asserted by the target indicating that the target is requesting the initiator to stop the current transaction. Before being 3-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| P_LOCK#   | V14   | PSTS | Primary LOCK (Active LOW). Asserted by master for multiple transactions to complete.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| P_IDSEL   | Y10   | PI   | <b>Primary ID Select.</b> Used as chip select line for Type 0 configuration access to PI7C7100 configuration space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| P_PERR#   | Y15   | PSTS | <b>Primary Parity Error (Active LOW).</b> Asserted when a data parity error is detected for data received on the primary interface. Before being 3-stated, it is driven to a deasserted state for one cycle.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| P_SERR#   | W15   | POD  | Primary System Error (Active LOW). Can be driven LOW by any device to indicate a system error condition, PI7C7100 drives this pin on:  • Address parity error  • Posted write data parity error on target bus  • Secondary S1_SERR# or S2_SERR# asserted  • Master abort during posted write transaction  • Target abort during posted write transaction  • Posted write transaction discarded  • Delayed write request discarded  • Delayed read request discarded  • Delayed transaction master timeout  This signal requires an external pull-up resistor for proper operation. |  |  |  |  |

| P_REQ#    | W6    | PTS  | <b>Primary Request (Active LOW).</b> This is asserted by PI7C7100 to indicate that it wants to start a transaction on the primary bus. PI7C7100 de-asserts this pin for at least 2 PCI clock cycles before asserting it again.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| P_GNT#    | U7    | PI   | <b>Primary Grant (Active LOW)</b> . When asserted, PI7C7100 can access the primary bus. During idle and P_GNT# asserted, PI7C7100 will drive P_AD, P_CBE and P_PAR to valid logic levels.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| P_RESET#  | Y5    | PI   | <b>Primary RESET (Active LOW).</b> When P_RESET# is active, all PCI signals should be asynchronously 3-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| P_FLUSH#  | W5    | PI   | <b>Primary FIFO FLUSH (Active LOW).</b> When P_FLUSH# is active, all primary FIFO(s) are cleared (invalidate all primary transactions). This signal should be pulled to a static "high."                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| P_M66EN   | V18   | _    | Reserved for Future Use. Must be tied to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

5

### 3.2.2 Secondary Bus Interface Signals

| Name                        | Pin #                                                                                                                                                        | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S1_AD[31:0], S2_AD[31:0]    | C18, D20, D19, D17,<br>E19, E18, E17, F20,<br>F19, F17, G20, G19,<br>L20, L19, L18, M20,<br>M19, M17, N20, N19,<br>N18, N17, P17, R20,<br>R19, R18, T20, T19 |      | Secondary Address/Data. Multiplexed address and data bus. Address is indicated by S1_FRAME# or S2_FRAME# assertion. Write data is stable and valid when S1_IRDY# or S2_IRDY# is asserted and read data is stable and valid when S1_TRDY# or S2_TRDY# is asserted. Data is transferred on rising clock edges when both S1_IRDY# and S1_TRDY# or S2_IRDY# and S2_TRDY# are asserted. During bus idle, PI7C7100 drives S1_AD or S2_AD to a valid logic level when the S1_GNT# or S2_GNT# is asserted respectively.                                                                                                                                                                                                                                                    |

| S1_CBE[3:0],<br>S2_CBE[3:0] | E20, G18, K17, P20<br>F1, A1, A4, A7                                                                                                                         | PB   | Secondary Command/Byte Enables. Multiplexed command field and byte enable field. During the address phase, the initiator drives the transaction type on these pins. After that the initiator drives the byte enables during data phases. During bus idle, PI7C7100 drives S1_CBE[3:0] or S2_CBE[3:0] to a valid logic level when the internal grant is asserted.                                                                                                                                                                                                                                                                                                                                                                                                   |

| S1_PAR,<br>S2_PAR           | K18,<br>B4                                                                                                                                                   | РВ   | Secondary Parity. Parity is even across S1_AD[31:0], S1_CBE[3:0], and S1_PAR or S2_AD[31:0], S2_CBE[3:0], and S2_PAR (i.e. an even number of '1's). S1_PAR or S2_PAR is an input and is valid and stable one cycle after the address parity (indicated by assertion of S1_FRAME# or S2_FRAME#) for address parity. For write data phases, S1_PAR or S2_PAR is an input and is valid one clock after S1_IRDY# or S2_IRDY# is asserted. For read data phase, S1_PAR or S2_PAR is an output and is valid one clock after S1_TRDY# or S2_TRDY# is asserted. Signal S1_PAR or S2_PAR is 3-stated one cycle after the S1_AD or S2_AD lines are tri-stated. During bus idle, PI7C7100 drives S1_PAR or S2_PAR to a valid logic level when the internal grant is asserted. |

| S1_FRAME#,<br>S2_FRAME#     | H20,<br>D2                                                                                                                                                   | PSTS | Secondary FRAME (Active LOW). Driven by the initiator of a transaction to indicate the beginning and duration of an access. De-assertion of S1_FRAME# or S2_FRAME# indicates the final data phase requested by initiator. Before being 3-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| S1_IRDY#,<br>S2_IRDY#       |                                                                                                                                                              |      | Secondary IRDY (Active LOW). Driven by the initiator of a transaction to indicate its ability to complete the current data phase on the primary side. Once asserted in a data phase, it is not de-asserted until end of the data phase. Before being 3-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| S1_TRDY#,<br>S2_TRDY#       | H18,<br>A2                                                                                                                                                   | PSTS | Secondary TRDY (Active LOW). Driven by the target of a transaction to indicate its ability to complete the current data phase on the primary side. Once asserted in a data phase, it is not de-asserted until end of the data phase. Before being 3-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| S1_DEVSEL#,<br>S2_DEVSEL#   | J20,<br>D3                                                                                                                                                   | PSTS | Secondary Device Select (Active LOW). Asserted by the target indicating that the device is accepting the transaction. As a master, PI7C7100 waits for the assertion of this signal within 5 cycles of S1_FRAME# or S2_FRAME# assertion; otherwise, terminate with master abort. Before being 3-stated, it is driven to a de-asserted state for one cycle.                                                                                                                                                                                                                                                                                                                                                                                                          |

6

### 3.2.2 Secondary Bus Interface Signals (continued)

| Name                          | Pin #                                                                                   | Туре | Description                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| S1_STOP#,<br>S2_STOP#         | J19,<br>C3                                                                              | PSTS | Secondary STOP (Active LOW). Asserted by the target indicating that the target is requesting the initiator to stop the current transaction. Before being 3-stated, it is driven to a de-asserted state for one cycle.                                                                                                                    |  |  |

| S1_LOCK#,<br>S2_LOCK#         | J18,<br>B3                                                                              | PSTS | Secondary LOCK (Active LOW). Asserted by master for multiple transactions to complete.                                                                                                                                                                                                                                                   |  |  |

| S1_PERR#,<br>S2_PERR#         | J17,<br>D4                                                                              | PSTS | Secondary Parity Error (Active LOW). Asserted when a data parity error is detected for data received on the secondary interface. Before being 3-stated, it is driven to a de-asserted state for one cycle.                                                                                                                               |  |  |

| S1_SERR#,<br>S2_SERR#         | K20,<br>C4                                                                              | PI   | <b>Secondary System Error (Active LOW).</b> Can be driven LOW by any device to indicate a system error condition.                                                                                                                                                                                                                        |  |  |

| S1_REQ#[7:0],<br>S2_REQ#[7:0] | B11, A12,<br>D13, C13,<br>C15, A16,<br>C17, B17<br>T2, R3, P2,<br>P1, M2, M1,<br>K1, K3 | PIU  | Secondary Request (Active LOW). This is asserted by an external device to indicate that it wants to start a transaction on the Secondary bus. The input is externally pulled up through a resistor to VDD.                                                                                                                               |  |  |

| S1_GNT#[7:0],<br>S2_GNT#[7:0] | C11, B12,<br>B13, A14,<br>D14, B16,<br>D16, B18<br>U1, P4, R1,<br>N4, M3, L4,<br>L1, K2 | PO   | Secondary Grant (Active LOW). PI7C7100 asserts this pin to access the secondary bus. PI7C7100 de-asserts this pin for at least 2 PCI clock cycles before asserting it again. During idle and S1_GNT# or S2_GNT# asserted, PI7C7100 will drive S1_AD, S1_CBE and S1_PAR or S2_AD, S2_CBE and S2_PAR to valid logic levels.                |  |  |

| S1_RESET#,<br>S2_RESET#       | B10,<br>T4                                                                              | PO   | Secondary RESET (Active LOW). Asserted when any of the following conditions are met:  1. Signal P_RESET# is asserted.  2. Secondary reset bit in bridge control register in configuration space is set.  When asserted, all control signals are 3-stated and zeros are driven on S1_AD, S1_CBE, and S1_PAR or S2_AD, S2_CBE, and S2_PAR. |  |  |

| S1_EN,<br>S2_EN               | W3,<br>W4                                                                               | PIU  | Secondary Enable (Active HIGH). When S1_EN or S2_EN is inactive, secondary PCI S1 or S2 bus will be asynchronously 3-stated.                                                                                                                                                                                                             |  |  |

| S_M66EN                       | D7                                                                                      | _    | Reserved for Future Use. Must be tied to ground.                                                                                                                                                                                                                                                                                         |  |  |

| S_CFN#                        | Y2                                                                                      | CIU  | Secondary Bus Central Function Control Pin. When tied LOW, it enables the internal arbiter. When tied HIGH, an external arbiter must be used. S1_REQ0# or S2_REQ0# is reconfigured to be the secondary bus grant input, and S1_GNT0# or S2_GNT0# is reconfigured to be the secondary bus request output.                                 |  |  |

7

### 3.2.3 Clock Signals

| Name               | Pin #                                                                               | Туре | Description                                                                         |

|--------------------|-------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------|

| P_CLK              | V6                                                                                  | PI   | Primary Clock Input. Provides timing for all transaction on primary interface.      |

| S_CLKOUT<br>[15:0] | T3, T1, P3,<br>N3,M4, L3, L2,<br>J1,A11, C12,<br>A13, B14,<br>B15, C16,<br>A18, A19 | PTS  | Secondary Clock Output. Provides secondary clocks phase synchronous with the P_CLK. |

### 3.2.4 Miscellaneous Signals

| Name     | Pin # | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|----------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BYPASS   | Y4    | _    | Reserved for Future Use. Must be tied HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| PLL_TM   | Y3    | _    | Reserved for Future Use. Must be tied LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| S_CLKIN  | V5    | PI   | Secondary Test Clock Input. It should be tied to LOW in normal mode. It also may be a secondary clock input for the secondary buses if both SCAN_TM# and SCAN_EN are connected to logic "1".                                                                                                                                                                                                                                                                                                                                                                         |  |

| SCAN_TM# | V4    | CI   | Full-scan Test Mode enable (Active LOW). When SCAN_TM# is active, the twelve scan chains will be enabled. The scan clock is P_CLK. The scan inputs and outputs are as follows:  S1_REQ[7], S1_REQ[6], S1_REQ[5], S1_REQ[4], S1_REQ[3], S1_REQ[2], S2_REQ[7], S2_REQ[6], S2_REQ[5], S2_REQ[4], S2_REQ[3], S2_REQ[2] and S1_GNT[7], S1_GNT[6], S1_GNT[5], S1_GNT[4], S1_GNT[3], S1_GNT[2], S2_GNT[7], S2_GNT[6], S2_GNT[5], S2_GNT[4], S2_GNT[3], S2_GNT[2] respectively                                                                                               |  |

| SCAN_EN  | U5    | CIU  | Full-scan Enable Control. When SCAN_EN is LOW, full-scan is in shift operation if SCAN_TM# is active. When SCAN_EN is HIGH, full-scan is in parallel operation if SCAN_TM# is active. SCAN_EN should be tied LOW in normal mode. If SCAN_TM# and SCAN_EN are connected to logic "1", S_CLKIN is the clock source for the internal secondary clock. If SCAN_TM# is connected to logic "1" and SCAN_EN is connected to logic "0", P_CLK is the clock source for the internal secondary clock.  Note: During power-up, SCAN_EN is the reset signal for the on-chip PLL. |  |

| CMPO1    | U6    | _    | Reserved for Future Use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Reserved | R4    |      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

### 3.2.5 JTAG Boundary Scan Signals

| Name  | Pin # | Туре | Description                                                                                                                                                          |

|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCK   | V2    | CIU  | <b>Test Clock.</b> Used to clock state information and data into and out of the PI7C7100 during boundary scan.                                                       |

| TMS   | W1    | CIU  | Test Mode Select. Used to control the state of the Test Access Port controller.                                                                                      |

| TDO   | V3    | СТО  | <b>Test Data Output.</b> When SCANEN is HIGH it is used (in conjunction with TCK) to shift data out of the Test Access Port (TAP) in a serial bit stream.            |

| TDI   | W2    | CIU  | <b>Test Data Input.</b> When SCANEN is HIGH it is used (in conjunction with TCK) to shift data and instructions into the Test Access Port (TAP) a serial bit stream. |

| TRST# | U3    | CIU  | <b>Test Reset.</b> Active LOW signal to reset the Test Access Port (TAP) controller into an initialized state.                                                       |

8

#### 3.2.6 Power and Ground

| Name | Pin #                                                                                                                               | Type | Description           |

|------|-------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|

| VDD  | B8, C14, D5, D11, D15, E2, F18, J3, L17, N2, P19, U10, V1, V7, V15, W20                                                             |      | +3.3V Digital Power   |

| VSS  | A3, A5, A8, A10, A15, A17, A20, C2, D12, D18, E3, G2, G17, H17, J2, K4, K19, M18, N1, P18, R2, T18, U2, U9, U14, U17 V17 W11 Y6 Y13 |      | Digital Ground        |

| AVCC | Y1                                                                                                                                  |      | Analog 3.3V for PLL   |

| AGND | U4                                                                                                                                  |      | Analog Ground for PLL |

### 3.3 PI7C7100 PBGA Pin List

| Pin No. | Name        | Туре | Pin No. | Name        | Туре |

|---------|-------------|------|---------|-------------|------|

| A1      | S2_CBE[2]   | PB   | A2      | S2_TRDY#    | PSTS |

| A3      | VSS         | _    | A4      | S2_CBE[1]   | РВ   |

| A5      | VSS         | _    | A6      | S2_AD[10]   | РВ   |

| A7      | S2_CBE[0]   | РВ   | A8      | VSS         | _    |

| A9      | S2_AD[2]    | PB   | A10     | VSS         | _    |

| A11     | S_CLKOUT[7] | PTS  | A12     | S1_REQ#[6]  | PIU  |

| A13     | S_CLKOUT[5] | PTS  | A14     | S1_GNT#[6]  | PO   |

| A15     | VSS         | _    | A16     | S1_REQ#[2]  | PIU  |

| A17     | VSS         | _    | A18     | S_CLKOUT[1] | PTS  |

| A19     | S_CLKOUT[0] | PTS  | A20     | VSS         | _    |

| B1      | S2_AD[16]   | РВ   | B2      | S2_IRDY#    | PSTS |

| B3      | S2_LOCK#    | PSTS | B4      | S2_PAR      | РВ   |

| B5      | S2_AD[14]   | РВ   | B6      | S2_AD[11]   | РВ   |

| B7      | S2_AD[8]    | PB   | B8      | VDD         | _    |

| B9      | S2_AD[3]    | РВ   | B10     | S1_RESET#   | PO   |

| B11     | S1_REQ#[7]  | PIU  | B12     | S1_GNT#[6]  | PO   |

| B13     | S1_GNT#[7]  | PO   | B14     | S_CLKOUT[4] | PTS  |

| B15     | S_CLKOUT[3] | PTS  | B16     | S1_GNT#[2]  | PO   |

| B17     | S1_REQ#[0]  | PIU  | B18     | S1_GNT#[0]  | PO   |

| B19     | S1_AD[30]   | РВ   | B20     | S1_AD[31]   | РВ   |

| C1      | S2_AD[17]   | РВ   | C2      | VSS         | _    |

| C3      | S2_STOP#    | PSTS | C4      | S2_SER#     | PI   |

| C5      | S2_AD[15]   | РВ   | C6      | S2_AD[12]   | РВ   |

| C7      | S2_AD[9]    | РВ   | C8      | S2_AD[6]    | РВ   |

| C9      | S2_AD[4]    | РВ   | C10     | S2_AD[0]    | РВ   |

| C11     | S1_GNT#[7]  | РО   | C12     | S_CLKOUT[6] | PTS  |

| C13     | S1_REQ#[4]  | PIU  | C14     | VDD         | _    |

| C15     | S1_REQ#[3]  | PIU  | C16     | S_CLKOUT[2] | PTS  |

9

### 3.3 PI7C7100 PBGA Pin List (continued)

| Pin No. | Name        | Туре | Pin No. | Name       | Туре |

|---------|-------------|------|---------|------------|------|

| C17     | S1_REQ#[1]  | PIU  | C18     | S1_AD[27]  | РВ   |

| C19     | S1_AD[28]   | PB   | C20     | S1_AD[29]  | РВ   |

| D1      | S2_AD[18]   | PB   | D2      | S2_FRAME#  | PSTS |

| D3      | S2_DEVSEL#  | PSTS | D4      | S2_PERR#   | PSTS |

| D5      | VDD         | _    | D6      | S2_AD[13]  | РВ   |

| D7      | S_M66EN     | _    | D8      | S2_AD[7]   | РВ   |

| D9      | S2_AD[5]    | PB   | D10     | S2_AD[1]   | РВ   |

| D11     | VDD         | _    | D12     | VSS        | _    |

| D13     | S1_REQ#[5]  | PIU  | D14     | S1_GNT#[3] | PO   |

| D15     | VDD         | _    | D16     | S1_GNT#[1] | PO   |

| D17     | S1_AD[24]   | PB   | D18     | VSS        | _    |

| D19     | S1_AD[25]   | PB   | D20     | S1_AD[26]  | PB   |

| E1      | S2_AD[20]   | PB   | E2      | VDD        | _    |

| E3      | VSS         | _    | E4      | S2_AD[19]  | PB   |

| E17     | S1_AD[21]   | PB   | E18     | S1_AD[22]  | PB   |

| E19     | S1_AD[23]   | PB   | E20     | S1_CBE[3]  | PB   |

| F1      | S2_CBE[3]   | PB   | F2      | S2_AD[23]  | РВ   |

| F3      | S2_AD[22]   | РВ   | F4      | S2_AD[21]  | РВ   |

| F17     | S1_AD[18]   | РВ   | F18     | VDD        | _    |

| F19     | S1_AD[19]   | PB   | F20     | S1_AD[20]  | PB   |

| G1      | S2_AD[26]   | PB   | G2      | VSS        | _    |

| G3      | S2_AD[25]   | PB   | G4      | S2_AD[24]  | РВ   |

| G17     | VSS         | _    | G18     | S1_CBE[2]  | РВ   |

| G19     | S1_AD[16]   | PB   | G20     | S1_AD[17]  | PB   |

| H1      | S2_AD[30]   | PB   | H2      | S2_AD[29]  | РВ   |

| H3      | S2_AD[28]   | PB   | H4      | S2_AD[27]  | РВ   |

| H17     | VSS         | _    | H18     | S1_TRDY#   | PSTS |

| H19     | S1_IRDY#    | PSTS | H20     | S1_FRAME#  | PSTS |

| J1      | S_CLKOUT[8] | PTS  | J2      | VSS        | _    |

| J3      | VDD         | _    | J4      | S2_AD[31]  | РВ   |

| J17     | S1_PERR#    | PSTS | J18     | S1_LOCK#   | PSTS |

| J19     | S1_STOP#    | PSTS | J20     | S1_DEVSEL# | PSTS |

10

### 3.3 PI7C7100 PBGA Pin List (continued)

| Pin No. | Name         | Туре | Pin No. | Name         | Туре |

|---------|--------------|------|---------|--------------|------|

| K1      | S2_REQ#[1]   | PIU  | K2      | S2_GNT#[0]   | PO   |

| K3      | S2_REQ#[0]   | PIU  | K4      | VSS          | _    |

| K17     | S1_CBE[1]    | РВ   | K18     | S1_PAR       | PB   |

| K19     | VSS          | _    | K20     | S1_SERR#     | PI   |

| L1      | S2_GNT#[1]   | РО   | L2      | S_CLKOUT[9]  | PTS  |

| L3      | S_CLKOUT[10] | PTS  | L4      | S2_GNT#[2]   | PO   |

| L17     | VDD          | _    | L18     | S1_AD[13]    | PB   |

| L19     | S1_AD[14]    | РВ   | L20     | S1_AD[15]    | PB   |

| M1      | S2_REQ#[2]   | PIU  | M2      | S2_REQ#[3]   | PIU  |

| M3      | S2_GNT#[3]   | РО   | M4      | S_CLKOUT[11] | PTS  |

| M17     | S1_AD[10]    | РВ   | M18     | VSS          | _    |

| M19     | S1_AD[11]    | РВ   | M20     | S1_AD[12]    | PB   |

| N1      | VSS          | _    | N2      | VDD          | _    |

| N3      | S_CLKOUT[12] | PTS  | N4      | S2_GNT#[4]   | PO   |

| N17     | S1_AD[6]     | РВ   | N18     | S1_AD[7]     | PB   |

| N19     | S1_AD[8]     | РВ   | N20     | S1_AD[9]     | PB   |

| P1      | S2_REQ#[4]   | PIU  | P2      | S2_REQ#[5]   | PIU  |