## Features

- 50 $\Omega$  Input Clock and Data (Differential ECL) through 2.54 mm Pitch Connectors

- Demultiplexed Outputs (Single-ended ECL) 50Ω Adapted on up to 8 x 2.54 mm Pitch Connectors

- DMUX Functions Adjusted by Jumpers and Potentiometers

- Separated Ground and Supplies

- Suitable for High-frequency Evaluation (up to 2.2 GHz) over the Military Temperature Range

- Board Dimensions: 200 mm x 190 mm

- Fully Assembled and Tested

For optimal understanding and use of this evaluation board, please refer to the TS81102G0 DMUX specification also.

# Description

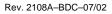

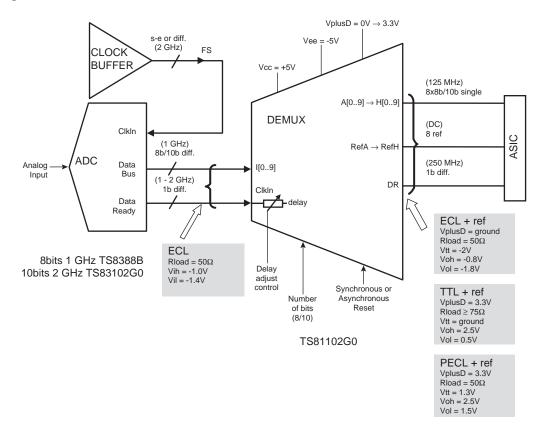

The TSEV81102G0TPZR3 DMUX Evaluation Board (EB) is designed to simplify the characterization and the evaluation of the TS81102G0 device (2 Gsps DMUX). The DMUX EB enables the test of all the functions of the DMUX: Synchronous and Asynchronous reset functions, selection of the DMUX ratio (1:4 or 1:8), selection of the number of bits (8 or 10), output data common mode and swing adjustment, die junction temperature measurements over military temperature range, etc.

The DMUX EB has been designed to enable an easy connection with Atmel ADC Evaluation Boards (i.e.: TSEV8388BG, TSEV83102G0 or TSEV83084G0) for an extended functionality evaluation (ADC+DMUX multi-channels applications).

The DMUX EB comes fully assembled and tested, with a TS81102G0 device implemented on-board and a heatsink assembled on the device.

DMUX 8-/10-bit 1:4/1:8 2 Gsps Evaluation Board

# <sup>2</sup> TSEV81102G0TPZR3

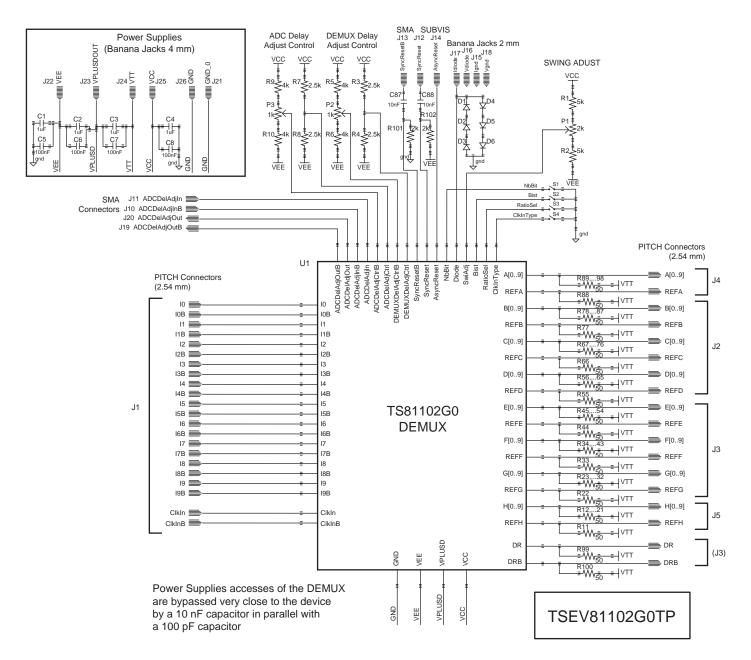

Figure 1. TSEV81102G0TPZR3 Block Diagram

**Block Diagram**

### **Board Structure**

Board Layers Thickness Profile The TSEV81102G0TPZR3 is a seven-layered PCB constituted by four copper layers and three dielectric layers. The board is 1.75 mm thick. The board has the following structure, from top to bottom.

Table 1. Board Layers Thickness Profile

| Layer                                                         | Characteristics                                                                                                                                            |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Layer 1<br>Copper layer                                       | Copper thickness = $35 \ \mu m$<br>Input signals: $50\Omega$ microstrip lines<br>Output data signals: $60\Omega$ microstrip lines, $50\Omega$ terminated   |

| Layer 2<br>R4003 dielectric layer<br>(Hydrocarbon/Wovenglass) | Layer thickness = 200 µm<br>Dielectric constant = 3.4 at 10 GHz<br>-0.044 dB / inch insertion loss at 2.5 GHz<br>-0.318 dB / inch insertion loss at 18 GHz |

| Layer 3<br>Copper layer                                       | Copper thickness = $35 \ \mu m$<br>Upper reference plane, divided in two parts: GND and V <sub>PLUSDOUT</sub>                                              |

| Layer 4<br>BT/Epoxy dielectric layer                          | Layer thickness = 0.4 mm                                                                                                                                   |

| Layer 5<br>Copper layer                                       | Copper thickness = 35 $\mu$ m<br>Power plane: V <sub>EE</sub> , V <sub>CC</sub> , V <sub>TT</sub> , GND                                                    |

| Layer 6<br>BT/Epoxy dielectric layer                          | Layer thickness = 1.0 mm                                                                                                                                   |

| Layer 7<br>Copper layer                                       | Copper thickness = 35 µm<br>Lower reference plane (replica of layer 3)                                                                                     |

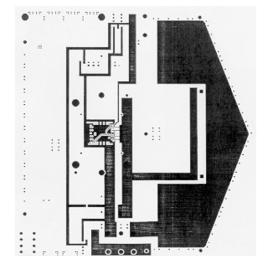

# Metal Layers The four metal layers respectively correspond to: the signals' layer (layer 1) (Figure 7), the two reference layers (layer 3 and layer 7) (Figure 8) and the supply layer (layer 5) (Figure 9 on page 16).

The upper and the lower reference planes (layer 3 and 7) are partitioned into GND (reference for input signals) and  $V_{PLUSDOUT}$  (reference for digital output signals), according to the same partition of the DMUX package.

Layer 5 is dedicated to power supplies (and ground).

### **Dielectric Layers**

The three dielectric layers are respectively constituted by a low insertion loss dielectric (RO4003) layer (layer 2) and by a BT/Epoxy dielectric layer (layer 4 and 6).

Considering the severe mechanical constraints due to the wide temperature range and the high frequency domain in which the board is to operate, two different dielectric materials are used:

- The low insertion loss RO4003 Hydrocarbon/Wovenglass dielectric (-0.044 dB/inch loss at 2.5 GHz) which has an enhanced dielectric consistency in the high frequency domain is dedicated to the routing of 50Ω and 60Ω traces. The RO4003 dielectric constant is typically 3.4 at 10 GHz.

- The BT/Epoxy layer is chosen because of its enhanced mechanical characteristics for elevated temperature operations. The typical dielectric constant is 4.5 at 1 MHz. The BT/Epoxy dielectric has enhanced characteristics compared to FR4 Epoxy dielectric, namely:

- higher operating temperature value: 170°C (125°C for FR4),

- better withstanding of thermal shocks (from -65°C up to 170°C).

The characteristics of these two dielectrics make the board particularly suitable for performing measurements in the high frequency domain and over the military temperature range.

### I/O Accesses

| Power Supplies<br>and Ground | The power supplies and ground access are provided by four 4 mm section banana jacks (red jacks) respectively for $V_{EE}$ , $V_{CC}$ , $V_{TT}$ , $V_{PLUSDOUT}$ .     |  |  |  |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Access                       | The Ground access is provided by two 4 mm banana jacks (black jacks).                                                                                                  |  |  |  |  |  |

|                              | Note: Two distinct Ground pads GND have been implemented on the board because of layout consid-<br>erations. For proper use, connect them together to the same Ground. |  |  |  |  |  |

### Input Access

Input Data and ClockAccess to the differential data and clock inputs (ClkIn, ClkInb, I[0..9], I[0..9]b) are provided by<br/>a female 2.54 mm pitch connector, via 50Ω microstrip lines.

The connector is made of 2 rows of pitches. The lower row is connected to GND. The upper row is used for the data and the clock connections. Each differential signal is separated by a pitch connected to GND, as shown:

Figure 2. Input Data Pitch Connector

| GN<br> | ln1 | In1b | GN | ln2 | In2b | GN |

|--------|-----|------|----|-----|------|----|

| GN<br> | GN  | GN   | GN | GN  | GN   | GN |

Note:  $100\Omega$  differential adaptation is performed on-chip.

# TSEV81102G0TPZR3

| Synchronous Reset<br>Access                 | <ul> <li>Access to the signals SyncReset and SyncResetb is provided by two SMA connectors, via 50Ω microstrip lines.</li> <li>Note: 100Ω differential adaptation is performed on-chip.</li> </ul>                                                                    |  |  |  |  |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Asynchronous Reset<br>Access                | Access to the signal AsyncReset is provided by a SUBVIS connector.                                                                                                                                                                                                   |  |  |  |  |  |

| ADC Synchronization<br>Input Signal Access  | Access to the differential signal ADCDELADJIN is provided by two SMA connectors, via 50Ω microstrip lines.<br>Note: 100Ω differential adaptation is performed on-chip.                                                                                               |  |  |  |  |  |

| Outputs Access                              |                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Digital Outputs                             | Access to the single-ended output data and to the differential output clock (A[09] to H[09], RefA to RefH, DR, DRb) is provided by male 2.54 mm pitch connectors, via $60\Omega$ microstrip lines. The microstrip lines are $50\Omega$ terminated.                   |  |  |  |  |  |

|                                             | The connectors are made of 2 rows of pitches. The upper rows are used for the signals' connections. The lower rows are connected to $V_{PLUSDOUT}$ . The output ports are separated from one another by a column (2 pitches) connected to $V_{PLUSDOUT}$ , as shown: |  |  |  |  |  |

|                                             | Figure 3. Output Data Pitch Connector                                                                                                                                                                                                                                |  |  |  |  |  |

|                                             | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               |  |  |  |  |  |

|                                             | Note: The characteristic impedance of the data output microstrip lines has been chosen to be $60\Omega$ , in order to terminate the lines either by $50\Omega$ (ECL/PECL output format) or $75\Omega$ resistors (TTL output format, available on request only).      |  |  |  |  |  |

| ADC Synchronization<br>Output Signal Access | Accesses to the differential signal ADCDELADJOUT are provided by two SMA connectors, via $50\Omega$ microstrip lines.                                                                                                                                                |  |  |  |  |  |

| DMUX Functions<br>Settings                  | Four 2 mm-section banana jacks are provided to perform die temperature measurements (see "DMUX Settings Adjustment" on page 14).                                                                                                                                     |  |  |  |  |  |

|                                             | Three potentiometers are provided for the adjustment of SWIADJ, ADCDELADJCTRL and DMUXDELADJCTRL respectively.                                                                                                                                                       |  |  |  |  |  |

|                                             | Four jumpers are provided for the setting of the static control signals NBBIT, RATIOSEL, CLKINTYPE and BIST (jumper on board = logic 0).                                                                                                                             |  |  |  |  |  |

| mpi |

|-----|

|     |

|     |

| R   |

| Layout<br>Information        | Because the DMUX processes high-frequency signals, special attention was given to the board layout in order to achieve full speed operation efficiency. Thus, special effort was made in order to match the length of transmission lines for both input and output signals. In addition, cross-talk effects were reduced by increasing, wherever possible, the space between the lines. |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Supplies<br>Decoupling | Each power supply is bypassed by a 1 µF Tantalum capacitor in parallel with a 100 nF chip capacitor.<br>Each power supply access of the DMUX is also bypassed as close as possible to the device, by a 10 nF and a 100 pF surface mount chip capacitor in parallel.<br>Note: Those capacitors are superposed.                                                                           |

| Reference Planes             | Each reference plane (layer 3 and layer 7) is physically divided in two parts: one GND trace and one $V_{PLUSDOUT}$ trace, which is the voltage reference of the output buffers of the DMUX. $V_{PLUSDOUT}$ can be set to GND (ECL format) or to 3.3V (PECL/TTL format) according to the desired output format.                                                                         |

| I/O Transmission<br>Lines    | The following table summarizes the main properties of the microstrip lines of all the input and output signals. Note that the transmission delay through a transmission line is approximately                                                                                                                                                                                           |

6.1 ps/mm.

| Signal                         | Туре         | Typical<br>Length    | Length<br>Matching | Characteristic<br>Impedance | Adaptation                | Comments                                                    |

|--------------------------------|--------------|----------------------|--------------------|-----------------------------|---------------------------|-------------------------------------------------------------|

| ClkIn<br>ClkInb                | Differential | 69 mm<br>69.7 mm     | -                  | 50Ω<br>50Ω                  | On-chip $100\Omega$ diff. |                                                             |

| l[09], l[09]b                  | Differential | 68.8 mm              | ±1                 | $50\Omega$                  | On-chip $100\Omega$ diff. | Min length (I3): 67.8 mm<br>Max length (I9): 69.6 mm        |

| A[09],, H[09]                  | Single       | 111.4 mm             | ±8                 | 60Ω                         | $50\Omega$                | Min length (F3 & E5): 104.2 mm<br>Max length (C9): 119.3 mm |

| DR<br>DRb                      | Differential | 111.9 mm<br>114.5 mm |                    | $60\Omega$<br>$60\Omega$    | 50Ω<br>50Ω                |                                                             |

| SyncReset,<br>SyncResetb       | Differential | 96 mm                | ±1                 | $50\Omega$                  | On-chip $100\Omega$ diff. |                                                             |

| ADCDELADJIN,<br>ADCDELADJINb   | Differential | 104 mm               | ±1                 | $50\Omega$                  | On-chip $100\Omega$ diff. |                                                             |

| ADCDELADJOUT,<br>ADCDELADJOUTb | Differential | 111 mm               | ±1                 | $50\Omega$                  | None                      |                                                             |

Note: Two ground accesses, OSC1 and OSC2, have been provided near the DMUX for measurements purposes.

# Pin and Package Description

Information in this section is extracted from the TS81102G0 DMUX datasheet. For exhaustive information about the device's package, please refer to its datasheet.

### **Pin Description**

| Table 3. ⊤ | SEV81102G0TPZR3 Pin Description |

|------------|---------------------------------|

|------------|---------------------------------|

| Туре            | Name                  | Levels                               | Comments                                                                                                                                                                            |  |  |  |  |  |

|-----------------|-----------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Digital Inputs  | I[09]                 | Differential ECL                     | Data input.                                                                                                                                                                         |  |  |  |  |  |

|                 | ClkIn                 | Differential ECL                     | Clock input.                                                                                                                                                                        |  |  |  |  |  |

| Outputs         | A[09] → H[09]         | Adjustable Logic<br>Single           | Data output for channel A to H.<br>Common mode is adjusted with V <sub>PLUSDOUT</sub> . Swing is adjusted w<br>SwiAdj.                                                              |  |  |  |  |  |

|                 | DR                    | Adjustable Logic<br>Single           | Data output for channel A to H.<br>Common mode is adjusted with V <sub>PLUSDOUT</sub> . Swing is adjusted with<br>SwiAdj.                                                           |  |  |  |  |  |

|                 | $RefA \to RefH$       | Adjustable Single                    | Reference voltage for channels A to H.<br>Common mode is adjustable with V <sub>PLUSDOUT</sub> .                                                                                    |  |  |  |  |  |

| Control Signals | ClkInType             | TTL                                  | Mode DR or DR/2 (logic 1: Data Ready).                                                                                                                                              |  |  |  |  |  |

|                 | RatioSel              | TTL                                  | DMUX ratio (logic 1: 1:4).                                                                                                                                                          |  |  |  |  |  |

|                 | Bist                  | TTL                                  | BIST selection (logic 0: BIST active).                                                                                                                                              |  |  |  |  |  |

|                 | SwiAdj                | 0V ± 0.5V                            | Swing fine adjustment of output buffers.                                                                                                                                            |  |  |  |  |  |

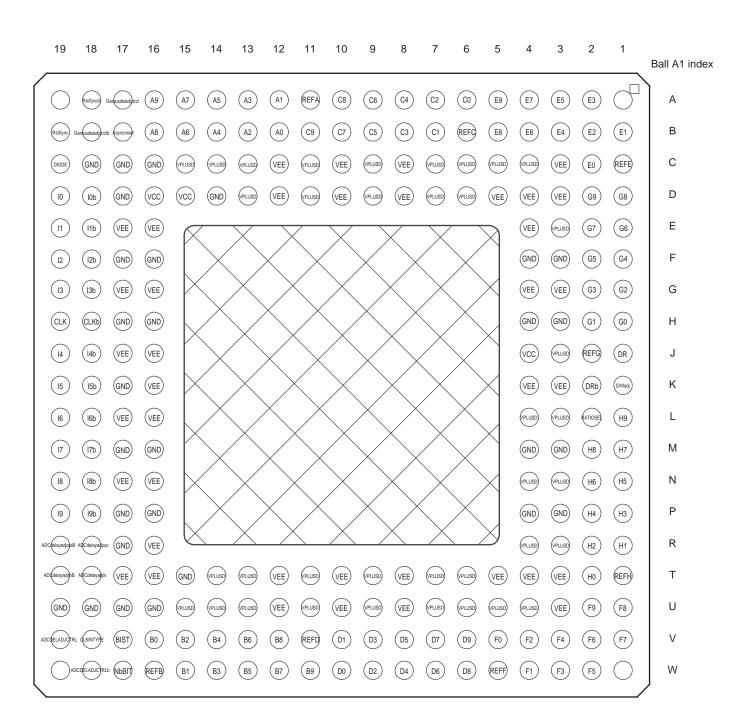

|                 | Diode                 | Analog                               | Diode for chip temperature measurement.                                                                                                                                             |  |  |  |  |  |

|                 | NbBit                 | TTL                                  | Number of bits: 8 or 10 (logic 1: 10 bits).                                                                                                                                         |  |  |  |  |  |

| Synchronization | AsyncReset            | TTL                                  | Asynchronous reset (logic 1: reset on).                                                                                                                                             |  |  |  |  |  |

|                 | SyncReset             | Differential ECL                     | Synchronous reset (on rising edge).                                                                                                                                                 |  |  |  |  |  |

|                 | DMUXDelAdjCtrl        | Differential analog input of ± 0.5V  | Control of the delay line of DataReady input:<br>Differential input = -0.5V, delay = 250 ps<br>Differential input = 0V, delay = 500 ps<br>Differential input = 0.5V, delay = 750 ps |  |  |  |  |  |

|                 | ADCDelAdjCtrl         | Differential analog input of ± 0.5V  | Control of the delay line for ADC:<br>Differential input = $-0.5V$ , delay = 250 ps<br>Differential input = 0V, delay = 500 ps<br>Differential input = $0.5V$ , delay = 750 ps      |  |  |  |  |  |

|                 | ADCDelAdjIn           | Differential ECL                     | Stand-alone delay adjust input for ADC. Differential termination of $100\Omega$ inside the buffer.                                                                                  |  |  |  |  |  |

|                 | ADCDelAdjOut          | $50\Omega$ differential output       | Stand-alone delay adjust output for ADC.                                                                                                                                            |  |  |  |  |  |

| Power Supplies  | GND                   | Ground 0V                            | Common ground.                                                                                                                                                                      |  |  |  |  |  |

|                 | V <sub>EE</sub>       | Power -5V                            | Digital negative power supply.                                                                                                                                                      |  |  |  |  |  |

|                 | V <sub>PLUSDOUT</sub> | Adjustable power<br>from 0V to +3.3V | Common mode adjustment for output buffers.                                                                                                                                          |  |  |  |  |  |

|                 | V <sub>cc</sub>       | Power +5V                            | Digital positive power supply.                                                                                                                                                      |  |  |  |  |  |

# 8 TSEV81102G0TPZR3

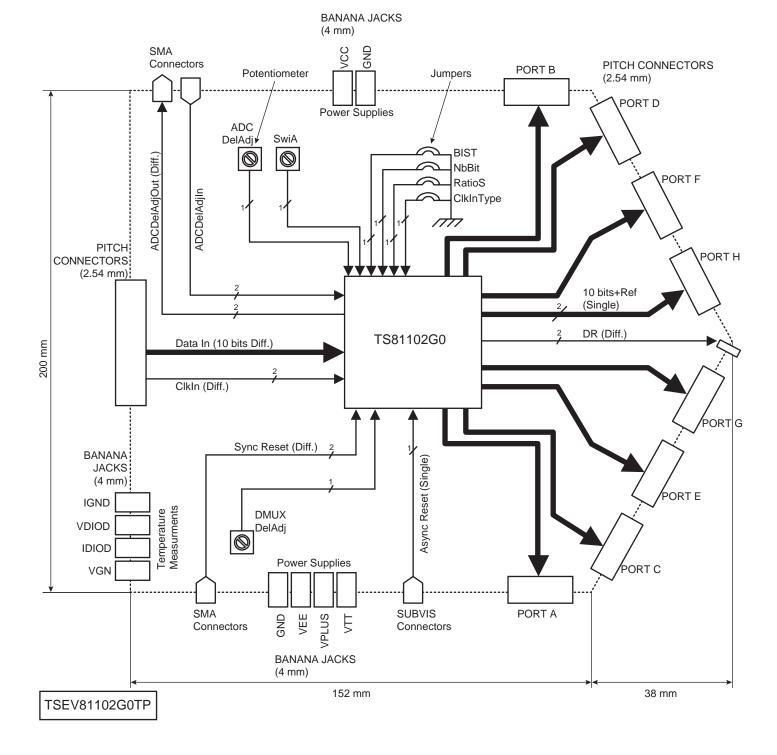

**TBGA 240 Package - Pinout**

| Row    | Col      | Name             | Row    | Col     | Name        | Row    | Col      | Name          | Row    | Col     | Name           |

|--------|----------|------------------|--------|---------|-------------|--------|----------|---------------|--------|---------|----------------|

| А      | 1        | NC               | D      | 4       | VEE         | К      | 16       | VEE           | Т      | 17      | VEE            |

| А      | 2        | E3               | D      | 5       | VEE         | к      | 17       | GND           | Т      | 18      | ADCDELADJIN    |

| А      | 3        | E5               | D      | 6       | VPLUSDOUT   | к      | 18       | 15B           | Т      | 19      | ADCDELADJINB   |

| А      | 4        | E7               | D      | 7       | VPLUSDOUT   | к      | 19       | 15            | U      | 1       | F8             |

| А      | 5        | E9               | D      | 8       | VEE         | L      | 1        | H9            | U      | 2       | F9             |

| А      | 6        | C0               | D      | 9       | VPLUSDOUT   | L      | 2        | RATIOSEL      | U      | 3       | VEE            |

| А      | 7        | C2               | D      | 10      | VEE         | L      | 3        | VPLUSDOUT     | U      | 4       | VPLUSDOUT      |

| Α      | 8        | C4               | D      | 11      | VPLUSDOUT   | L      | 4        | VPLUSDOUT     | U      | 5       | VPLUSDOUT      |

| Α      | 9        | C6               | D      | 12      | VEE         | L      | 16       | VEE           | U      | 6       | VPLUSDOUT      |

| Α      | 10       | C8               | D      | 13      | VPLUSDOUT   | L      | 17       | VEE           | U      | 7       | VPLUSDOUT      |

| Α      | 11       | REFA             | D      | 14      | GND         | L      | 18       | 16B           | U      | 8       | VEE            |

| Α      | 12       | A1               | D      | 15      | VCC         | L      | 19       | 16            | U      | 9       | VPLUSDOUT      |

| А      | 13       | A3               | D      | 16      | VCC         | М      | 1        | H7            | U      | 10      | VEE            |

| А      | 14       | A5               | D      | 17      | GND         | М      | 2        | H8            | U      | 11      | VPLUSDOUT      |

| А      | 15       | A7               | D      | 18      | 10B         | М      | 3        | GND           | U      | 12      | VEE            |

| A      | 16       | A9               | D      | 19      | 10          | M      | 4        | GND           | U      | 13      | VPLUSDOUT      |

| A      | 17       | DEMUXDELADJCTRL  | E      | 1       | G6          | М      | 16       | GND           | U      | 14      | VPLUSDOUT      |

| A      | 18       | RSTSYNCB         | E      | 2       | G7          | М      | 17       | GND           | U      | 15      | VPLUSDOUT      |

| A      | 19       | NC               | E      | 3       | VPLUSDOUT   | M      | 18       | 17B           | U      | 16      | GND            |

| B      | 1        | E1               | E      | 4       | VEE         | M      | 19       | 17            | U      | 17      | GND            |

| B      | 2        | E2               | E      | 16      | VEE         | N      | 1        | H5            | U      | 18      | GND            |

| B      | 3        | E4               | E      | 17      | VEE         | N      | 2        | H6            | U      | 19      | GND            |

| B      | 4        | E6               | E<br>E | 18      | 11B         | N      | 3<br>4   | VPLUSDOUT     | V      | 1       | F7             |

| B      | 5        | E8<br>REFC       | F      | 19      | l1<br>G4    | N      | -        | VPLUSDOUT     | V      | 2       | F6             |

| B<br>B | 6<br>7   | C1               | F      | 1<br>2  | G5          | N<br>N | 16<br>17 | VEE           | V<br>V | 3<br>4  | F4<br>F2       |

| B      | 8        | C3               | F      | 2       | GND         | N      | 18       | I8B           | V      | 4<br>5  | F2<br>F0       |

| B      | 9        | C5               | F      | 4       | GND         | N      | 19       | 18            | V      | 6       | D9             |

| B      | 10       | C7               | F      | 16      | GND         | P      | 1        | H3            | v      | 7       | D3<br>D7       |

| В      | 11       | C9               | F      | 17      | GND         | P      | 2        | H4            | v      | 8       | D5             |

| В      | 12       | AO               | F      | 18      | I2B         | P      | 3        | GND           | v      | 9       | D3             |

| В      | 13       | A2               | F      | 19      | 12          | P      | 4        | GND           | v      | 10      | D1             |

| В      | 14       | A4               | G      | 1       | G2          | P      | 16       | GND           | V      | 11      | REFD           |

| В      | 15       | A6               | G      | 2       | G3          | Р      | 17       | GND           | V      | 12      | B8             |

| В      | 16       | A8               | G      | 3       | VEE         | Р      | 18       | 19B           | V      | 13      | B6             |

| В      | 17       | ASYNCRESET       | G      | 4       | VEE         | Р      | 19       | 19            | V      | 14      | B4             |

| В      | 18       | DEMUXDELADJCTRLB | G      | 16      | VEE         | R      | 1        | H1            | V      | 15      | B2             |

| В      | 19       | RSTSYNC          | G      | 17      | VEE         | R      | 2        | H2            | V      | 16      | B0             |

| С      | 1        | REFE             | G      | 18      | I3B         | R      | 3        | VPLUSDOUT     | V      | 17      | BIST           |

| С      | 2        | E0               | G      | 19      | 13          | R      | 4        | VPLUSDOUT     | V      | 18      | CLKINTYPE      |

| С      | 3        | VEE              | Н      | 1       | G0          | R      | 16       | VEE           | V      | 19      | ADCDELADJCTRL  |

| С      | 4        | VPLUSDOUT        | н      | 2       | G1          | R      | 17       | GND           | W      | 1       | NC             |

| С      | 5        | VPLUSDOUT        | Н      | 3       | GND         | R      | 18       | ADCDELADJOUT  | W      | 2       | F5             |

| С      | 6        | VPLUSDOUT        | Н      | 4       | GND         | R      | 19       | ADCDELADJOUTB | W      | 3       | F3             |

| С      | 7        | VPLUSDOUT        | Н      | 16      | GND         | T      | 1        | REFH          | W      | 4       | F1             |

| C      | 8        | VEE              | н      | 17      | GND         | T      | 2        | HO            | W      | 5       | REFF           |

| C      | 9        | VPLUSDOUT        | н      | 18      | CLKINB      | T      | 3        | VEE           | W      | 6       | D8             |

| C<br>C | 10       | VEE              | H<br>J | 19      | CLKIN<br>DR | T<br>T | 4<br>5   | VEE           | W      | 7       | D6<br>D4       |

| C      | 11<br>12 | VPLUSDOUT<br>VEE | J      | 1<br>2  | REFG        | T      | 5<br>6   | VEL           | W<br>W | 8<br>9  | D4<br>D2       |

| C      | 12       | VEL              | J      | 2       | VPLUSDOUT   | T      | 6<br>7   | VPLUSDOUT     | W      | 9<br>10 | D2<br>D0       |

| c      | 13       | VPLUSDOUT        | J      | 4       | VEC         | T      | 8        | VEE           | W      | 11      | B9             |

| c      | 14       | VPLUSDOUT        | J      | 4<br>16 | VEE         | T      | 9        | VEL           | W      | 12      | B7             |

| c      | 16       | GND              | J      | 17      | VEE         | T      | 10       | VEE           | W      | 13      | B5             |

| c      | 17       | GND              | J      | 18      | I4B         | T      | 11       | VPLUSDOUT     | Ŵ      | 14      | B3             |

| c      | 18       | GND              | J      | 19      | 14          | Ť      | 12       | VEE           | Ŵ      | 15      | B1             |

| c      | 19       | DIODE            | ĸ      | 1       | SWIADJ      | T      | 13       | VPLUSDOUT     | Ŵ      | 16      | REFB           |

| D      | 1        | G8               | ĸ      | 2       | DRB         | T      | 14       | VPLUSDOUT     | Ŵ      | 17      | NBBIT          |

| D      | 2        | G9               | ĸ      | 3       | VEE         | Ť      | 15       | GND           | W      | 18      | ADCDELADJCTRLB |

| D      | 3        | VEE              | K      | 4       | VEE         | Т      | 16       | VEE           | W      | 19      | NC             |

|        | -        | <u> </u>         |        |         | ļ           |        | · · •    | 1             | ļ      |         |                |

**MEL**

Figure 4. TBGA 240 Package: Bottom View

### Thermal and Moisture Characteristics

| Thermal Resistance<br>from Junction to<br>Case: RTHJC    | <ul> <li>The Rth from junction to case for the TBGA package is estimated at 0.7°C/W which can be decomposed in:</li> <li>Silicon: 0.1°C/W</li> <li>Die attach epoxy: 0.5°C/W (thickness # 50 μm)</li> <li>Copper block (back side of the package): 0.1°C/W.</li> </ul>                                  |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Thermal Resistance<br>from Junction to<br>Ambient: RTHJA | A pin-fin type heatsink, size 40 mm x 40 mm x 8 mm can be used to reduce thermal resis-<br>tance. This heatsink should not be glued on top of the package as Atmel does not guarantee<br>the attachment on the board in such a configuration. The heatsink could be clipped or screwed<br>on the board. |

|                                                          | With such a heatsink the Rthj-a is about 6°C/W. (If Atmel takes 10°C/W for Rth through the heatsink in parallel with 15°C/W for Rth through the balls).                                                                                                                                                 |

|                                                          | Without a heatsink, the Rth junction to air for a package reported on-board can be estimated from 13 to 20°C/W (depending on the board used).                                                                                                                                                           |

|                                                          | The worst value 20°C/W is given for 1-layer board (13°C for 4-layer board).                                                                                                                                                                                                                             |

| Temperature Diode                                        | The theoretical characteristic of the diode, in function of the temperature when $I = 3$ mA is                                                                                                                                                                                                          |

#### Moisture Characteristic

Characteristic

This device is sensitive to the moisture (MSL3 according JEDEC standard).

Shelf life in sealed bag: 12 months at < 40°C and < 90% relative humidity (RH).

After this bag is opened, devices that will be subjected to infrared reflow, vapor-phase reflow, or equivalent processing (peak package body temperature 220°C) must be:

- mounted within 168 hours at factory conditions of  $\leq$  30°C/60% RH, or

- stored at  $\leq$  20% RH.

depicted below.

Devices require baking, before mounting, if Humidity Indicator is > 20% when read at 23°C  $\pm$ 5°C.

If baking is required, devices may be baked for:

- 192 hours at 40°C + 5°C/-0°C and < 5% RH for low temperature device containers, or

- 24 hours at 125°C ± 5°C for high-temperature device containers.

## DC Characteristics and Current Consumption

In this section, the typical values of the board's I/O signals and power sources are listed. These values refer to a nominal use of the evaluation board. These values are purely indicative and may depend on temperature, frequency of use, etc.

The following tables give an estimation of the power consumption of the board, including the current consumption of DMUX and the current consumption induced by the components added on the board. The values given below are relevant for ECL 50 $\Omega$ , PECL 50 $\Omega$  and TTL 75 $\Omega$  output formats only, assuming that the DMUX is working in ratio 1:8, 10 bits. For further information about output formats, please also refer to "DMUX Settings Adjustment" on page 14.

| Parameter             | ECL 50Ω | PECL 50Ω | TTL 75Ω | Unit |

|-----------------------|---------|----------|---------|------|

| V <sub>cc</sub>       | 5       | 5        | 5       | V    |

| V <sub>PLUSDOUT</sub> | 0       | 3.3      | 3.3     | V    |

| V <sub>TT</sub>       | -2      | 1.3      | 0.25    | V    |

| V <sub>EE</sub>       | -5      | -5       | -5      | V    |

#### Table 4. Supply Voltage

### **Table 5.** Output Voltage (at T = 125°C)

| Parameter        | ECL 50Ω | PECL 50Ω | TTL 75Ω | Unit |

|------------------|---------|----------|---------|------|

| V <sub>OL</sub>  | -1.8    | 1.5      | 0.5     | V    |

| V <sub>PH</sub>  | -0.8    | 2.5      | 2.5     | V    |

| V <sub>REF</sub> | -1.3    | 2.0      | 1.5     | V    |

#### Table 6. Maximum Current Consumption

| Parameter             | ECL 50Ω<br>(SWIADJ = 0V) | PECL 50Ω<br>(SWIADJ = 0V) | TTL 75Ω<br>(SWIADJ = 0.5V) | Unit |

|-----------------------|--------------------------|---------------------------|----------------------------|------|

| I <sub>cc</sub>       | 40                       | 40                        | 40                         | mA   |

| I <sub>PLUSDOUT</sub> | 2200                     | 2200                      | 3010                       | mA   |

| I <sub>TT</sub>       | 1940                     | 1940                      | 2630                       | mA   |

| I <sub>EE</sub>       | 800                      | 800                       | 880                        | mA   |

## Absolute Maximum Ratings

The following table lists the absolute maximum values of the board. These maximum ratings are limiting values to be considered individually, while other parameters are within specified operating conditions. Long exposure to maximum ratings may affect the DMUX reliability.

| Parameter                                                  | Symbol                                                                                                      | Comments                                                       | Value                  | Unit |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------|------|

| Positive supply voltage                                    | V <sub>cc</sub>                                                                                             |                                                                | GND to 6               | V    |

| Positive output buffer supply voltage                      | V <sub>PLUSD</sub>                                                                                          |                                                                | GND to 4               | V    |

| Negative supply voltage                                    | V <sub>EE</sub>                                                                                             |                                                                | GND to -6              | V    |

| Analog input voltages                                      | ADCDelAdjCtrl,<br>ADCDelAdjCtrlb or<br>DMUXDelAdjCtrl,<br>DMUXDelAdjCtrlb or<br>SwiAdj                      | Voltage range for each<br>pad<br>Differential voltage<br>range | 0 to 1<br>-1 to 1      | V    |

| ECL 50Ω input voltage                                      | ClkIn or ClkInb or<br>I[09] or I[09]b or<br>SyncReset or<br>SyncResetb or<br>ADCDelAdjIn or<br>ADCDelAdjInb | Voltage range for each pad                                     | -2.2 to 0.6            | V    |

| Maximum difference between ECL $50\Omega$ input voltages   | ClkIn – ClkInb or<br>I[09] - I[09]b or<br>SyncReset –<br>Syncresetb or<br>ADCDelAdjIn -<br>ADCDelAdjInb     | Minimum differential<br>swing<br>Maximum differential<br>swing | 0.1<br>2               | V    |

| Data output current                                        | A[09] to H[09] or<br>RefA to RefH or<br>DR or DRb                                                           | Maximum current                                                | 36                     | mA   |

| TTL input voltages                                         | ClkIn Type<br>RatioSel<br>NbBit<br>AsyncReset<br>BIST                                                       |                                                                | GND to V <sub>CC</sub> | V    |

| Maximum input voltage on diode for temperature measurement | DIODE                                                                                                       |                                                                | 700                    | mV   |

| Maximum input current on diode                             | DIODE                                                                                                       |                                                                | 8                      | mA   |

| Maximum junction temperature                               | T <sub>j</sub>                                                                                              |                                                                | 135                    | °C   |

| Storage temperature                                        | T <sub>stg</sub>                                                                                            |                                                                | TBD                    | °C   |

Note: Absolute maximum ratings are limiting values, to be applied individually, while other parameters are within specified operating conditions. Long exposure to maximum rating may affect device reliability. The use of a thermal heat sink is mandatory.

# Main Function Description

Other function descriptions are available in the TS81102G0 DMUX datasheet.

### Quick Start

The evaluation board is delivered fully assembled and tested. A heatsink, which is strongly recommended, is also delivered assembled.

# Do not turn on the power supplies until all power connections to the evaluation board are established.

The procedure described below aims at helping when the board is used for the first time. It describes the steps to accomplish a BIST test (Built-In Self Test, see "Miscellaneous" on page 15) in order to verify whether the board is functional or not. At the end of the procedure, the DMUX will be in the following configuration: DR mode, 10 bits mode, 1:8 ratio, BIST activated, SWIADJ = 0V, ECL output format.

- 1. Connect the board's ground pads together.

- 2. Connect the pad marked V<sub>PLUSDOUT</sub> to the GND pad.

- 3. Connect a -5V power supply source to the pad marked  $V_{\text{EE}}$ . Then, connect the supply's ground to the GND pad.

- 4. Connect a +5V power supply source to the pad marked  $V_{CC}$ . Then, connect the supply's ground to the GND pad.

- 5. Connect a -2V power supply source to the pad marked  $V_{TT}$ . Then, connect the supply's ground to the GND pad.

- 6. Connect your input clock to the board (pitches CLKIN and CLKINB). This clock may either be differential or single-ended (see "BIST" on page 14).

- 7. Remove the jumpers marked NBBIT and CLKINTYPE. The remaining jumpers are RATIOSEL and BIST.

- 8. Connect a logic analyzer, such as an HP16500 at the output of the board.

- 9. Turn on the supply and signal sources according to the following sequence:

- V<sub>EE</sub> first

- V<sub>CC</sub>

- V<sub>PLUSDOUT</sub>

- V<sub>tt</sub>

- Input clock

- 10. Set the potentiometer marked SWIADJ such that the voltage on the SWIADJ pin of the DMUX is 0V.

- 11. Connect pad ASYNCRESET to ground (the ASYNCHRESET is active at TTL high level and must be tied to ground when the device is running).

At the output, the demultiplexed BIST sequence shall be observed.

Note: It is not necessary to verify the 512 codes of the BIST to make sure that the DMUX is functional. Verifying the first 16 codes is indeed sufficient.

### DMUX Settings Adjustment

Four jumpers are provided in order to activate the functions RATIOSEL, BIST, CLKINTYPE and NBBIT. When the jumper is on-board, it corresponds to logic 0. The following table recapitulates which functions are active when the jumpers are on-board or not.

#### Table 8. DUMX Settings Adjustment

| Name      | Jumper | Function        |

|-----------|--------|-----------------|

| CLKINTYPE | ON     | DR/2 mode       |

|           | OUT    | DR mode         |

| BIST      | ON     | BIST active     |

|           | OUT    | BIST inactive   |

| NBBIT     | ON     | 8 bits mode     |

|           | OUT    | 10 bits mode    |

| RATIOSEL  | ON     | 1:8 DMUX Ration |

|           | OUT    | 1:8 DMUX Ration |

**BIST** A pseudo-random 10-bit generator is implemented in the DMUX. It generates a 10 bits signal at the output of the DMUX, with a period of 512 input clock's periods. The sequence start on port A. The output obtained on port A to H depends on the conversion ratio. The driving clock of BIST is ClkIn. CLKINTYPE must be set to logic 1 (jumper out) to have different 10-bit code on each output. The complete BIST sequence is available on request.

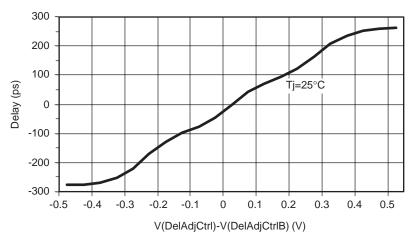

**Delay Adjust** Two delay adjusts of ±250 ps, controlled by potentiometers, are available in order to synchronize the input clock and data of the DMUX on the one hand, and to delay the signal ADCDELADJIN on the other hand. The input DelAdjCtrl has been set to 0V. The input DelAdjCtrlb varies from -0.55V to 0.55V, according to the potentiometer position. The generated delay is proportional to the differential voltage V(DelAdjCtrl)–V(DelAdjCtrlb) as shown in the next graph.

### Figure 6. Delay Adjustment Characteristic

Note: The variation of the delay in function of the temperature is insignificant.

### **Miscellaneous**

- Always wear an anti-static strap when manipulating the board, the DMUX being very sensitive to ESDs.

- Make sure that the current as delivered by your power supplies is sufficient to supply the board.

- Always switch on the DMUX board supplies in the following order:  $V_{\text{PLUSDOUT}}$  first,  $V_{\text{EE}},$   $V_{\text{CC}},$   $V_{\text{TT}}.$

- Always make sure that the output current through the termination resistors does not exceed 36 mA.

- After the supplies are switched on, send an asynchronous reset pulse into the DMUX (i.e. leave the pad ASYNCRESET open and then connect it to the ground).

Evaluation Board Schematics

Figure 7. Component Side

Figure 9. Power Supplies Plane

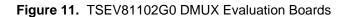

### TSEV81102G0TPZR3 Electric Schematic

Figure 10. TSEV81102G0TPZR3 Electric Schematic

# 18 TSEV81102G0TPZR3

|                                       | RADIALL R125 620 001         | 4  | J10, J11, J19, J20                                                                                                                                                                                                           |

|---------------------------------------|------------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BANANA JACK 4 mm                      | DELTRON                      | 6  | J21 to J26                                                                                                                                                                                                                   |

|                                       | E. F. JOHNSON                | 4  | J15 to J18                                                                                                                                                                                                                   |

| SUBVIS<br>CONNECTOR                   | RADIALL R112 665             | 1  | J14                                                                                                                                                                                                                          |

| PITCH CONNECTOR<br>2.54 mm (two rows) | -                            | 5  | J1 to J5                                                                                                                                                                                                                     |

| CAPACITOR                             | CHIP TANTALE 1 uF, 20V       | 4  | C1 to C4                                                                                                                                                                                                                     |

|                                       | CHIP Ceramic 100 nF          | 4  | C5 to C8                                                                                                                                                                                                                     |

|                                       | CHIP Ceramic 10 nF           | 39 | C9, C11, C13, C15, C17, C19,<br>C21, C23, C25, C27, C29, C31,<br>C33, C35, C37, C39, C41, C43,<br>C45, C47, C49, C51, C53, C55,<br>C57, C59, C61, C63, C65, C67,<br>C69, C71, C73, C75, C77, C79,<br>C81, C83, C85, C87, C88 |

|                                       | Ceramic 10 nF                | 39 | C10, C12, C14, C16, C18, C20,<br>C22, C24, C26, C28, C30, C32,<br>C34, C36, C38, C40, C42, C44,<br>C46, C48, C50, C52, C54, C56,<br>C58, C60, C62, C64, C66, C68,<br>C70, C72, C74, C76, C78, C80,<br>C82, C84, C86          |

| RESISTOR                              | CHIP 5 KΩ 1%                 | 2  | R1, R2                                                                                                                                                                                                                       |

|                                       | CHIP 4 KΩ 1%                 | 4  | R5, R6, R9, R10                                                                                                                                                                                                              |

|                                       | CHIP 2.5 KΩ 1%               | 2  | R3, R4, R7, R8                                                                                                                                                                                                               |

|                                       | CHIP 2 KΩ 1%                 | 2  | R101, R102                                                                                                                                                                                                                   |

|                                       | CHIP 50Ω 1%                  | 90 | R11 to R100                                                                                                                                                                                                                  |

| POTENTIOMETER                         | BOURNS 2 K $\Omega$ 25 turns | 1  | P1                                                                                                                                                                                                                           |

|                                       | BOURNS 1 K $\Omega$ 25 turns | 2  | P2, P3                                                                                                                                                                                                                       |

| DIODE                                 | -                            | 6  | D1 to D6                                                                                                                                                                                                                     |

| DMUX                                  | TS81102G0                    | 1  | U1                                                                                                                                                                                                                           |

Quantity

2

Label

J12, J13

### Table 9. Component List

SMA CONNECTOR

Туре

**Component List**

VITELEC 142 - 0701 - 851

Reference

## Applying the TSEV81102G0 DMUX

The TSEV81102G0 DMUX evaluation board has been designed to be connected with TSEV8388G and TSEV83102G0 ADC evaluation boards.

Please, refer to the specific document "DMUX and ADC APPLICATION NOTES" for more information.

### ADC to DMUX Connections

The DMUX inputs configuration has been optimized to be connected to the TS8388B ADC.

The die in the TBGA package is up. For the ADC, different types of packages can be used such as CBGA with die up or the CQFP68 with die down. The DMUX device being completely symmetrical, both ADC packages can be connected to the TBGA package of the DMUX without crisscrossing the lines (see table below).

| ADC Digital Outputs<br>CQFP68 Package | DMUX Data Inputs<br>TBGA Package | ADC Digital Outputs<br>CBGA Package | DMUX Data Inputs<br>TBGA Package |

|---------------------------------------|----------------------------------|-------------------------------------|----------------------------------|

| D0                                    | 17                               | D0                                  | 10                               |

| D1                                    | 16                               | D1                                  | l1                               |

| D2                                    | 15                               | D2                                  | 12                               |

| D3                                    | 14                               | D3                                  | 13                               |

| D4                                    | 13                               | D4                                  | 14                               |

| D5                                    | 12                               | D5                                  | 15                               |

| D6                                    | l1                               | D6                                  | 16                               |

| D7                                    | 10                               | D7                                  | 17                               |

| -                                     | 18 not connected                 | -                                   | 18 not connected                 |

| -                                     | 19 not connected                 | -                                   | 19 not connected                 |

Table 10. ADC to DMUX Connections

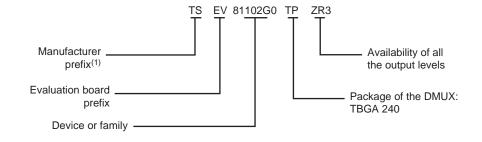

# Ordering Information

### **Evaluation Board**

Note: 1. For availability of the different versions, contact your ATMEL sale office.

The board includes the bonded package and the heatsink.

### Datasheet Status Description

### Table 11. Datasheet Status

| Datasheet Status                                         |                                                                                                                                                                                                          | Validity                                                         |  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| Objective specification                                  | This datasheet contains target and goal specifications for discussion with customer and application validation.                                                                                          | Before design phase                                              |  |

| Target specification                                     | This datasheet contains target or goal specifications for product development.                                                                                                                           | Valid during the design phase                                    |  |

| Preliminary specification $\alpha$ -site                 | This datasheet contains preliminary<br>data. Additional data may be<br>published later; could include<br>simulation results.                                                                             | Valid before characterization phase                              |  |

| Preliminary specification<br>β-site                      | This datasheet contains also characterization results.                                                                                                                                                   | Valid before the industrialization phase                         |  |

| Product specification                                    | This datasheet contains final product specification.                                                                                                                                                     | Valid for production purposes                                    |  |

| Limiting Values                                          |                                                                                                                                                                                                          |                                                                  |  |

| above one or more of the linstress ratings only and open | accordance with the Absolute Maximum<br>miting values may cause permanent dam<br>ration of the device at these or at any othe<br>s of the specification is not implied. Expose<br>ct device reliability. | hage to the device. These are er conditions above those given in |  |

| Application Information                                  |                                                                                                                                                                                                          |                                                                  |  |

| Where application informat                               | ion is given, it is advisory and does not fo                                                                                                                                                             | orm part of the specification.                                   |  |

### Life Support Applications

These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Atmel customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Atmel for any damages resulting from such improper use or sale.

### **Atmel Headquarters**

#### **Corporate Headquarters**

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

### **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

# Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

### e-mail

literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL® is the registered trademark of Atmel.

Other terms and product names may be the trademarks of others.

Printed on recycled paper.