# MC68160B MC68160C

# **Enhanced Ethernet Transceiver**

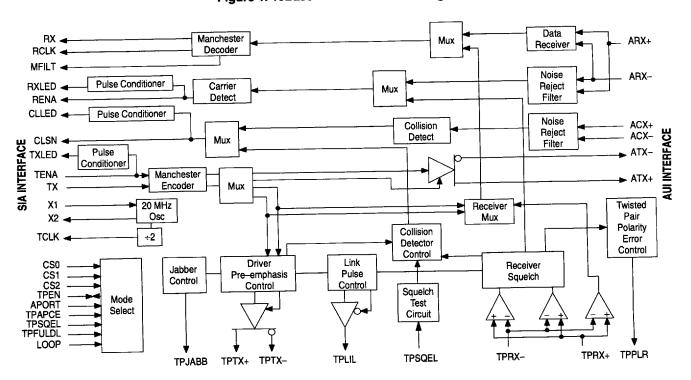

The MC68160, B and C Enhanced Ethernet Interface Circuit is a BiCMOS device which supports both IEEE 802.3\* Access Unit Interface (AUI) and 10BASE—T Twisted Pair (TP) Interface media connections through external isolation transformers. It encodes NRZ data to Manchester data and supplies the signals which are required for data communication via 10BASE—T or AUI interfaces. The MC68160, B and C gluelessly interface to the Ethernet controller contained in the MC68360 Quad Integrated Communications Controller (QUICC) device. The MC68160 also interfaces easily to most other industry—standard IEEE 802.3 LAN controllers.\*\* Prior to twisted pair data reception, Smart Squelch circuitry qualifies input signals for correct amplitude, pulse width, and sequence requirements.

- Automatic Twisted Pair Wiring Polarity Fault Detection and Correction Option

- Automatic Port Selection Option with Status Output

- Driver Pre-emphasis for Twisted Pair Output Data

- Crystal Controlled Clock Oscillator or External Clock Generator Option

- Digital Phase-Locked-Loop (DPLL) Timing Recovery and Data Decoding

- Standby Mode with Reduced Power Consumption

- Twisted Pair Signal Quality Error (Heartbeat) Test Option

- Diagnostic Local Loop Back Option

- Transmit, Receive and Collision Detection Status Output

- Full-Duplex Operation Option on Twisted Pair Port

- Twisted Pair Jabber Detection and Status Output

- Link Integrity Testing and Status Output

- MC68160B does not support all IEEE 802.3 specifications over extended temperature range. Exceptions noted in specifications.

- \*\* MC68160B, C only support Motorola controllers

The sale and use of this product is licensed under technology covered by one or more Digital Equipment Corporation patents.

# ENHANCED ETHERNET INTERFACE TRANSCEIVER

SEMICONDUCTOR TECHNICAL DATA

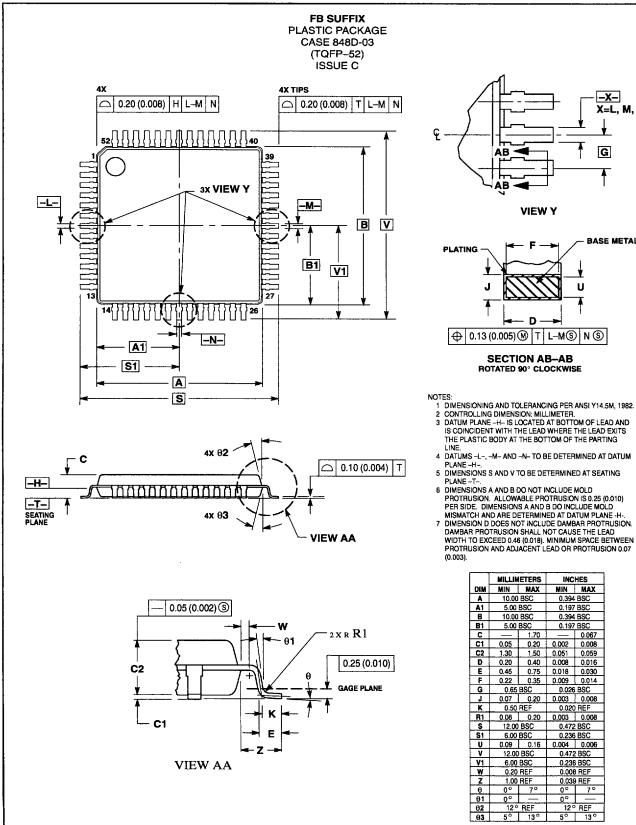

FB SUFFIX

PLASTIC PACKAGE

CASE 848D

(TQFP-52)

# ORDERING INFORMATION

|            | LUING INFORMATI                 | UN      |

|------------|---------------------------------|---------|

| Device     | Operating<br>Temperature Range  | Package |

| MC68160FB  | Ta = 0% to = 7000               | TQFP-52 |

| MC68160CFB | T <sub>A</sub> = 0° to + 70°C   | TQFP-52 |

| MC68160BFB | T <sub>A</sub> = -40° to + 85°C | TQFP-52 |

© Motorola, Inc. 1997

Rev 1

Figure 1. 10Base-T Interface Block Diagram

This device contains 20,000 active transistors.

# MC68160 MC68160B MC68160C Enhanced Ethernet Serial Transceiver

| Table 1. Pin Descriptions  Controller Interface Pins  AUI Interface Pins  Twisted Pair Interface Pins  Oscillator and Frequency Multiplier Pins  Mode Select Pins  Status Indicator Pins  Power Supply and Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4 4 5 5 6 6 6                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Table 2. Controller Interface Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7                                                                          |

| Table 3. Controller Independent Mode Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7                                                                          |

| Electrical Characteristics  Maximum Ratings  Recommended Operating Conditions  ESD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                                                                          |

| Power Supply DC Characteristics TTL/CMOS Input and Output DC Characteristics Twisted Pair Input and Output DC Characteristics AUI Input and Output DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9                                                                          |

| External Clock Input (X1) Switching Characteristics Receive Phase Locked Loop Switching Characteristics Controller Transmit Switching Characteristics (Motorola Mode) Controller Receive Switching Characteristics (Motorola Mode) Controller Transmit Switching Characteristics (Intel Mode) Controller Receive Switching Characteristics (Intel Mode) Controller Transmit Switching Characteristics (Intel Mode) Controller Receive Switching Characteristics (Fujitsu Mode) Controller Receive Switching Characteristics (Fujitsu Mode) Controller Receive Switching Characteristics (National Mode) Controller Receive Switching Characteristics (National Mode) TP Transmit Switching Characteristics (National Mode) TP Transmit Jabber Switching Characteristics TP Transmit Signal Quality Error Test Switching Characteristics TP Receive Switching Characteristics TP Receive Switching Characteristics TP Collision Switching Characteristics TP Full Duplex Switching Characteristics AUI Transmit Switching Characteristics AUI Transmit Switching Characteristics AUI Receive Switching Characteristics | 12<br>12<br>12<br>14<br>14<br>15<br>16<br>16<br>18<br>20<br>21<br>23<br>23 |

| Functional Description  Data Transmission  Data Reception  Collision  Jabber  Full Duplex  Auto Port Selection  Auto Polarity Selection  Loop Back Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25<br>26<br>26<br>26<br>26<br>26<br>26                                     |

| Applications Selection of Crystal and External Components PLL Filter Components 10BASE-T Filter and Transformer Choice AUI Transformer Choice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27<br>27<br>27                                                             |

**Table 1. Pin Function Descriptiont**

| Pin(s)    | Symbol         | Туре          | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ONTROLL   | ER INTERFA     | CE            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

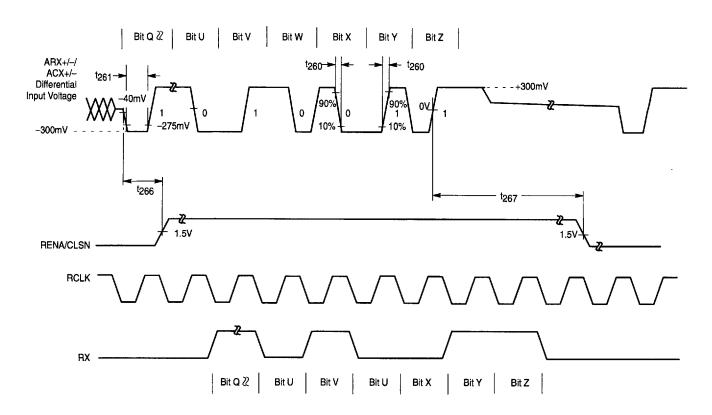

| 1         | RENA           | O<br>TTL/CMO  | Receive Enable Output: Indication of the presence of network activity, synchronous to RCLK. In the standby mode, RENA is driven to the high impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2         | RX             | O<br>TTL/CMOS | Receive Data Output: Recovered data, synchronous to RCLK. Following a reset operation, 100 ms should be allowed before attempting to read data processed by the MC68160, B and C. This delay is needed to insure that the receive phase locked loop is properly synchronize with incoming data. In the standby mode, RX is driven to the high impedance state.                                                                                                                                                                                                                              |

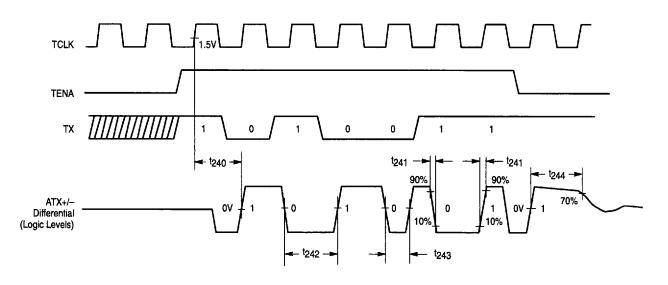

| 48        | TCLK           | O<br>TTL/CMOS | Transmit Clock Output CMOS/TTL Output: TCLK provides a symmetrical clock signal at 10 MHz for reference timing of data to be encoded. In the standby mode, TCLK is driven to the high impedance state.                                                                                                                                                                                                                                                                                                                                                                                      |

| 49        | TENA           | I<br>TTL      | Transmit Enable Input: Input signal synchronous to TCLK which enables data transmission on the active port. An internal pull—down resistor is provided so that the input is low under no connect conditions. (This resistor is removed in the standby mode). If TENA is asserted at the conclusion of a reset operation, it must first be deasserted and then reasserted before data transmission can occur. In the standby mode, TENA is driven to the high impedance state.                                                                                                               |

| 50        | RCLK           | O<br>TTL/CMOS | <b>Receive Clock Output:</b> Recovered clock. In the standby mode, RCLK is driven to the high impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

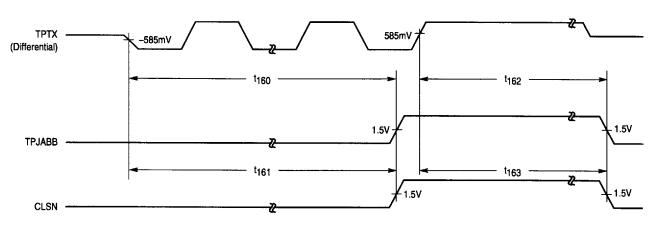

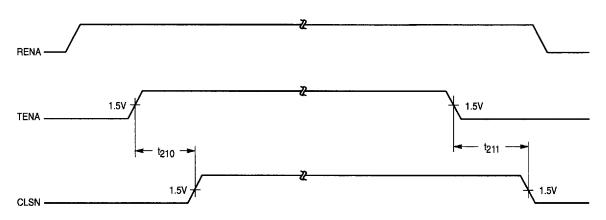

| 51        | CLSN           | O<br>TTL/CMOS | <b>Collision Output:</b> In the AUI mode, indicates the presence of signals at the ACX+ and ACX- terminals which meet threshold and pulse width requirements. In the TP mode, indicates simultaneous transmit and receive activity, a heartbeat (SQE Test) signal was generated, or the jabber timer has expired. In the standby mode, CLSN is driven to the high impedance state.                                                                                                                                                                                                          |

| 52        | TX             | I<br>TTL      | <b>Transmit Data Input:</b> Input signal synchronous to TCLK which provides NRZ serial data to be Manchester encoded. In the standby mode, TX is driven to the high impedance state.                                                                                                                                                                                                                                                                                                                                                                                                        |

| UI INTERF | ACE            |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 21<br>22  | ACX-<br>ACX+   | I             | <b>AUI Differential Collision Inputs:</b> These inputs are connected to a pair of internally biased line receivers consisting of a carrier detect receiver with offset threshold and noise filtering detect the line activity. Signals at ACX+/– have no effect on data path functions.                                                                                                                                                                                                                                                                                                     |

| 23<br>24  | ARX-<br>ARX+   | ı             | <b>AUI Differential Receiver Inputs:</b> These inputs are connected to a pair of internally biased line receivers consisting of a carrier detect receiver with offset threshold and noise filtering detect the line activity, and a data receiver with no offset for Manchester Data reception.                                                                                                                                                                                                                                                                                             |

| 25<br>26  | ATX-<br>ATX+   | 0             | <b>AUI Differential Transmit Outputs :</b> This line pair is intended to operate into terminated transmission lines. For TX signals meeting setup and hold time to TCLK when TENA is previously asserted, Manchester encoded data is outputted at ATX+/–. When operating into a 78 $\Omega$ terminated transmission line, signaling meets the required output levels and skew for IEEE–802.3 drop cables. When the 10BASE–T port is automatically or manually selected, the AUI outputs are driven to a low power standby state in which the outputs deliver a balanced high state voltage. |

| WISTED F  | AIR INTERF     | ACE           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

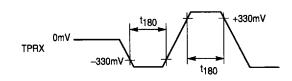

| 31<br>32  | TPRX-<br>TPRX+ | I             | Twisted Pair Differential Receiver Inputs: These inputs are connected to a receiver with Smart Squelch capability which only allows differential receive data to pass as long as the input amplitude is greater than a minimum signal threshold level and a specific pulse sequence is received. This assures a good signal to noise ratio while the signal pair is actiby preventing crosstalk and impulse noise conditions from activating the receive function.                                                                                                                          |

| 36<br>37  | TPTX-<br>TPTX+ | 0             | Twisted Pair Differential Transmitter Outputs: These lines have pre—distortion drive capability and are intended to drive terminated twisted pair transmission lines. When the A port is manually selected, the 10BASE—T outputs are driven to a low power standby state which the outputs deliver a balanced high state voltage. However, when the AUI port is automatically selected, the 10BASE—T outputs remain active.                                                                                                                                                                 |

NOTE: The sense of the controller interface pins will change, depending on the controller selected.

**■** 6367253 0102995 863 **■** <sup>-</sup>

Table 1. Pin Function Description (continued)

| Pin(s)      | Symbol            | Туре                     | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | OR AND FREG       |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12          | MFILT             | C                        | Frequency Multiplier Filter Connection Point: An external resistor capacitor filter must be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | 1411 1.2.1        |                          | attached to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

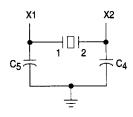

| 16          | X1                | I/C<br>CMOS              | Oscillator Inverter Input and Crystal Connection Point: When connected for crystal oscillator operation, the frequency of the clock which appears at TCLK is half that of the crystal oscillator. As an option, instead of connecting to a crystal, X1 may be driven from an external 20 MHz CMOS compatible clock generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 17          | X2                | O/C<br>CMOS              | Oscillator Inverter Output and Crystal Connection Point: This pin is used only for the connection of an external crystal and capacitor. It must be left unconnected if X1 is driven by an external CMOS Clock generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MODE SEL    | ECT               |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3<br>4<br>5 | CS0<br>CS1<br>CS2 | I<br>TTL                 | <b>Mode Select:</b> The logic states applied to these pins select the appropriate interface for the desired IEEE–802.3 controller or enable the standby mode. When the standby mode is selected, the MC68160, B and C power supply current is greatly reduced. Additionally, in the standby mode, all of the controller inputs and outputs are driven to the high impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6           | LOOP              | I<br>TTL                 | Diagnostic Loopback: Asserting this function causes serial NRZ data at the TX input to be Manchester encoded and then looped back through the Manchester decoder, appearing at the RX output. This diagnostic loopback function operates independent of Twisted Pair (TP) or Access Unit Interface (AUI) port connectivity or activity. Neither the TP port nor the AUI port transmits data from the controller while diagnostic loopback is selected. Likewise, the controller interface receives data neither from the TP nor the AUI receivers while in this mode. The polarity fault detection and link integrity functions are not inhibited by the diagnostic loopback mode. If otherwise enabled, they continue to function. If the twisted pair port is selected, and TPSQEL is driven to the low logic state, a collision detect pulse is delivered following each transmission to simulate the twisted pair SQE test. |

| 9           | APORT             | TTL                      | Automatic Port Selection Enable: When high, MC68160, B and C will automatically select the TP or AUI port based on the presence or absence of valid link beats or frames at the TP receive input. If the AUI port is automatically selected, the MC68160, B and C will continue to produce link pulses for the TP port. Changing ports requires approximately 1.0 ms to allow the circuitry for the new port to resume normal operation. The power consumption is minimized in the circuitry associated with the unselected port.                                                                                                                                                                                                                                                                                                                                                                                               |

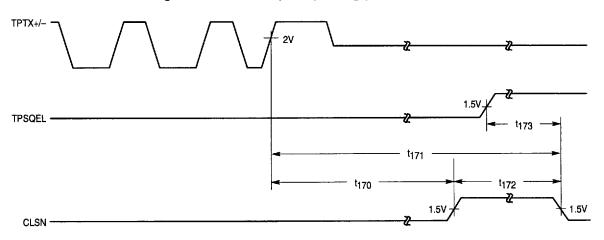

| 27          | TPSQEL            | TTL                      | Twisted Pair Signal Quality Error Test Enable: Forcing this pin low enables testing of the internal TP collision detect circuitry after each transmit operation to the TP media. This function provides a simulated collision to as much of the MC68160, B and C collision detect circuitry as possible without affecting the attached twisted pair channel. A normal SQE test results in a high logic state at the CLSN controller interface pin which begins 6 to 16—bit times after the last transition of a transmitted signal and continues for 5 to 15—bit times. (When the AUI port is selected, SQE test signals are generated by the coaxial cable transceiver and delivered to the controller via the MC68160, B and C ACX+/- receive inputs)                                                                                                                                                                         |

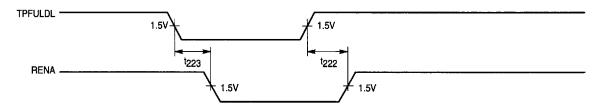

| 28          | TPFULDL           | TTL                      | Twisted Pair Full Duplex Mode Select: Forcing this pin low allows simultaneous transmit and receive operation on the twisted pair port without an indicated collision. This pin is not to be asserted with LOOP as a test mode is enabled that disrupts normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 29          | TPAPCE            | I<br>TTL                 | Twisted Pair Automatic Polarity Correction Enable: When TPAPCE is high, automatic polarity correction is enabled, and MC68160, B and C will internally correct for a polarity fault on the receive circuit. Additionally, when TPAPCE is high, the presence of a polarity fault is indicated on TPPLR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 46          | TPEN              | I/O<br>TTL<br>(TTL/CMOS) | Twisted Pair Port Enable: If APORT is low, TPEN is an input which determines whether the AUI port (TPEN low) or TP port (TPEN high) will be manually selected. If the AUI port is manually selected, the MC68160, B and C will not produce link pulses for the TP port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                   |                          | If APORT is high, TPEN is an output which will indicate which port has been automatically selected by driving TPEN low (for AUI) or high (for TP). In its output mode TPEN can sink 10 mA in the low output state and source 10 mA in the high output state. (See Pin 9 Description.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |                   |                          | Changing ports requires approximately 1.0 ms to allow the circuitry for the new port to resume normal operation. The power consumption is minimized in the circuitry associated with the unselected port. In the standby mode, this pin is driven to the high impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

■ 6367253 0102996 7TT **■**

**Table 1. Pin Function Description (continued)**

| Pin(s)     | Symbol  | Туре          | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|---------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATUS INI | DICATOR |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 40         | TXLED   | O<br>TTL/CMOS | Transmit Status LED Driver Output: This pin indicates the transmit status of the currently selected TP or AUI port. When there is no transmit activity detected, an internal pull—up takes this pin to its normal off (high) state. When transmit activity is detected, the LED driver turns on. In its on state, TXLED flashes the LED by driving low at approximately 10 Hz at a 50% duty cycle. In the standby mode, this output is driven to the high impedance state.                                                                                                         |

| 41         | RXLED   | O<br>TTL/CMOS | Receive Status LED Driver Output: This pin indicates the receive status of the currently selected TP or AUI port. When there is no receive activity detected, an internal pull—up takes this pin to its normal off (high) state. When receive activity is detected, the LED driver turns on. In its on state, RXLED flashes the LED by driving low at approximately 10 Hz at a 50% duty cycle. In the standby mode, this output is driven to the high impedance state.                                                                                                             |

| 42         | CLLED   | O<br>TTL/CMOS | Collision Status LED Driver Output: This pin indicates the collision status of the currently selected TP or AUI port. When there is no collision activity detected, an internal pull—up takes this pin to its normal off (high) state. When collision activity is detected, the LED driver turns on. In its on state, CLLED flashes the LED by driving low at approximately 10 Hz at a 50% duty cycle. In the standby mode, this output is driven to the high impedance state.                                                                                                     |

| 43         | TPLIL   | O<br>TTL/CMOS | Twisted Pair Link Integrity Output: This output is driven to the low output state to indicate good link integrity on the TP port during TP mode. It is deasserted (high) when link integrity fails in TP mode. The TPLIL output is driven to the high impedance state when the AUI port is selected. In the standby mode, this output is also driven to the high impedance state.                                                                                                                                                                                                  |

| 44         | TPPLR   | O<br>TTL/CMOS | Twisted Pair Polarity Error Output: If TPAPCE is high and the wires connected to the Twisted Pair Receiver Inputs (TPRX+, TPRX-) are reversed, TPPLR will be driven to the low logic state to indicate the fault. TPPLR remains low when the MC68160, B and C has automatically corrected for the reversed wires. If the twisted pair link integrity tests fail, this output will be driven to the high logic state. When the AUI mode is selected this output is driven to the high impedance state. In the standby mode, this output is also driven to the high impedance state. |

| 45         | TPJABB  | O<br>TTL/CMOS | Twisted Pair Jabber Output: This pin is driven high to indicate a jabber condition at the TPTX+/- outputs. (Jabber condition also causes CLLED to be driven alternately to the high and low output levels). TPJABB is driven to the low output state when no jabber condition is present. When the AUI mode is selected this output is driven to the high impedance state. In the standby mode, this output is also driven to the high impedance state.                                                                                                                            |

## **POWER SUPPLY AND GROUND**

| 10                   | VDDDIV                               | Frequency Divider Supply Pin                         |

|----------------------|--------------------------------------|------------------------------------------------------|

| 11<br>13             | VDDFM<br>GNDFM                       | Frequency Multiplier Supply and Ground Pins          |

| 14<br>15             | GNDVCO<br>VDDVCO                     | Voltage Controlled Oscillator Ground and Supply Pins |

| 20                   | GNDSUB                               | Substrate Ground Pin                                 |

| 7<br>8<br>18<br>19   | VDDDIG<br>GNDDIG<br>VDDDIG<br>GNDDIG | Digital Supply and Ground Pins                       |

| 30<br>33             | VDDANA<br>GNDANA                     | Analog Supply and Ground Pins                        |

| 34<br>35<br>38<br>39 | GNDPWR<br>VDDPWR<br>VDDPWR<br>GNDPWR | Power Supply and Ground Pins                         |

| 47                   | GNDCTL                               | Controller Interface Ground Pin                      |

NOTE: Power and ground pins are not connected internally. Failure to connect externally may cause malfunction or damage to the IC.

- 📟 6367253 0102997 636 📰

**Table 2. Controller Interface Selection**

| Motorola Transceiver MC68160, B and C (EEST™)  CS0 CS1 CS2 | Motorola<br>Controller <sup>2</sup><br>MC68360<br>(QUICC™) |       | Contr<br>82586, | rel <sup>4</sup><br>rollers<br>82590,<br>, 82596 | Fujitsu <sup>4</sup><br>Controllers<br>86950 (Etherstar™)<br>86960 (NICE™) |       | Cont.<br>8390, 8 | onal <sup>4</sup><br>rollers<br>33C690,<br>(SONIC™) |

|------------------------------------------------------------|------------------------------------------------------------|-------|-----------------|--------------------------------------------------|----------------------------------------------------------------------------|-------|------------------|-----------------------------------------------------|

|                                                            |                                                            |       | 0<br>1<br>0     |                                                  | 1<br>0<br>0                                                                |       |                  | 0<br>0<br>0                                         |

| Pin                                                        | Pin                                                        | Sense | Pin             | Sense                                            | Pin                                                                        | Sense | Pin              | Sense                                               |

| TCLK                                                       | TCLK                                                       | High  | TXC             | Low                                              | TCKN                                                                       | Low   | TXC              | High                                                |

| TX                                                         | TX                                                         | High  | TXD             | High                                             | TXD                                                                        | High  | TXD              | High                                                |

| TENA                                                       | TENA                                                       | High  | RTS             | Low                                              | TEN                                                                        | High  | TXE              | High                                                |

| RCLK                                                       | RCLK                                                       | High  | RXC             | Low                                              | RCN                                                                        | Low   | RXC              | High                                                |

| RX                                                         | RX                                                         | High  | RXD             | High                                             | RXD                                                                        | High  | RXD              | High                                                |

| RENA                                                       | RENA                                                       | High  | CRS             | Low                                              | XCD                                                                        | High  | CRS              | High                                                |

| CLSN                                                       | CLSN                                                       | High  | CDT             | Low                                              | XCOL                                                                       | Low   | COL              | High                                                |

| LOOP1                                                      | N.A.                                                       | High  | LPBK            | Low                                              | LBC                                                                        | High  | LPBK             | High                                                |

NOTES: 1. Although LOOP input is not ordinarily classifed as a controller pin, it is included in this table because its sense varies according to the controller used.

- 2. The Motorola controller interface contained in the MC68360 (QUICC™) is compatible with the AMD 7990 (LANCE™) and 79C900 (ILACC™) controllers.

- 3. The pin sense is shown from the perspective of the identified controller pin.

4. Supported only by MC68160.

**Table 3. Controller Independent Mode Selection**

| Pin | Standby Mode | Reserved | Reserved | Reserved |

|-----|--------------|----------|----------|----------|

| CS0 | 1            | 0        | 1        | 0        |

| CS1 | 1            | 1        | l o      | 0        |

| CS2 | 1            | 1        | 1        | 1        |

NOTE: In standby mode, the MC68160, B, C consumes less power supply current than in any other mode. Additionally, in the standby mode, all of the controller inputs and outputs are driven to the high impedance state. When the standby mode is deasserted, an internal reset pulse of approximately 6.0 μs duration is generated.

Following a period of operation in the standby mode, the time required to insure stable data reception is approximately 100 ms.

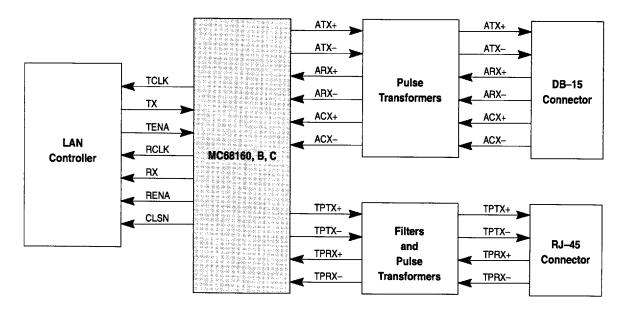

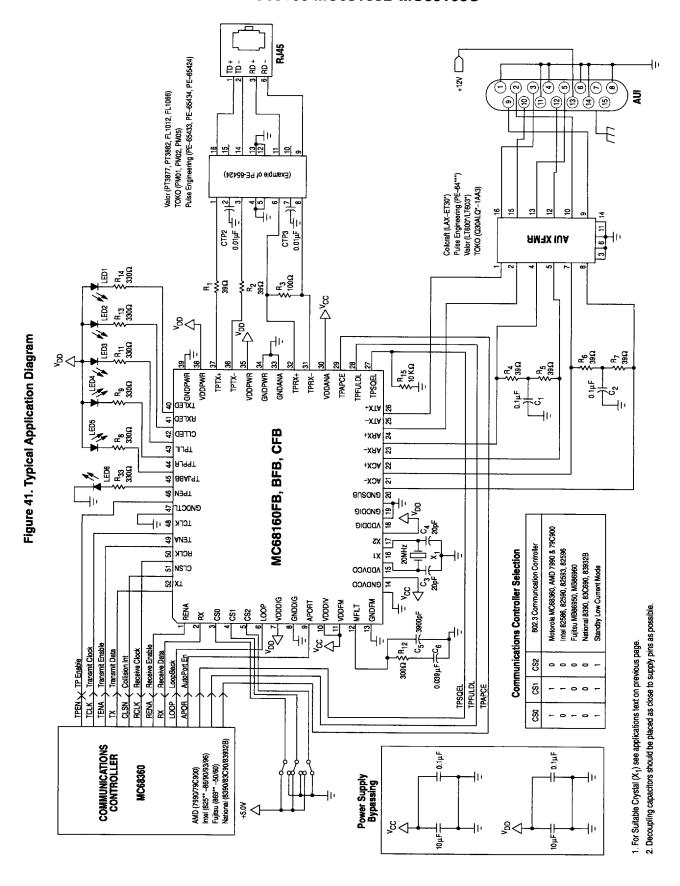

Figure 2. Applications Block Diagram

**MOTOROLA ANALOG IC DEVICE DATA**

**■** 6367253 0102998 572 **■**

# MC68160 MC68160B MC68160C ELECTRICAL CHARACTERISTICS

#### **MAXIMUM RATINGS**

| Characteristic                                                                                                                | Symbol                               | Min          | Max                          | Unit |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------|------------------------------|------|

| Storage Temperature Range                                                                                                     | T <sub>stg</sub>                     | -65          | 150                          | °C   |

| Power Supply Voltage Range<br>Analog<br>Digital                                                                               | V <sub>DDA</sub><br>V <sub>DDD</sub> | -<br>-       | 7.0<br>7.0                   | V    |

| Voltage on any TTL compatible input pin with respect to Ground Voltage on TPRX, ARX, or ACX input pins with respect to Ground | V                                    | -0.5<br>-0.5 | V <sub>DD</sub> + 0.5<br>6.0 | V    |

| Differential Voltage on TPRX, ARX, or ACX Input Pins                                                                          | VDIFF                                | -6.0         | 6.0                          | ٧    |

NOTE: Stresses in excess of the Absolute Maximum Ratings can cause permanent damage to the device. Functional operation of the device is not implied at these or any other conditions in excess of those indicated in the operation sections of this data sheet. Exposure to Absolute Maximum Ratings conditions for extended periods can adversely affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

| Characteristic                                                | Symbol           | Min             | Max  | Unit |

|---------------------------------------------------------------|------------------|-----------------|------|------|

| Power Supply Voltage Range                                    | V <sub>DD</sub>  | 4.75            | 5.25 | V    |

| Power Supply Ripple (20 kHz to 100 kHz)                       | _                | _               | 50   | mV   |

| Power Supply Impulse Noise (Either Polarity)                  | _                | _               | 100  | mV   |

| Ambient Operating Temperature Range (MC68160, MC68160C)       | TA               | 0               | 70   | °C   |

| Ambient Operating Temperature Range (MC68160B)                | TA               | <del>-4</del> 0 | 85   | °C   |

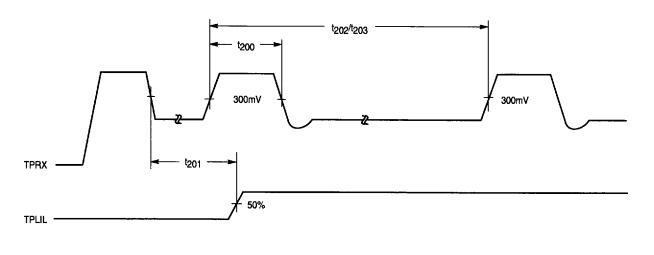

| ARX/ACX Input Differential Rise and Fall Time (see Figure 39) | t <sub>260</sub> | 2.0             | 10   | ns   |

| ARX Pair Idle Time after Transmission (see Figure 39)         | <sup>†</sup> 265 | 8.0             | _    | μs   |

#### **ESD**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. Motorola employs a Human Body Model (HBM) and a Charged Device Model (CDM) for ESD–susceptibility testing and protection design evaluation. ESD has been adopted for the CDM, however, a standard HBM (resistance = 1500  $\Omega$  capacitance – 100 pF) is widely used and, therefore, can be used for comparison purposes. The HBM ESD threshold presented here was obtained by using the circuit parameters contained in this specification. ESD threshold voltage is designed to 700 kV Human Body Model.

# **DC ELECTRICAL CHARACTERISTICS** (Unless otherwise noted, minimum and maximum limits apply over the recommended ambient operating temperature and power supply voltage ranges.)

| Characteristic                  | Symbol | Test Conditions   | Min | Тур      | Max        | Unit |

|---------------------------------|--------|-------------------|-----|----------|------------|------|

| POWER SUPPLY                    |        |                   |     |          |            |      |

| Undervoltage Shutdown Threshold | -      | <del>-</del>      | -   | _        | 4.4        | V    |

| Power Supply Current            | lDD    | _<br>Standby Mode |     | 145<br>- | 200<br>5.0 | mA   |

**■** 6367253 0102999 409 **■**

DC ELECTRICAL CHARACTERISTICS ( $T_A$  = 25°C,  $V_{CC}$  = 5.0 V  $\pm$  5%. Unless otherwise noted, minimum and maximum limits apply over the recommended ambient operating temperature and power supply voltage ranges for each MC68160, B, C except where noted.)

**Test Conditions**

Min

Max

Unit

**Symbol**

|                                                                  | •                      |                                               | 1    | · ·  | 1           |

|------------------------------------------------------------------|------------------------|-----------------------------------------------|------|------|-------------|

| TTL COMPATIBLE INPUTS                                            |                        |                                               |      | •    | 1           |

| TTL Compatible Input Voltage                                     |                        | _                                             |      |      | V           |

| Low State                                                        | V <sub>IL</sub> (TTL)  |                                               | _    | 0.8  |             |

| High State                                                       | V <sub>IH</sub> (TTL)  |                                               | 2.0  | -    |             |

| Input Current TTL Compatible Input Pins (Note 1)                 |                        | 0 V < V <sub>I</sub> < V <sub>DD</sub>        | _    | ±10  | μА          |

| Input Current TENA TTL Compatible Input Pin:                     |                        |                                               |      |      |             |

| with Pull-Down Resistor                                          |                        |                                               |      |      | 1           |

| ļін                                                              | lн                     |                                               | -    | +200 |             |

| IIL                                                              | IIL.                   |                                               | -    | -20  |             |

| with Pull-Down Resistor removed in Standby Mode                  | liH & li⊾              |                                               | _    | ±10  |             |

| CMOS COMPATIBLE INPUTS                                           |                        |                                               |      |      |             |

| CMOS Compatible Input Voltage                                    |                        | _                                             |      |      | V           |

| Low State                                                        | V <sub>IL</sub> (CMOS) |                                               | -    | 1.0  | 1           |

| High State                                                       | V <sub>IH</sub> (CMOS) |                                               | 3.0  | _    |             |

| Input Current (Pin X1)                                           | կը & կլ_               | 0 V < V <sub>I</sub> < V <sub>DD</sub>        | -    | ±100 | μΑ          |

| TTL/CMOS COMPATIBLE OUTPUTS                                      |                        |                                               |      |      |             |

| TTL/CMOS Compatible Output Voltage                               | VOL                    |                                               |      |      | V           |

| Low State (Note 2)                                               |                        | l <sub>OL</sub> = 4.0 mA                      | -    | 0.45 |             |

| Low State (Note 3)                                               |                        | I <sub>OL</sub> = 10 mA                       | _    | 0.45 |             |

| TTL/CMOS Compatible Output Voltage                               | VOH                    |                                               |      |      | V           |

| High State (Note 4)                                              |                        | IOH = -500 μA                                 | 3.9  | -    |             |

| High State (Note 5)                                              |                        | IOH = -10 mA                                  | 3.9  | -    |             |

| High State (Note 2)                                              |                        | $I_{OH} = -4.0 \text{ mA}$                    | 2.4  | _    |             |

| Three State Output Leakage Current                               | loz                    | $0 \text{ A} \leq \text{AOZ} \leq \text{ADD}$ | _    | ±10  | μΑ          |

|                                                                  | ī                      | T                                             | T .  | 1    | <del></del> |

| Characteristic                                                   | Symbol                 | Test Conditions                               | Min  | Max  | Unit        |

| TWISTED PAIR RECEIVER INPUTS                                     | ,                      |                                               |      | ,    | <del></del> |

| Input Voltage Range (DC + AC)                                    | V <sub>ITP</sub>       | _                                             | 1.5  | 4.3  | V           |

| Differential Input Squelch Threshold Voltage (MC68160, MC68160C) | VITPSQ                 | Note 10                                       | 270  | 390  | mV          |

| Differential Input Squelch Threshold Voltage (MC68160B)          | VITPSQ                 | Note 10                                       | 260  | 400  | mV          |

| Common Mode Bias Generator Voltage                               | V <sub>BCMTP</sub>     | Note 9                                        | 1.8  | 3.2  | V           |

| Common Mode Input Resistance                                     | RCMTP                  |                                               | 1000 | _    | Ω           |

| Differential Input Resistance                                    | RDIFFTP                | _                                             | 2.5  | _    | kΩ          |

|                                                                  | 1 5,, , , ,            |                                               | ı    | 1    |             |

# TWISTED PAIR TRANSMITTER OUTPUTS

Characteristic

| Differential Output Voltage                |          | Note 7                    |                       |                 | V |

|--------------------------------------------|----------|---------------------------|-----------------------|-----------------|---|

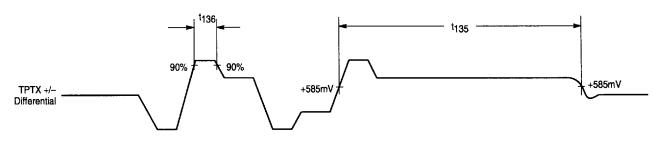

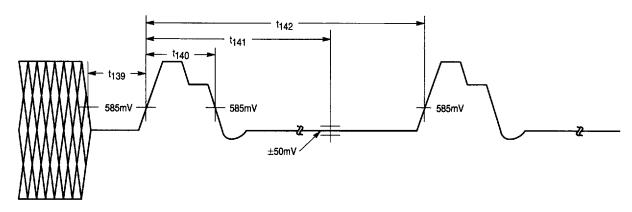

| Pre-Emphasis Level                         | VODFTPP  |                           | ±2.2                  | ±2.8            |   |

| Signal Level (MC68160, MC68160C)           | VODFTPS  |                           | ±1.56                 | ±1.98           |   |

| Signal Level (MC68160B)                    | VODFTPS  |                           | ±1.38                 | ±1.98           |   |

| Common Mode Output Voltage Range           | VOCMTP   | Note 6                    | 0                     | 4.0             | V |

| Common Mode Output Voltage in Standby Mode | VOCMTPSB | I <sub>OH</sub> = -100 μA | V <sub>DD</sub> – 1.0 | V <sub>DD</sub> | V |

NOTES: 1. APORT, TPAPCE, CS0, CS1, CS2, TX, LOOP, TPFULDL, TPSQEL and TPEN (in Input Mode).

2. TCLK, RX, RCLK, RENA and CLSN.

5. TPJABB and TPEN (In Output Mode).

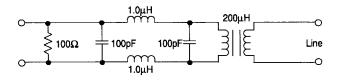

6. Measured with Test Load B1 (shown in Figure 3), applied directly to the TPTX+/- pins of the device.

7. Measured differentially with Test Load B2 (shown in Figure 4), applied directly to the TPTX+/- pins of the device.

Measured directly on the TPTX+/- pins of the device.

9. Measured with Test Load B3 (shown in Figure 5), applied directly to the TPRX+/- pins of the device.

10. The Common Mode Input Voltage is between 1.8 V and 3.2 V.

**■** 6367253 0103000 829 **■**

<sup>3.</sup> TPPLR, TPLIL, TPJABB, TXLED, RXLED, CLLED and TPEN (In Output Mode).

4. TPPLR, TPLIL, CLLED, TXLED and RXLED.

DC ELECTRICAL CHARACTERISTICS (continued) ( $T_A$  = 25°C,  $V_{CC}$  = 5.0 V  $\pm$  5%. Unless otherwise noted, minimum and maximum limits apply over the recommended ambient operating temperature and power supply voltage ranges for each MC68160, B, C except where noted.)

| Characteristic                                                                                                     | Symbol                        | Test Conditions  | Min               | Max              | Unit    |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------|-------------------|------------------|---------|

| TWISTED PAIR TRANSMITTER OUTPUTS                                                                                   |                               |                  |                   |                  | •       |

| Differential Output Voltage<br>IDLE Mode<br>Open Circuit                                                           | VODFTPI<br>VODFTPO            | Note 6<br>Note 8 |                   | ±50<br>5.25      | mV<br>V |

| Differential Output Impedance<br>TRANSMISSION Mode<br>IDLE Mode                                                    | RODFTPT<br>RODFTPI            | Note 8           | 12<br>8.0         | 28<br>29         | Ω       |

| Common Mode Output Impedance<br>TRANSMISSION Mode (MC68160, MC68160C)<br>TRANSMISSION Mode (MC68160B)<br>IDLE Mode | ROCMTPT<br>ROCMTPT<br>ROCMTPI | Note 8           | 3.0<br>2.5<br>1.0 | 7.0<br>7.0<br>10 | Ω<br>kΩ |

NOTES: 1. APORT, TPAPCE, CS0, CS1, CS2, TX, LOOP, TPFULDL, TPSQEL and TPEN (In Input Mode).

2. TCLK, RX, RCLK, RENA and CLSN.

3. TPPLR, TPLIL, TPJABB, TXLED, RXLED, CLLED and TPEN (In Output Mode).

4. TPPLR, TPLIL, CLLED, TXLED and RXLED.

5. TPJABB and TPEN (In Output Mode).

6. Measured with Test Load B1 (shown in Figure 3), applied directly to the TPTX+/- pins of the device.

7. Measured differentially with Test Load B2 (shown in Figure 4), applied directly to the TPTX+/- pins of the device.

8. Measured directly on the TPTX+/- pins of the device.

9. Measured with Test Load B3 (shown in Figure 5), applied directly to the TPRX+/- pins of the device.

10. The Common Mode Input Voltage is between 1.8 V and 3.2 V.

DC ELECTRICAL CHARACTERISTICS (Unless otherwise noted, minimum and maximum limits apply over the recommended ambient operating temperature and power supply voltage ranges for each MC68160, B, C except where noted.)

| Characteristic                                                         | Symbol                     | Test Conditions                                                           | Min                                 | Max                                 | Unit |

|------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------|-------------------------------------|-------------------------------------|------|

| AUI RECEIVER INPUTS                                                    |                            |                                                                           | •                                   |                                     |      |

| Input Voltage Range (DC + AC)                                          | VIA                        | _                                                                         | 1.0                                 | 4.2                                 | ٧    |

| Differential Mode Input Voltage Range                                  | V <sub>IDFA</sub>          | -                                                                         | ±318                                | ±1315                               | mV   |

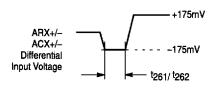

| Differential Input Squelch Threshold Voltage (MC68160, MC68160C)       | VIASQ                      | -                                                                         | -275                                | -175                                | mV   |

| Differential Mode Input Voltage Range (MC68160B)                       | VIASQ                      | _                                                                         | -300                                | -175                                | mV   |

| Common Mode Input Resistance                                           | RICMA                      | 1.0 V < V <sub>ICMA</sub> < 4.2 V                                         | 1.5                                 | _                                   | kΩ   |

| Differential Input Resistance (ARX, ACX Inputs)                        | R <sub>IDFA</sub>          | 1.0 V < V <sub>ICMA</sub> < 4.2 V<br>318 mV < V <sub>IDMA</sub> < 1315 mV | 5.0                                 | -                                   | kΩ   |

| AUI TRANSMITTER OUTPUTS                                                |                            | •                                                                         | •                                   |                                     |      |

| Common Mode Output Voltage<br>IDLE Mode<br>ACTIVE Mode<br>STANDBY Mode | VOCMIA<br>VOCMAA<br>VOCMSA | Figure 6<br>I <sub>O</sub> = -100 μA                                      | 1.0<br>1.0<br>V <sub>DD</sub> – 2.0 | 4.2<br>4.2<br>V <sub>DD</sub> – 1.2 | V    |

| Differential Output Voltage<br>IDLE Mode<br>ACTIVE Mode                | VODFIA<br>VODFAA           | Figure 6                                                                  | _<br>±600                           | ±40<br>±1315                        | mV   |

| Differential Output Load Current<br>IDLE Mode                          | IODFIA                     | Figure 7                                                                  | _                                   | ±4.0                                | mA   |

| Output Short Circuit Current                                           | IODSA                      | Output Short Circuited to VDD or GND                                      | -                                   | ±150                                | mA   |

6367253 0103001 765

**MOTOROLA ANALOG IC DEVICE DATA**

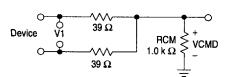

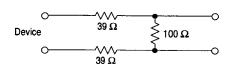

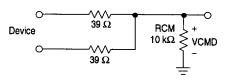

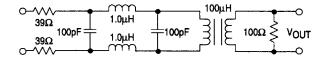

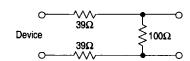

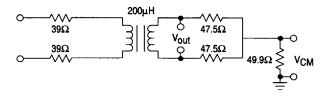

Figure 3. Test Load B1

Figure 4. Test Load B2

Figure 5. Test Load B3

**NOTE:** A total of  $50~\Omega$  per driver output is required for proper series line termination. This is realized with the  $39~\Omega$  external resistors shown in Figures 3, 4 and 5, together with the internal driver output resistance.

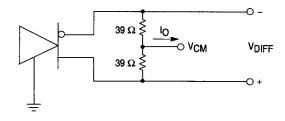

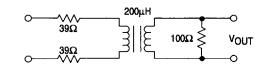

Figure 6. AUI Common Mode Termination

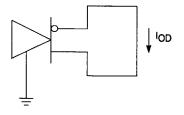

Figure 7. AUI Differential Output Short Circuit Current

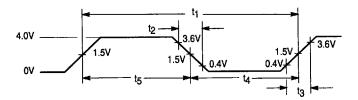

AC ELECTRICAL CHARACTERISTICS (Unless otherwise noted, minimum and maximum limits apply over the recommended temperature and power supply voltage ranges for each MC68160, B, C except where noted.)

| Characteristic                                     | Symbol            | Min    | Max    | Unit |

|----------------------------------------------------|-------------------|--------|--------|------|

| EXTERNAL CLOCK INPUT (X1)                          |                   |        |        |      |

| Cycle Time (Note 1) (See Figure 8)                 | tı                | 49.995 | 50.005 | ns   |

| Fall Time                                          | t <sub>2</sub>    | _      | 5.0    |      |

| Rise Time                                          | t3                | _      | 5.0    |      |

| Low Time                                           | t4                | 20     | 30     |      |

| High Time                                          | t <sub>5</sub>    | 20     | 30     |      |

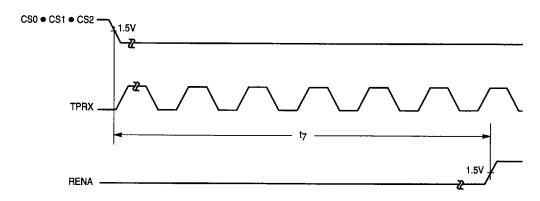

| RECEIVE PHASE-LOCKED-LOOP SWITCHING                |                   | .,     |        |      |

| Stabilization Time                                 | t <sub>7</sub>    |        | 100    | ms   |

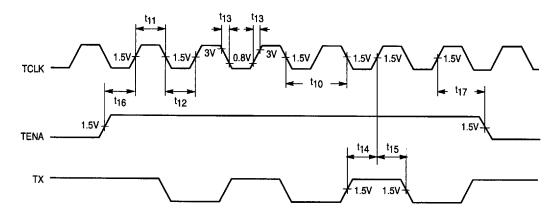

| CONTROLLER TRANSMIT SWITCHING (MOTOROLA MODE)      |                   |        |        |      |

| TCLK Cycle Time                                    | t <sub>10</sub>   | 99     | 101    | ns   |

| TCLK High Time                                     | t <sub>11</sub>   | 45     | 55     |      |

| TCLK Low Time                                      | t <sub>12</sub>   | 45     | 55     |      |

| TCLK Rise and Fall Time                            | <sup>†</sup> 13   | -      | 8.0    |      |

| TX Setup Time to TCLK ↑                            | t <sub>14</sub>   | 20     | _      | ns   |

| TX Hold Time to TCLK ↑                             | t <sub>15</sub>   | 0      | _      |      |

| TENA Setup Time to TCLK ↑                          | t <sub>16</sub>   | 20     | -      | ns   |

| TENA Hold Time to TCLK ↑                           | t <sub>17</sub>   | 0      |        |      |

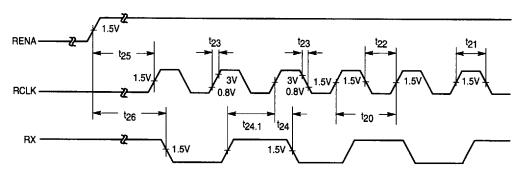

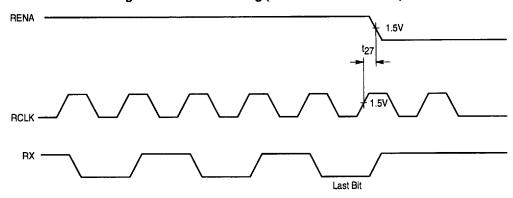

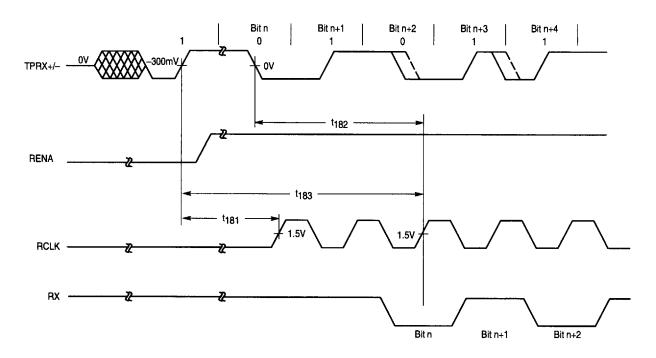

| CONTROLLER RECEIVE SWITCHING                       |                   |        |        |      |

| RCLK Cycle Time                                    | t <sub>20</sub>   | 90     | -      | ns   |

| RCLK High Time                                     | t <sub>21</sub>   | 42     | _      |      |

| RCLK Low Time (MC68160, MC68160C)                  | t22               | 47     | 55     |      |

| RCLK Low Time (MC68160B)                           | t <sub>22</sub>   | 44     | 58     |      |

| RCLK Rise and Fall Time                            | t23               |        | 8.0    |      |

| RX Hold Time from RCLK ↑                           | t <sub>24</sub>   | 10     | _      | ns   |

| RX Set-Up Time to RCLK ↑                           | <sup>t</sup> 24.1 | 70     | -      |      |

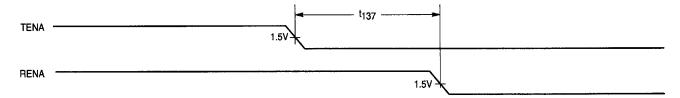

| RCLK Delay from RENA ↑                             | t <sub>25</sub>   | _      | 650    | ns   |

| RX Delay from RENA ↑                               | t <sub>26</sub>   | _      | 600    | 1    |

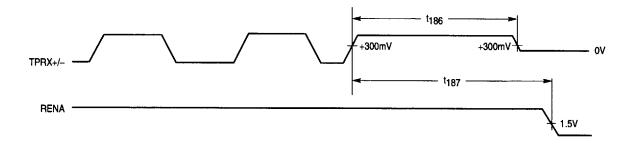

| RENA Deassertion Delay from RCLK ↑ (See Figure 12) | <sup>†</sup> 27   | 10     | 30     | ns   |

NOTES: 1. To meet IEEE-802.3 specifications.

Load on specified output is 20 pF to ground, unless otherwise noted.

↑ = Rising Edge

Figure 8. X1 Input Voltage Levels for Timing Measurements

6367253 OlO3003 538 **E**

Figure 9. Receive Phase-Locked-Loop Switching

NOTE: CS0 • CS1 • CS2 is the logical AND operation and refers to the pins not at Logic 1.

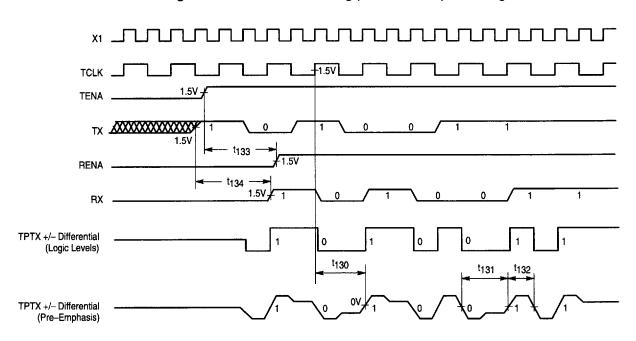

Figure 10. Transmit Timing (Motorola Mode)

Figure 11. Receive Timing (Motorola Start of Frame)

Figure 12. Receive Timing (Motorola End of Frame)

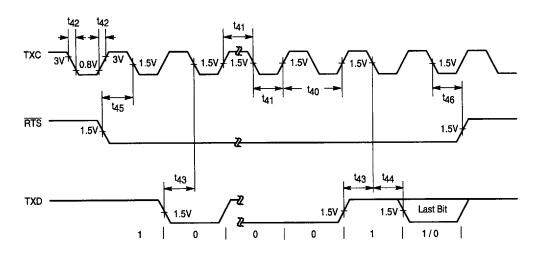

#### CONTROLLER TRANSMIT SWITCHING (Intel Mode - Support by MC68160 Only)

| Characteristic                                                                                         | Symbol            | Min           | Max            | Unit |

|--------------------------------------------------------------------------------------------------------|-------------------|---------------|----------------|------|

| TXC Cycle Time TXC High and Low Time TXC Rise and Fall Time                                            | t40<br>t41<br>t42 | 99<br>40<br>- | 101<br><br>5.0 | ns   |

| TXD Setup Time to $\overline{\text{TXC}}\downarrow$ TXD Hold Time to $\overline{\text{TXC}}\downarrow$ | t43<br>t44        | 20<br>0       |                | ns   |

| RTS Setup Time to TXC ↓ RTS Hold Time to TXC ↓                                                         | t45<br>t46        | 20<br>0       |                | ns   |

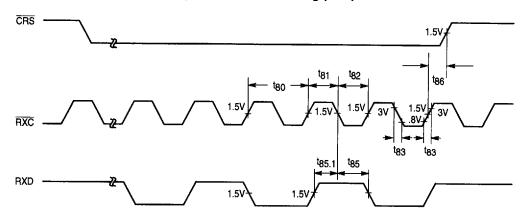

#### **CONTROLLER RECEIVE SWITCHING**

| RXC Cycle Time RXC High Time RXC Low Time RXC Rise and Fall Time       | <sup>t</sup> 80<br><sup>t</sup> 81<br><sup>t</sup> 82<br><sup>t</sup> 83 | 90<br>45<br>40<br>– | -<br>55<br>-<br>5.0 | ns |

|------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------|---------------------|----|

| RXD Hold Time from RXC ↓ RXD Set-Up Time to RXC ↓ CRS Delay from RXC ↑ | <sup>t</sup> 85<br><sup>t</sup> 85.1<br><sup>t</sup> 86                  | 50<br>35<br>12      | -<br>-<br>30        | ns |

Load on specified output is 20 pF to ground, unless otherwise noted.  $\uparrow$  = Rising Edge  $\downarrow$  = Falling Edge

Figure 13. Transmit Timing (Intel)

6367253 0103005 300

**MOTOROLA ANALOG IC DEVICE DATA**

Figure 14. Receive Timing (Intel)

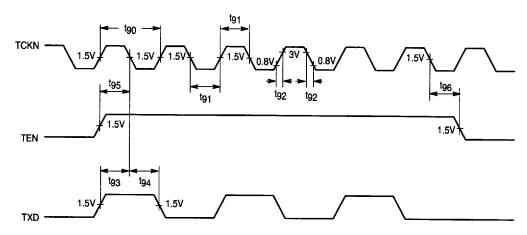

# CONTROLLER TRANSMIT SWITCHING (Fujitsu Mode - Supported by MC68160 Only)

| Characteristic                                                 | Symbol            | Min           | Max              | Unit |

|----------------------------------------------------------------|-------------------|---------------|------------------|------|

| TCKN Cycle Time TCKN High and Low Time TCKN Rise and Fall Time | t90<br>t91<br>t92 | 99<br>45<br>– | 101<br>55<br>8.0 | ns   |

| TXD Setup Time to TCKN ↓ TXD Hold Time to TCKN ↓               | t93<br>t94        | 20<br>0       |                  | ns   |

| TEN Setup Time to TCKN ↓ TEN Hold Time to TCKN ↓               | t95<br>t96        | 20<br>0       |                  | ns   |

#### **CONTROLLER RECEIVE SWITCHING**

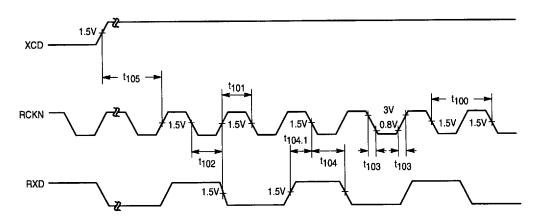

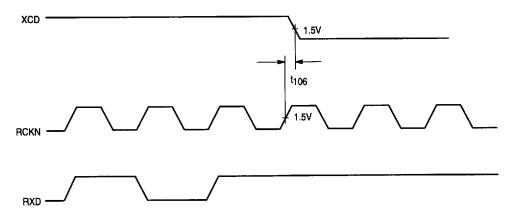

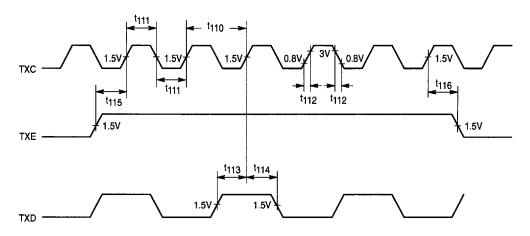

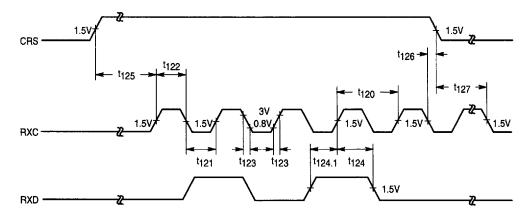

| RCKN Cycle Time<br>RCKN High Time<br>RCKN Low Time<br>RCKN Rise and Fall Time | t100<br>t101<br>t102<br>t103                               | 90<br>40<br>45<br>– | <br>-<br>55<br>8.0 | ns |