# SED1355 Embedded RAMDAC LCD/CRT Controller

# SED1355 TECHNICAL MANUAL

Document Number: X23A-Q-001-09

# www.DataSheet.in

Copyright © 1998, 1999 Epson Research and Development, Inc. All Rights Reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other trademarks are the property of their respective owners.

www.DataSheet.in

# **Customer Support Information**

# **Comprehensive Support Tools**

Seiko Epson Corp. provides to the system designer and computer OEM manufacturer a complete set of resources and tools for the development of graphics systems.

### **Evaluation / Demonstration Board**

- Assembled and fully tested graphics evaluation board with installation guide and schematics.

- To borrow an evaluation board, please contact your local Seiko Epson Corp. sales representative.

# **Chip Documentation**

• Technical manual includes Data Sheet, Application Notes, and Programmer's Reference.

#### **Software**

- · OEM Utilities.

- · User Utilities.

- · Evaluation Software.

- To obtain these programs, contact Application Engineering Support.

# **Application Engineering Support**

#### **Engineering and Sales Support is provided by:**

#### Japar

Seiko Epson Corporation Electronic Devices Marketing Division 421-8, Hino, Hino-shi Tokyo 191-8501, Japan Tel: 042-587-5812 Fax: 042-587-5564 http://www.epson.co.jp

#### **Hong Kong**

Epson Hong Kong Ltd. 20/F., Harbour Centre 25 Harbour Road Wanchai, Hong Kong Tel: 2585-4600 Fax: 2827-4346

#### **North America**

Epson Electronics America, Inc. 150 River Oaks Parkway San Jose, CA 95134, USA Tel: (408) 922-0200 Fax: (408) 922-0238 http://www.eea.epson.com

#### Europe

Epson Europe Electronics GmbH Riesstrasse 15 80992 Munich, Germany Tel: 089-14005-0 Fax: 089-14005-110 Taiwan, R.O.C.

Epson Taiwan Technology & Trading Ltd. 10F, No. 287 Nanking East Road Sec. 3, Taipei, Taiwan, R.O.C. Tel: 02-2717-7360 Fax: 02-2712-9164

#### Singapore

Epson Singapore Pte., Ltd.

No. 1

Temasek Avenue #36-00

Millenia Tower

Singapore, 039192

Tel: 337-7911

Tel: 337-7911 Fax: 334-2716

### **Table of Contents**

#### INTRODUCTION

SED1355 Embedded RAMDAC LCD/CRT Controller Product Brief

#### **SPECIFICATION**

SED1355 Hardware Functional Specification

#### PROGRAMMER'S REFERENCE

SED1355 Programming Notes and Examples SED1355 Register Summary

#### **UTILITIES**

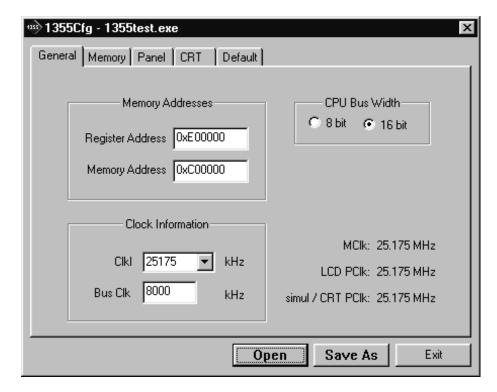

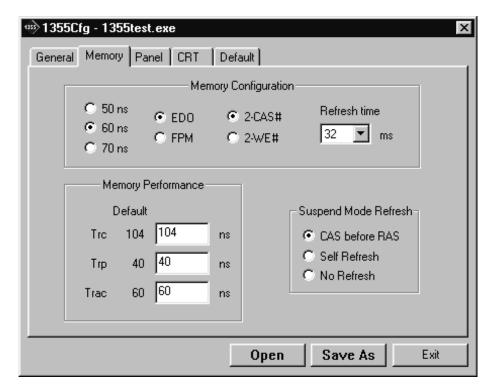

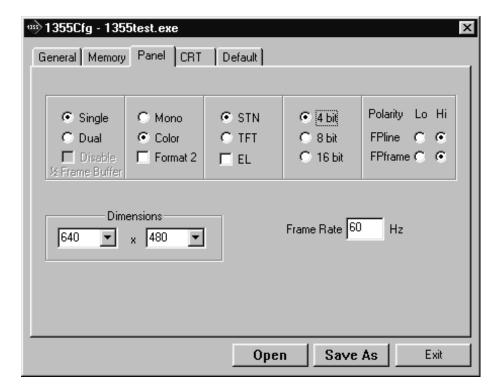

1355CFG Configuration Program

1355SHOW Demonstration Program

1355SPLT Display Utility

1355VIRT Display Utility

1355PLAY Diagnostic Utility

1355BMP Demonstration Program

1355PWR Software Suspend Power Sequencing Utility

#### **DRIVERS**

SED1355 Windows® CE Display Drivers

#### **EVALUATION**

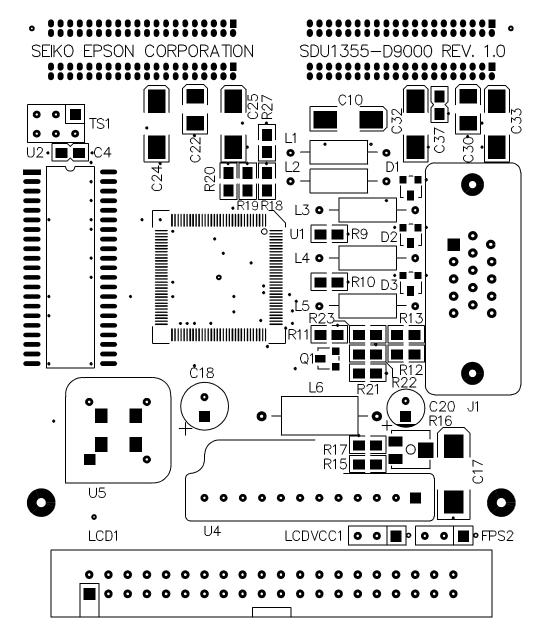

SDU1355B0C Rev. 1.0 ISA Bus Evaluation Board User Manual SDU1355-D9000 Evaluation Board User Guide

### **APPLICATION NOTES**

Power Consumption

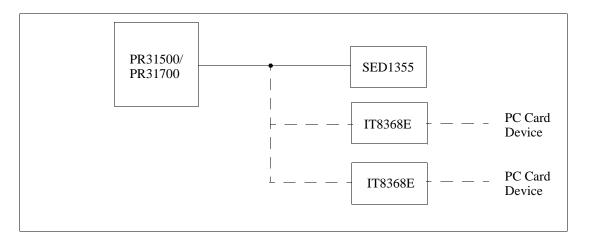

Interfacing to the Philips MIPS PR31500/PR31700 Processor

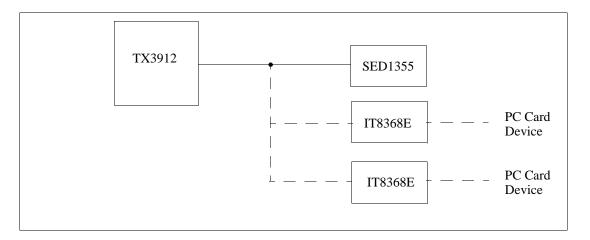

Interfacing to the PC Card Bus

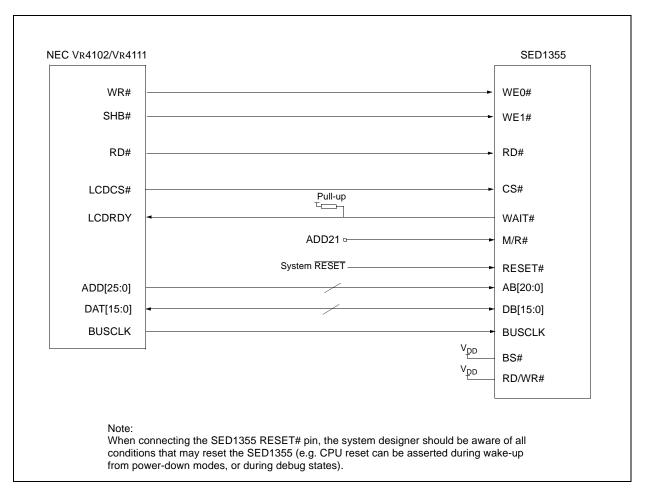

Interfacing to the NEC VR4102/VR4111TM Microprocessor

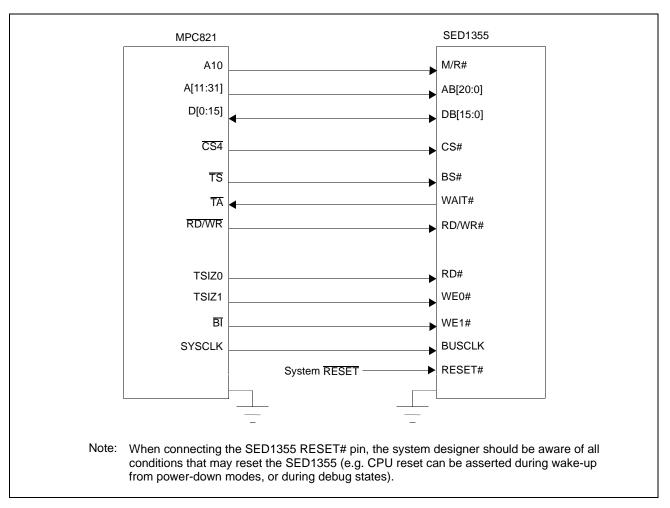

Interfacing to the Motorola MPC821 Microprocessor

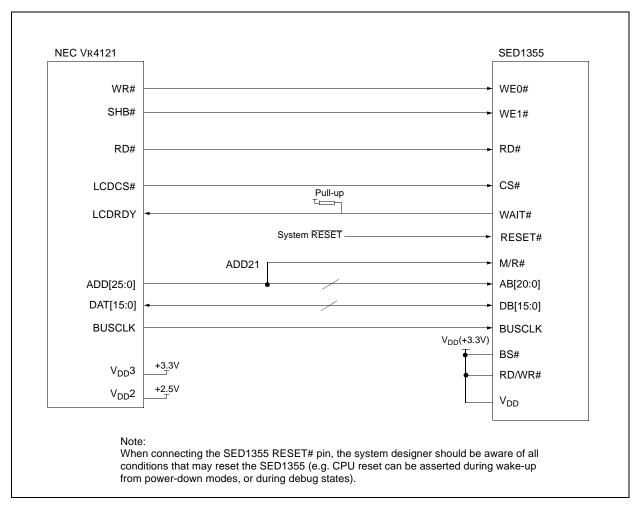

Interfacing to the NEC VR4121<sup>TM</sup> Microprocessor

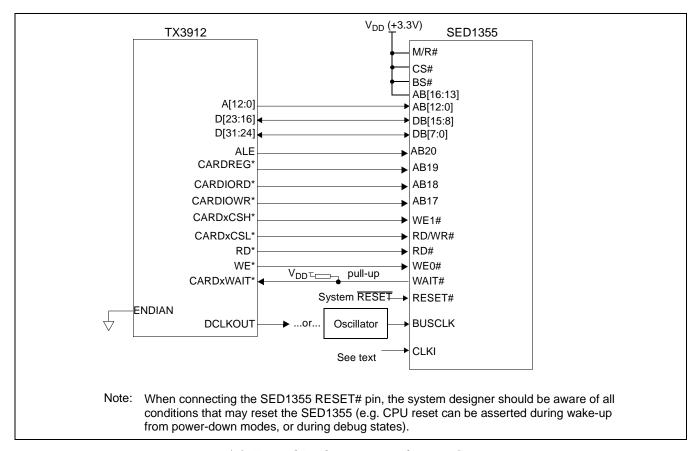

Interfacing to the Toshiba MIPS TX3912 Processor

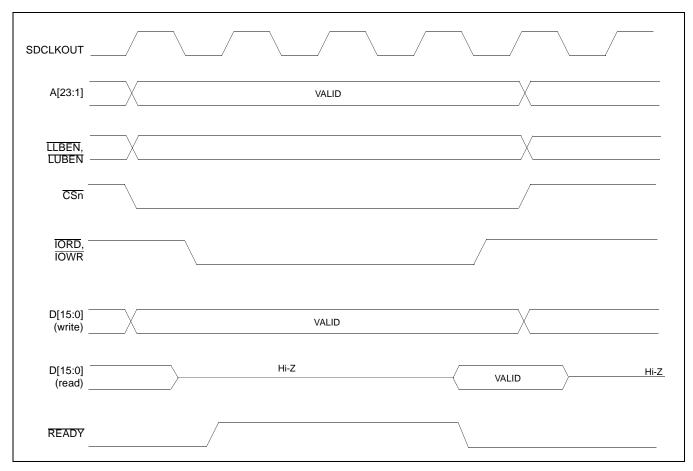

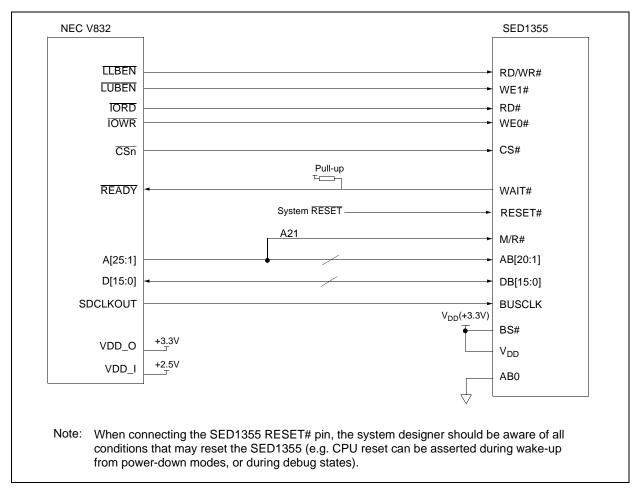

Interfacing to the NEC V832 Microprocessor

# **GRAPHICS**

# **SED1355**

### SED1355 EMBEDDED RAMDAC LCD/CRT CONTROLLER

October 1998

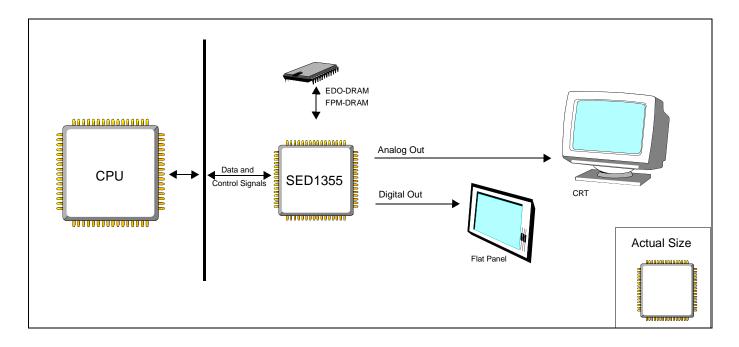

#### ■ DESCRIPTION

The SED1355 is a color/monochrome LCD/CRT graphics controller interfacing to a wide range of CPUs and display devices. The SED1355 architecture is designed to meet the low cost, low power requirements of the embedded markets, such as Mobile Communications, Hand-Held PCs, and Office Automation.

The SED1355 supports multiple CPUs, all LCD panel types, CRT, and additionally provides a number of differentiating features. Products requiring a "Portrait" mode display can take advantage of the Hardware Portrait Mode feature. Simultaneous, Virtual and Split Screen Display are just some of the display modes supported, while the Hardware Cursor, Ink Layer, and the Memory Enhancement Registers offer substantial performance benefits. These features, combined with the SED1355's Operating System independence, make it an ideal display solution for a wide variety of applications.

#### **■ FEATURES**

#### **Memory Interface**

- 16-bit EDO-DRAM or FPM-DRAM interface.

- Memory size options:

512K bytes using one 256K×16 device.

2M bytes using one 1M×16 device.

- Addressable as a single linear address space.

#### **CPU Interface**

Supports the following interfaces:

Hitachi SH-4.

Hitachi SH-3.

Motorola M68K.

Philips MIPS PR31500/PR31700.

Toshiba MIPS TX3912.

Motorola Power PC MPC821.

NEC MIPS VR4102/VR4111.

Epson E0C33.

PC Card (PCMCIA).

StrongARM (PC Card).

ISA bus.

MPU bus interface with programmable READY.

CPU write buffer.

#### **Display Support**

- 4/8-bit monochrome passive LCD interface.

- 4/8/16-bit color passive LCD interface.

- Single-panel, single-drive displays.

- Dual-panel, dual-drive displays.

- Direct support for 9/12-bit TFT/D-TFD; 18-bit TFT/D-TFD is supported up to 64K color depth (16-bit data).

- Embedded RAMDAC with direct analog CRT drive.

- Simultaneous display of CRT and passive or TFT/D-TFD panels.

- Maximum resolution of 800x600 pixels at a color depth of 16 bpp.

#### **Display Modes**

- 1/2/4/8/16 bit-per-pixel (bpp) support on LCD/CRT.

- Up to 16 shades of gray using FRM on monochrome passive LCD panels.

- Up to 4096 colors on passive LCD panels.

- Up to 64K colors on active matrix TFT/D-TFD LCD panels and CRT in 16 bpp modes.

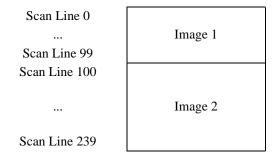

- Split Screen Display: allows two different images to be simultaneously viewed on the same display.

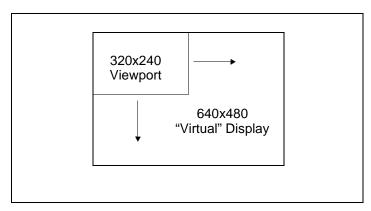

- Virtual Display Support: displays images larger than the display size through the use of panning.

- Double Buffering/multi-pages: provides smooth animation and instantaneous screen update.

- Hardware Portrait Mode: direct hardware 90° rotation of display image for portrait mode display.

- Acceleration of screen updates by allocating full display memory bandwidth to CPU.

- Hardware 64x64 pixel 2-bit cursor or full screen 2-bit ink layer.

#### **Clock Source**

- Single clock input for both pixel and memory clocks.

- Memory clock can be input clock or (input clock/2), providing flexibility to use CPU bus clock as input.

- Pixel clock can be memory clock or (memory clock/2) or (memory clock/3) or (memory clock/4).

### **Power Down Modes**

- Software power save mode.

- LCD power sequencing.

#### **General Purpose IO Pins**

• Up to 3 General Purpose IO pins are available.

#### **Operating Voltage**

• 2.7 volts to 5.5 volts.

#### Package

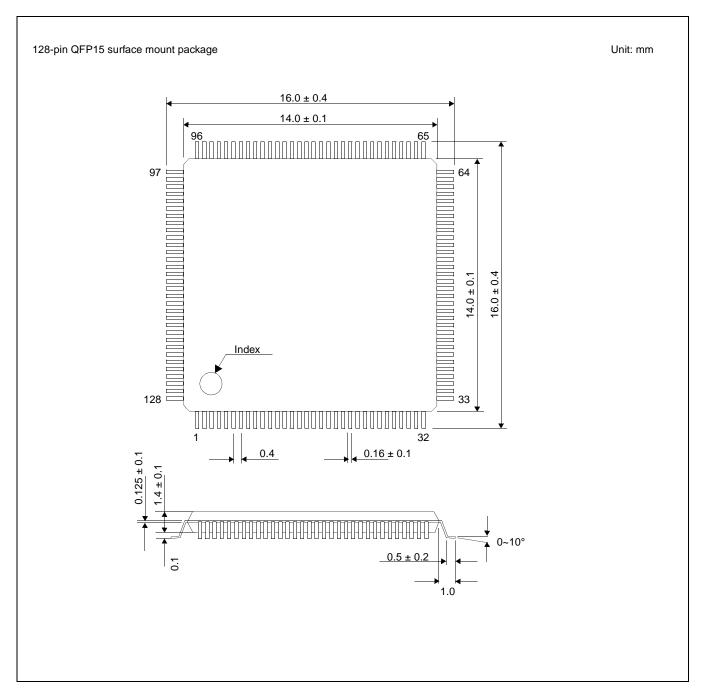

• 128-pin QFP15 surface mount package.

X23A-C-002-13

# **SED1355**

#### **■ SYSTEM BLOCK DIAGRAM**

# CONTACT YOUR SALES REPRESENTATIVE FOR THESE COMPREHENSIVE DESIGN TOOLS:

- SED1355 Technical Manual

- SDU1355 Evaluation Boards

- Windows<sup>®</sup> CE Display Driver

- CPU Independent Software Utilities

#### Japan

Seiko Epson Corporation Electronic Devices Marketing Division 421-8, Hino, Hino-shi Tokyo 191-8501, Japan Tel: 042-587-5812 Fax: 042-587-5564 http://www.epson.co.jp

### **Hong Kong**

Epson Hong Kong Ltd. 20/F., Harbour Centre 25 Harbour Road Wanchai, Hong Kong Tel: 2585-4600 Fax: 2827-4346

#### **North America**

Epson Electronics America, Inc. 150 River Oaks Parkway San Jose, CA 95134, USA Tel: (408) 922-0200 Fax: (408) 922-0238 http://www.eea.epson.com

#### Europe

Epson Europe Electronics GmbH Riesstrasse 15 80992 Munich, Germany Tel: 089-14005-0 Fax: 089-14005-110

# FOR SYSTEM INTEGRATION SERVICES FOR WINDOWS® CE CONTACT:

Epson Research & Development, Inc. Suite #320 - 11120 Horseshoe Way Richmond, B.C., Canada V7A 5H7

Tel: (604) 275-5151 Fax: (604) 275-2167

Email: wince@erd.epson.com http://www.erd.epson.com

#### Taiwan, R.O.C.

Epson Taiwan Technology & Trading Ltd. 10F, No. 287 Nanking East Road Sec. 3, Taipei, Taiwan, R.O.C. Tel: 02-2717-7360 Fax: 02-2712-9164

#### Singapore

Epson Singapore Pte., Ltd. No. 1

Temasek Avenue #36-00

Millenia Tower

Singapore, 039192

Tel: 337-7911

Fax: 334-2716

Copyright © 1998 Epson Research and Development, Inc. All Rights Reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. Microsoft, Windows, and the Windows CE Logo are registered trademarks of Microsoft Corporation.

2 X23A-C-002-13

# SED1355 Embedded RAMDAC LCD/CRT Controller

# **Hardware Functional Specification**

Document Number: X23A-A-001-11

Copyright © 1998, 1999 Epson Research and Development, Inc. All Rights Reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other trademarks are the property of their respective owners.

# **Table of Contents**

| 1 | Introd | ductio | n                             | 11 |

|---|--------|--------|-------------------------------|----|

|   | 1.1    | Scope  |                               | 11 |

|   | 1.2    | Overv  | riew Description              | 11 |

| 2 | Featu  | ires . |                               | 12 |

|   | 2.1    | Memo   | ory Interface                 | 12 |

|   | 2.2    | CPU I  | Interface                     | 12 |

|   | 2.3    | Displa | ay Support                    | 13 |

|   | 2.4    | Displa | ay Modes                      | 13 |

|   | 2.5    | Displa | ay Features                   | 13 |

|   | 2.6    | Clock  | Source                        | 13 |

|   | 2.7    | Misce  | llaneous                      | 14 |

| 3 | Typic  | al Sy  | stem Implementation Diagrams  | 15 |

| 4 | Interr | nal De | scription                     | 20 |

|   | 4.1    | Block  | Diagram Showing Datapaths     | 20 |

|   | 4.2    | Block  | Descriptions                  | 20 |

|   | 4.     | 2.1    | Register                      | 20 |

|   | 4.     | 2.2    | Host Interface                | 20 |

|   | 4.     | 2.3    | CPU R/W                       | 20 |

|   | 4.     | 2.4    | Memory Controller             | 21 |

|   | 4.     | 2.5    | Display FIFO                  | 21 |

|   | 4.     | 2.6    | Cursor FIFO                   | 21 |

|   | 4.     | 2.7    | Look-Up Tables                | 21 |

|   | 4.     | 2.8    | CRTC                          | 21 |

|   | 4.     | 2.9    | LCD Interface                 | 21 |

|   | 4.     | 2.10   | DAC                           | 21 |

|   |        | 2.11   | Power Save                    |    |

|   | 4.     | 2.12   | Clocks                        | 21 |

| 5 | Pins   |        |                               | 22 |

|   | 5.1    | Pinou  | t Diagram                     | 22 |

|   | 5.2    | Pin D  | escription                    | 23 |

|   | 5.     | 2.1    | Host Interface                | 23 |

|   | 5.     | 2.2    | Memory Interface              | 29 |

|   | 5.     | 2.3    | LCD Interface                 |    |

|   | 5.     | 2.4    | CRT Interface                 | 31 |

|   | 5.     | 2.5    | Miscellaneous                 | 32 |

|   | 5.3    | Sumn   | nary of Configuration Options | 33 |

|   | 5.4    | Multij | ple Function Pin Mapping      | 34 |

|   | 5.5    | CRT 1  | Interface                     | 36 |

| 6 | D.C. ( | Chara  | cteristics                    | 37 |

| 7 | A.C | C. Chara | acteristics                                                |

|---|-----|----------|------------------------------------------------------------|

|   | 7.1 | CPU      | Interface Timing                                           |

|   |     | 7.1.1    | SH-4 Interface Timing                                      |

|   |     | 7.1.2    | SH-3 Interface Timing                                      |

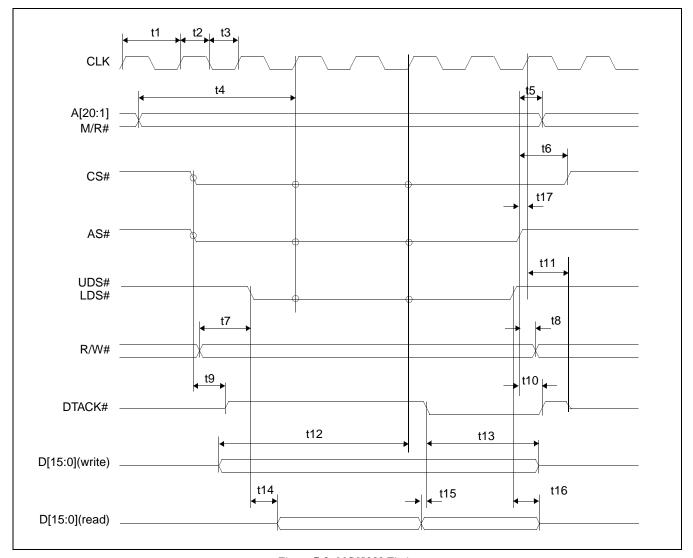

|   |     | 7.1.3    | MC68K Bus 1 Interface Timing (e.g. MC68000)                |

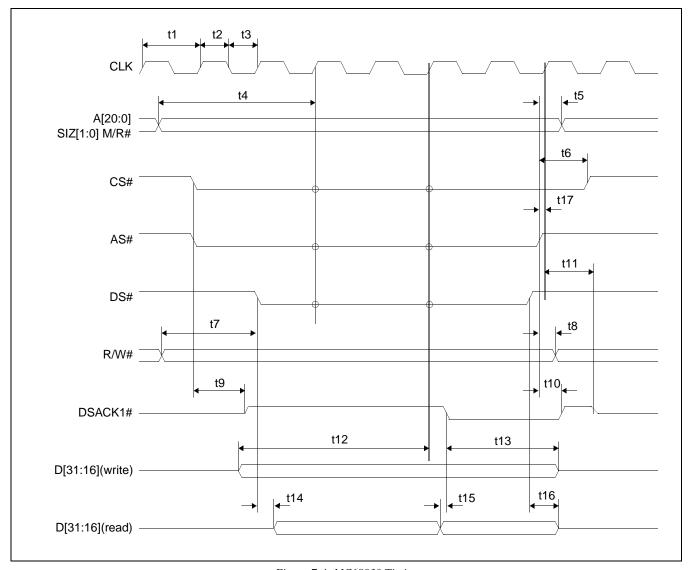

|   |     | 7.1.4    | MC68K Bus 2 Interface Timing (e.g. MC68030)                |

|   |     | 7.1.5    | PC Card Interface Timing                                   |

|   |     | 7.1.6    | Generic Interface Timing                                   |

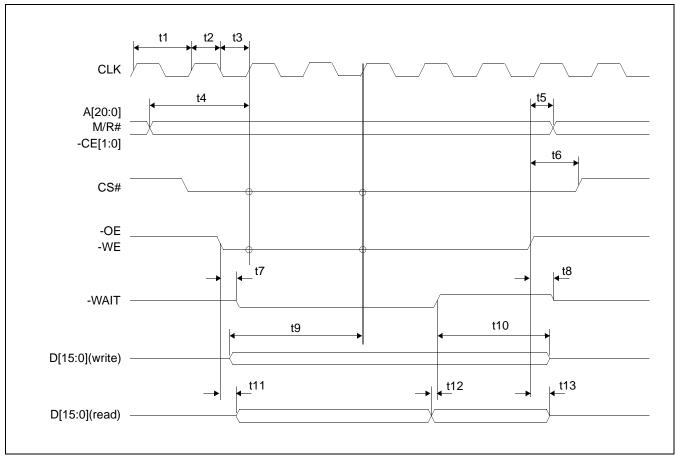

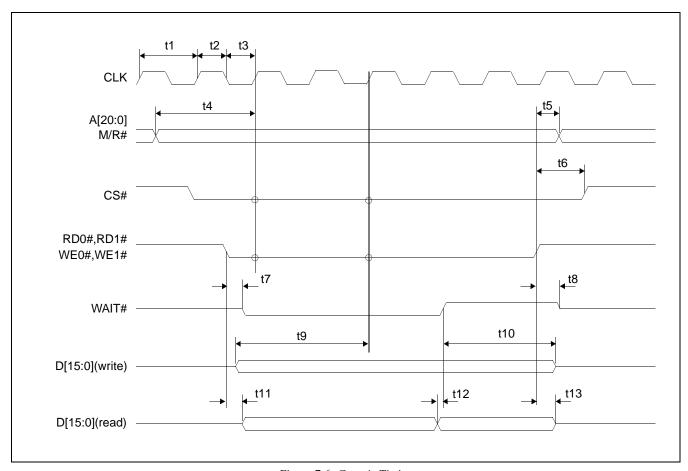

|   |     | 7.1.7    | MIPS/ISA Interface Timing                                  |

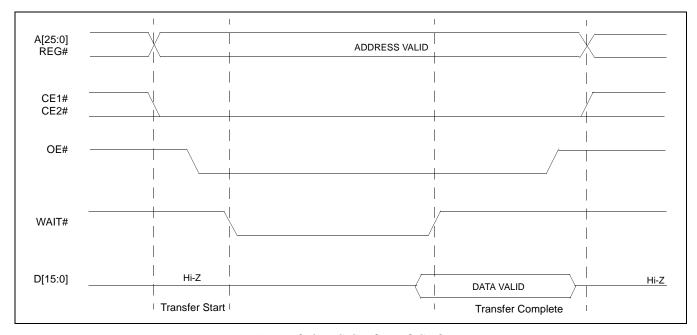

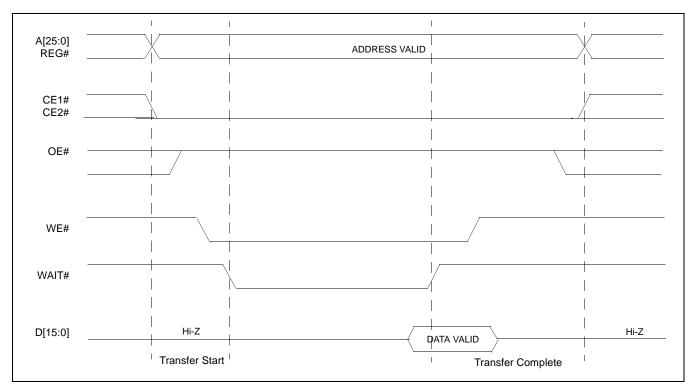

|   |     | 7.1.8    | Philips Interface Timing (e.g. PR31500/PR31700)            |

|   |     | 7.1.9    | Toshiba Interface Timing (e.g. TX3912)                     |

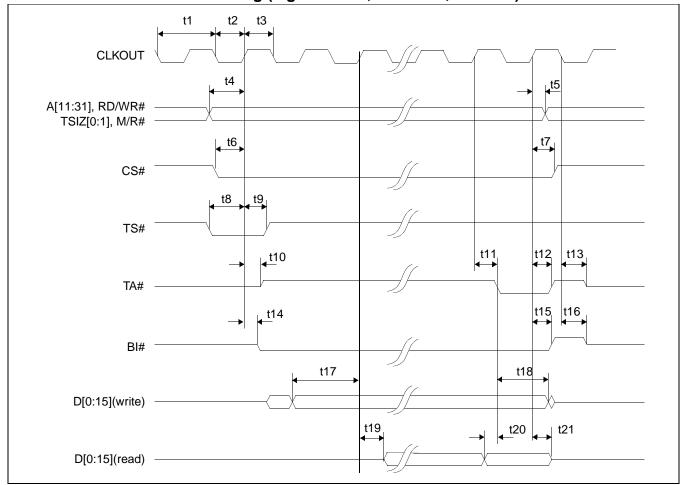

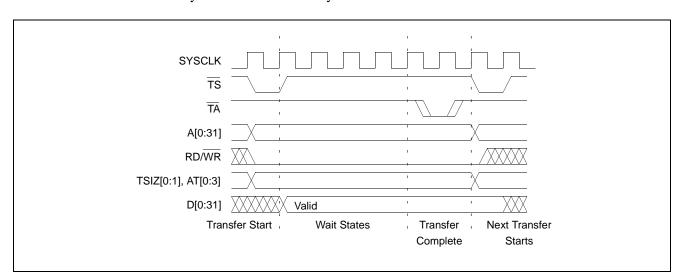

|   |     | 7.1.10   | Power PC Interface Timing (e.g. MPC8xx, MC68040, Coldfire) |

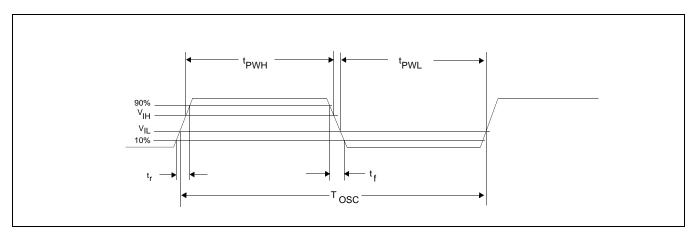

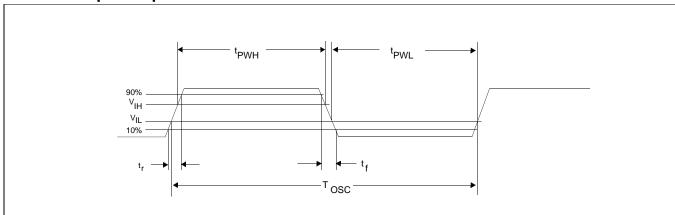

|   | 7.2 | Clock    | Input Requirements                                         |

|   | 7.3 | Mem      | ory Interface Timing                                       |

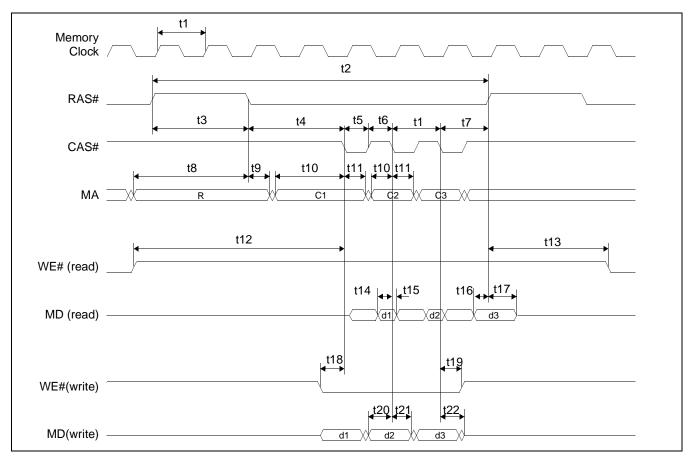

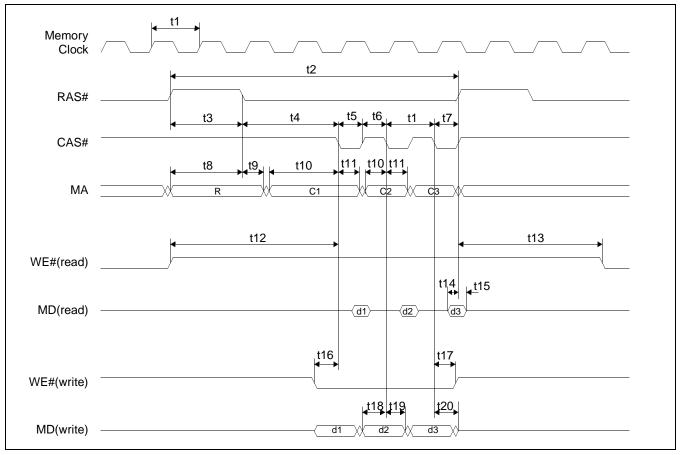

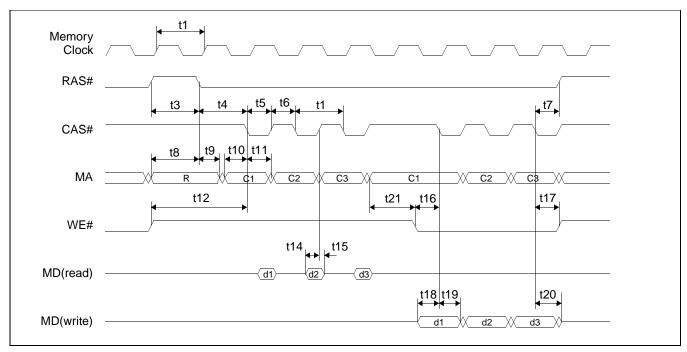

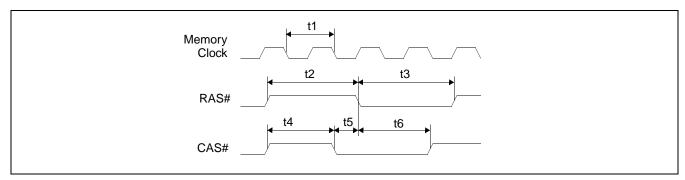

|   |     | 7.3.1    | EDO-DRAM Read/Write/Read-Write Timing                      |

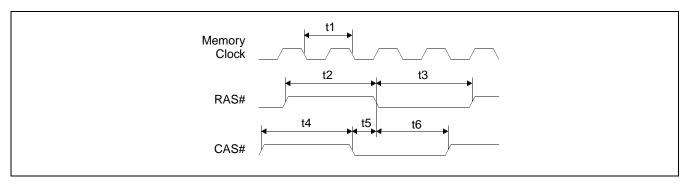

|   |     | 7.3.2    | EDO-DRAM CAS Before RAS Refresh Timing                     |

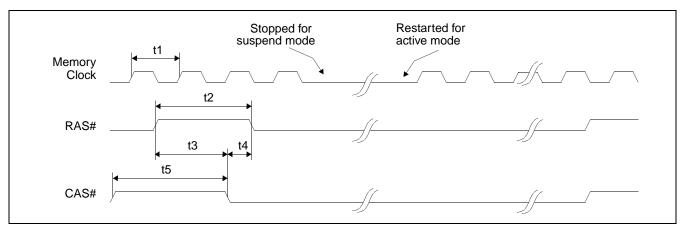

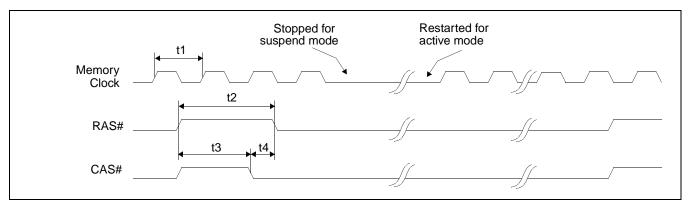

|   |     | 7.3.3    | EDO-DRAM Self-Refresh Timing                               |

|   |     | 7.3.4    | FPM-DRAM Read/Write/Read-Write Timing                      |

|   |     | 7.3.5    | FPM-DRAM CAS Before RAS Refresh Timing                     |

|   |     | 7.3.6    | FPM-DRAM Self-Refresh Timing                               |

|   | 7.4 | Powe     | r Sequencing                                               |

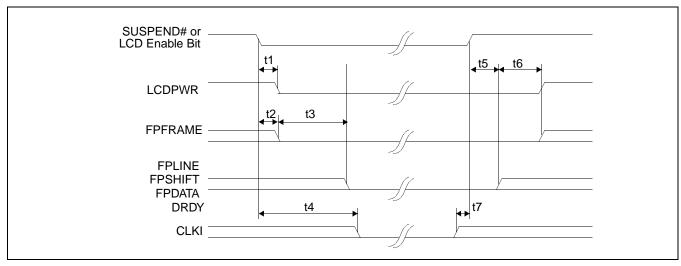

|   |     | 7.4.1    | LCD Power Sequencing                                       |

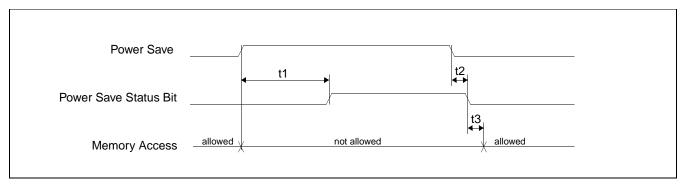

|   |     | 7.4.2    | Power Save Status                                          |

|   | 7.5 | Displ    | ay Interface                                               |

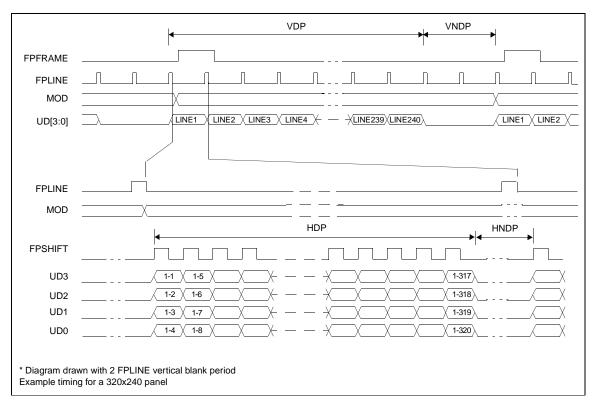

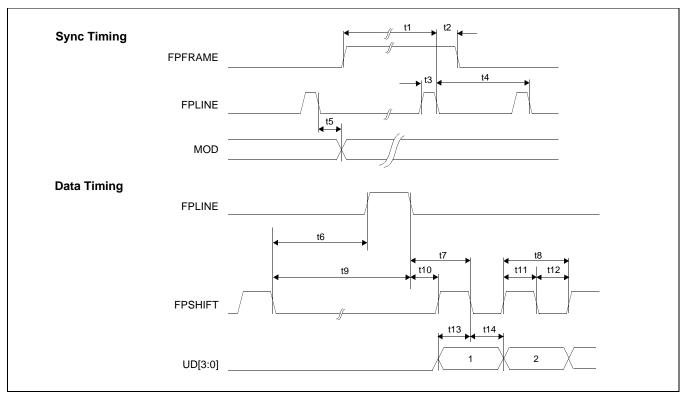

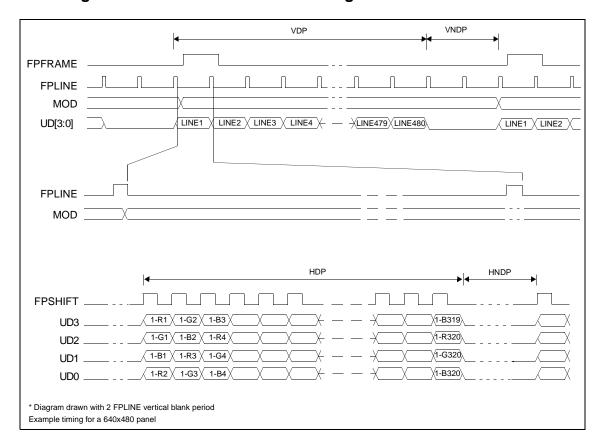

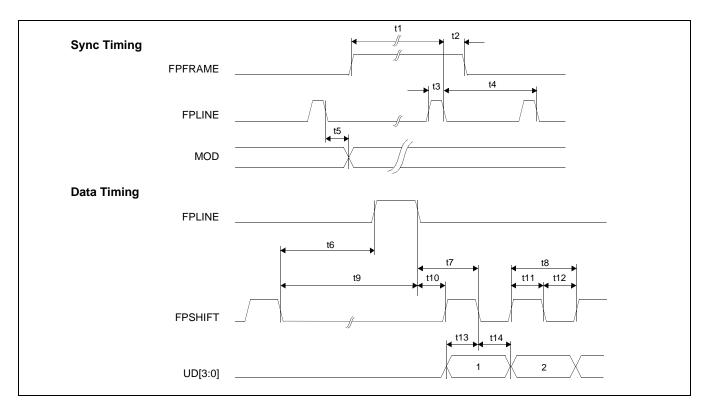

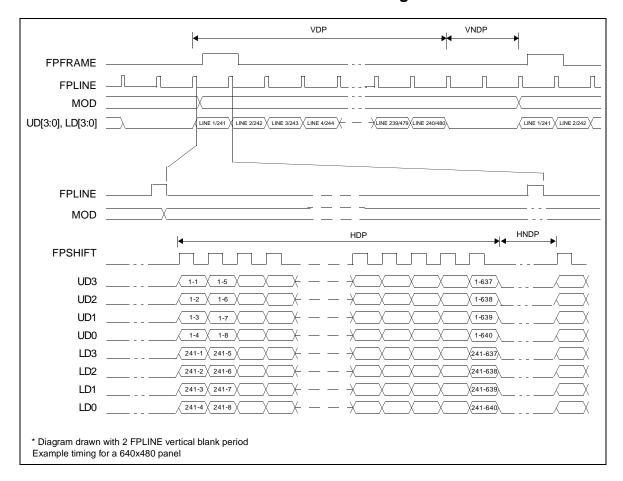

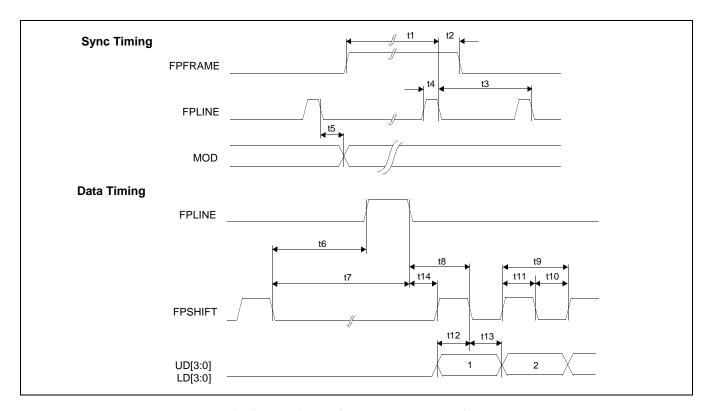

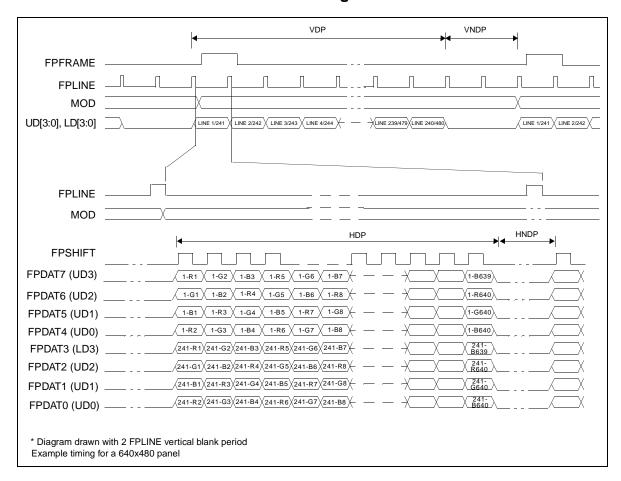

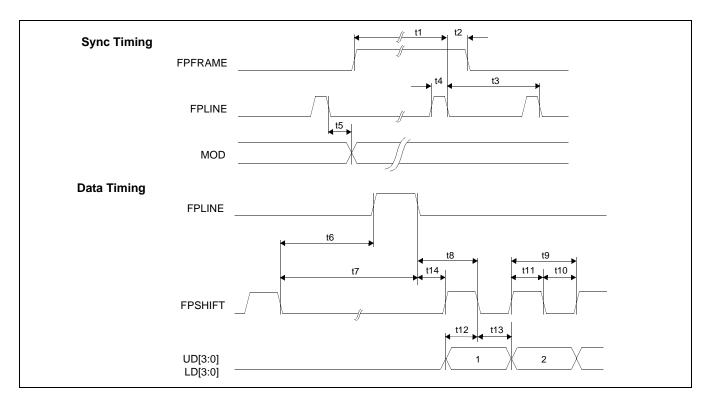

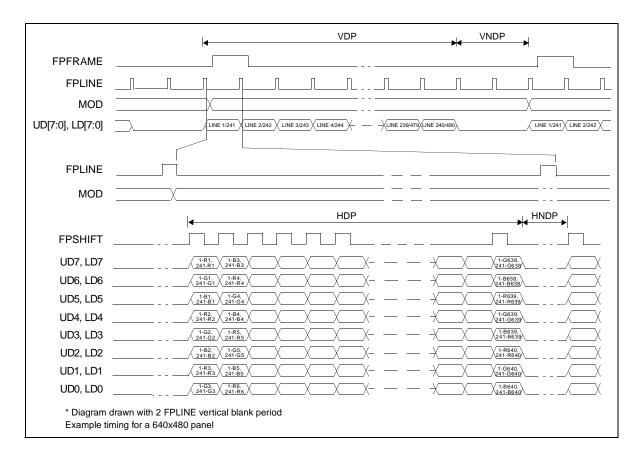

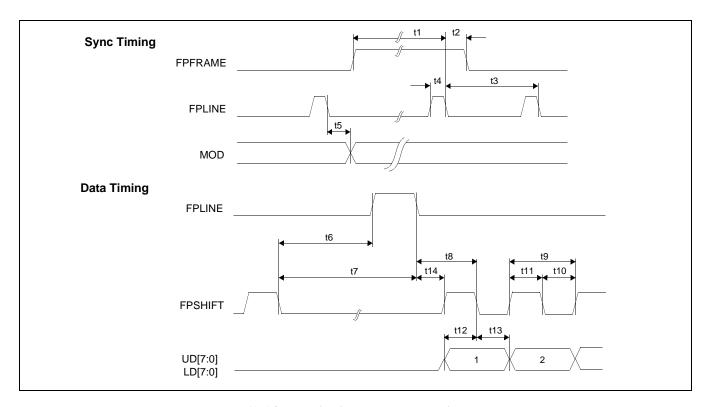

|   |     | 7.5.1    | 4-Bit Single Monochrome Passive LCD Panel Timing           |

|   |     | 7.5.2    | 8-Bit Single Monochrome Passive LCD Panel Timing           |

|   |     | 7.5.3    | 4-Bit Single Color Passive LCD Panel Timing                |

|   |     | 7.5.4    | 8-Bit Single Color Passive LCD Panel Timing (Format 1)     |

|   |     | 7.5.5    | 8-Bit Single Color Passive LCD Panel Timing (Format 2)     |

|   |     | 7.5.6    | 16-Bit Single Color Passive LCD Panel Timing               |

|   |     | 7.5.7    | 8-Bit Dual Monochrome Passive LCD Panel Timing             |

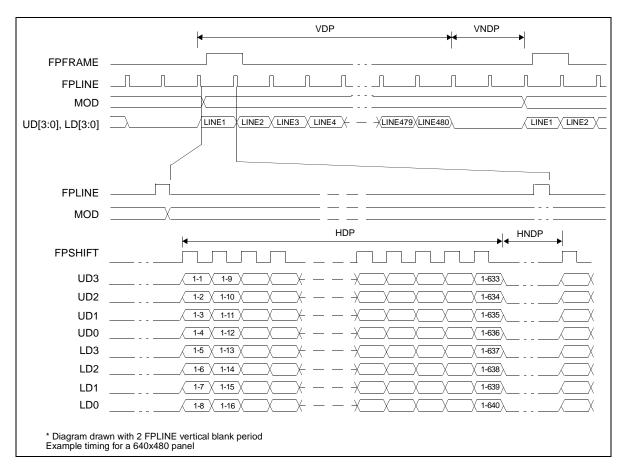

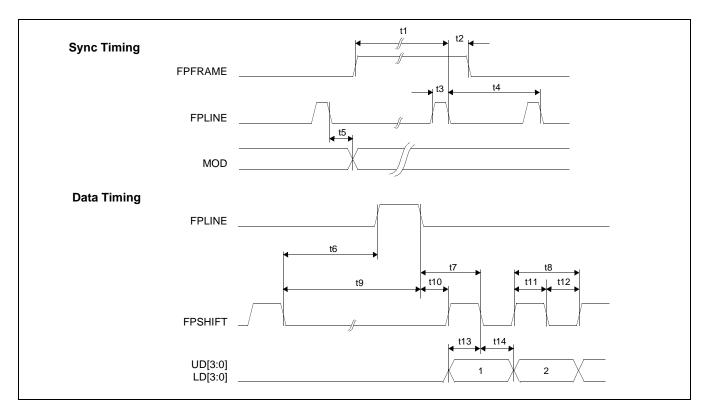

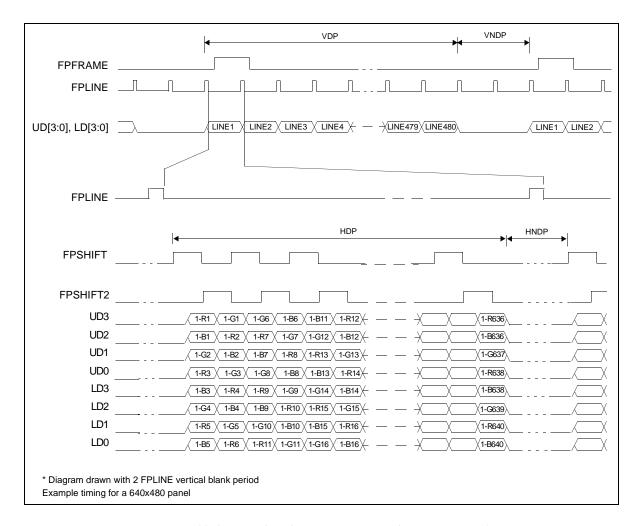

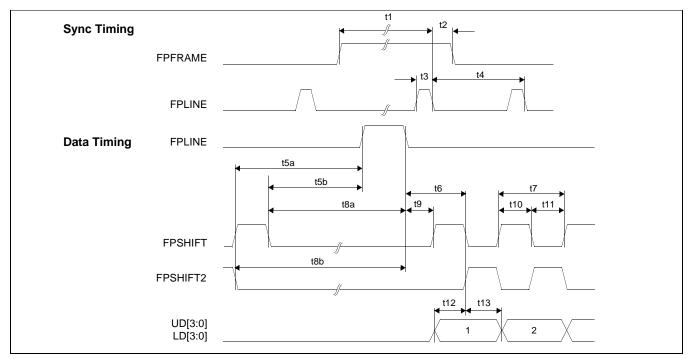

|   |     | 7.5.8    | 8-Bit Dual Color Passive LCD Panel Timing                  |

|   |     | 7.5.9    | 16-Bit Dual Color Passive LCD Panel Timing                 |

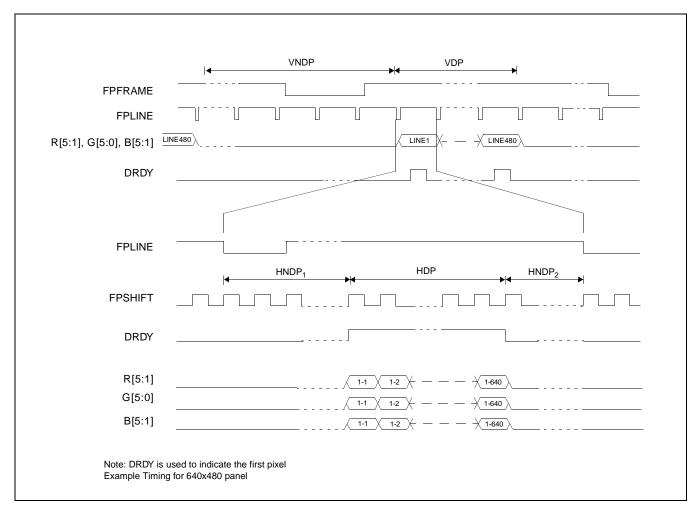

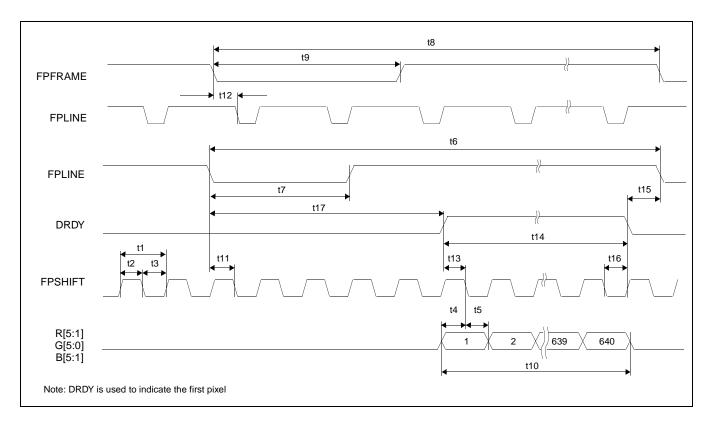

|   |     | 7.5.10   | 16-Bit TFT/D-TFD Panel Timing                              |

|   |     | 7.5.11   | CRT Timing                                                 |

| 8 | Re  | gisters  |                                                            |

|   | 8.1 | Regis    | ster Mapping                                               |

|   | 8.2 | Regis    | ster Descriptions                                          |

|   |     | 8.2.1    | Revision Code Register                                     |

|   |     | 8.2.2    | Memory Configuration Registers                             |

|   |     | 8.2.3    | Panel/Monitor Configuration Registers                      |

|   |     | 8.2.4    | Display Configuration Registers                            |

|    | 8     | .2.5   | Clock Configuration Register       |

|----|-------|--------|------------------------------------|

|    | 8     | .2.6   | Power Save Configuration Registers |

|    | 8     | .2.7   | Miscellaneous Registers            |

|    | 8     | .2.8   | Look-Up Table Registers            |

|    | 8     | .2.9   | Ink/Cursor Registers               |

| 9  | Disp  | lay Bu | ffer                               |

|    | 9.1   | Image  | Buffer                             |

|    | 9.2   | Ink/C  | ursor Buffers                      |

|    | 9.3   | Half I | Frame Buffer                       |

| 10 | Disp  | lay Co | nfiguration                        |

|    | 10.1  | Displa | ay Mode Data Format                |

|    | 10.2  | Image  | Manipulation                       |

| 11 | Look  | -Up Ta | able Architecture                  |

|    | 11.1  | Mono   | chrome Modes                       |

|    | 11.2  | Color  | Modes                              |

| 12 | Ink/C | ursor  | Architecture                       |

|    | 12.1  | Ink/C  | ursor Buffers                      |

|    | 12.2  | Ink/C  | ursor Data Format                  |

|    | 12.3  | Ink/C  | ursor Image Manipulation           |

|    | 1     | 2.3.1  | Ink Image                          |

|    | 1     | 2.3.2  | Cursor Image                       |

| 13 | Swiv  | elViev | v™                                 |

|    | 13.1  | Conce  | ept                                |

|    | 13.2  | Image  | Manipulation in SwivelView         |

|    | 13.3  | •      | cal Memory Requirement             |

|    |       |        | ations                             |

| 14 | Cloc  | king . |                                    |

|    | 14.1  | Maxii  | num MCLK: PCLK Ratios              |

|    | 14.2  | Frame  | e Rate Calculation                 |

|    | 14.3  | Bandy  | width Calculation                  |

| 15 | Powe  | er Sav | e Modes                            |

| 16 | Mech  | nanica | l Data                             |

# **List of Tables**

| Table 5-1:  | Host Interface Pin Descriptions                                           | . 23 |

|-------------|---------------------------------------------------------------------------|------|

| Table 5-2:  | Memory Interface Pin Descriptions                                         | . 29 |

| Table 5-2:  | LCD Interface Pin Descriptions                                            | . 31 |

| Table 5-3:  | CRT Interface Pin Descriptions                                            | . 31 |

| Table 5-4:  | Miscellaneous Interface Pin Descriptions                                  | . 32 |

| Table 5-5:  | Summary of Power On/Reset Options                                         | . 33 |

| Table 5-6:  | CPU Interface Pin Mapping                                                 | . 34 |

| Table 5-7:  | Memory Interface Pin Mapping                                              | . 35 |

| Table 5-8:  | LCD Interface Pin Mapping                                                 | . 35 |

| Table 6-1:  | Absolute Maximum Ratings                                                  | . 37 |

| Table 6-2:  | Recommended Operating Conditions                                          | . 37 |

| Table 6-3:  | Electrical Characteristics for VDD = 5.0V typical                         | . 38 |

| Table 6-4:  | Electrical Characteristics for VDD = 3.3V typical                         | . 39 |

| Table 6-5:  | Electrical Characteristics for VDD = 3.0V typical                         | . 40 |

| Table 7-1:  | SH-4 Timing                                                               | . 42 |

| Table 7-2:  | SH-3 Timing                                                               |      |

| Table 7-3:  | MC68000 Timing                                                            |      |

| Table 7-4:  | MC68030 Timing                                                            |      |

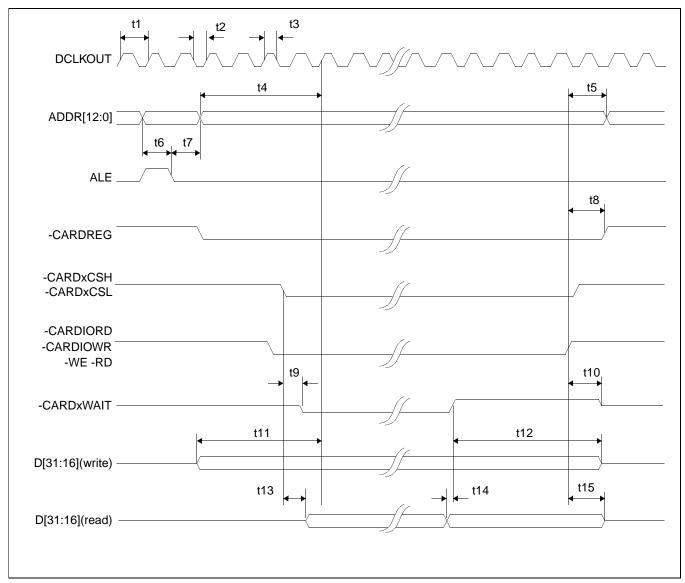

| Table 7-5:  | PC Card Timing                                                            | . 50 |

| Table 7-6:  | Generic Timing                                                            |      |

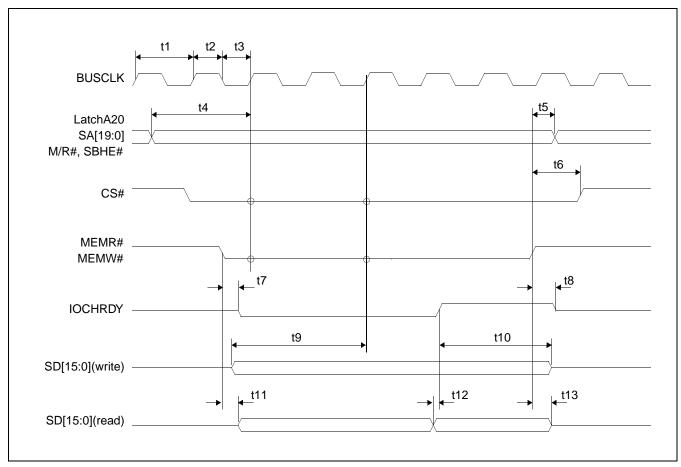

| Table 7-7:  | MIPS/ISA Timing                                                           | . 54 |

| Table 7-8:  | Philips Timing                                                            |      |

| Table 7-9:  | Clock Input Requirements for BUSCLK using Philips local bus               | . 57 |

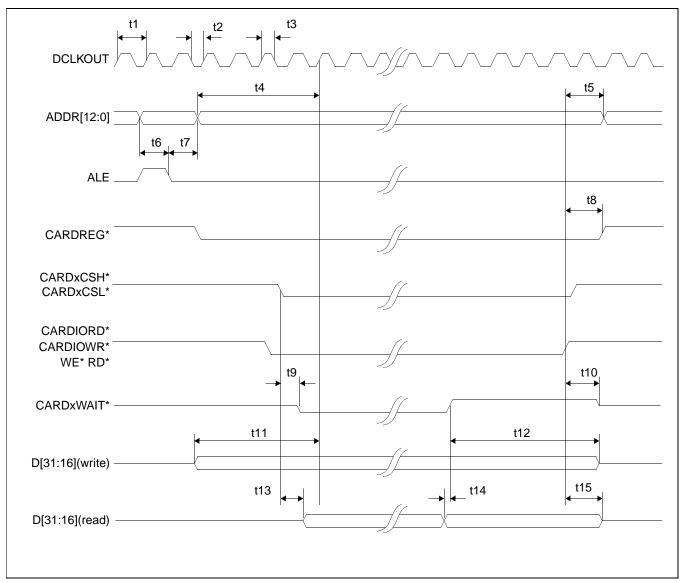

| Table 7-10: | Toshiba Timing                                                            |      |

|             | Clock Input Requirements for BUSCLK using Toshiba local bus               |      |

|             | Power PC Timing                                                           |      |

|             | Clock Input Requirements for CLKI divided down internally (MCLK = CLKI/2) |      |

|             | Clock Input Requirements for CLKI                                         |      |

|             | EDO-DRAM Read/Write/Read-Write Timing                                     |      |

| Table 7-16: | EDO-DRAM CAS Before RAS Refresh Timing                                    | . 67 |

|             | EDO-DRAM Self-Refresh Timing                                              |      |

|             | FPM-DRAM Read/Write/Read-Write Timing                                     |      |

|             | FPM-DRAM CAS Before RAS Refresh Timing                                    |      |

|             | FPM-DRAM CBR Self-Refresh Timing                                          |      |

|             | LCD Panel Power Off/ Power On                                             |      |

|             | Power Save Status and Local Bus Memory Access Relative to Power Save Mode |      |

|             | 4-Bit Single Monochrome Passive LCD Panel A.C. Timing                     |      |

|             | 8-Bit Single Monochrome Passive LCD Panel A.C. Timing                     |      |

|             | 4-Bit Single Color Passive LCD Panel A.C. Timing                          |      |

| Table 7-26: | 8-Bit Single Color Passive LCD Panel A.C. Timing (Format 1)               | . 84 |

| Table 7-27: | 8-Bit Single Color Passive LCD Panel A.C. Timing (Format 2)   |

|-------------|---------------------------------------------------------------|

| Table 7-28: | 16-Bit Single Color Passive LCD Panel A.C. Timing             |

| Table 7-29: | 8-Bit Dual Monochrome Passive LCD Panel A.C. Timing           |

| Table 7-30: | 8-Bit Dual Color Passive LCD Panel A.C. Timing                |

| Table 7-31: | 16-Bit Dual Color Passive LCD Panel A.C. Timing               |

| Table 7-32: | TFT/D-TFD A.C. Timing                                         |

| Table 8-1:  | SED1355 Addressing                                            |

| Table 8-2:  | DRAM Refresh Rate Selection                                   |

| Table 8-3:  | Panel Data Width Selection                                    |

| Table 8-4:  | FPLINE Polarity Selection                                     |

| Table 8-5:  | FPFRAME Polarity Selection                                    |

| Table 8-6:  | Simultaneous Display Option Selection                         |

| Table 8-7:  | Bit-per-pixel Selection                                       |

| Table 8-8:  | Pixel Panning Selection                                       |

| Table 8-9:  | PCLK Divide Selection                                         |

| Table 8-10: | Suspend Refresh Selection                                     |

| Table 8-11: | MA/GPIO Pin Functionality                                     |

| Table 8-12: | Minimum Memory Timing Selection                               |

| Table 8-13: | RAS#-to-CAS# Delay Timing Select                              |

| Table 8-14: | RAS Precharge Timing Select                                   |

|             | Optimal NRC, NRP, and NRCD values at maximum MCLK frequency   |

| Table 8-16: | Minimum Memory Timing Selection                               |

| Table 8-17: | Ink/Cursor Selection                                          |

| Table 8-18: | Ink/Cursor Start Address Encoding                             |

| Table 8-19: | Recommended Alternate FRM Scheme                              |

| Table 9-1:  | SED1355 Addressing                                            |

| Table 12-1: | Ink/Cursor Start Address Encoding                             |

| Table 12-2: | Ink/Cursor Color Select                                       |

| Table 13-2  | Minimum DRAM Size Required for SwivelView                     |

| Table 14-1: | Maximum PCLK Frequency with EDO-DRAM                          |

| Table 14-2: | Maximum PCLK Frequency with FPM-DRAM                          |

| Table 14-3: | Example Frame Rates with Ink Disabled                         |

| Table 14-4: | Number of MCLKs required for various memory access            |

| Table 14-5: | Total # MCLKs taken for Display refresh                       |

| Table 14-6: | Theoretical Maximum Bandwidth M byte/sec, Cursor/Ink disabled |

| Table 15-1: | Power Save Mode Function Summary                              |

| Table 15-2: | Pin States in Power-save Modes                                |

# **List of Figures**

| Figure 3-1:  | Typical System Diagram (SH-4 Bus)                                                                           |

|--------------|-------------------------------------------------------------------------------------------------------------|

| Figure 3-2:  | Typical System Diagram (SH-3 Bus)                                                                           |

| Figure 3-3:  | Typical System Diagram (MC68K Bus 1, 16-Bit 68000)                                                          |

| Figure 3-4:  | Typical System Diagram (MC68K Bus 2, 32-Bit 68030)                                                          |

| Figure 3-5:  | Typical System Diagram (Generic Bus)                                                                        |

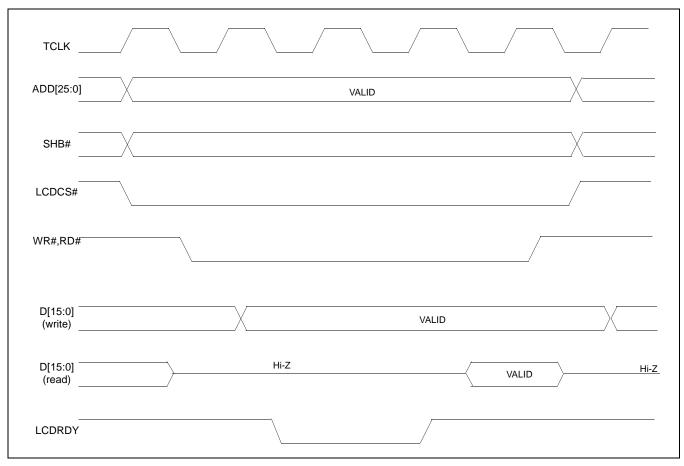

| Figure 3-6:  | Typical System Diagram (NEC VR41xx (MIPS) Bus)                                                              |

| Figure 3-7:  | Typical System Diagram (Philips PR31500/PR31700 Bus)                                                        |

| Figure 3-8:  | Typical System Diagram (Toshiba TX3912 Bus)                                                                 |

| Figure 3-9:  | Typical System Diagram (Power PC Bus)                                                                       |

| Figure 3-10: | Typical System Diagram (PC Card (PCMCIA) Bus)                                                               |

| Figure 5-1:  | Pinout Diagram                                                                                              |

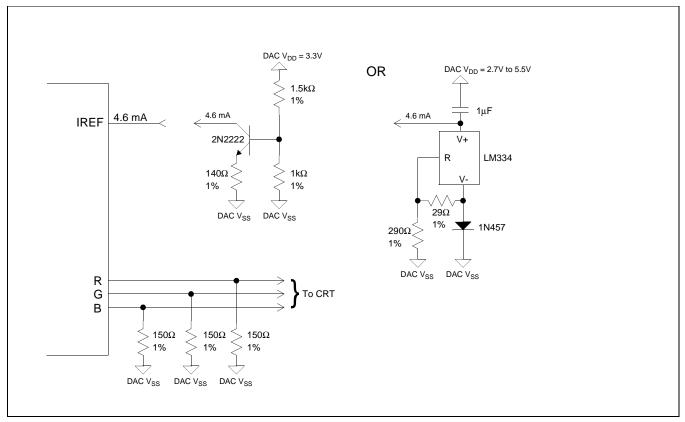

| Figure 5-3:  | External Circuitry for CRT Interface                                                                        |

| Figure 7-1:  | SH-4 Timing                                                                                                 |

| Figure 7-2:  | SH-3 Timing                                                                                                 |

| Figure 7-3:  | MC68000 Timing                                                                                              |

| Figure 7-4:  | MC68030 Timing                                                                                              |

| Figure 7-5:  | PC Card Timing                                                                                              |

| Figure 7-6:  | Generic Timing                                                                                              |

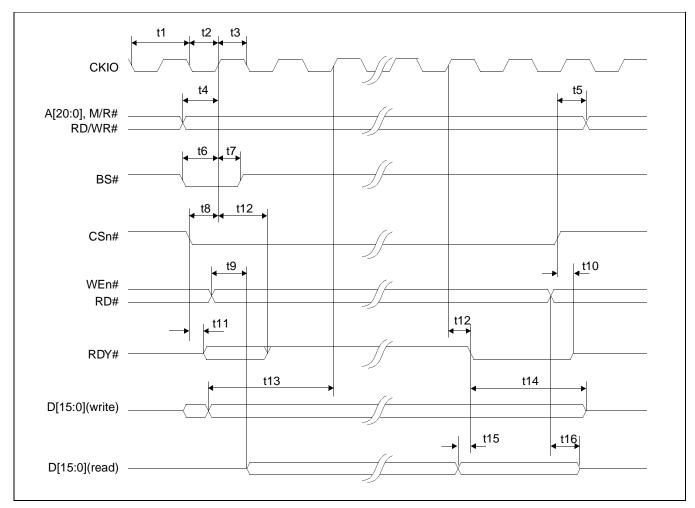

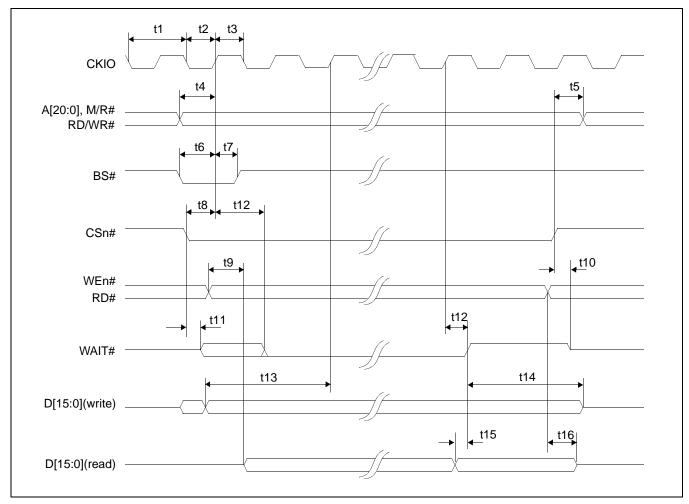

| Figure 7-7:  | MIPS/ISA Timing                                                                                             |

| Figure 7-8:  | Philips Timing                                                                                              |

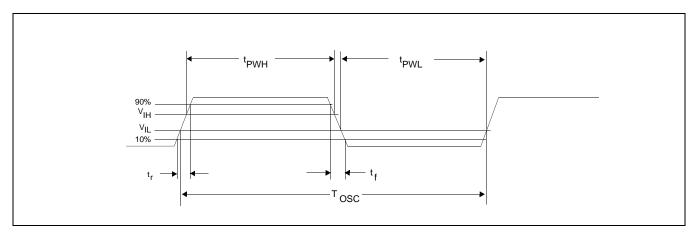

| Figure 7-9:  | Clock Input Requirement                                                                                     |

| Figure 7-10: | Toshiba Timing                                                                                              |

| Figure 7-11: | Clock Input Requirement                                                                                     |

| Figure 7-12: | Power PC Timing                                                                                             |

| Figure 7-13: | Clock Input Requirement                                                                                     |

| Figure 7-14: | EDO-DRAM Read/Write Timing                                                                                  |

| Figure 7-15: | EDO-DRAM Read-Write Timing                                                                                  |

| Figure 7-16: | EDO-DRAM CAS Before RAS Refresh Timing                                                                      |

| Figure 7-17: | EDO-DRAM Self-Refresh Timing                                                                                |

| Figure 7-18: | FPM-DRAM Read/Write Timing                                                                                  |

| Figure 7-19: | FPM-DRAM Read-Write Timing                                                                                  |

| Figure 7-20: | FPM-DRAM CAS Before RAS Refresh Timing                                                                      |

| Figure 7-21: | FPM-DRAM Self-Refresh Timing                                                                                |

| Figure 7-22: | $LCD\ Panel\ Power\ Off\ /\ Power\ On\ Timing.\ Drawn\ with\ LCDPWR\ set\ to\ active\ high\ polarity\ . 75$ |

| Figure 7-23: | Power Save Status and Local Bus Memory Access Relative to Power Save Mode 76                                |

| Figure 7-24: | 4-Bit Single Monochrome Passive LCD Panel Timing                                                            |

| Figure 7-25: | 4-Bit Single Monochrome Passive LCD Panel A.C. Timing                                                       |

| Figure 7-26: | 8-Bit Single Monochrome Passive LCD Panel Timing                                                            |

| Figure 7-27: | 8-Bit Single Monochrome Passive LCD Panel A.C. Timing                                                       |

| Figure 7-28: | 4-Bit Single Color Passive LCD Panel Timing                                                                 |

| Figure 7-29: | 4-Bit Single Color Passive LCD Panel A.C. Timing                                                            |

| Figure 7-30: | 8-Bit Single Color Passive LCD Panel Timing (Format 1)                             | . 83 |

|--------------|------------------------------------------------------------------------------------|------|

| Figure 7-31: | 8-Bit Single Color Passive LCD Panel A.C. Timing (Format 1)                        | . 84 |

| Figure 7-32: | 8-Bit Single Color Passive LCD Panel Timing (Format 2)                             | . 85 |

| Figure 7-33: | 8-Bit Single Color Passive LCD Panel A.C. Timing (Format 2)                        | . 86 |

| Figure 7-34: | 16-Bit Single Color Passive LCD Panel Timing                                       | . 87 |

| Figure 7-35: | 16-Bit Single Color Passive LCD Panel A.C. Timing                                  | . 88 |

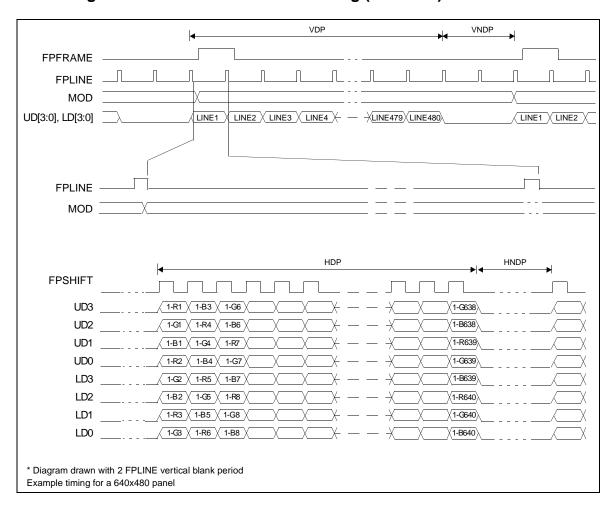

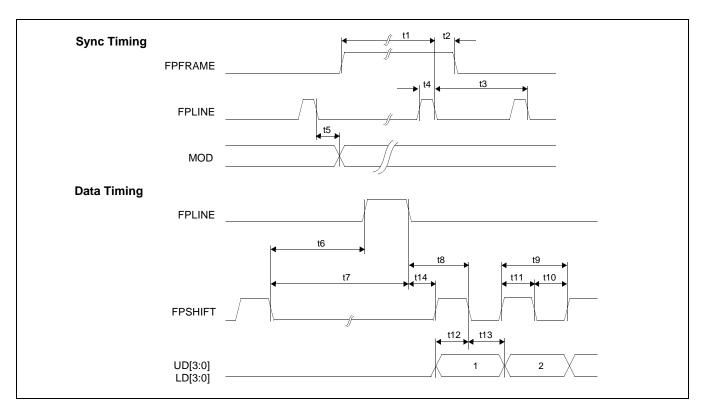

| Figure 7-36: | 8-Bit Dual Monochrome Passive LCD Panel Timing                                     | . 89 |

| Figure 7-37: | 8-Bit Dual Monochrome Passive LCD Panel A.C. Timing                                | . 90 |

| Figure 7-38: | 8-Bit Dual Color Passive LCD Panel Timing                                          | . 91 |

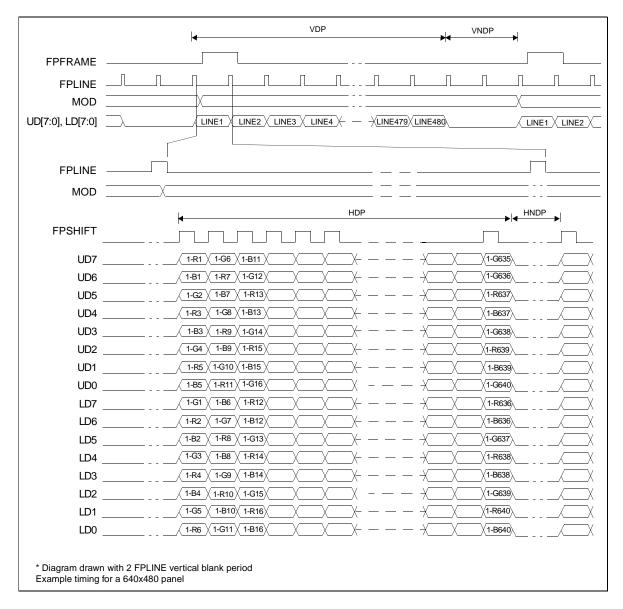

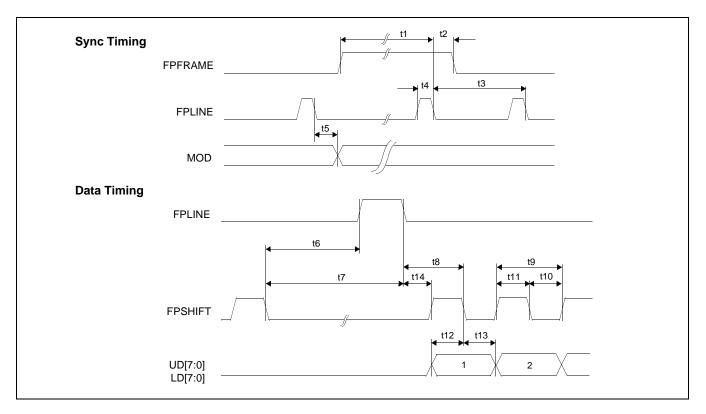

| Figure 7-39: | 8-Bit Dual Color Passive LCD Panel A.C. Timing                                     | . 92 |

| Figure 7-40: | 16-Bit Dual Color Passive LCD Panel Timing                                         | . 93 |

| Figure 7-41: | 16-Bit Dual Color Passive LCD Panel A.C. Timing                                    | . 94 |

| Figure 7-42: | 16-Bit TFT/D-TFD Panel Timing                                                      | . 95 |

| Figure 7-43: | TFT/D-TFD A.C. Timing                                                              | . 96 |

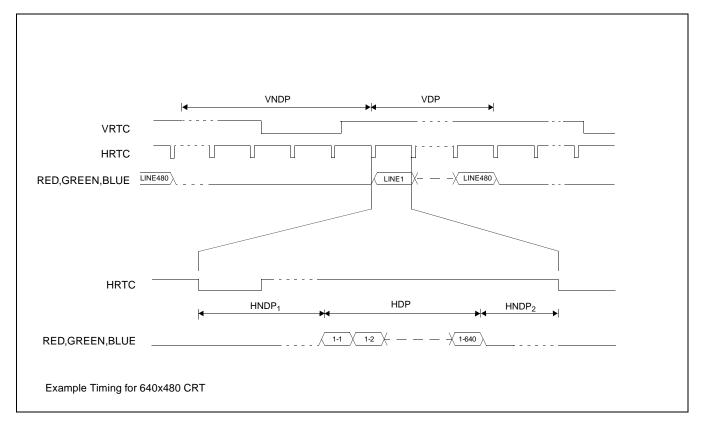

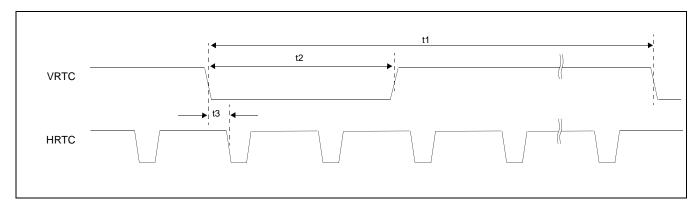

| Figure 7-44: | CRT Timing                                                                         | . 98 |

| Figure 7-45: | CRT A.C. Timing                                                                    | . 99 |

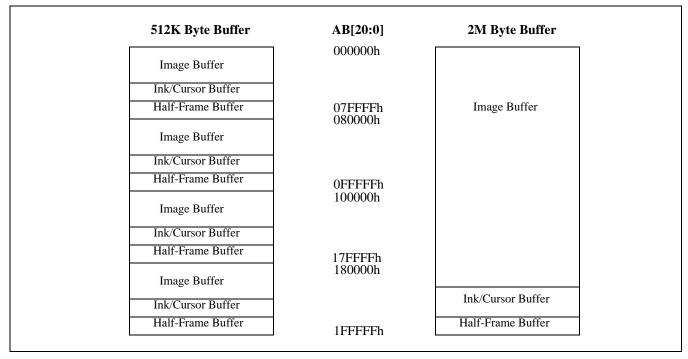

| Figure 9-1:  | Display Buffer Addressing                                                          | 123  |

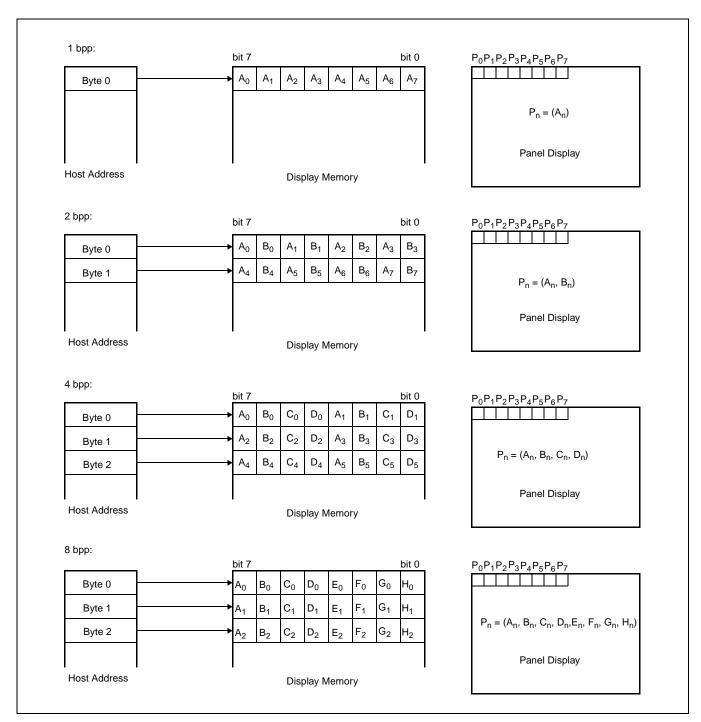

| Figure 10-1: | 1/2/4/8 Bit-per-pixel Format Memory Organization                                   | 125  |

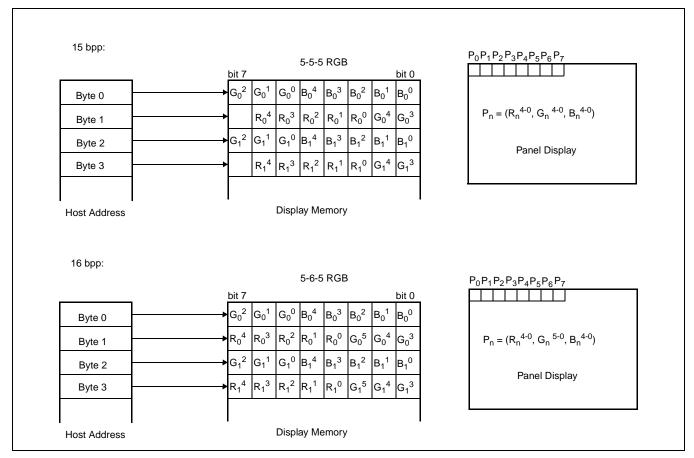

| Figure 10-2: | 15/16 Bit-per-pixel Format Memory Organization                                     | 126  |

| Figure 10-3: | Image Manipulation                                                                 | 127  |

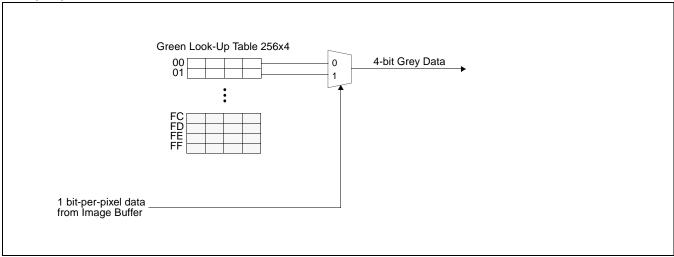

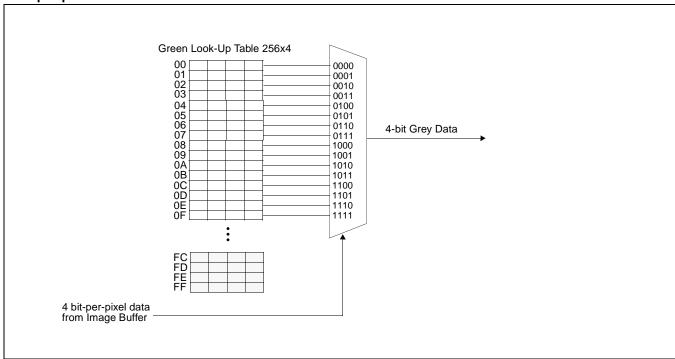

| Figure 11-1: | 1 Bit-per-pixel Monochrome Mode Data Output Path                                   | 128  |

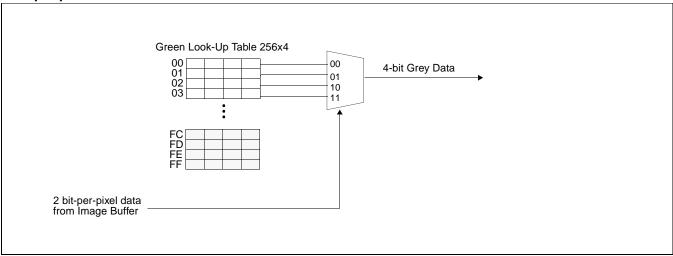

| Figure 11-2: | 2 Bit-per-pixel Monochrome Mode Data Output Path                                   | 128  |

| Figure 11-3: | 4 Bit-per-pixel Monochrome Mode Data Output Path                                   | 129  |

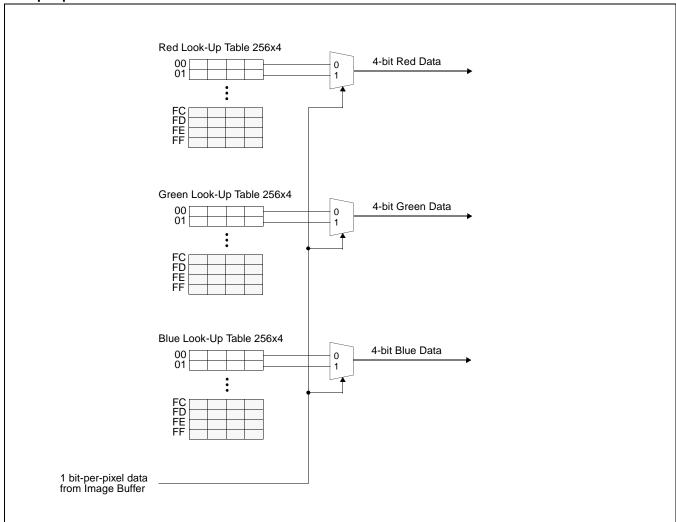

| Figure 11-4: | 1 Bit-per-pixel Color Mode Data Output Path                                        | 130  |

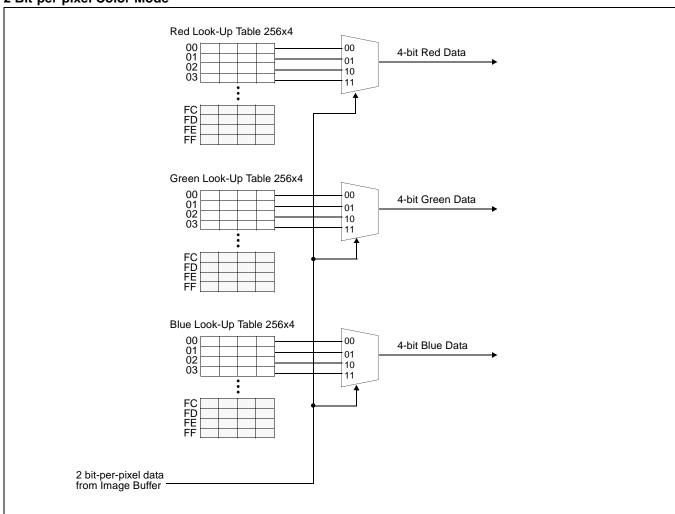

| Figure 11-5: | 2 Bit-per-pixel Color Mode Data Output Path                                        | 131  |

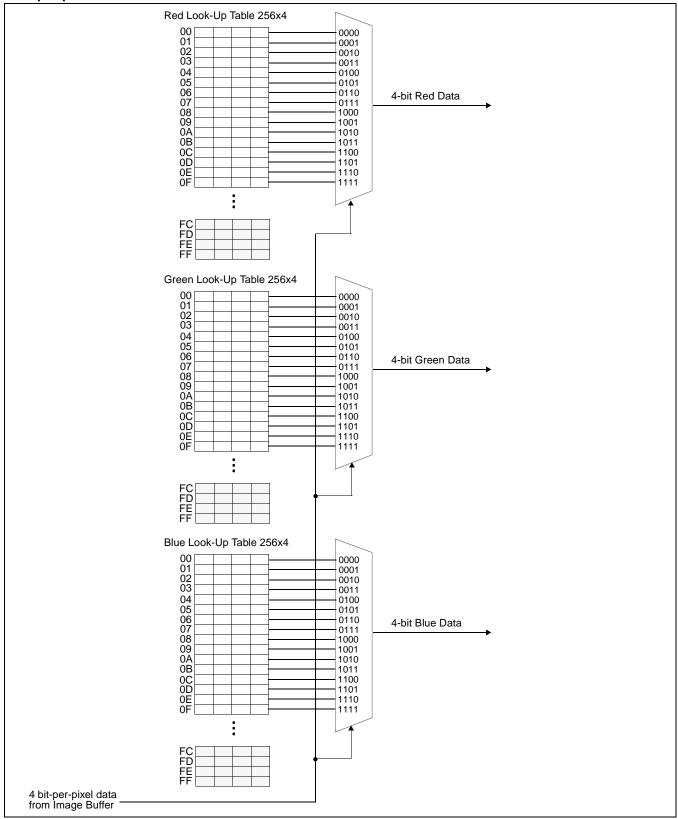

| Figure 11-6: | 4 Bit-per-pixel Color Mode Data Output Path                                        | 132  |

| Figure 11-7: | 8 Bit-per-pixel Color Mode Data Output Path                                        | 133  |

| Figure 12-1: | Ink/Cursor Data Format                                                             | 134  |

| Figure 12-2: | Cursor Positioning                                                                 | 135  |

| Figure 13-1: | Relationship Between The Screen Image and the Image Residing in the Display Buffer | 136  |

| Figure 16-1: | Mechanical Drawing QFP15                                                           | 149  |

### 1 Introduction

## 1.1 Scope

This is the Hardware Functional Specification for the SED1355 Embedded RAMDAC LCD/CRT Controller. Included in this document are timing diagrams, AC and DC characteristics, register descriptions, and power management descriptions. This document is intended for two audiences: Video Subsystem Designers and Software Developers.

This specification will be updated as appropriate. Please check the Epson Electronics America Website at http://www.eea.epson.com for the latest revision of this document before beginning any development.

We appreciate your comments on our documentation. Please contact us via email at techpubs@erd.epson.com.

# 1.2 Overview Description

The SED1355 is a color/monochrome LCD/CRT graphics controller interfacing to a wide range of CPUs and display devices. The SED1355 architecture is designed to meet the low cost, low power requirements of the embedded markets, such as Mobile Communications, Hand-Held PCs, and Office Automation.

The SED1355 supports multiple CPUs, all LCD panel types, CRT, and additionally provides a number of differentiating features. Products requiring a "Portrait" mode display can take advantage of the SwivelView<sup>TM</sup> feature. Simultaneous, Virtual and Split Screen Display are just some of the display modes supported, while the Hardware Cursor, Ink Layer, and the Memory Enhancement Registers offer substantial performance benefits. These features, combined with the SED1355's Operating System independence, make it an ideal display solution for a wide variety of applications.

#### 2 Features

# 2.1 Memory Interface

- 16-bit DRAM interface:

- EDO-DRAM up to 40MHz data rate (80M bytes/sec.).

- FPM-DRAM up to 25MHz data rate (50M bytes/sec.).

- Memory size options:

- 512K bytes using one 256K×16 device.

- 2M bytes using one 1M×16 device.

- Performance Enhancement Register to tailor the memory control output timing for the DRAM device.

### 2.2 CPU Interface

- Supports the following interfaces:

- 8/16-bit SH-4 bus interface.

- 8/16-bit SH-3 bus interface.

- 8/16-bit interface to 8/16/32-bit MC68000 microprocessors/microcontrollers.

- 8/16-bit interface to 8/16/32-bit MC68030 microprocessors/microcontrollers.

- Philips PR31500/PR31700 (MIPS).

- Toshiba TX3912 (MIPS)

- 16-bit Power PC (MPC821) microprocessor.

- 16-bit Epson E0C33 microprocessor.

- PC Card (PCMCIA).

- StrongARM (PC Card).

- NEC VR41xx (MIPS).

- ISA bus.

- Supports the following interface with external logic:

- GX486 microprocessor.

- One-stage write buffer for minimum wait-state CPU writes.

- Registers are memory-mapped the M/R# pin selects between the display buffer and register address space.

- The complete 2M byte display buffer address space is addressable as a single linear address space through the 21-bit address bus.

## 2.3 Display Support

- 4/8-bit monochrome passive LCD interface.

- 4/8/16-bit color passive LCD interface.

- · Single-panel, single-drive displays.

- Dual-panel, dual-drive displays.

- Direct support for 9/12-bit TFT/D-TFD; 18-bit TFT/D-TFD is supported up to 64K color depth (16-bit data).

- Embedded RAMDAC (DAC) with direct analog CRT drive.

- Simultaneous display of CRT and passive or TFT/D-TFD panels.

# 2.4 Display Modes

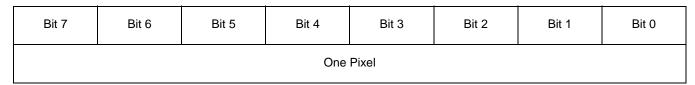

- 1/2/4/8/15/16 bit-per-pixel (bpp) support on LCD/CRT.

- Up to 16 shades of gray using FRM on monochrome passive LCD panels.

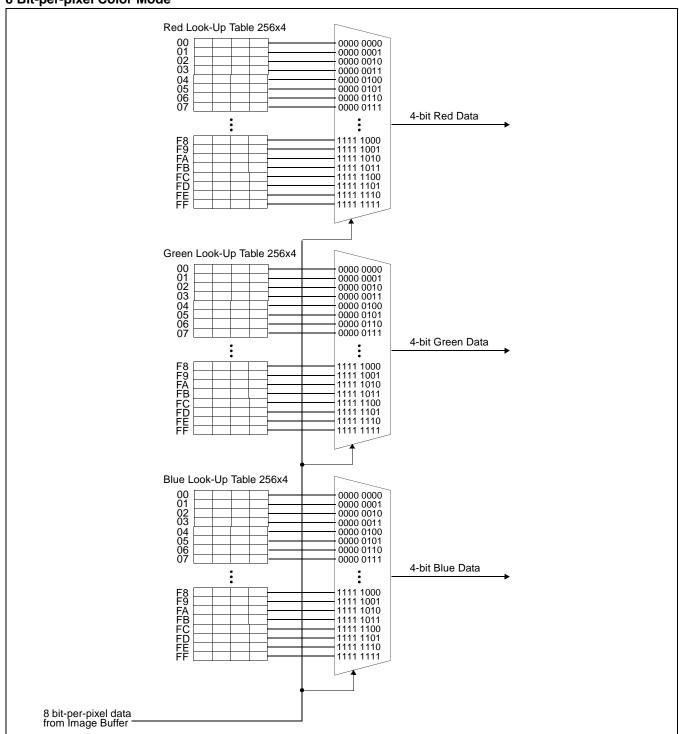

- Up to 4096 colors on passive LCD panels; three 256x4 Look-Up Tables (LUT) are used to map 1/2/4/8 bpp modes into these colors, 15/16 bpp modes are mapped directly using the 4 most significant bits of the red, green and blue colors.

- Up to 64K colors on TFT/D-TFD LCD panels and CRT; three 256x4 Look-Up Tables are used to map 1/2/4/8 bpp modes into 4096 colors, 15/16 bpp modes are mapped directly.

## 2.5 Display Features

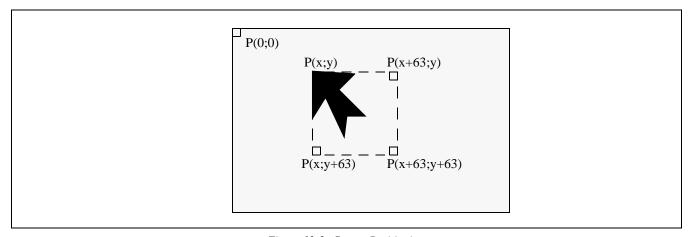

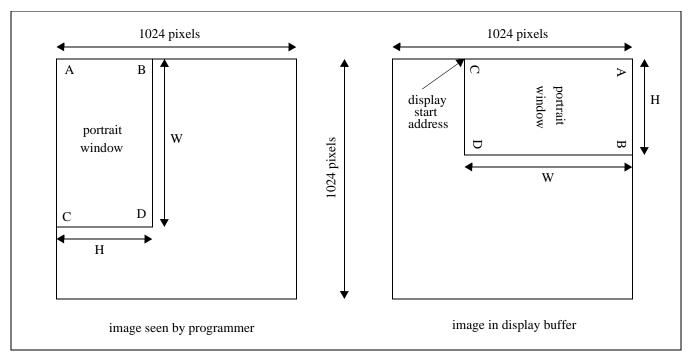

- SwivelView<sup>TM</sup>: direct hardware 90° rotation of display image for "portrait" mode display.

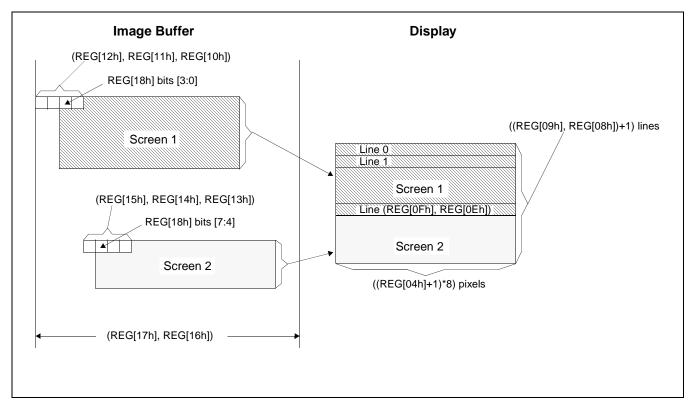

- Split Screen Display: allows two different images to be simultaneously viewed on the same display.

- Virtual Display Support: displays images larger than the display size through the use of panning.

- · Double Buffering/multi-pages: provides smooth animation and instantaneous screen update.

- Acceleration of screen updates by allocating full display memory bandwidth to CPU (see REG[23h] bit 7).

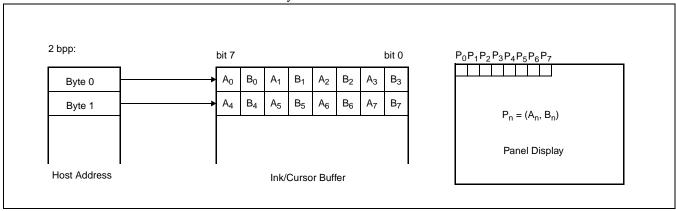

- Hardware 64x64 pixel 2-bit cursor or full screen 2-bit ink layer.

- Simultaneous display of CRT and passive panel or TFT/D-TFD panel.

- Normal mode for cases where LCD and CRT screen sizes are identical.

- Line-doubling for simultaneous display of 240-line images on 240-line LCD and 480-line CRT.

- Even-scan or interlace modes for simultaneous display of 480-line images on 240-line LCD and 480-line CRT.

### 2.6 Clock Source

- Single clock input for both the pixel and memory clocks.

- Memory clock can be input clock or (input clock/2), providing flexibility to use CPU bus clock as input.

- Pixel clock can be the memory clock, (memory clock/2), (memory clock/3) or (memory clock/4).

### 2.7 Miscellaneous

- The memory data bus, MD[15:0], is used to configure the chip at power-on.

- Three General Purpose Input/Output pins, GPIO[3:1], are available if the upper Memory Address pins are not required for asymmetric DRAM support.

- Suspend power save mode can be initiated by either hardware or software.

- The SUSPEND# pin is used either as an input to initiate Suspend mode, or as a General Purpose

Output that can be used to control the LCD backlight. Power-on polarity is selected by an MD

configuration pin.

- Operating voltages from 2.7 volts to 5.5 volts are supported

- 128-pin QFP15 surface mount package

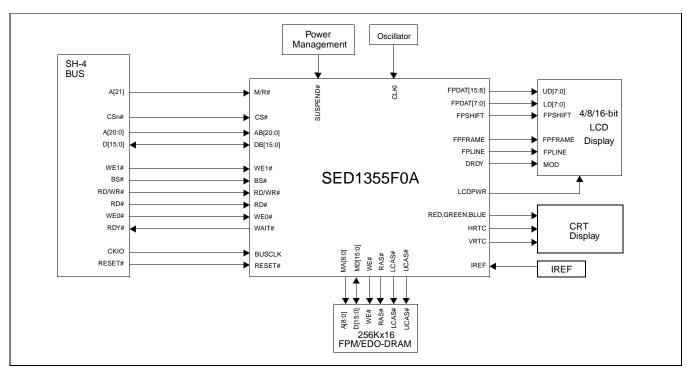

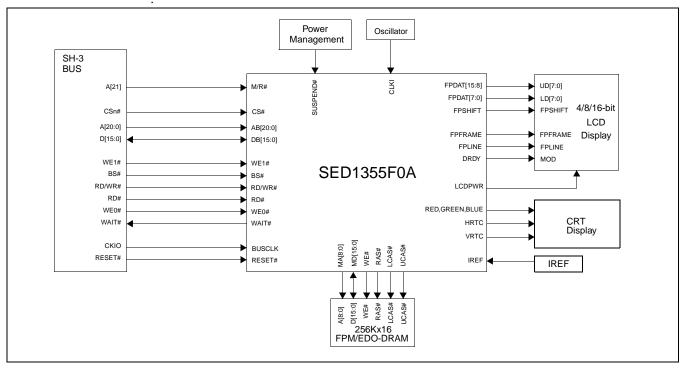

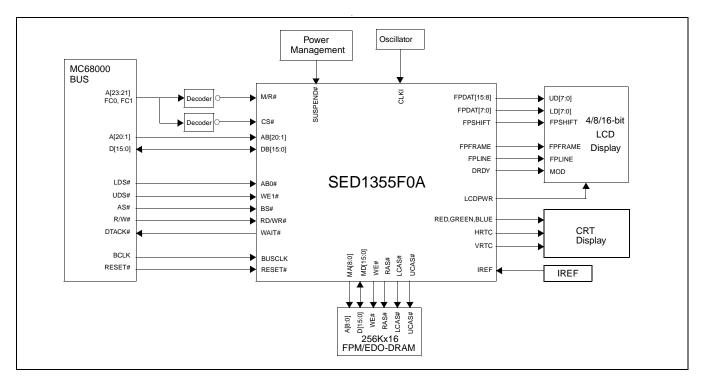

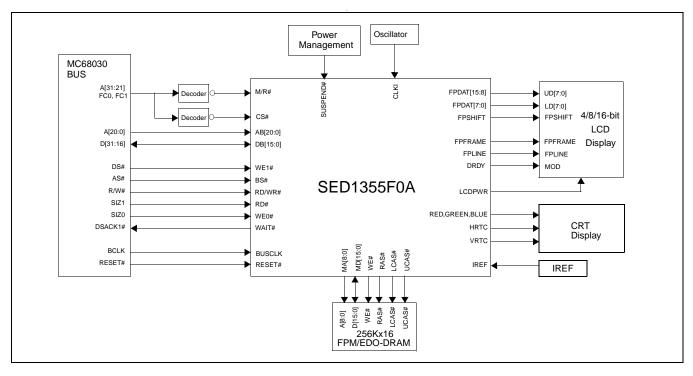

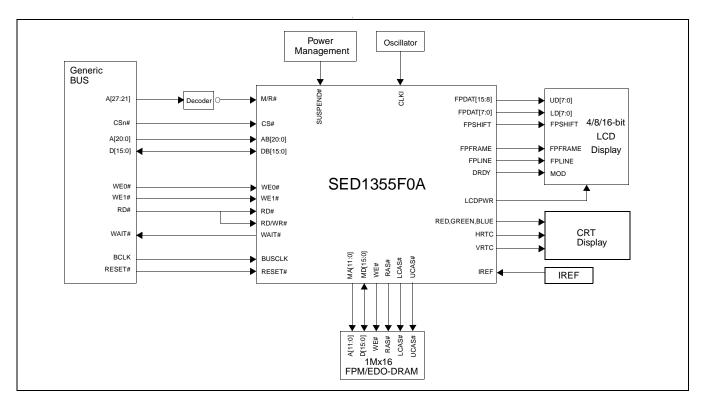

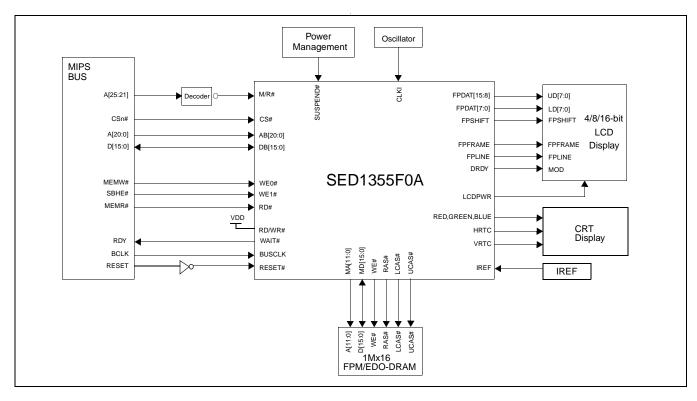

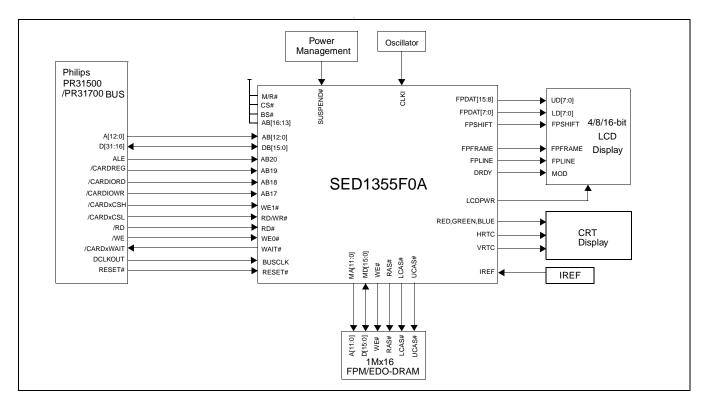

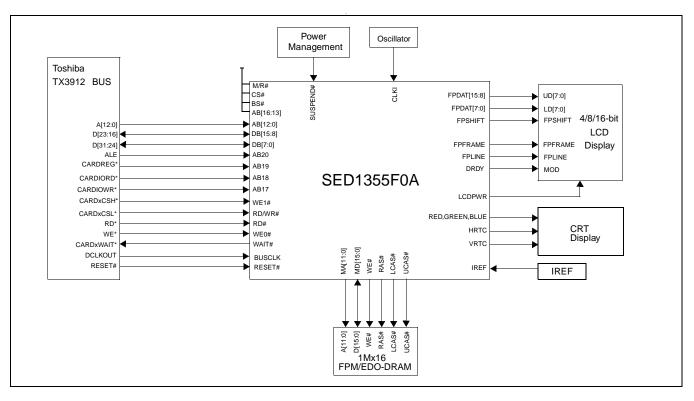

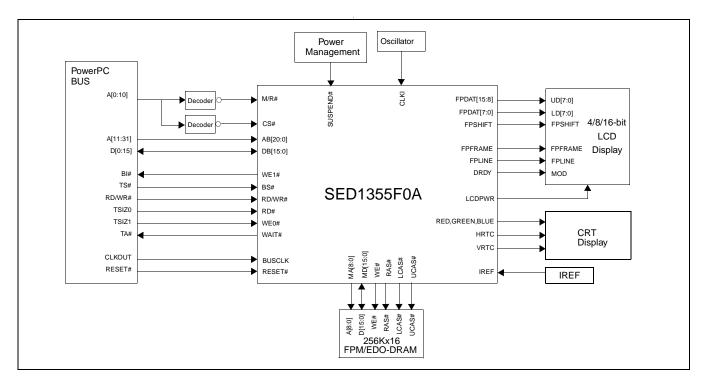

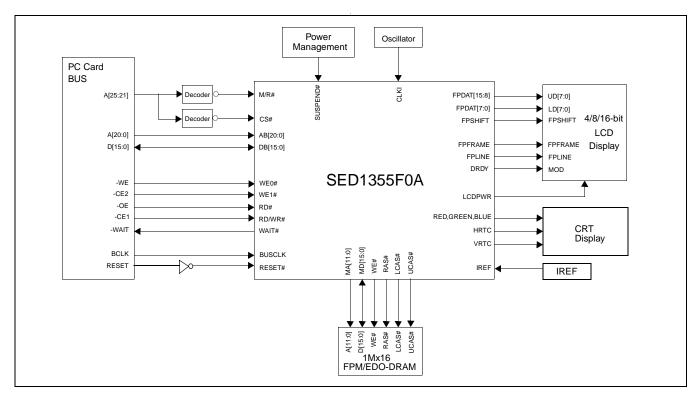

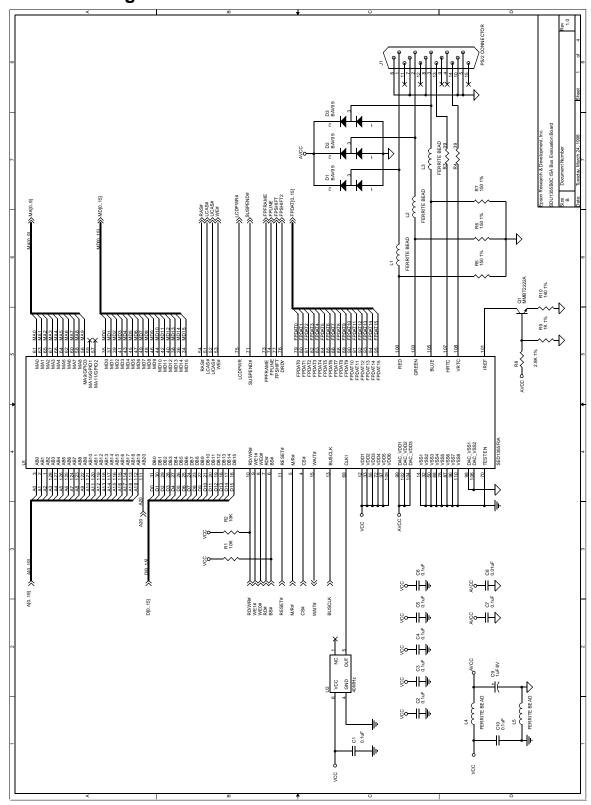

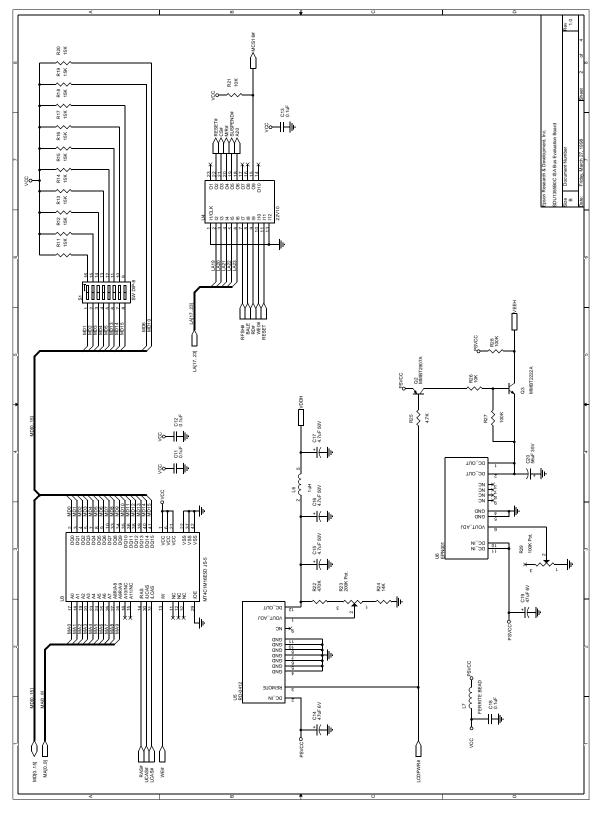

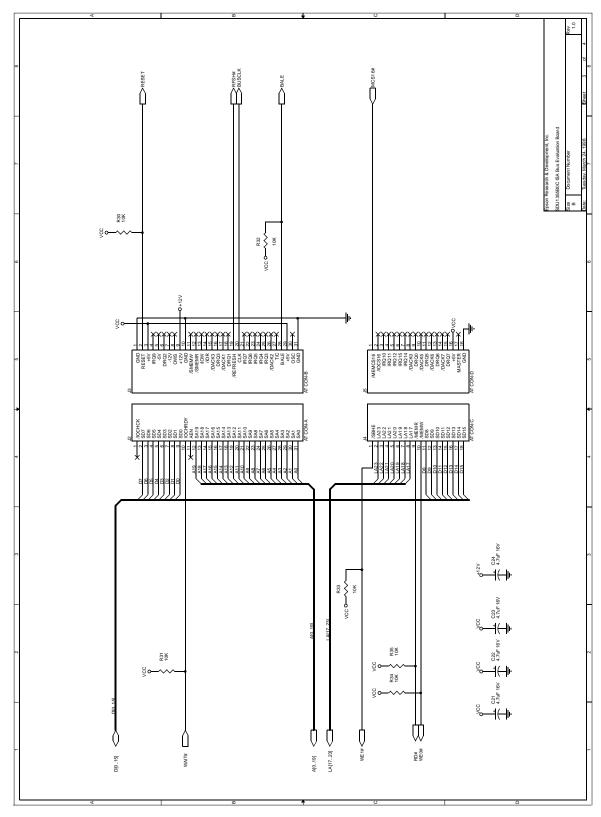

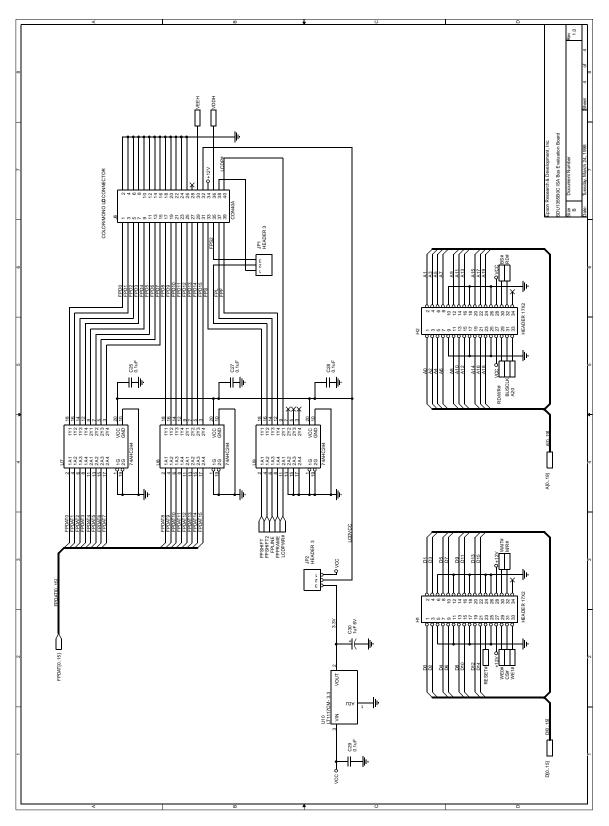

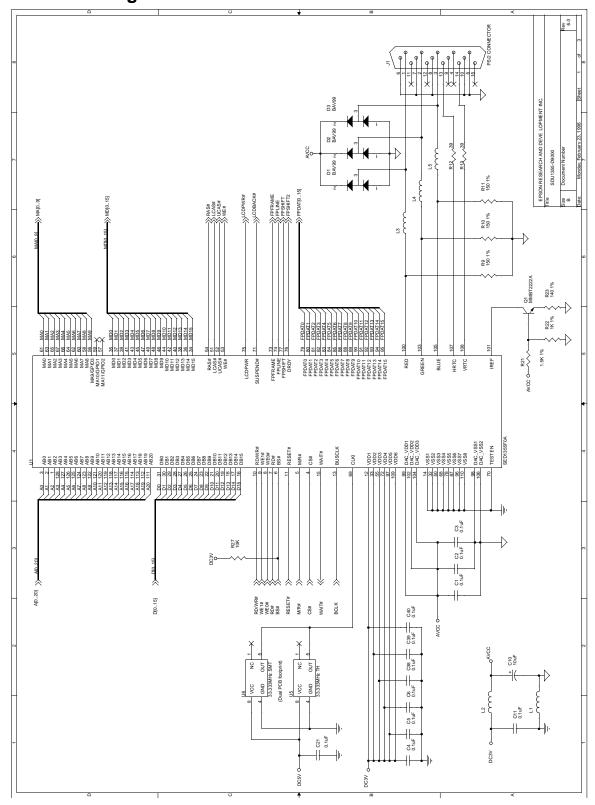

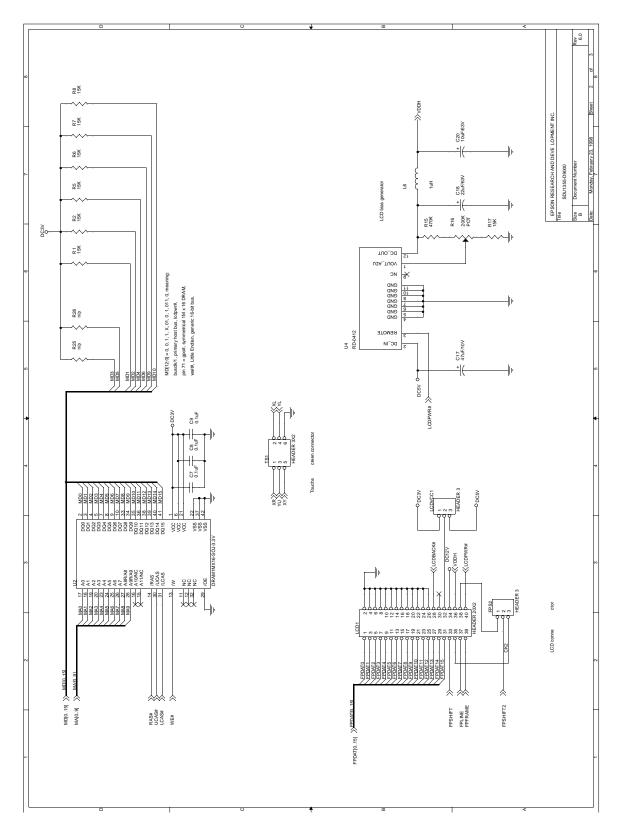

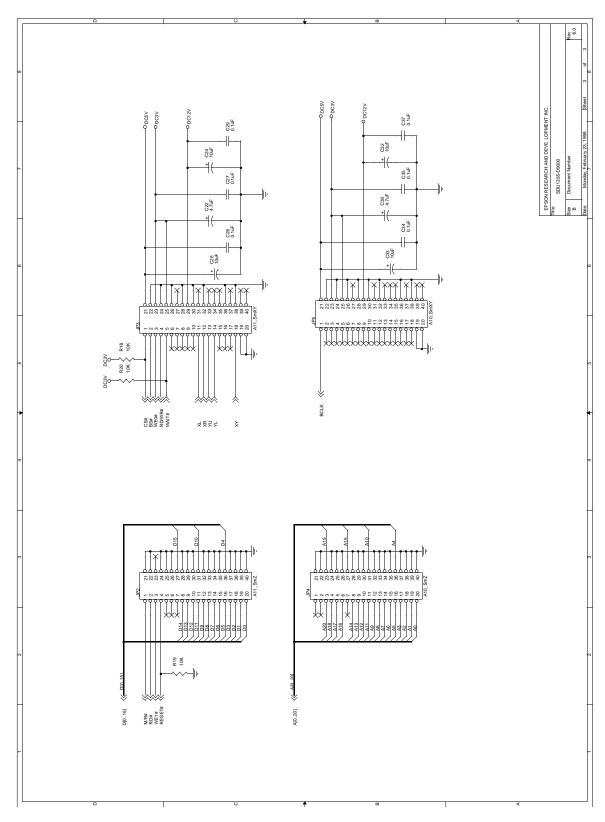

# 3 Typical System Implementation Diagrams

Figure 3-1: Typical System Diagram (SH-4 Bus)

Figure 3-2: Typical System Diagram (SH-3 Bus)

Figure 3-3: Typical System Diagram (MC68K Bus 1, 16-Bit 68000)

Figure 3-4: Typical System Diagram (MC68K Bus 2, 32-Bit 68030)

Figure 3-5: Typical System Diagram (Generic Bus)

Figure 3-6: Typical System Diagram (NEC VR41xx (MIPS) Bus)

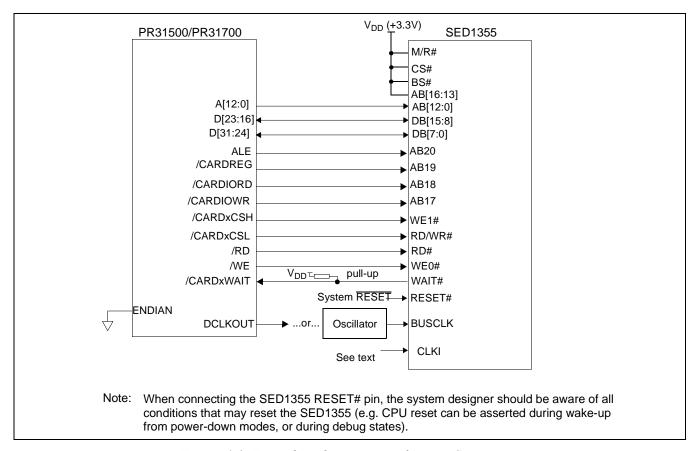

Figure 3-7: Typical System Diagram (Philips PR31500/PR31700 Bus)

Figure 3-8: Typical System Diagram (Toshiba TX3912 Bus)

Figure 3-9: Typical System Diagram (Power PC Bus)

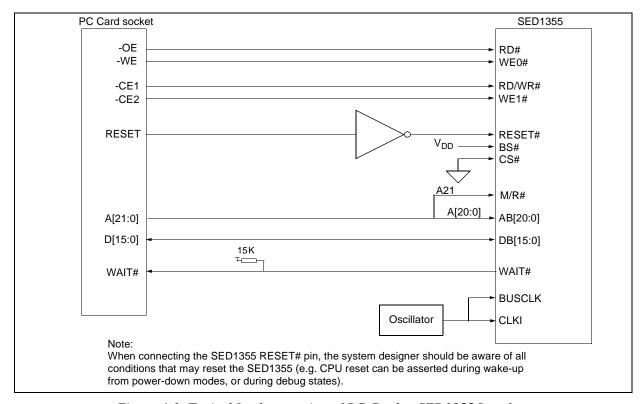

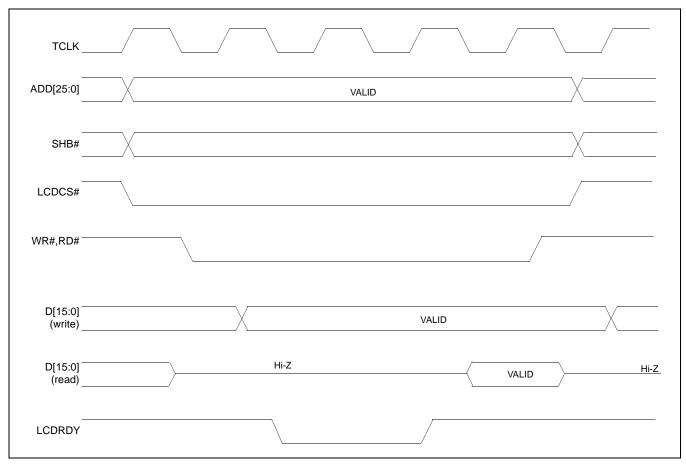

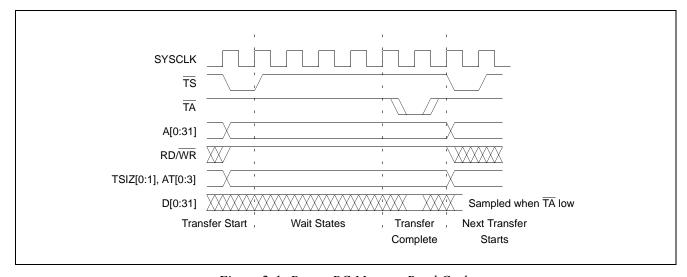

Figure 3-10: Typical System Diagram (PC Card (PCMCIA) Bus)

# 4 Internal Description

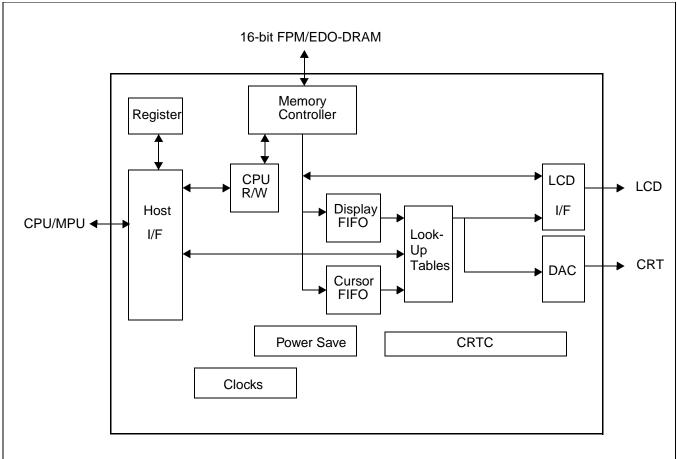

# 4.1 Block Diagram Showing Datapaths

# 4.2 Block Descriptions

# 4.2.1 Register

The Register block contains all the register latches

### 4.2.2 Host Interface

The Host Interface (I/F) block provides the means for the CPU/MPU to communicate with the display buffer and internal registers via one of the supported bus interfaces.

### 4.2.3 CPU R/W

The CPU R/W block synchronizes the CPU requests for display buffer access. If SwivelView is enabled, the data is rotated in this block.

# 4.2.4 Memory Controller

The Memory Controller block arbitrates between CPU accesses and display refresh accesses as well as generates the necessary signals to interface to one of the supported 16-bit memory devices (FPM-DRAM or EDO-DRAM).

# 4.2.5 Display FIFO

The Display FIFO block fetches display data from the Memory Controller for display refresh.

#### 4.2.6 Cursor FIFO

The Cursor FIFO block fetches Cursor/ink data from the Memory Controller for display refresh.

## 4.2.7 Look-Up Tables

The Look-Up Tables block contains three 256x4 Look-Up Tables (LUT), one for each primary color. In monochrome mode, only the green LUT is selected and used. This block contains antisparkle circuitry. The cursor/ink and display data are merged in this block.

#### 4.2.8 CRTC

The CRTC generates the sync timing for the LCD and CRT, defining the vertical and horizontal display periods.

#### 4.2.9 LCD Interface

The LCD Interface block performs Frame Rate Modulation (FRM) for passive LCD panels and generates the correct data format and timing control signals for various LCD and TFT/D-TFD panels.

### 4.2.10 DAC

The DAC is the Digital to Analog converter for analog CRT support.

#### 4.2.11 Power Save

The Power Save block contains the power save mode circuitry.

#### 4.2.12 Clocks

The Clocks module is the source of all clocks in the chip.

# 5 Pins

# 5.1 Pinout Diagram

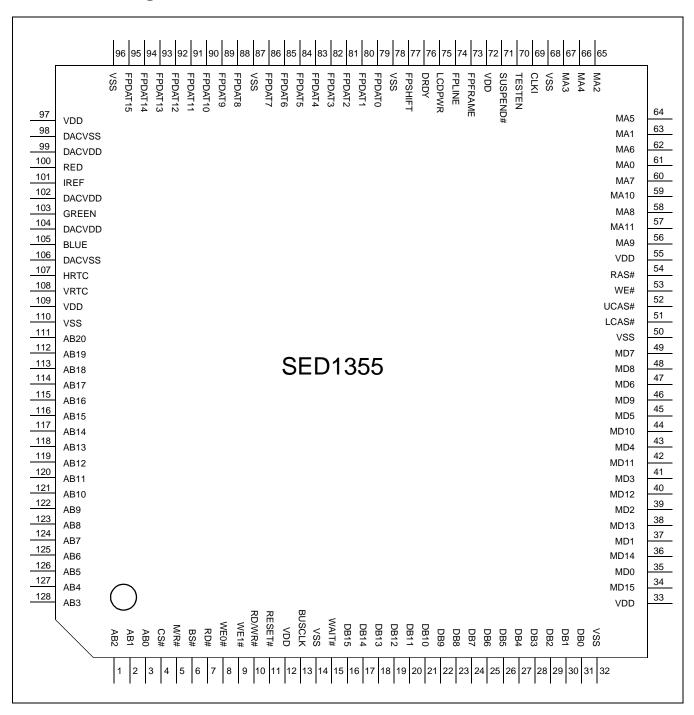

Figure 5-1: Pinout Diagram

128-pin QFP15 surface mount package

# 5.2 Pin Description

### Key:

I = Input

O = Output

IO = Bi-Directional (Input/Output)

A = Analog

P = Power pin

C = CMOS level input

CD = CMOS level input with pull down resistor (typical values of  $100K\Omega/180K\Omega$  at 5V/3.3V respectively)

CS = CMOS level Schmitt input

COx = CMOS output driver, x denotes driver type (see tables 6-3, 6-4, 6-5 for details)

TSx = Tri-state CMOS output driver, x denotes driver type (see tables 6-3, 6-4, 6-5 for details)

TSxD = Tri-state CMOS output driver with pull down resistor (typical values of  $100K\Omega/180K\Omega$  at 5V/3.3V)

respectively), x denotes driver type (see tables 6-3, 6-4, 6-5 for details)

CNx = CMOS low-noise output driver, x denotes driver type (see tables 6-3, 6-4, 6-5 for details)

# 5.2.1 Host Interface

Table 5-1: Host Interface Pin Descriptions

| Pin Name | Туре | Pin#             | Cell | RESET#<br>State | Description                                                                                                        |

|----------|------|------------------|------|-----------------|--------------------------------------------------------------------------------------------------------------------|

|          |      |                  |      |                 | For SH-3/SH-4 Bus, this pin inputs system address bit 0 (A0).                                                      |

|          |      |                  |      |                 | For MC68K Bus 1, this pin inputs the lower data strobe (LDS#).                                                     |

|          |      |                  |      |                 | For MC68K Bus 2, this pin inputs system address bit 0 (A0).                                                        |

|          |      |                  |      |                 | For Generic Bus, this pin inputs system address bit 0 (A0).                                                        |

|          |      |                  | cs   | Hi-Z            | For MIPS/ISA Bus, this pin inputs system address bit 0 (SA0).                                                      |

| AB0      | I    | 3                |      |                 | • For Philips PR31500/31700 Bus, this pin inputs system address bit 0 (A0).                                        |

|          |      |                  |      |                 | For Toshiba TX3912 Bus, this pin inputs system address bit 0 (A0).                                                 |

|          |      |                  |      |                 | For PowerPC Bus, this pin inputs system address bit 31 (A31).                                                      |

|          |      |                  |      |                 | For PC Card (PCMCIA) Bus, this pin inputs system address bit 0 (A0).                                               |

|          |      |                  |      |                 | See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality. |

|          |      | 119-128,<br>1, 2 | С    | Hi-Z            | <ul> <li>For PowerPC Bus, these pins input the system address bits 19<br/>through 30 (A[19:30]).</li> </ul>        |

| AB[12:1] | I    |                  |      |                 | <ul> <li>For all other busses, these pins input the system address bits 12<br/>through 1 (A[12:1]).</li> </ul>     |

|          |      |                  |      |                 | See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality. |

Table 5-1: Host Interface Pin Descriptions (Continued)

| Pin Name  | Туре | Pin#    | Cell | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|------|---------|------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AB[16:13] | ı    | 115-118 | С    | Hi-Z            | <ul> <li>For Philips PR31500/31700 Bus, these pins are connected to V<sub>DD</sub>.</li> <li>For Toshiba TX3912 Bus, these pins are connected to V<sub>DD</sub>.</li> <li>For PowerPC Bus, these pins input the system address bits 15 through 18 (A[15:18]).</li> <li>For all other busses, these pins input the system address bits 16 through 13 (A[16:13]).</li> <li>See "Host Bus Interface Pin Mapping" for summary. See the respective</li> </ul>                                                                                                                                                                                   |

| AB17      | ı    | 114     | С    | Hi-Z            | <ul> <li>AC Timing diagram for detailed functionality.</li> <li>For Philips PR31500/31700 Bus, this pin inputs the IO write command (/CARDIOWR).</li> <li>For Toshiba TX3912 Bus, this pin inputs the IO write command (CARDIOWR*).</li> <li>For PowerPC Bus, this pin inputs the system address bit 14 (A14).</li> <li>For all other busses, this pin inputs the system address bit 17 (A17).</li> <li>See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality.</li> </ul>                                                                                                      |

| AB18      | I    | 113     | С    | Hi-Z            | <ul> <li>For Philips PR31500/31700 Bus, this pin inputs the IO read command (/CARDIORD).</li> <li>For Toshiba TX3912 Bus, this pin inputs the IO read command (CARDIORD*).</li> <li>For PowerPC Bus, this pin inputs the system address bit 13 (A13).</li> <li>For all other busses, this pin inputs the system address bit 18 (A18).</li> <li>See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality.</li> </ul>                                                                                                                                                               |

| AB19      | I    | 112     | С    | Hi-Z            | <ul> <li>For Philips PR31500/31700 Bus, this pin inputs the card control register access (/CARDREG).</li> <li>For Toshiba TX3912 Bus, this pin inputs the card control register (CARDREG*).</li> <li>For PowerPC Bus, this pin inputs the system address bit 12 (A12).</li> <li>For all other busses, this pin inputs the system address bit 19 (A19).</li> <li>See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality.</li> </ul>                                                                                                                                              |

| AB20      | I    | 111     | С    | Hi-Z            | <ul> <li>For the MIPS/ISA Bus, this pin inputs system address bit 20. Note that for the ISA Bus, the unlatched LA20 must first be latched before input to AB20.</li> <li>For Philips PR31500/31700 Bus, this pin inputs the address latch enable (ALE).</li> <li>For Toshiba TX3912 Bus, this pin inputs the address latch enable (ALE).</li> <li>For PowerPC Bus, this pin inputs the system address bit 11 (A11).</li> <li>For all other busses, this pin inputs the system address bit 20 (A20).</li> <li>See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality.</li> </ul> |

Table 5-1: Host Interface Pin Descriptions (Continued)

| Pin Name                               | Туре | Pin # | Cell       | RESET#<br>State | Description                                                                                                                                                             |

|----------------------------------------|------|-------|------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        |      |       |            |                 | These pins are the system data bus. For 8-bit bus modes, unused data pins should be tied to $V_{DD}$ .                                                                  |

|                                        |      |       |            |                 | For SH-3/SH-4 Bus, these pins are connected to D[15:0].                                                                                                                 |

|                                        |      |       |            |                 | For MC68K Bus 1, these pins are connected to D[15:0].                                                                                                                   |

|                                        |      |       |            |                 | For MC68K Bus 2, these pins are connected to D[31:16] for 32-bit devices (e.g. MC68030) or D[15:0] for 16-bit devices (e.g. MC68340).                                   |

|                                        |      |       |            |                 | For Generic Bus, these pins are connected to D[15:0].                                                                                                                   |

| DB[15:0]                               | IO   | 16-31 | C/TS2      | Hi-Z            | For MIPS/ISA Bus, these pins are connected to SD[15:0].                                                                                                                 |

|                                        |      |       |            |                 | For Philips PR31500/31700 Bus, these pins are connected to D[31:16].                                                                                                    |

|                                        |      |       |            |                 | For Toshiba TX3912 Bus, pins [15:8] are connected to D[23:16] and pins [7:0] are connected to D[31:24].                                                                 |

|                                        |      |       |            |                 | For PowerPC Bus, these pins are connected to D[0:15].                                                                                                                   |

|                                        |      |       |            |                 | For PC Card (PCMCIA) Bus, these pins are connected to D[15:0].                                                                                                          |

|                                        |      |       |            |                 | See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality.                                                      |

|                                        |      |       |            |                 | This is a multi-purpose pin:                                                                                                                                            |

|                                        |      |       |            |                 | • For SH-3/SH-4 Bus, this pin inputs the write enable signal for the upper data byte (WE1#).                                                                            |

|                                        | Ю    | 9     |            | Hi-Z            | • For MC68K Bus 1, this pin inputs the upper data strobe (UDS#).                                                                                                        |

|                                        |      |       | CS/TS<br>2 |                 | For MC68K Bus 2, this pin inputs the data strobe (DS#).                                                                                                                 |

|                                        |      |       |            |                 | For Generic Bus, this pin inputs the write enable signal for the upper data byte (WE1#).                                                                                |

| \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |      |       |            |                 | For MIPS/ISA Bus, this pin inputs the system byte high enable signal (SBHE#).                                                                                           |

| WE1#                                   |      |       |            |                 | For Philips PR31500/31700 Bus, this pin inputs the odd byte access enable signal (/CARDxCSH).                                                                           |

|                                        |      |       |            |                 | For Toshiba TX3912 Bus, this pin inputs the odd byte access enable signal (CARDxCSH*).                                                                                  |

|                                        |      |       |            |                 | For PowerPC Bus, this pin outputs the burst inhibit signal (BI#).                                                                                                       |

|                                        |      |       |            |                 | For PC Card (PCMCIA) Bus, this pin inputs the card enable 2 signal (-CE2).                                                                                              |

|                                        |      |       |            |                 | See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality.                                                      |

|                                        |      |       |            |                 | For Philips PR31500/31700 Bus, this pin is connected to V <sub>DD</sub> .                                                                                               |

|                                        |      |       |            |                 | For Toshiba TX3912 Bus, this pin is connected to V <sub>DD</sub> .                                                                                                      |

|                                        |      |       |            |                 | For all other busses, this input pin is used to select between the                                                                                                      |

| M/R#                                   |      | 5     | С          | Hi-Z            | display buffer and register address spaces of the SED1355. M/R# is set high to access the display buffer and low to access the registers. See <i>Register Mapping</i> . |

|                                        |      |       |            |                 | See Table 5-6:, "CPU Interface Pin Mapping," on page 34.                                                                                                                |

|                                        |      |       |            |                 | For Philips PR31500/31700 Bus, this pin is connected to V <sub>DD</sub> .                                                                                               |

|                                        |      |       |            |                 | For Toshiba TX3912 Bus, this pin is connected to V <sub>DD</sub> .                                                                                                      |

| CS#                                    | ı    | 4     | С          | Hi-Z            | For all other busses, this is the Chip Select input.                                                                                                                    |

|                                        |      |       |            |                 | See Table 5-6:, "CPU Interface Pin Mapping," on page 34. See the respective AC Timing diagram for detailed functionality.                                               |

Table 5-1: Host Interface Pin Descriptions (Continued)

| Pin Name | Туре | Pin# | Cell | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|------|------|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSCLK   | I    | 13   | С    | Hi-Z            | This pin inputs the system bus clock. It is possible to apply a 2x clock and divide it by 2 internally - see MD12 in <i>Summary of Configuration Options</i> .  • For SH-3/SH-4 Bus, this pin is connected to CKIO.  • For MC68K Bus 1, this pin is connected to CLK.  • For MC68K Bus 2, this pin is connected to CLK.  • For Generic Bus, this pin is connected to BCLK.  • For MIPS/ISA Bus, this pin is connected to CLK.  • For Philips PR31500/31700 Bus, this pin is connected to DCLKOUT.  • For Toshiba TX3912 Bus, this pin is connected to DCLKOUT.  • For PowerPC Bus, this pin is connected to CLKOUT.  • For PC Card (PCMCIA) Bus, this pin is connected to CLKI.  See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality.                                                                                                                                                                                                              |

| BS#      | I    | 6    | cs   | Hi-Z            | This is a multi-purpose pin:  For SH-3/SH-4 Bus, this pin inputs the bus start signal (BS#).  For MC68K Bus 1, this pin inputs the address strobe (AS#).  For MC68K Bus 2, this pin inputs the address strobe (AS#).  For Generic Bus, this pin is connected to V <sub>DD</sub> .  For MIPS/ISA Bus, this pin is connected to V <sub>DD</sub> .  For Phillips PR31500/31700 Bus, this pin is connected to V <sub>DD</sub> .  For Toshiba TX3912 Bus, this pin is connected to V <sub>DD</sub> .  For PowerPC Bus, this pin inputs the Transfer Start signal (TS#).  For PC Card (PCMCIA) Bus, this pin is connected to V <sub>DD</sub> .  See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality.                                                                                                                                                                                                                                                     |

| RD/WR#   | I    | 10   | cs   | Hi-Z            | <ul> <li>This is a multi-purpose pin:</li> <li>For SH-3/SH-4 Bus, this pin inputs the read write signal (RD/WR#). The SED1355 needs this signal for early decode of the bus cycle.</li> <li>For MC68K Bus 1, this pin inputs the read write signal (R/W#).</li> <li>For MC68K Bus 2, this pin inputs the read write signal (R/W#).</li> <li>For Generic Bus, this pin inputs the read command for the upper data byte (RD1#).</li> <li>For MIPS/ISA Bus, this pin is connected to V<sub>DD</sub>.</li> <li>For Phillips PR31500/31700 Bus, this pin inputs the even byte access enable signal (/CARDxCSL).</li> <li>For Toshiba TX3912 Bus, this pin inputs the even byte access enable signal (CARDxCSL*).</li> <li>For PowerPC Bus, this pin inputs the read write signal (RD/WR#).</li> <li>For PC Card (PCMCIA) Bus, this pin inputs the card enable 1 signal (-CE1).</li> <li>See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality.</li> </ul> |

Table 5-1: Host Interface Pin Descriptions (Continued)

| Pin Name | Туре | Pin# | Cell | RESET#<br>State | Description                                                                                                        |

|----------|------|------|------|-----------------|--------------------------------------------------------------------------------------------------------------------|

|          |      |      |      |                 | This is a multi-purpose pin:                                                                                       |

|          |      |      |      |                 | <ul> <li>For SH-3/SH-4 Bus, this pin inputs the read signal (RD#).</li> </ul>                                      |

|          |      |      |      |                 | • For MC68K Bus 1, this pin is connected to V <sub>DD</sub> .                                                      |

|          |      |      |      |                 | For MC68K Bus 2, this pin inputs the bus size bit 1 (SIZ1).                                                        |

|          |      |      |      |                 | For Generic Bus, this pin inputs the read command for the lower data byte (RD0#).                                  |

|          |      |      |      |                 | • For MIPS/ISA Bus, this pin inputs the memory read signal (MEMR#).                                                |

| RD#      | I    | 7    | cs   | Hi-Z            | <ul> <li>For Philips PR31500/31700 Bus, this pin inputs the memory read<br/>command (/RD).</li> </ul>              |

|          |      |      |      |                 | <ul> <li>For Toshiba TX3912 Bus, this pin inputs the memory read command<br/>(RD*).</li> </ul>                     |

|          |      |      |      |                 | For PowerPC Bus, this pin inputs the transfer size 0 signal (TSIZ0).                                               |

|          |      |      |      |                 | For PC Card (PCMCIA) Bus, this pin inputs the output enable signal (-OE).                                          |

|          |      |      |      |                 | See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality. |

|          |      |      | cs   |                 | This is a multi-purpose pin:                                                                                       |

|          |      | 8    |      |                 | For SH-3/SH-4 Bus, this pin inputs the write enable signal for the lower data byte (WE0#).                         |

|          |      |      |      |                 | For MC68K Bus 1, this pin must be connected to V <sub>DD</sub>                                                     |

|          |      |      |      |                 | For MC68K Bus 2, this pin inputs the bus size bit 0 (SIZ0).                                                        |

|          |      |      |      |                 | <ul> <li>For Generic Bus, this pin inputs the write enable signal for the lower<br/>data byte (WE0#).</li> </ul>   |

| WE0#     |      |      |      | Hi-Z            | <ul> <li>For MIPS/ISA Bus, this pin inputs the memory write signal<br/>(MEMW#).</li> </ul>                         |

| VVLO#    |      | 0    |      | 111-2           | For Philips PR31500/31700 Bus, this pin inputs the memory write command (/WE).                                     |

|          |      |      |      |                 | • For Toshiba TX3912 Bus, this pin inputs the memory write command (WE*).                                          |

|          |      |      |      |                 | • For PowerPC Bus, this pin inputs the Transfer Size 1 signal (TSIZ1).                                             |

|          |      |      |      |                 | For PC Card (PCMCIA) Bus, this pin inputs the write enable signal (-WE).                                           |

|          |      |      |      |                 | See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality. |

Table 5-1: Host Interface Pin Descriptions (Continued)

| Pin Name | Туре | Pin # | Cell | RESET#<br>State | Description                                                                                                                                                                           |

|----------|------|-------|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT#    |      | 15    | TS2  | Hi-Z            | The active polarity of the WAIT# output is configurable; the state of MD5 on the rising edge of RESET# defines the active polarity of WAIT# - see "Summary of Configuration Options". |

|          |      |       |      |                 | • For SH-3 Bus, this pin outputs the wait request signal (WAIT#); MD5 must be pulled low during reset by the internal pull-down resistor.                                             |

|          |      |       |      |                 | <ul> <li>For SH-4 Bus, this pin outputs the ready signal (RDY#); MD5 must<br/>be pulled high during reset by an external pull-up resistor.</li> </ul>                                 |

|          |      |       |      |                 | <ul> <li>For MC68K Bus 1, this pin outputs the data transfer acknowledge<br/>signal (DTACK#); MD5 must be pulled high during reset by an<br/>external pull-up resistor.</li> </ul>    |

|          |      |       |      |                 | • For MC68K Bus 2, this pin outputs the data transfer and size acknowledge bit 1 (DSACK1#); MD5 must be pulled high during reset by an external pull-up resistor.                     |

|          |      |       |      |                 | • For Generic Bus, this pin outputs the wait signal (WAIT#); MD5 must be pulled low during reset by the internal pull-down resistor.                                                  |

|          | 0    |       |      |                 | <ul> <li>For MIPS/ISA Bus, this pin outputs the IO channel ready signal<br/>(IOCHRDY); MD5 must be pulled low during reset by the internal<br/>pull-down resistor.</li> </ul>         |

|          |      |       |      |                 | • For Philips PR31500/31700 Bus, this pin outputs the wait state signal (/CARDxWAIT); MD5 must be pulled low during reset by the internal pull-down resistor.                         |

|          |      |       |      |                 | <ul> <li>For Toshiba TX3912 Bus, this pin outputs the wait state signal<br/>(CARDxWAIT*); MD5 must be pulled low during reset by the internal<br/>pull-down resistor.</li> </ul>      |

|          |      |       |      |                 | <ul> <li>For PowerPC Bus, this pin outputs the transfer acknowledge signal<br/>(TA#); MD5 must be pulled high during reset by an external pull-up<br/>resistor.</li> </ul>            |

|          |      |       |      |                 | <ul> <li>For PC Card (PCMCIA) Bus, this pin outputs the wait signal (-WAIT);<br/>MD5 must be pulled low during reset by the internal pull-down<br/>resistor.</li> </ul>               |

|          |      |       |      |                 | See "Host Bus Interface Pin Mapping" for summary. See the respective AC Timing diagram for detailed functionality.                                                                    |

| RESET#   | ı    | 11    | cs   | Output          | Active low input that clears all internal registers and forces all outputs to their inactive states. Note that active high RESET signals must be inverted before input to this pin.   |

# 5.2.2 Memory Interface

Table 5-2: Memory Interface Pin Descriptions

| Pin Name | Туре | Pin#                                                                          | Cell       | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|------|-------------------------------------------------------------------------------|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      |                                                                               |            |                 | For dual-CAS# DRAM, this is the column address strobe for the lower byte (LCAS#).                                                                                                                                                                                                                                                                                                                   |

| LCAS#    | 0    | 51                                                                            | CO1        | 1               | For single-CAS# DRAM, this is the column address strobe (CAS#).                                                                                                                                                                                                                                                                                                                                     |

|          |      |                                                                               |            |                 | See "Memory Interface Pin Mapping" for summary. See Memory Interface Timing for detailed functionality.                                                                                                                                                                                                                                                                                             |

|          |      |                                                                               |            |                 | This is a multi-purpose pin:                                                                                                                                                                                                                                                                                                                                                                        |

|          | Ο    | 52                                                                            | CO1        | 1               | For dual-CAS# DRAM, this is the column address strobe for the upper byte (UCAS#).                                                                                                                                                                                                                                                                                                                   |