bq2081

## SBS COMPLIANT GAS GAUGE IC FOR USE WITH THE bq29311

#### FEATURES

- Provides Accurate Measurement of Available Charge in Li-Ion and Li-Polymer Batteries

- Supports the Smart Battery Specification (SBS) V1.1

- Works With the TI bq29311 Protection IC to Provide Complete Pack Electronics for 10.8-V or 14.4-V Battery Packs with Few External Components

- Based on a Powerful Low-Power RISC CPU Core With High-Performance Peripherals

- Integrated FLASH Memory Eliminates the Need for External Configuration EEPROM

- Measures Charge Flow Using a High Resolution 15–Bit Integrating Converter

- Better Than 3-nVh of Resolution

- Self-Calibrating

- Offset Error Less Than 1- $\mu\text{V}$

- Uses 15-Bit Delta Sigma Converter for Accurate Voltage, Temperature, and Current Measurements

- Programmable Cell Modeling for Maximum Battery Fuel Gauge Accuracy

- Drives 4- or 5-Segment LED Display for Remaining Capacity Indication

- 38-pin TSSOP (DBT)

### DESCRIPTION

The bq2081 SBS Compliant gas gauge IC for battery pack or in-system installation maintains an accurate record of available charge in Li-Ion or Li-Polymer batteries. The bg2081 monitors capacity and other critical parameters of the battery pack and reports the information to the system host controller over а serial communication bus. It is designed to work with the bq29311 protection IC to maximize functionality and safety and minimize component count and cost in smart battery circuits.

The bq2081 uses an integrating converter with continuous sampling for the measurement of battery charge and discharge currents. Optimized for coloumb counting in portable applications, the self-calibrating integrating converter has a resolution better than 3-nVh and an offset measurement error of less than 1- $\mu$ V (typical). For voltage, temperature, and current reporting, the bq2081 uses a 15-bit A-to-D converter. In conjunction with the bq29311, the onboard ADC also monitors individual cell voltages in a battery pack and allows the bq2081 to generate the control signals necessary to implement the required safety protection for Li-lon and Li-Polymer battery chemistries.

The bq2081 supports the smart battery data (SBData) commands and charge control functions. It communicates data using the System Management Bus (SMBus) 2-wire protocol or the 1-wire HDQ16 protocol. The data available includes the battery's remaining capacity, temperature, voltage, current, and remaining run-time predictions. The bq2081 provides LED drivers and a push button input to depict remaining battery capacity from full to empty in 20% or 25% increments with a 4 or 5 segment display.

The bq2081 contains 512 bytes of internal FLASH EPROM, whith store configuration information. The information includes nominal capacity and voltage, self-discharge rate, rate compensation factors, and other programmable cell-modeling factors used to accurately adjust remaining capacity for use-conditions based on time, rate, and temperature. The bq2081 also automatically calibrates or learns the true battery capacity in the course of a discharge cycle from programmable near full to near empty levels.

The bq29311 protection IC provides power to the bq2081 from a 3 or 4 series Li-Ion cell stack, eliminating the need for an external regulator circuit.

#### **Terminal Functions**

| TERMINAL |                                |     |                                                                                                                                                                     |  |  |  |

|----------|--------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | No.                            | I/O | DESCRIPTION                                                                                                                                                         |  |  |  |

| CLKOUT   | 35                             | Ι   | 32.768-kHz output to the bq29311                                                                                                                                    |  |  |  |

| DISP     | 25                             | Ι   | Display control for the LED drivers LED1 through LED5                                                                                                               |  |  |  |

| FILT     | 32                             | I   | Serial memory clock for data transfer between the bq2063 and the external nonvolatile configuration memory                                                          |  |  |  |

| HDQ16    | 14                             | I/O | Serial communication open-drain bidirectional communications port                                                                                                   |  |  |  |

| INT      | 17                             | Ι   | Safety interrupt from the bq2081                                                                                                                                    |  |  |  |

| LED1     | 20                             | 0   | LED display segments that each may drive an external LED                                                                                                            |  |  |  |

| LED2     | 21                             | 0   |                                                                                                                                                                     |  |  |  |

| LED3     | 22                             | 0   |                                                                                                                                                                     |  |  |  |

| LED4     | 23                             | 0   |                                                                                                                                                                     |  |  |  |

| LED5     | 24                             | 0   |                                                                                                                                                                     |  |  |  |

| MRST     | 26                             | Ι   | Master reset input that forces the device into reset when held high                                                                                                 |  |  |  |

| N/C      | 4, 5, 7, 12,<br>13, 18, 36, 37 | -   | No connection                                                                                                                                                       |  |  |  |

| OC       | 3                              | I   | Analog input for auto ADC offset compensation.                                                                                                                      |  |  |  |

| RBI      | 9                              | Ι   | Register backup that provides backup potential to the bq2081 registers during periods of low operating voltage. RBI accepts a storage capacitor or a battery input. |  |  |  |

| SCLK     | 6                              | 0   | Communication clock to the bq29311                                                                                                                                  |  |  |  |

| SDATA    | 10                             | I/O | Data transfer to and from bq29311                                                                                                                                   |  |  |  |

| SMBC     | 15                             | I/O | SMBus clock open-drain bidirectional pin used to clock the data transfer to and from the bq2081                                                                     |  |  |  |

| SMBD     | 16                             | I/O | SMBus data open-drain bidirectional pin used to transfer address and data to and from the bq2081                                                                    |  |  |  |

| SR1      | 28                             | Ι   | Connections for a small-value sense resistor to monitor the battery charge- and discharge-current                                                                   |  |  |  |

| SR2      | 27                             | I   | flow                                                                                                                                                                |  |  |  |

| TS       | 2                              | Ι   | Thermistor voltage input connection to monitor temperature                                                                                                          |  |  |  |

| VDDA     | 31                             | I   | Positive supply for analog circuitry                                                                                                                                |  |  |  |

| VDDD     | 8                              | Ι   | Positive supply for digital circuitry and I/O pins                                                                                                                  |  |  |  |

| VIN      | 1                              | Ι   | Single cell voltage input from the bq29311                                                                                                                          |  |  |  |

| VSSA     | 30                             | Ι   | Negative supply for analog circuitry                                                                                                                                |  |  |  |

| VSSD     | 11, 19, 38                     | Ι   | Negative supply for digital circuitry                                                                                                                               |  |  |  |

| VSSP     | 29                             | I   | Negative supply for output circuitry                                                                                                                                |  |  |  |

| XCK1     | 34                             | Ι   | 32.768kHz crystal oscillator input pin                                                                                                                              |  |  |  |

| XCK2     | 33                             | 0   | 32.768kHz crystal oscillator output pin                                                                                                                             |  |  |  |

#### AVAILABLE OPTIONS

| PART NUMBER | PACKAGE<br>(38-PIN TSSOP) |

|-------------|---------------------------|

| bq20811DBT  | Standard device           |

SLUS502 - SEPTEMBER 2001

#### absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>DD</sub> relative to V <sub>SS</sub> (see Note 1)                                               | / |

|------------------------------------------------------------------------------------------------------------------------------|---|

| Open-drain I/O pins, V <sub>(IOD)</sub> relative to V <sub>SS</sub> (see Note 1)                                             | / |

| Input voltage range to all other pins, V <sub>I</sub> relative to V <sub>SS</sub> (see Note 1)0.3 V to V <sub>DD</sub> + 0.3 | / |

| Operating free-air temperature range, T <sub>A</sub> –20°C to 70°C                                                           | ) |

| Storage temperature range, T <sub>stg</sub> –65°C to 150°C                                                                   | ) |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE: 1: V<sub>SS</sub> refers to the common node of V<sub>(SSA)</sub>, V<sub>(SSD)</sub>, and V<sub>SS</sub>.

## electrical characteristics for $V_{DD}$ = 3.0 V to 3.6 V, $T_A$ = -20°C to 70°C (unless otherwise noted)

| PARAMETER          |                                                      | TEST CONDITIONS                                   | MIN                   | TYP | MAX                   | UNIT |  |

|--------------------|------------------------------------------------------|---------------------------------------------------|-----------------------|-----|-----------------------|------|--|

| V <sub>DD</sub>    | Supply voltage                                       |                                                   | 3.0                   | 3.3 | 3.6                   | V    |  |

| IDD                | Operating current                                    |                                                   |                       | 200 |                       | μA   |  |

| I(SLP)             | Low-power storage mode current                       |                                                   |                       | 1   |                       | μA   |  |

| VI(OLS)            | Output voltage low: (LED1–LED5)                      | I <sub>(OLS)</sub> = 10 mA                        |                       |     | 0.4                   | V    |  |

| V <sub>(IL)</sub>  | Input voltage low DISP                               |                                                   | -0.3                  |     | 0.8                   | V    |  |

| VIH                | Input voltage high DISP                              |                                                   | 2                     |     | V <sub>CC</sub> + 0.3 | V    |  |

| V <sub>OL</sub>    | Output voltage low SMBC, SMBD,<br>HDQ16, SDATA, SCLK | I <sub>OL</sub> = 0.5 mA                          |                       |     | 0.4                   | V    |  |

| V <sub>(ILS)</sub> | Input voltage low SMBC, SMBD,<br>HDQ16, SDATA, SCLK  |                                                   | -0.3                  |     | 0.8                   | V    |  |

| V <sub>(IHS)</sub> | Input voltage high SMBC, SMBD,<br>HDQ16, SDATA, SCLK |                                                   | 1.7                   |     | 6                     | V    |  |

| V <sub>(AI)</sub>  | Input voltage range VIN, TS, OC                      |                                                   | V <sub>SS</sub> - 0.3 |     | 1.0                   | V    |  |

| I(RB)              | RBI data-retention input current                     | V <sub>(RBI)</sub> > 3 V, V <sub>CC</sub> < 2.5 V |                       | 10  | 50                    | nA   |  |

| V(RBI)             | RBI data-retention voltage                           |                                                   | 1.3                   |     |                       | V    |  |

| Z <sub>(Al1)</sub> | Input impedance SR1, SR2                             | 0 V–1.0 V                                         | 10                    |     |                       | MΩ   |  |

| Z <sub>(Al2)</sub> | Input impedance VIN, TS, OC                          | 0 V–1.0 V                                         | 8                     |     |                       | MΩ   |  |

#### integrating ADC characteristics, $V_{DD}$ = 3.0 V to 3.6 V, $T_A$ = -20°C to 70°C (unless otherwise noted)

|                   | PARAMETER                                        | TEST CONDITIONS       | MIN  | TYP    | MAX    | UNIT |

|-------------------|--------------------------------------------------|-----------------------|------|--------|--------|------|

| V <sub>(SR)</sub> | Input voltage range, $V_{(SR2)}$ and $V_{(SR1)}$ | VSR = V(SR2) - V(SR1) | -0.3 |        | 1.0    | V    |

| V(SROS)           | Input offset                                     |                       |      | 1      |        | μV   |

| INL               | Integral nonlinearity error                      |                       |      | 0.003% | 0.009% |      |

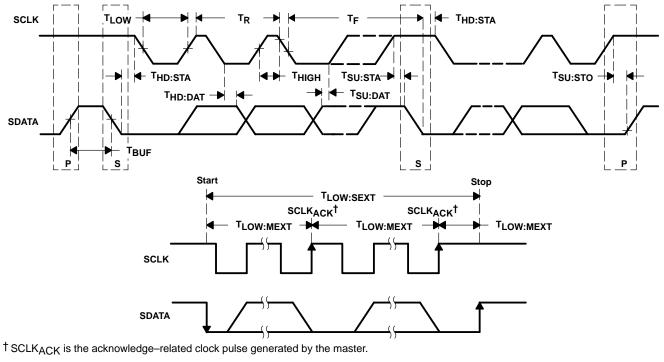

#### SMBus timing specifications, $T_A = -20^{\circ}C$ to $70^{\circ}C$ , 3.0 V < V<sub>DD</sub> < 3.6 V (unless other noted)

| PARAMETER           |                                         | TEST CONDITIONS                        | MIN | TYP  | MAX  | UNIT |  |

|---------------------|-----------------------------------------|----------------------------------------|-----|------|------|------|--|

| FSMB                | SMBus operating frequency               | Slave mode, SMBC 50% duty cycle        | 10  |      | 100  | kHz  |  |

| FMAS                | SMBus master clock frequency            | Master mode, no clock low slave extend |     | 51.2 |      | kHz  |  |

| T <sub>BUF</sub>    | Bus free time between start and stop    |                                        | 4.7 |      |      | μs   |  |

| THD:STA             | Hold time after (repeated) start        |                                        | 4.0 |      |      | μs   |  |

| TSU:STA             | Repeated start setup time               |                                        | 4.7 |      |      | μs   |  |

| TSU:STO             | Stop setup time                         |                                        | 4.0 |      |      | μs   |  |

| T <sub>HD:DAT</sub> | Data hald time                          | Receive mode                           | 0   |      |      | μs   |  |

|                     | Data hold time                          | Transmit mode                          | 300 |      |      |      |  |

| TSU:DAT             | Data setup time                         |                                        | 250 |      |      | μs   |  |

| TTIMEOUT            | Error signal/detect                     | See Note 1                             | 25  |      | 35   | ms   |  |

| TLOW                | Clock low period                        |                                        | 4.7 |      |      | μs   |  |

| THIGH               | Clock high period                       | See Note 2                             | 4.0 |      | 50   | μs   |  |

| TLOW:SEXT           | Cumulative clock low slave extend time  | See Note 3                             |     |      | 25   | ms   |  |

| TLOW:MEXT           | Cumulative clock low master extend time | See Note 4                             |     |      | 10   | ms   |  |

| T <sub>F</sub>      | Clock/data fall time                    | See Note 5                             |     |      | 300  | ns   |  |

| T <sub>R</sub>      | Clock/data rise time                    | See Note 6                             |     |      | 1000 | ns   |  |

NOTES: 1. The bq2081 times out when any clock low exceeds TTIMEOUT 2. THIGH Max. is minimum bus idle time. SMBC = SMBD = 1 for t > 50  $\mu$ s causes reset of any transaction involving bq2081 that is in progress.

3. TLOW:SEXT is the cumulative time a slave device is allowed to extend the clock cycles in one message from initial start to the stop.

4. TLOW:MEXT is the cumulative time a master device is allowed to extend the clock cycles in one message from initial start to the stop.

5. Rise time  $T_R = (V_{ILMAX} - 0.15 \text{ V})$  to  $(V_{IHMIN} + 0.15 \text{ V})$ . 6. Fall time  $T_F = 0.9 \text{ V}_{DD}$  to  $(V_{ILMAX} - 0.15 \text{ V})$ .

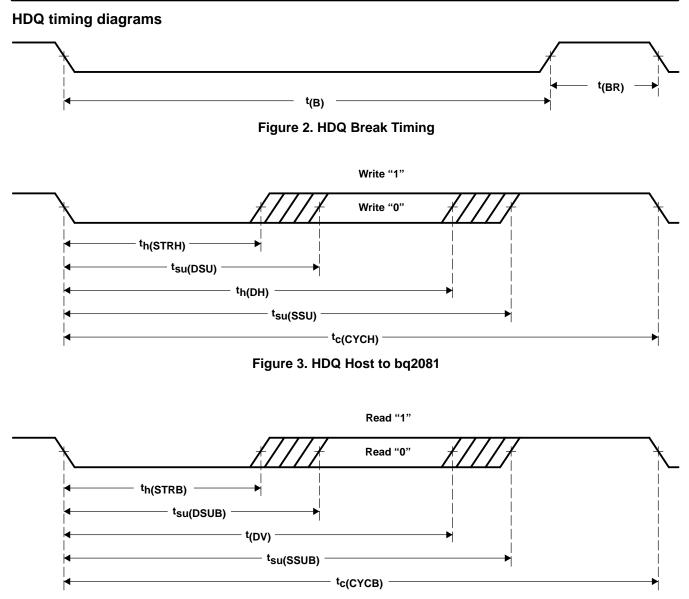

#### HDQ timing characteristics, $T_A = -20^{\circ}C$ to $70^{\circ}C$ , 3.0 V < V<sub>DD</sub> < 3.6 V (unless otherwise noted)

|                       | PARAMETER                               | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------------|-----------------------------------------|-----------------|-----|-----|-----|------|

| t <sub>c(CYCH)</sub>  | Cycle time, host to bq2081 (write)      |                 | 190 |     |     | μs   |

| <sup>t</sup> c(CYCB)  | Cycle time, bq2081 to host (read)       |                 | 190 | 205 | 250 | μs   |

| <sup>t</sup> h(STRH)  | Start hold time, host to bq2081 (write) |                 | 5   |     |     | ns   |

| <sup>t</sup> h(STRB)  | Start hold time, host to bq2081 (read)  |                 | 32  |     |     | μs   |

| <sup>t</sup> su(DSU)  | Data setup time                         |                 |     |     | 50  | μs   |

| <sup>t</sup> su(DSUB) | Data setup time                         |                 |     |     | 50  | μs   |

| <sup>t</sup> h(DH)    | Data hold time                          |                 | 100 |     |     | μs   |

| <sup>t</sup> (DV)     | Data valid time                         |                 | 80  |     |     | μs   |

| <sup>t</sup> su(SSU)  | Stop setup time                         |                 |     |     | 145 | μs   |

| <sup>t</sup> su(SSUB) | Stop setup time                         |                 |     |     | 145 | μs   |

| t(RSPS)               | Response time, bq2081 to host           |                 | 190 |     | 320 | μs   |

| t(B)                  | Break time                              |                 | 190 |     |     | μs   |

| <sup>t</sup> (BR)     | Break recovery time                     |                 | 40  |     |     | μs   |

Figures 6-9 are timing diagrams for the bq2081.

# bq2081

| TSSOP PACKAGE<br>(TOP VIEW)                                                                           |                                                                                      |                                                                                  |                                                                                                                                        |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| VIN [<br>TS [<br>OC [<br>N/C [<br>SCLK [<br>VDDD [<br>VDDD [<br>SDATA [<br>VSSD [<br>N/C [<br>HDQ16 [ | 1 <sup>O</sup><br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14 | 38<br>37<br>36<br>35<br>34<br>33<br>32<br>31<br>30<br>29<br>28<br>27<br>26<br>25 | ] VSSD<br>] N/C<br>] N/C<br>] CLKOUT<br>] XCK2<br>] XCK2<br>] FILT<br>] VDDA<br>] VSSA<br>] VSSP<br>] SR2<br>] SR1<br>] MRST<br>] DISP |  |  |  |  |

| SMBC [<br>SMBD [<br>INT [<br>N/C [<br>VSSD [                                                          | 15<br>16<br>17<br>18<br>19                                                           | 24<br>23<br>22<br>21<br>20                                                       | LED5<br>LED4<br>LED3<br>LED2<br>LED1                                                                                                   |  |  |  |  |

SMBus timing diagrams

# bq2081

SLUS502 - SEPTEMBER 2001

**PRODUCT PREVIEW**

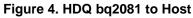

#### **APPLICATION INFORMATION**

### typical application

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated