# 1.5 – 2.5 GHz LNA Switch PA

# **Technical Data**

#### HPMX-3003

#### **Features**

- GaAs MMIC LNA-Switch-Power Amp for 1.5 – 2.5 GHz Transceiver Use

- LNA: 2.2 dB NF, 13 dB G<sub>a</sub> @ 1.9 GHz

- Switch: 55 dBm OIP @ 1.9 GHz

- Power Amp: +4 dBm in, +27.5 dBm out, 23.5 dB Gain, 35%  $\eta_{add}$  @ 1.9 GHz

- 3 or 5 V Operation

- JEDEC Standard SSOP-28 Surface Mount Package

#### Applications

- Personal Communications Systems (PCS)

- Cordless Telephone Systems

- 2400 MHz Wireless LANs and ISM Band Spread Spectrum Applications

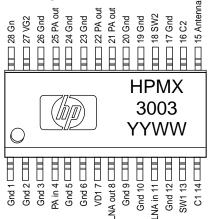

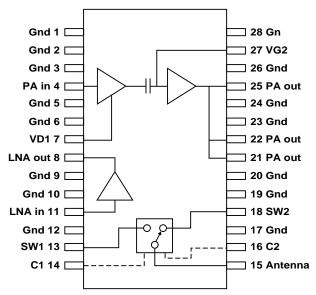

### Package Pin Configuration

**Plastic SSOP-28**

#### Description

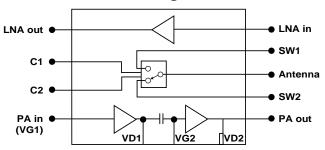

Hewlett-Packard's HPMX-3003 combines a Low Noise Amplifier, GaAs MMIC switch, and 27.5 dBm power amp in a single miniature 28 lead surface mount plastic package. This RFIC would typically serve as the "front end" and power stage of a battery operated wireless transceiver for PCS or ISM band use. Each section of the RFIC can also be used independently.

The single-supply LNA makes use of the low noise characteristics of GaAs to create a matched, broadband amplifier with target performance of 13 dB gain and 2.2 dB noise figure. The switch provides +55 dBm IP3 for linear operation. The power amplifier produces up to 820 mW with 35% power added efficiency.

The HPMX-3003 is fabricated with Hewlett-Packard's GaAs MMIC process, and features a nominal 0.5 micron recessed Schottkybarrier-gate, gold metallization, and silicon nitride passivation to produce MMICs with superior performance, uniformity and reliability.

HPMX-3003 Absolute Maximum Ratings<sup>[1]</sup>

| Symbol            | Parameter                          | Units | Absolute<br>Maximum <sup>[1]</sup><br>LNA | Absolute<br>Maximum <sup>[1]</sup><br>Switch | Absolute<br>Maximum <sup>[1]</sup><br>Power Amp |

|-------------------|------------------------------------|-------|-------------------------------------------|----------------------------------------------|-------------------------------------------------|

| P <sub>diss</sub> | Power Dissipation <sup>[2,3]</sup> | mW    | 250 <sup>[2,3]</sup>                      |                                              | 1500 <sup>[2,3]</sup>                           |

| P <sub>in</sub>   | CW RF Input Power                  | dBm   | +20                                       | +33                                          | +20                                             |

| Vd                | Device Voltage                     | V     | 8                                         | —                                            | 8                                               |

| V <sub>cont</sub> | Control Voltage                    | V     |                                           | -6                                           | _                                               |

| T <sub>ch</sub>   | Channel Temperature                | °C    | 175                                       | 175                                          | 175                                             |

| T <sub>STG</sub>  | Storage Temperature                | °C    | -65 to 150                                | -65 to 150                                   | -65 to 150                                      |

Notes:

1. Operation of this device above any of these limits may cause permanent damage.

Thermal Resistance<sup>[2]</sup>:  $\theta_{jc} = 55^{\circ}C/W$

- 2.  $T_{case} = 25^{\circ}C$

- 3. Derate at 18.2 mW/°C for  $T_C > 78$  °C

Recommended operating range of V<sub>cc</sub> = 2.7 to 5.5 V, T<sub>a</sub> = -40 to + 85 °C

#### **HPMX-3003 Standard Test Conditions**

Unless otherwise stated, all test data was taken on packaged parts under the following conditions:

$$\begin{split} T_a &= 25 \,^{\circ}\text{C}, Z_o = 50 \,\Omega \\ V_{cc} &= +3.0 \,\text{VDC}, V_{control} = -3.0 \,\text{VDC}, V_{D1} = +3.6 \,\text{VDC} \\ \text{LNA P}_{in} &= -20 \,\text{dBm}, \text{PA P}_{in} = +4 \,\text{dBm}, \text{frequency} = 1.9 \,\text{GHz} \\ \text{Perfomance cited is performance in test circuit shown in Figure 17}. \end{split}$$

#### **HPMX-3003** Guaranteed Electrical Specifications

Standard test conditions apply unless otherwise noted.

| Symbol             | Parameters and Test Conditions | Units | Min. | Тур. | Max. |

|--------------------|--------------------------------|-------|------|------|------|

| G <sub>test</sub>  | LNA gain through switch        | dB    | 9.0  | 11   |      |

| Pout               | Output power through switch    | dBm   | 24.0 | 25.5 |      |

| I <sub>d</sub> LNA | LNA bias current               | mA    |      | 6.5  | 9.5  |

#### HPMX-3003 Summary Characterization Information

Standard test conditions apply unless otherwise noted. All information tested in 1900 MHz Test Circuit, and reflects performance of test circuit at 1900 MHz.

| Symbol            | Parameters and Test Conditi                       | ons                                                                  | Units | Тур   |

|-------------------|---------------------------------------------------|----------------------------------------------------------------------|-------|-------|

| LNA               |                                                   |                                                                      |       |       |

| NF                | Noise Figure                                      |                                                                      | dB    | 2.2   |

| $ S_{21} ^2$      | $50\Omega\mathrm{Gain}$                           |                                                                      | dB    | 13    |

| IRL               | Input Return Loss                                 |                                                                      | dB    | 15    |

| ORL               | Output Return Loss                                |                                                                      |       | 12    |

| $IIP_3$           | Input Third Order Intercept                       |                                                                      | dBm   | -1    |

| Switch            |                                                   |                                                                      |       |       |

| P <sub>1dB</sub>  | Output Power<br>where insertion loss is increase  | $\Delta C1 \text{ to } C2 = 3 \text{ V}$ d by 1 dB                   | dBm   | +23   |

| P <sub>1dB</sub>  | Output Power<br>where insertion loss is increased | $\Delta C1 \text{ to } C2 = 5 \text{ V}$<br>d by 1 dB <sup>[1]</sup> | dBm   | +29   |

| $IP_3$            | Third Order Intercept                             |                                                                      | dBm   | +55   |

| $S_{21}$ on       | Insertion Loss, on channel                        |                                                                      | dB    | 0.8   |

| $S_{21}$ off      | Isolation, off channel                            |                                                                      | dB    | 15    |

| IRLon             | Return Loss, on channel                           |                                                                      | dB    | 26    |

| IRLoff            | Return Loss, off channel                          |                                                                      | dB    | 0.5   |

| Powerar           | <b>np</b> (Vg = $8$ V required)                   |                                                                      |       |       |

| GP                | Gain                                              | $V_{D1} = 3.6 V, P_{in} = +4 dBm$                                    | dB    | 23.5  |

| $\eta_{PA_{add}}$ | Power Added Efficiency                            | $V_{D1} = 3.6 V$                                                     | %     | 35    |

| Pout              | Output Power                                      | $V_{D1} = 3.6 V, P_{in} = +4 dBm$                                    | dBm   | +27.5 |

| I <sub>d</sub> PA | Transmit Current                                  | $V_{D1} = 3.6 V, P_{in} = +4 dBm$                                    | mA    | 450   |

Note:

1. The  $P_{1dB}$  of the switch can be improved by increasing the difference between the values of C1 and C2 from the normal  $3 V (+23 dB P_{1dB})$  to  $5 V (+29 dB P_{1dB})$ .

#### HPMX-3003 Pin Description

Figure 1. HPMX-3003 Pin Outs and Schematic.

| No.      | Mnemonic         | Description                  | <b>Typical Signal</b>           | Description                                                                                                                                                                                                                                  |

|----------|------------------|------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Gnd              | ground                       | 0 V                             | Short path with minimal parasitics. Ground pins are                                                                                                                                                                                          |

| 2        | Gnd              | ground                       | 0 V                             | also the primary thermal path for heatsinking the device.                                                                                                                                                                                    |

| 3        | Gnd              | ground                       | 0 V                             |                                                                                                                                                                                                                                              |

| 4        | PA <sub>in</sub> | input to Power<br>Amplifier  | DC: -0.75 V<br>RF: +4 dBm       | Bias through $500 \Omega$ resistor and $100 \text{ pF}$ capacitor. $50 \Omega$ transmission line with DC blocking capacitor (>24 pF) to input.<br>Shunt 2.7 pF used on test board to match input at 1.9 GHz.                                 |

| 5        | Gnd              | ground                       | 0 V                             | Short path with minimal parasitics. Ground pins are also                                                                                                                                                                                     |

| 6        | Gnd              | ground                       | 0 V                             | the primary thermal path for heatsinking the device.                                                                                                                                                                                         |

| 7        | VD1              | Drain bias<br>of PA stage 1  | +3V, 100 mA                     | Set drain bias to 3 V (can be tied to same rail as PA out).<br>Bypass with 100 pF capacitor at pin.                                                                                                                                          |

| 8        | LNA out          | output of LNA                | DC: +3V, 5 mA<br>RF: -7 dBm     | Bias through 5 nH choke (printed on PC board) and 100 pF bypass capacitor to $10 \Omega$ resistor and 1000 pF bypass capacitor. Can be operated from 3 to 5 V supply line. 50 $\Omega$ transmission line with DC block (>24 pF) to receiver. |

| 9<br>10  | Gnd<br>Gnd       | ground<br>ground             | 0 V<br>0 V                      | Short path with minimal parasitics. Ground pins are also<br>the primary thermal path for heatsinking the device.                                                                                                                             |

| 11       | LNA in           | input of LNA                 | DC: 0 V<br>RF: -20 dBm          | $50 \Omega$ transmission line from switch. Input blocking capacitor (24 pF) and shunt 5 nH inductor to ground (noise match at 1.9 GHz) required. Typically a filter is employed between the LNA input and the switch.                        |

| 12       | Gnd              | ground                       | 0 V                             | Short path with minimal parasitics. Ground pins are also<br>the primary thermal path for heatsinking the device.                                                                                                                             |

| 13       | SW1              | switch<br>terminal 1         | DC: 0 V<br>RF: -20 dBm          | Switch input or output. Symmetrical with SW2. 50 $\Omega$ transmission line to LNA (or PA). Line should not carry DC voltage.                                                                                                                |

| 14       | C1               | switch control 1             | closed: 0 V<br>open: -3 to -5 V | High impedance line to control switch, used in conjunction with C2. C2 should be open when C1 is closed.                                                                                                                                     |

| 15       | Antenna          | switch center<br>pole        | DC: 0 V<br>RF: +26 dBm          | $50~\Omega$ transmisson line to/from antenna. Line should not carry DC voltage.                                                                                                                                                              |

| 16       | C2               | switch control 2             | closed: 0 V<br>open: -3 to -5 V | High impedance line to control switch, used in conjunction<br>with C1. C1 should be open when C2 is closed.                                                                                                                                  |

| 17       | Gnd              | ground                       | 0 V                             | Short path with minimal parasitics. Ground pins are also the primary thermal path for heatsinking the device.                                                                                                                                |

| 18       | SW2              | switch<br>terminal 2         | DC: 0 V<br>RF: +4 dBm           | Switch input or output. Symmetrical with SW1. 50 $\Omega$ transmission line to PA (or LNA). Line should not carry DC voltage.                                                                                                                |

| 19<br>20 | Gnd<br>Gnd       | ground<br>ground             | 0 V<br>0 V                      | Short path with minimal parasitics. Ground pins are also<br>the primary thermal path for heatsinking the device.                                                                                                                             |

| 21<br>22 | PA out<br>PA out | output of PA<br>output of PA | DC: 3 V, 350 mA<br>RF: +27 dBm  | 2.7 pF chip capacitor to ground provides 1.9 GHz output match for PA. 50 $\Omega$ transmission line to switch. LC choke and blocking C used. Typically a filter is employed between the PA output and the switch input.                      |

| 23<br>24 | Gnd<br>Gnd       | ground<br>ground             | 0 V<br>0 V                      | Short path with minimal parasitics. Ground pins are also<br>the primary thermal path for heatsinking the device.                                                                                                                             |

| 25       | PA out           | output of PA                 | DC: 3 V, 350 mA<br>RF: +27 dBm  | Leave unconnected; use pins 21 & 22 for PA out.                                                                                                                                                                                              |

| 26       | Gnd              | ground                       | 0 V                             | Short path with minimal parasitics. Ground pins are also<br>the primary thermal path for heatsinking the device.                                                                                                                             |

| 27       | VG2              | Gate bias on<br>PA stage 2   | -0.75V                          | Provide bias through $10 \Omega$ resistor. Bypass to ground at pin with 10 pF capacitor, and on power supply side of resistor with 1000 pF capacitor.                                                                                        |

| 28       | Gnd              | ground                       | OV                              | Short path with minimal parasitics. Ground pins are also the primary thermal path for heatsinking the device.                                                                                                                                |

# HPMX-3003 Pin Description Table

#### **HPMX-3003** Typical Performance

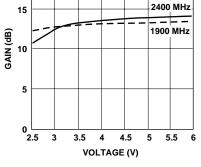

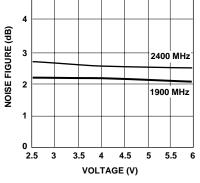

Standard test conditions apply unless otherwise noted. 2.4 GHz performance is performance in test circuit shown in Figure 18. Some aspects of performance are determined by the test circuit impedances.

20

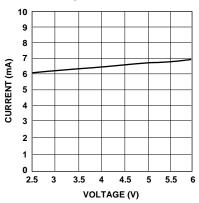

Figure 2. LNA Current vs. Device Voltage at 1900 MHz.

Figure 4. LNA Noise Figure vs. Device Voltage and Frequency.

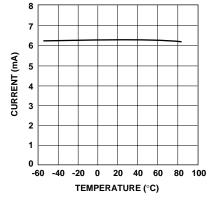

Figure 5. LNA Current vs. Temperature at 1900 MHz.

at 1900 MHz.

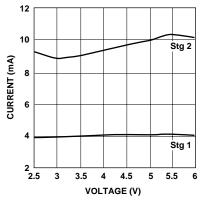

Figure 8. PA Current vs. Device Voltage at 1900 MHz.

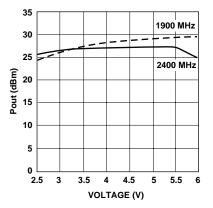

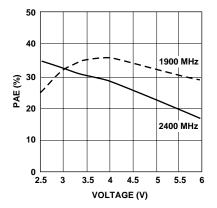

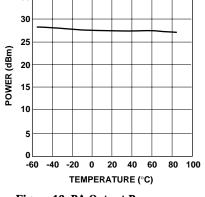

Figure 9. PA Output Power vs. Supply **Voltage and Frequency.**

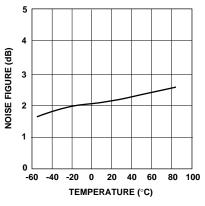

Figure 7. LNA Noise Figure vs. Temperature at 1900 MHz.

Figure 10. PA Power Added Efficiency vs. Supply Voltage and Frequency.

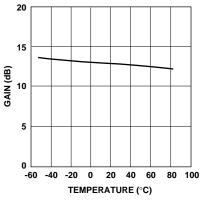

Figure 6. LNA Gain vs. Temperature

#### HPMX-3003 Typical Performance, continued

Standard test conditions apply unless otherwise noted. 2.4 GHz performance is performance in test circuit shown in Figure 18. Some aspects of performance are determined by the test circuit impedances.

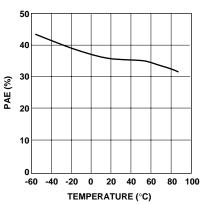

35

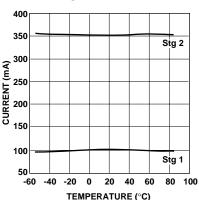

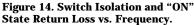

Figure 11. PA Current vs. Temperature at 1900 MHz and VD1 = 3.6V.

Figure 12. PA Output Power vs. Temperature at 1900 MHz and VD1 = 3.6V.

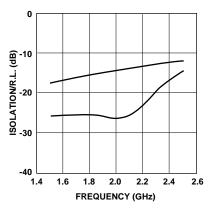

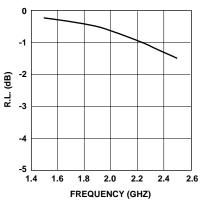

Figure 15. Switch "OFF" State Return Loss vs. Frequency.

Figure 13. PA Power Added Efficiency vs. Temperature at 1900 MHz and VD1 = 3.6V.

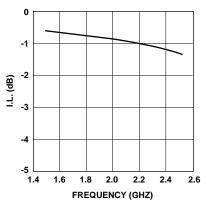

Figure 16. Switch "ON" State Insertion Loss vs. Frequency.

HPMX-3003 Typical Scattering Parameters for the LNA,

| Common Source, $Z_0 = 50 \Omega$ , $V_D = 3 V$ , $I_D = 5 mA$ | A | = 5  m/s | In | V. | 3 | . = | V | Ω | 50 | . = | $. Z_{0}$ | ource. | n So | ommo | C |

|---------------------------------------------------------------|---|----------|----|----|---|-----|---|---|----|-----|-----------|--------|------|------|---|

|---------------------------------------------------------------|---|----------|----|----|---|-----|---|---|----|-----|-----------|--------|------|------|---|

| Frequency | S    | 11   | S <sub>2</sub> | 21  | S     | 12   | S    | 22  |

|-----------|------|------|----------------|-----|-------|------|------|-----|

| GHz       | Mag  | Ang  | Mag            | Ang | Mag   | Ang  | Mag  | Ang |

| 1.0       | 0.97 | -27  | 2.00           | 158 | 0.035 | -12  | 0.91 | -22 |

| 1.2       | 0.96 | -33  | 2.06           | 150 | 0.036 | -17  | 0.91 | -27 |

| 1.4       | 0.95 | -40  | 2.13           | 142 | 0.037 | -23  | 0.90 | -31 |

| 1.6       | 0.94 | -47  | 2.20           | 134 | 0.038 | -30  | 0.88 | -36 |

| 1.8       | 0.92 | -54  | 2.28           | 125 | 0.038 | -39  | 0.87 | -41 |

| 2.0       | 0.90 | -62  | 2.36           | 117 | 0.039 | -49  | 0.86 | -46 |

| 2.2       | 0.88 | -70  | 2.45           | 109 | 0.039 | -62  | 0.84 | -50 |

| 2.4       | 0.85 | -79  | 2.54           | 100 | 0.040 | -77  | 0.83 | -55 |

| 2.6       | 0.82 | -89  | 2.63           | 90  | 0.042 | -95  | 0.81 | -60 |

| 2.8       | 0.78 | -99  | 2.71           | 81  | 0.045 | -115 | 0.79 | -65 |

| 3.0       | 0.75 | -110 | 2.79           | 71  | 0.050 | -135 | 0.78 | -71 |

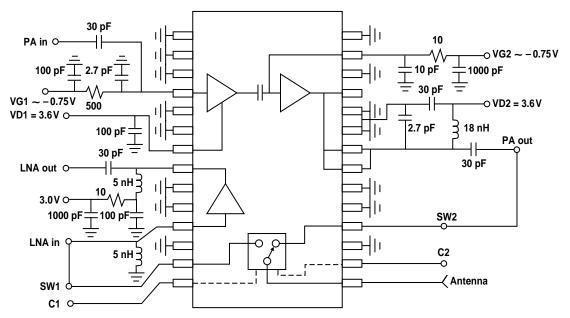

Figure 17. HPMX-3003 Test Circuit (1900 MHz).

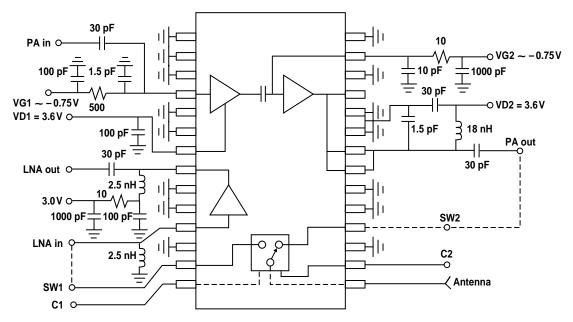

Figure 18. HPMX-3003 Test Circuit (2400 MHz).

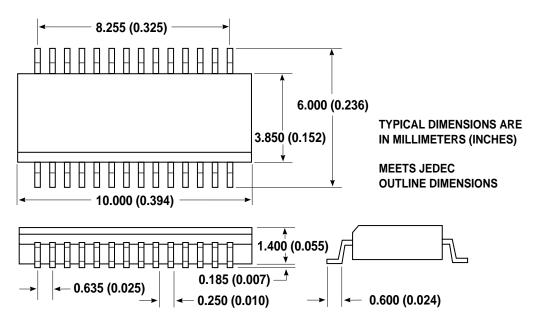

## JEDEC Standard SSOP-28 Package Outline Drawing

### **Part Number Ordering Information**

| Part Number   | No. of Devices | Container     |

|---------------|----------------|---------------|

| HPMX-3003-TR1 | 1000           | Tape and Reel |

| HPMX-3003-BLK | 25             | Таре          |