# Advance Information

# **Subcarrier Phase-Locked Loop**

The MC44144–1 is a gated phase–locked loop intended for, but not restricted to, video applications. The integrated circuit contains a gated phase detector, voltage controlled crystal oscillator, divide–by–4 circuitry, and a video clamp. This device provides a 4X reference frequency output, and a 1X reference frequency output.

The MC44144–1 is manufactured using Motorola's high density, bipolar MOSAIC $^{\text{TM}}$  process.

- 8-Pin DIP or Surface Mount Package

- Gated-Phase Detector

- Single Pin Voltage Controlled Crystal Oscillator

- 1X and 4X Subcarrier Output

- Operates Off of a Standard 5.0 V Supply

MOSAIC is a trademark of Motorola, Inc.

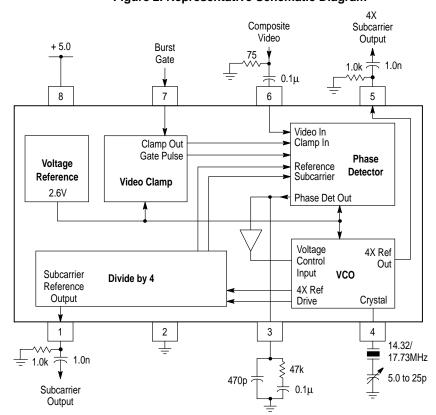

#### Representative Block Diagram Composite 4X Video Subcarrier +5.0Burst Output Gate 1.0n $0.1\mu$ 8 7 6 5 Video In Clamp Out Clamp In Gate Pulse Phase Voltage Reference Detector Reference Subcarrier Video Clamp 2.6V Phase Det Out Voltage 4X Ref Control Out Input VCO Subcarrier Divide by 4 Reference 4X Ref Output Crystal 1 2 3 14.32/ 1.0n 17.73MHz Subcarrier 5.0 to 25p Output

This document contains information on a new product. Specifications and information herein are subject to change without notice.

# MC44144-1

# SUBCARRIER PHASE-LOCKED LOOP

SEMICONDUCTOR TECHNICAL DATA

#### ORDERING INFORMATION

| Device    | Operating<br>Temperature Range           | Package |

|-----------|------------------------------------------|---------|

| MC44144D1 | T 0 to 70°C                              | SO-8    |

| MC44144P1 | $T_A = 0 \text{ to } 70^{\circ}\text{C}$ | Plastic |

#### **MAXIMUM RATINGS**

| Rating                         | Symbol           | Value      | Unit |

|--------------------------------|------------------|------------|------|

| Supply Voltage                 | Vcc              | 6.0        | Vdc  |

| Operating Ambient Temperature  | TA               | 0 to 70    | °C   |

| Storage Temperature Range      | T <sub>stg</sub> | -65 to 150 | °C   |

| Operating Junction Temperature | TJ               | 150        | °C   |

NOTE: ESD data available upon request.

#### RECOMMENDED OPERATING CONDITIONS

| Characteristic                                               | Pin | Symbol | Min | Тур | Max  | Unit |

|--------------------------------------------------------------|-----|--------|-----|-----|------|------|

| Supply Voltage                                               | 8   | VCC    | 4.5 | 5.0 | 5.5  | Vdc  |

| Composite Video Input [Note] Burst Amplitude to Acquire Lock | 6   | -      | 50  | 300 | 1000 | mVpp |

$\textbf{NOTE:} \quad \text{Total peak-to-peak voltage of video should not exceed ground or } \lor_{CC}.$

# **ELECTRICAL CHARACTERISTICS** $(V_{CC} = 5.0 \text{ Vdc}, T_A = 25^{\circ}\text{C})$

| Characteristic                                              | Pin  | Min | Тур   | Max  | Unit       |

|-------------------------------------------------------------|------|-----|-------|------|------------|

| Operating Current                                           | 8    | 8.0 | 10    | 12   | mA         |

| Burst Gate Threshold Voltage: VIH                           | 7    | 3.0 | -     | -    | Vdc        |

| VIL                                                         |      | _   | -     | 1.5  |            |

| Burst Gate Input Current: $I_{IH} (V_{in} = 5.0 \text{ V})$ |      | _   | _     | 20   | μΑ         |

| I <sub>IL</sub> (V <sub>in</sub> = 0 V)                     |      | _   | -     | -0.5 |            |

| 4X Subcarrier                                               | 5    |     |       |      |            |

| Output Voltage: (14.32 MHz)                                 |      | 400 | 610   | 650  | mVpp       |

| (17.73 MHz)                                                 |      | _   | 450   | -    |            |

| Output Impedance: (14.3 MHz and 17.73 MHz)                  |      | _   | 25    | _    | Ω          |

| Subcarrier Output                                           |      |     |       |      |            |

| Output Voltage: (3.58 MHz and 4.43 MHz)                     |      | 200 | 300   | 400  | mVpp       |

| Output Impedance: (3.58 MHz and 4.43 MHz)                   | 1    | _   | 200   | _    | Ω          |

| Phase Angle (Note 1)                                        |      | -   | -60   | _    | deg        |

| Phase Sensitivity (Notes 1 & 2)                             |      | -   | 3.0   | -    | Note 2     |

| Static Phase Error (Note 2)                                 | 1, 2 | -   | 3     | -    | deg/100 Hz |

| Phase–Locked Loop Pull–In Range                             |      | _   | ± 350 | -    | Hz         |

| Phase–Locked Loop Hold–In Range                             |      | _   | ± 500 | _    |            |

NOTES: 1. Referenced to composite video input color burst.

Figure 1. Typical VCXO Gain 17.745 (WHz) 17.745 (WHz) 17.735 (WHz) 17.735 (WHz) 17.735 (WHz) 14.322 4Xf<sub>SC</sub>, OUTPUT (PIN 5) FREQUENCY (MHz) FOR NTSC **KOPAL** 14.320  $\mathsf{KO}_{\mathsf{NTSC}}$ 14.318 14.316 The gain must be estimated from the operating point. KO<sub>PAL</sub> is the gain for PAL applications and KO<sub>NTSC</sub> is the gain for NTSC applications. 14.314 ) | 17.719 | X | Š | Š 14.312 -1.05.0 VCO CONTROL VOLTAGE (PIN 3 VOLTAGE) (V)

**Table 1. Crystal Specifications**

| Frequency                                          | 14.31818 MHz (NTSC)<br>17.734475 MHz (PAL) |

|----------------------------------------------------|--------------------------------------------|

| Mode                                               | Fundamental                                |

| Frequency Tolerance<br>@ 25°C<br>df/dfo 0°C – 70°C | 40 ppm                                     |

| Load Capacitance                                   | 20 pF                                      |

| ESR                                                | 50 Ω                                       |

| C1 (Internal Series Capacitance)                   | 15 mpF                                     |

<sup>2.</sup> See paragraph 1 of the Functional Description text.

Figure 2. Representative Schematic Diagram

#### **FUNCTIONAL DESCRIPTION**

The MC44144–1 is designed to implement the color sync function in a video system. When provided NTSC/PAL composite video or composite chroma and burst gate inputs, the IC will phase–lock a Voltage Controlled Crystal Oscillator (VCXO) to the color burst. Both 4X and 1X subcarrier frequency outputs are provided by the IC. The VCXO operates off of a 4X subcarrier crystal and The VCXO operates off a 4X subcarrier crystal and is capable of at least  $\pm\,600$  Hz of pull–in. The tradeoff for such a wide pull–in range is a resultant "soft" lock, or a 3° phase shift per 100 Hz change in oscillator free–run or input reference frequency.

In addition to providing the gate pulse for the MC44144–1 phase detector, the Burst Gate input also initiates a clamp pulse that sets up the level of the composite video at the input to the Phase Detector. The start and duration of the Gate Pulse should be timed so that the pulse envelopes the color burst of the video signal, but not so wide as to gate sync or video into the Phase Detector.

The Phase Detector is enabled when the voltage at the Burst Gate input (Pin 7) is above the nominal 2.2 V threshold. While this makes possible the ability to lock to a color burst, it does not exclude the possibility of lock to a constant reference. If a constant source is to be the reference, the Phase Detector can be permanently enabled by holding the voltage on the Phase Detector input pin higher than the threshold voltage.

The phase detector gain must be specified in two ways, for a constant reference and for a burst–locked application. The gain in a constant reference application is specified by the maximum current output with the maximum phase error. For a maximum phase error of  $\pi/2$  radians the maximum current available is approximately 200  $\mu A$ . So the phase detector gain is defined as,

$$KPD = 200/(\pi/2)(\mu A/rad \cdot sec)$$

For a burst-locked application, the Phase Detector is active for only the duration of the color burst. Therefore the phase detector gain must be specified as an average gain over a line period. In this case the phase detector gain for NTSC and for PAL applications is,

KPD<sub>NTSC</sub> =

$$(8/(\pi/2))(\mu A/rad \cdot sec)$$

and,

KPD<sub>PAL</sub> =  $(7/(\pi/2))(\mu A/rad \cdot sec)$

A suitable filter for both types of applications is shown in the test schematic Figure 2. This same filter also works for both NTSC and PAL applications.

The 4X subcarrier Voltage Controlled Crystal Oscillator (VCXO) uses a design that enables the use of series or parallel resonant types of crystals. Still, layout and crystal positioning are critical as the oscillator frequency is sensitive to shunt capacitance. Care should be taken to keep the crystal close to the IC and crystal switching should be avoided. A suitable parallel type crystal would meet the specifications in Table 1.

A plot showing the VCXO gain is shown in Figure 1. From this plot the gain must be estimated from the operating point. KOPAL is the gain for PAL applications and KONTSC is the gain for NTSC applications.

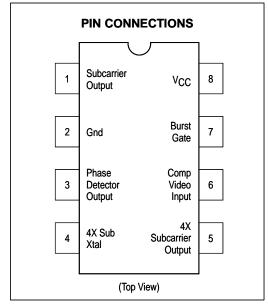

# PIN FUNCTION DESCRIPTION

| Name                                                                                          | Pin | Representative Circuitry                               | Description                                                                                                                                                                                            | Expected Waveforms                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------|-----|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Subcarrier<br>Output                                                                          | 1   | VCC 200   5.0k   =                                     | Subcarrier Output. A phase–locked reference of the PAL or NTSC color burst is output at this pin.                                                                                                      | A 300 mVpp square wave is output.<br>Some high frequency content is<br>present.                                                                                                                                        |

| Ground                                                                                        | 2   |                                                        | Circuit Ground                                                                                                                                                                                         |                                                                                                                                                                                                                        |

| Phase<br>Detector<br>Output                                                                   | 3   | 1.0k 31k 33k 2.5V =                                    | The error current from the phase detector is output at this pin. A filter circuit should be connected at this pin.                                                                                     | A beat waveform, showing both horizontal period and half the subcarrier period, is present.  1/2 Subcarrier Period  Line Period  Vlock                                                                                 |

| 4X Sub Xtal                                                                                   | 4   | 400 Vref Vcc Vcc Vref Vref 2.0k                        | Crystal Oscillator Pin. A 4X subcarrier parallel resonant crystal, in series with a 5.0 to 25 pF trimmer capacitor provides the resonant element for the Voltage Controlled Crystal Oscillator (VCXO). | Approximately 40 mVpp. A scope probe will disturb the frequency of oscillation.                                                                                                                                        |

| 4X Subcarrier<br>Output (or<br>Black Burst)                                                   | 5   | VCC<br>5.0k                                            | Buffered output from the 4X voltage controlled oscillator.                                                                                                                                             | The sinusoidal 4Xf <sub>SC</sub> oscillator output is available at this pin. The output is nominally: 525 mVpp for NTSC, 425 mVpp for PAL.                                                                             |

| Composite Video Input (Black Burst, Continuous Wave, or Composite Chroma can also be applied) | 6   | V <sub>CC</sub><br>V <sub>CC</sub><br>V <sub>22k</sub> | Composite Video Input. Color burst from the video present at this pin is used as a reference to phase lock the VCXO. Positive or negative video may be used.                                           | Composite video should be applied at this pin. The color burst amplitude of the input video should be at least 50 mV, but no more than 1000 mV. The waveform at this pin should not exceed ground or V <sub>CC</sub> . |

| Burst Gate<br>Input                                                                           | 7   | VCC                                                    | Input for the phase detector gate pulse. TTL compatible. The threshold is nominally 2.6V.                                                                                                              | A positive going gate pulse should be applied at this pin. The Burst Gate input should envelope the color burst.  Pin 6  Pin 7  2.2V                                                                                   |

| Vcc                                                                                           | 8   |                                                        | Power Supply Pin. 5.0 Vdc should be applied at this pin.                                                                                                                                               |                                                                                                                                                                                                                        |

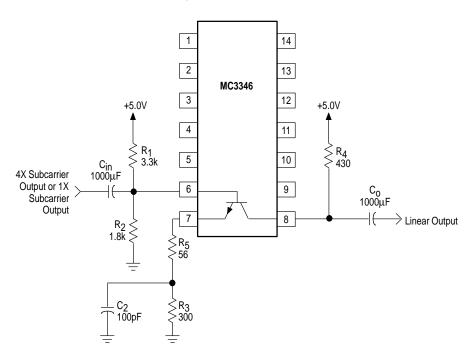

## **Linear and TTL Output Buffers**

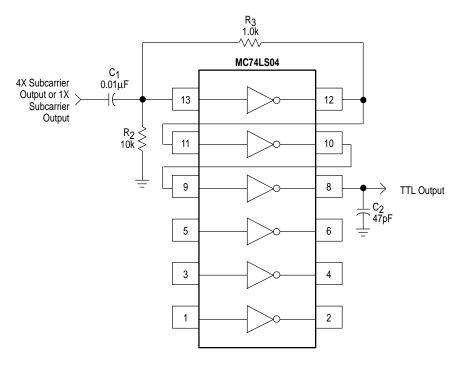

The output buffers of the MC44144-1 are not designed to any specific logic family. If it is desired, Linear or TTL buffers can be added externally. Figure 3 shows an example of a

Linear buffer using an MC3346 Transistor array; virtually any utility transistor can be used. Figure 4 shows a TTL type buffer using an MC74LS04 buffer.

Figure 3. Linear Buffer

Figure 4. TTL Buffer

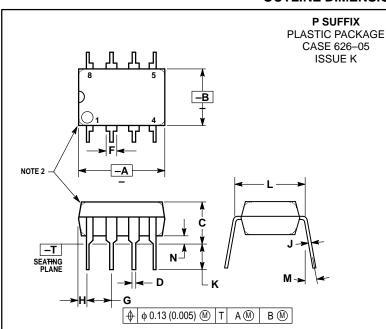

## **OUTLINE DIMENSIONS**

#### NOTES:

- DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

- PACKAGE CONTOUR OPTIONAL (ROUND OR SQUARE CORNERS).

- DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982. 4. 626-03 AND 626-04 OBSOLETE, NEW STANDARD 626-05.

|     | MILLIM   | ETERS | INCHES    |       |  |

|-----|----------|-------|-----------|-------|--|

| DIM | MIN      | MAX   | MIN       | MAX   |  |

| Α   | 9.40     | 10.16 | 0.370     | 0.400 |  |

| В   | 6.10     | 6.60  | 0.240     | 0.260 |  |

| С   | 3.94     | 4.45  | 0.155     | 0.175 |  |

| D   | 0.38     | 0.51  | 0.015     | 0.020 |  |

| F   | 1.02     | 1.78  | 0.040     | 0.070 |  |

| G   | 2.54 BSC |       | 0.100 BSC |       |  |

| Н   | 0.76     | 1.27  | 0.030     | 0.050 |  |

| J   | 0.20     | 0.30  | 0.008     | 0.012 |  |

| K   | 2.92     | 3.43  | 0.115     | 0.135 |  |

| L   | 7.62     | BSC   | 0.300 BSC |       |  |

| M   | -        | 10°   | -         | 10°   |  |

| N   | 0.76     | 1.01  | 0.030     | 0.040 |  |

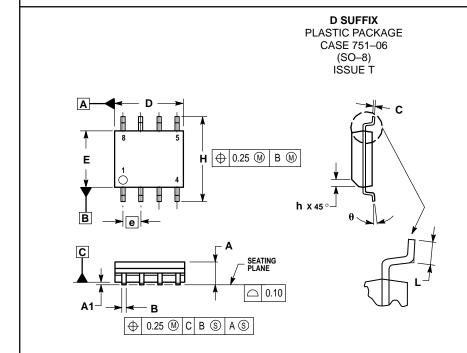

#### NOTES:

- NOTES:

1 DIMENSIONING AND TOLERANCING PER ASME

Y14.5M, 1994.

2 DIMENSIONS ARE IN MILLIMETER.

3 DIMENSION D AND E DO NOT INCLUDE MOLD

PROTRUSION.

- PRU I RUSION.

AMAIMUM MOLD PROTRUSION 0.15 PER SIDE.

DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTAL IN EXCESS OF THE B DIMENSION AT MAXIMUM MATERIAL CONDITION.

MILLIMETERS MIN MAX 1.35 1.75 1.35 Α A1 0.10 0.25 В 0.35 0.49 0.19 0.25 D 4.80 5.00 Е 3.80 4.00 1.27 BSC 5.80 6.20 0.25 0.40 0.50

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and manufacture of the part. Motor

Mfax is a trademark of Motorola, Inc.

#### How to reach us:

**USA/EUROPE/Locations Not Listed**: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447

JAPAN: Motorola Japan Ltd.; SPD, Strategic Planning Office, 141, 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan. 81–3–5487–8488

#### Customer Focus Center: 1-800-521-6274

Mfax™: RMFAX0@email.sps.mot.com - TOUCHTONE 1-602-244-6609

Motorola Fax Back System - US & Canada ONLY 1-800-774-1848

- http://sps.motorola.com/mfax/

**ASIA/PACIFIC:** Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2, Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852–26629298

HOME PAGE: http://motorola.com/sps/

♦ MC44144–1/D