# REALTEK SINGLE-CHIP **USB To FAST ETHERNET** NTROLLER WITH MII INTERFACE **RTL8150L(M)**

#### 1 Features:

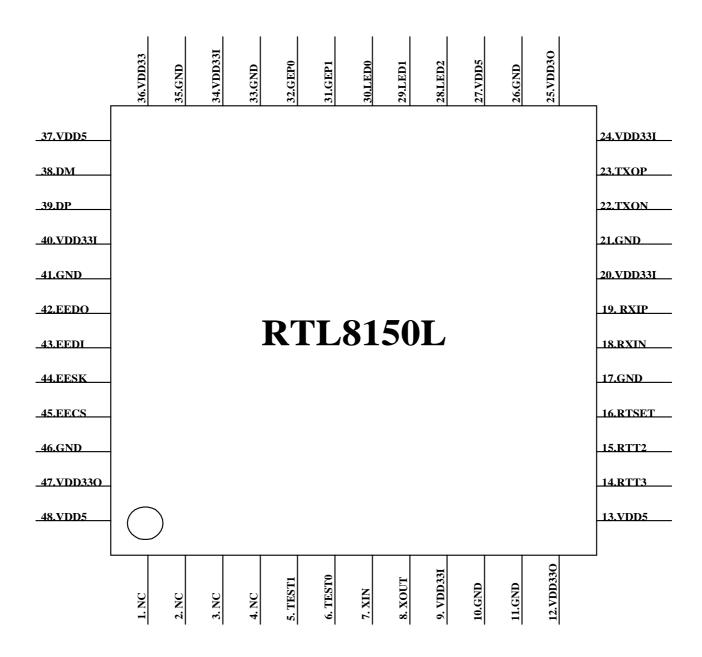

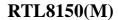

- RTL8150L supports 48 pins LQFP

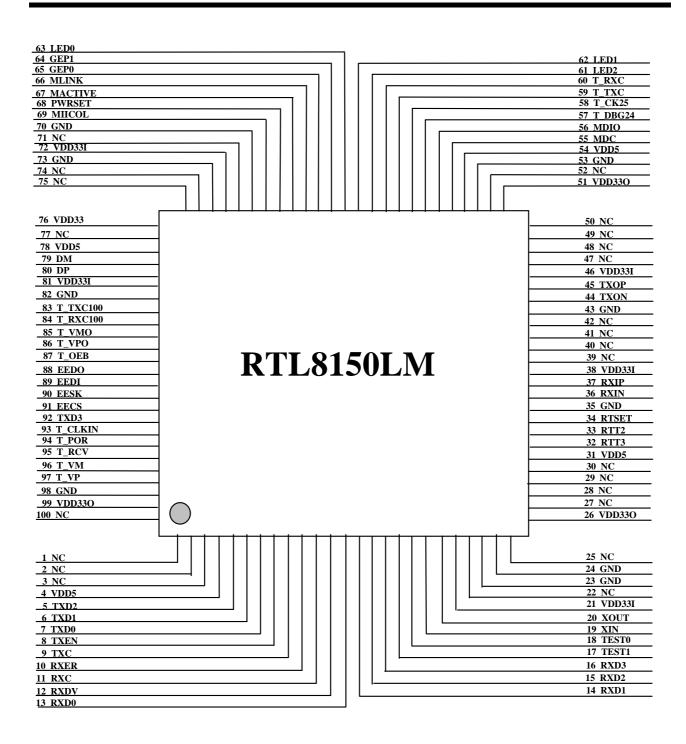

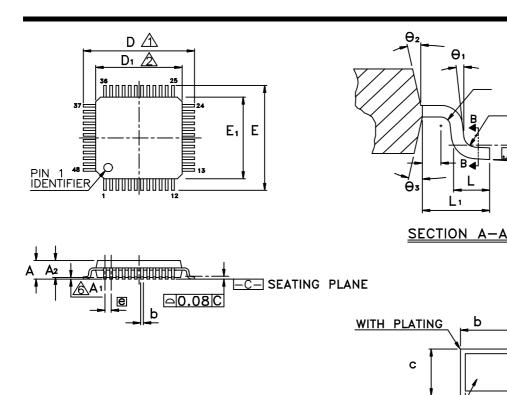

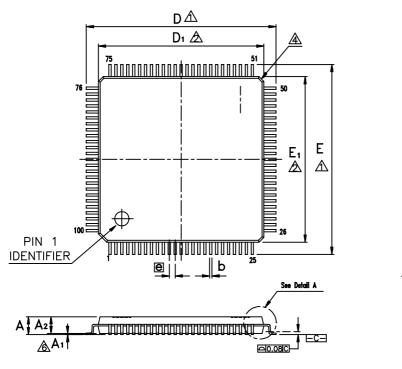

- RTL8150LM supports 100 pins LQFP

- Integrated Fast Ethernet MAC, Physical chip and transceiver in one chip

- Supports 10 Mb/s and 100 Mb/s N-way Auto-negotiation operation.

- Single-chip USB to Fast Ethernet controller

- ♦ Compliant to USB interface ver 1.0/1.1.

- → Full-Speed (12 Mb/s) USB Device

- ♦ Supports all USB standard commands

- **♦** Supports Suspend/Resume logic

- ♦ Supports 4 endpoints

- 1 control endpoint with maximum 8-byte packet

- 1 bulk IN endpoint with 64 bytes/packet

- 1 bulk OUT endpoint with 64 bytes/packet

- 1 interrupt IN endpoint with 8 bytes/packet

- RTL8150LM supports MII interface

- Supports Wake-On-LAN function and remote wakeup (Magic Packet\*, LinkChg and Microsoft® wake-up frame).

- 18K bytes SRAM built in.(2k bytes for Tx buffer, and 16k bytes for Rx buffer).

- Uses 93C46 to store resource configuration, ID parameter, etc.

- Supports LED pins for various network activity indications.

- Half/Full duplex 10/100Mbps operation.

- Supports Full Duplex Flow Control (IEEE 802.3x)

- Uses 25MHz crystal as the internal clock source.

- 5 V power supply

www.Datasheethl.com \*Third-party brands and names are the property of their respective owners.

2002/2/18 Ver1.40

# **2 General Description**

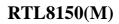

The RTL8150L controller is a 48-pin LQFP single chip that supports USB to 10/100Mbps Fast Ethernet function. To connect to Home PNA 1.0 PHY or HomePNA 2.0 PHY, the 100-pin RTL8150LM provides MII interface supporting the MII transmit clock from 0.1 MHz to 25 MHz.

The Realtek RTL8150L(M) is a highly integrated and cost-effective single-chip Fast Ethernet controller that provides USB to Fast Ethernet capability, and full compliance with IEEE 802.3u 100Base-T specifications and IEEE 802.3x Full Duplex Flow Control. It also supports power management for modern operating systems that is capable of Operating System Directed Power Management (OSPM) to achieve the most efficient power management. Besides the PM feature, the RTL8150L(M) also supports remote wake-up (including AMD Magic Packet\*, LinkChg, and Microsoft® wake-up frame).

For sake of cost-effective, the RTL8150L(M) only requires one 25MHz crystal as its internal clock source, and requires no "glue" logic or external memory.

The RTL8150L(M) keeps network maintenance cost low and eliminates usage barriers. It is the easiest way to connect a PC to the computer network without opening the cover, adding cards, reconfiguring software, or any of the other technicalities.

# 3 Pin Assignment

# 4 Pin Descriptions

# 4.1 RTL8150L Pin Descriptions

### **4.1.1 POWER PINS**

| Symbol | Type | Pin No                | Description                                    |

|--------|------|-----------------------|------------------------------------------------|

| VDD5   | P    | 13,27,37,48           | 5.0V power supply as internal regulators input |

| VDD33O | P    | 12,25,47              | 3.3V power output from internal regulators     |

|        |      |                       | Pin 47: Digital power                          |

| VDD33I | P    | 9,20,24,34,40         | 3.3V power                                     |

|        |      |                       | Pin 40: Digital power                          |

| GND    | P    | 10,11,17,21,26,33,35, | Ground                                         |

|        |      | 41,46                 |                                                |

| VDD33  | P    | 36                    | 3.3V Standby power                             |

### 4.1.2 USB INTERFACE

| Symbol | Type | Pin No | Description                                     |

|--------|------|--------|-------------------------------------------------|

| DM     | I/O  | 38     | Negative data line of USB differential data bus |

| DP     | I/O  | 39     | Positive data line of USB differential data bus |

### 4.1.3 10/100 BASE-T UTP INTERFACE

| Symbol | Type | Pin No | Description                 |  |  |  |

|--------|------|--------|-----------------------------|--|--|--|

| TXD+   | 0    | 23     | 10/100 BASE-T transmit data |  |  |  |

| TXD-   | 0    | 22     | 10/100 BASE-T transmit data |  |  |  |

| RXIN+  | I    | 19     | 10/100 BASE-T receive data  |  |  |  |

| RXIN-  | I    | 18     | 10/100 BASE-T receive data  |  |  |  |

| X1     | I    | 7      | 25 MHz crystal input        |  |  |  |

| X2     | 0    | 8      | 25 MHz crystal output       |  |  |  |

### 4.1.4 LED Interface

| Symbol     | Type | Pin No   | Description |                      |            |             |                 |  |

|------------|------|----------|-------------|----------------------|------------|-------------|-----------------|--|

| LED0, 1, 2 | О    | 30,29,28 | LED pins(ac | LED pins(active low) |            |             |                 |  |

|            |      |          | LEDS1-0     | 00                   | 01         | 10          | 11              |  |

|            |      |          | LED0        | TX/RX                | TX/RX      | TX          | TX/RX@ LINK10   |  |

|            |      |          | LED1        | LINK100              | LINK10/100 | LINK10/100  | TX/RX@ LINK100  |  |

|            |      |          | LED2        | LINK10               | FULL       | RX          | FULL            |  |

|            |      |          | During pow  |                      |            | LED's are O | FF if SYSLED in |  |

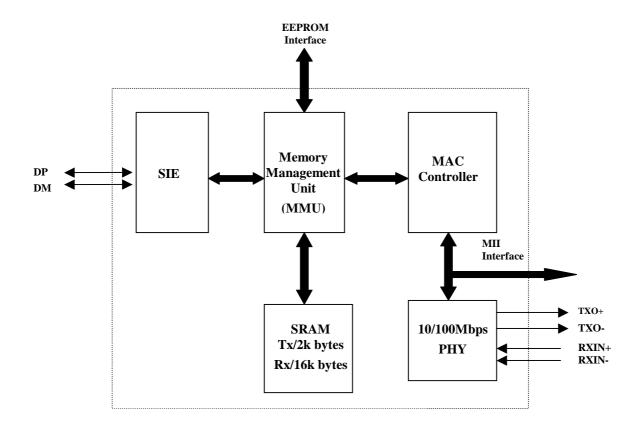

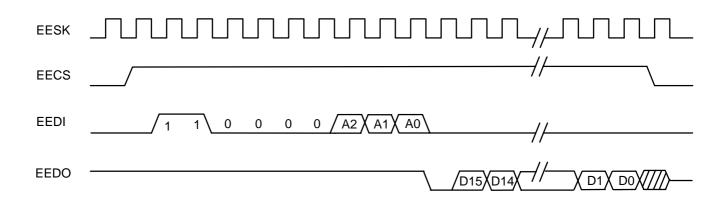

### 4.1.5 EEPROM INTERFACE

| Symbol | Type | Pin No | Description       |  |  |  |

|--------|------|--------|-------------------|--|--|--|

| EECS   | 0    | 45     | 93C46 chip select |  |  |  |

| EESK   | 0    | 44     | 93C46 clock       |  |  |  |

| EEDI   | О    | 43     | 93C46 data input  |  |  |  |

| EEDO   | I    | 42     | 93C46 data output |  |  |  |

### 4.1.6 TEST AND THE OTHER PINS

| Symbol  | Type | Pin No  | Description                                                  |  |  |

|---------|------|---------|--------------------------------------------------------------|--|--|

| RTT2-3  | TEST | 15,14   | Chip test pins.                                              |  |  |

| TEST0-1 | TEST | 6,5     | Chip test pins.                                              |  |  |

| RTSET   | I/O  | 16      | This pin must be pulled low by a $1.69$ K $\Omega$ resistor. |  |  |

| GEP0-1  | I/O  | 32,31   | General purpose pin 0,1                                      |  |  |

| NC      |      | 1,2,3,4 | Reserved                                                     |  |  |

# **4.2 RTL8150LM Pin Descriptions**

#### 4.2.1 RTL8150LM POWER PINS

| Symbol | Type | Pin No                | Description                                    |

|--------|------|-----------------------|------------------------------------------------|

| VDD5   | P    | 4,31,54,78            | 5.0V power supply as internal regulators input |

| VDD33O | P    | 26,51,99              | 3.3V power output from internal regulators     |

|        |      |                       | Pin 99: Digital power                          |

| VDD33I | P    | 21,38,46,72,81        | 3.3V power                                     |

|        |      |                       | Pin 81: Digital power                          |

| GND    | P    | 23,24,35,43,53,70,73, | Ground                                         |

|        |      | 82,98                 |                                                |

| VDD33  | P    | 76                    | 3.3V Standby power                             |

#### 4.2.2 RTL8150LM USB INTERFACE

| Symbol | Type | Pin No | Description                                     |  |  |

|--------|------|--------|-------------------------------------------------|--|--|

| DM     | I/O  | 79     | Negative data line of USB differential data bus |  |  |

| DP     | I/O  | 80     | Positive data line of USB differential data bus |  |  |

### 4.2.3 RTL8150LM 10/100 BASE-T UTP INTERFACE

| Symbol | Type | Pin No | Description                 |

|--------|------|--------|-----------------------------|

| TXD+   | О    | 45     | 10/100 BASE-T transmit data |

| TXD-   | 0    | 44     | 10/100 BASE-T transmit data |

| RXIN+ | I | 37 | 10/100 BASE-T receive data |

|-------|---|----|----------------------------|

| RXIN- | I | 36 | 10/100 BASE-T receive data |

| X1    | I | 19 | 25 MHz crystal input       |

| X2    | 0 | 20 | 25 MHz crystal output      |

### 4.2.4 RTL8150LM MII INTERFACE

| Symbol                 | Type | Pin No      | Description                                                                             |

|------------------------|------|-------------|-----------------------------------------------------------------------------------------|

| RXD0-3                 | I    | 13,14,15,16 | MII receive data 0-3                                                                    |

| TXD0-3                 | 0    | 7,6,5,92    | MII transmit data 0-3                                                                   |

| TXC                    | I    | 9           | MII Transmit Clock: 25 MHz or 2.5 MHz Tx clock supplied by                              |

|                        |      |             | the external PMD device.                                                                |

| MIICOL                 | I    | 69          | MII Collision Detected: This signal is asserted high                                    |

|                        |      |             | synchronously by the external physical unit upon detection of a                         |

|                        |      |             | collision on the medium. It will remain asserted as long as the                         |

|                        |      |             | collision condition persists.                                                           |

| TXEN                   | О    | 8           | MII Transmit Enable: Indicates the presence of valid nibble data on TXD[3:0].           |

| RXC                    | I    | 11          | MII Receive Clock: 25 MHz or 2.5 MHz Rx clock supplied by the                           |

|                        |      |             | external PMD device.                                                                    |

| RXDV                   | I    | 12          | MII Receive Data Valid: Data valid is asserted by an external                           |

|                        |      |             | PHY when receive data is present on the RXD[3:0], and it is                             |

|                        |      |             | de-asserted at the end of the packet. This signal is valid on the                       |

|                        | _    |             | rising edge of the RXC.                                                                 |

| RXER                   | I    | 10          | MII Receive Error: This pin is asserted to indicate that invalid                        |

|                        |      |             | symbol has been detected in 100Mbps MII mode. This signal is                            |

|                        |      |             | synchronized to RXC and can be asserted for a minimum of one                            |

| MDC                    |      | <i></i>     | receive clock.                                                                          |

| MDC                    | О    | 55          | MII Management Data Clock: Synchronous clock for MDIO data transfer.                    |

| MDIO                   | I/O  | 5.0         | U WII DI U                                                                              |

| MDIO                   | I/O  | 56          | MII Management Data: Bi-directional signal used to transfer                             |

| M111                   | т т  |             | management information.                                                                 |

| Mlink                  | I    | 66          | MII link status notification, indicates to the MAC that external PMD is link Ok or not. |

| Ma atimala             | Ī    | (7          |                                                                                         |

| Mactive <mark>b</mark> | 1    | 67          | MII active status notification, when Mactiveb=high, Mlink is low                        |

|                        |      |             | active, and vice versa.                                                                 |

### 4.2.5 RTL8150LM LED Interface

| Symbol     | Type | Pin No   | Description          |         |            |             |                 |

|------------|------|----------|----------------------|---------|------------|-------------|-----------------|

| LED0, 1, 2 | О    | 63,62,61 | LED pins(active low) |         |            |             |                 |

|            |      |          | LEDS1-0              | 00      | 01         | 10          | 11              |

|            |      |          | LED0                 | TX/RX   | TX/RX      | TX          | TX/RX@ LINK10   |

|            |      |          | LED1                 | LINK100 | LINK10/100 | LINK10/100  | TX/RX@ LINK100  |

|            |      |          | LED2                 | LINK10  | FULL       | RX          | FULL            |

|            |      |          | During pow           |         |            | LED's are O | FF if SYSLED in |

### 4.2.6 RTL8150LM EEPROM INTERFACE

| Symbol | Type | Pin No | Description       |

|--------|------|--------|-------------------|

| EECS   | 0    | 91     | 93C46 chip select |

| EESK   | 0    | 90     | 93C46 clock       |

| EEDI   | 0    | 89     | 93C46 data input  |

| EEDO   | I    | 88     | 93C46 data output |

# 4.2.7 RTL8150LM TEST AND THE OTHER PINS

| Symbol   | Type | Pin No                                                                         | Description                                                        |  |  |  |

|----------|------|--------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|

| RTT2-3   | TEST | 33,32                                                                          | Chip test pins.                                                    |  |  |  |

| T_***    | TEST | 17,18,57,58,59,60,83,<br>84,85,86,87,93,94,95,<br>96,97                        | Chip test pins.                                                    |  |  |  |

| RTSET    | I/O  | 34                                                                             | This pin must be pulled low by a $1.69 \mathrm{K}\Omega$ resistor. |  |  |  |

| GEP0-1   | I/O  | 65,64                                                                          | General purpose pin 0,1                                            |  |  |  |

| PWRESETB | 0    | 68                                                                             | Power-on reset for external PHY, active low                        |  |  |  |

| NC       |      | 1,2,3,22,25,27,28,29,<br>30,39,40,41,42,47,48,<br>49,50,52,71,74,75,77,<br>100 | Reserved                                                           |  |  |  |

### 5. SIE -USB Commands

### **5.1 Vender Memory Read**

#### Setup transaction:

| BmReq      | bReq    | wValueL    | wValueH    | wIndexL | wIndexH | wLengthL | wLengthH |

|------------|---------|------------|------------|---------|---------|----------|----------|

| C0         | 05      | regoffsetL | regoffsetH | 00      | 00      | LengL    | LengH    |

| Data trans | action: | •          | •          | •       |         | •        | •        |

| DATA0      | DATA1   | DATA2      | DATA3      | DATA4   | DATA5   | DATA6    | DATA7    |

| reo()      | reo1    | reo2       | reg3       | reo4    | reo5    | reo6     | reo7     |

The total length response by 8150L depends on (LengH,LengL) values.

### **5.2 Vender Memory Write**

#### Setup transaction:

| BmReq      | bReq    | wValueL    | wValueH    | wIndexL | wIndexH | wLengthL | wLengthH |

|------------|---------|------------|------------|---------|---------|----------|----------|

| 40         | 05      | regoffsetL | regoffsetH | 00      | 00      | LenghL   | LenghH   |

| Data trans | action: |            |            |         |         |          |          |

| DATA0      | DATA1   | DATA2      | DATA3      | DATA4   | DATA5   | DATA6    | DATA7    |

| reo()      | reo1    | reg2       | reo3       | reo4    | reo5    | reo6     | reo7     |

Offset 0x1200 to 0x127f register must write by word mode.

#### 5.3 Set address

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 00    | 05   | addrL   | addrH   | 00      | 00      | 00       | 00       |

Data transaction: None

### **5.4 Clear Feature EP0**

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 02    | 01   | 00      | 00      | 00      | 00      | 00       | 00       |

Data transaction: None

### 5.5 Clear Feature EP1

#### Setup transaction:

| BmReq | breq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 02    | 01   | 00      | 00      | 81      | 00      | 00       | 00       |

Data transaction: None

#### **5.6 Clear Feature EP2**

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 02    | 01   | 00      | 00      | 02      | 00      | 00       | 00       |

Data transaction: None

#### 5.7 Clear Feature EP3

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 02    | 01   | 00      | 00      | 83      | 00      | 00       | 00       |

Data transaction: None

#### 5.8 Set Feature EP1

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 02    | 03   | 00      | 00      | 81      | 00      | 00       | 00       |

Data transaction: None

### 5.9 Set Feature EP2

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 02    | 03   | 00      | 00      | 02      | 00      | 00       | 00       |

Data transaction: None

### **5.10 Set Feature EP3**

Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 02    | 03   | 00      | 00      | 00      | 83      | 00       | 00       |

Data transaction: None

### **5.11 Set Interface 0**

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 01    | 0B   | 00      | 00      | 00      | 00      | 00       | 00       |

Data transaction: None

### **5.12 Set Feature Device**

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 00    | 03   | 01      | 00      | 00      | 00      | 00       | 00       |

Data transaction: None

### **5.13 Clear Feature Device**

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 00    | 01   | 01      | 00      | 00      | 00      | 00       | 00       |

Data transaction: None

# 5.14 Set Config 0

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 00    | 09   | 00      | 00      | 00      | 00      | 00       | 00       |

Data transaction: None

# 5.15 Set Config 1

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 00    | 09   | 01      | 00      | 00      | 00      | 00       | 00       |

Data transaction: None

### 5.16 Get Descriptor Device

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 80    | 06   | 00      | 01      | 00      | 00      | Lengh_L  | Lengh_H  |

#### Data transaction:

| DATA0 | DATA1 | DATA2 | DATA3 | DATA4 | DATA5 | DATA6 | DATA7 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 12    | 01    | 10    | 01    | 00    | 00    | 00    | 08    |

| DA    | 0B    | 50    | 81    | 00    | 01    | 01    | 02    |

| 03    | 01    | -     | -     | -     | -     | -     | -     |

The total length response by 8150L depends on (LengH,LengL) values.

### 5.17 Get Descriptor Configuration

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 80    | 06   | 00      | 02      | 00      | 00      | Lengh_L  | Lengh_H  |

#### Data transaction:

| DATA0 | DATA1 | DATA2 | DATA3 | DATA4 | DATA5 | DATA6 | DATA7 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 09    | 02    | 27    | 00    | 01    | 01    | 00    | A0    |

| 50    | 09    | 04    | 00    | 00    | 03    | FF *  | 00    |

| FF *  | 00    | 07    | 05    | 81    | 02    | 40    | 00    |

| 00    | 07    | 05    | 02    | 02    | 40    | 00    | 00    |

| 07    | 05    | 83    | 03    | 08    | 00    | 01    | -     |

The total length response by 8150L depends on (LengH,LengL) values.

### 5.18 Get Descriptor String Index 0

#### Setup transaction:

| BmReq      | bReq    | w ValueL | w ValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|------------|---------|----------|----------|---------|---------|----------|----------|

| 80         | 06      | 00       | 03       | 00      | 00      | Lengh_L  | Lengh_H  |

| Data trans | action: |          |          |         |         |          |          |

#### Data transaction:

| DATA0 | DATA1 | DATA2 | DATA3 | DATA4 | DATA5 | DATA6 | DATA7 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 04    | 03    | 04    | 09    | -     | -     | -     | -     |

The total length response by 8150L depends on (LengH,LengL) values.

### **5.19 Get Descriptor String Index 1**

<sup>\*</sup>The E version is 0xFF, before E version it is 0x00.

| Setup     | transaction:                            |

|-----------|-----------------------------------------|

| ~ • • • • | *************************************** |

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 80    | 06   | 01      | 03      | 09      | 04      | Lengh_L  | Lengh_H  |

#### Data transaction:(REALTEK)

| DATA0 | DATA1 | DATA2 | DATA3 | DATA4 | DATA5 | DATA6 | DATA7 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 10    | 03    | 52    | 00    | 45    | 00    | 41    | 00    |

| 4C    | 00    | 54    | 00    | 45    | 00    | 4B    | 00    |

The total length response by 8150L depends on (LengH,LengL) values.

### 5.20 Get Descriptor String Index 2

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 80    | 06   | 02      | 03      | 09      | 04      | Lengh_L  | Lengh_H  |

#### Data transaction:(USB 10/100 LAN)

| DATA0 | DATA1 | DATA2 | DATA3 | DATA4 | DATA5 | DATA6 | DATA7 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 1E    | 03    | 55    | 00    | 53    | 00    | 42    | 00    |

| 20    | 00    | 31    | 00    | 30    | 00    | 2F    | 00    |

| 31    | 00    | 30    | 00    | 30    | 00    | 20    | 00    |

| 4C    | 00    | 41    | 00    | 4E    | 00    | -     | -     |

### 5.21 Get Descriptor String Index 3

#### Setup transaction:

| BmReq | bReq | wValueL | wValueH | wIndexL | WindexH | wLengthL | wLengthH |

|-------|------|---------|---------|---------|---------|----------|----------|

| 80    | 06   | 03      | 03      | 09      | 04      | Lengh_L  | Lengh_H  |

#### Data transaction:

| DATA0 | DATA1 | DATA2 | DATA3 | DATA4 | DATA5 | DATA6 | DATA7 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0A    | 03    | 30    | 00    | 30    | 00    | 30    | 00    |

| 31    | 00    | -     | -     | -     | -     | -     | -     |

The total length response by 8150L depends on (LengH,LengL) values.

### 5.22 Get Config

#### Setup transaction:

| BmRe | q bReq | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|------|--------|---------|---------|---------|---------|----------|----------|

| 80   | 08     | 00      | 00      | 00      | 00      | 01       | 00       |

| _    |        |         |         |         |         | •        |          |

#### Data transaction:

| DATA0 | DATA1 | DATA2 | DATA3 | DATA4 | DATA5 | DATA6 | DATA7 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Value | -     | -     | -     | -     | -     | -     | -     |

### **5.23 Get Status Device**

#### Setup transaction:

| BmReq      | bReq    | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|------------|---------|---------|---------|---------|---------|----------|----------|

| 80         | 00      | 00      | 00      | 00      | 00      | 02       | 00       |

| Data trans | action: | •       | •       | •       | •       | •        | •        |

| DATA0      | DATA1   | DATA2   | DATA3   | DATA4   | DATA5   | DATA6    | DATA7    |

| Value      | Volue   |         |         |         |         |          |          |

#### 5.24 Get Status EP0

#### Setup transaction:

| BmReq      | bReq    | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|------------|---------|---------|---------|---------|---------|----------|----------|

| 82         | 00      | 00      | 00      | 00      | 00      | 02       | 00       |

| Data trans | action: |         |         |         |         |          |          |

| DATA0      | DATA1   | DATA2   | DATA3   | DATA4   | DATA5   | DATA6    | DATA7    |

| Value      | Value   | _       | _       | _       |         | _        |          |

### 5.25 Get Status EP1

#### Setup transaction:

| BmReq        | bReq   | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|--------------|--------|---------|---------|---------|---------|----------|----------|

| 82           | 00     | 00      | 00      | 81      | 00      | 02       | 00       |

| Data transac | ction: |         |         |         |         |          |          |

| DATA0        | DATA1  | DATA2   | DATA3   | DATA4   | DATA5   | DATA6    | DATA7    |

| Value        | value  | -       | -       | -       | -       | -        | -        |

### 5.26 Get Status EP2

#### Setup transaction:

| BmReq | bReq | w ValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------|------|----------|---------|---------|---------|----------|----------|

| 82    | 00   | 00       | 00      | 02      | 00      | 02       | 00       |

| _     |      |          |         |         |         |          |          |

#### Data transaction:

| DATA0 | DATA1 | DATA2 | DATA3 | DATA4 | DATA5 | DATA6 | DATA7 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Value | value | -     | -     | -     | -     | -     | -     |

### 5.27 Get Status EP3

| Setup transaction: |                   |         |         |         |         |          |          |

|--------------------|-------------------|---------|---------|---------|---------|----------|----------|

| BmReq              | bReq              | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

| 82                 | 00                | 00      | 00      | 83      | 00      | 02       | 00       |

| Data trans         | Data transaction: |         |         |         |         |          |          |

| DATA0              | DATA1             | DATA2   | DATA3   | DATA4   | DATA5   | DATA6    | DATA7    |

| Value              | Value             | _       | _       | _       | _       | _        | _        |

### 5.28 Get Status Interface 0

#### Setup transaction:

| BmReq             | bReq  | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------------------|-------|---------|---------|---------|---------|----------|----------|

| 81                | 00    | 00      | 00      | 00      | 00      | 02       | 00       |

| Data transaction: |       |         |         |         |         |          |          |

| DATA0             | DATA1 | DATA2   | DATA3   | DATA4   | DATA5   | DATA6    | DATA7    |

| Value             | value | _       | -       | -       | -       | _        | -        |

# 5.29 Get Interface 0

#### Setup transaction:

| BmReq             | bReq  | wValueL | wValueH | wIndexL | wIndexH | wLengthL | wLengthH |

|-------------------|-------|---------|---------|---------|---------|----------|----------|

| 81                | 0A    | 00      | 00      | 00      | 00      | 01       | 00       |

| Data transaction: |       |         |         |         |         |          |          |

| DATA0             | DATA1 | DATA2   | DATA3   | DATA4   | DATA5   | DATA6    | DATA7    |

| value             | -     | -       | -       | -       | -       | -        | -        |

# 6. Memory Allocation

\$0000H~\$011FH----- Reserved

\$0120H~\$01FFH------ RTL8150L(M) REGISTER

\$1200H~\$127FH-----Serial EEPROM(9346)

| Offset      | Type | Pin No    | Description                                     |

|-------------|------|-----------|-------------------------------------------------|

| 0120h-0125h | R/W* | IDR0-5    | Ethernet Address ,load from 93C46               |

| 0126h-012Dh | R/W  | MAR0-7    | Multicast register                              |

| 012Eh       | R/W  | CR        | Command Register                                |

| 012Fh       | R/W  | TCR       | Transmit configuration register                 |

| 0130-0131h  | R/W  | RCR       | Receive configuration register                  |

| 0132h       | R/W  | TSR       | Transmit status register                        |

| 0133h       | R/W  | RSR       | Receive status register                         |

| 0134h       | R/W  | Reserved  | -                                               |

| 0135h       | R/W* | CON0      | Configuration register0                         |

| 0136h       | R/W* | CON1      | Configuration register1                         |

| 0137h       | R/W  | MSR       | Medium status                                   |

| 0138h       | R/W  | PHYADD    | MII PHY address select                          |

| 0139-013Ah  | R/W  | PHYDAT    | MII PHY data                                    |

| 013Bh       | R/W  | PHYCNT    | MII PHY control                                 |

| 013Ch       | R/W  | Reserved  |                                                 |

| 013Dh       | R/W* | GPPC      | General purpose pin control                     |

| 013Eh       | R/W  | WAKECNT   | Wake up event control                           |

| 0140h-0141h | R/W* | BMCR      | Basic mode control register                     |

| 0142h-0143h | R    | BMSR      | Basic mode status register                      |

| 0144h-0145h | R/W* | ANAR      | Auto-negotiation advertisement register         |

| 0146h-0147h | R/W  | ANLP      | Auto-negotiation link partner ability register  |

| 0148h-0149h | R/W  | AER       | Auto-negotiation expansion register             |

| 014Ah-014Bh | R/W  | NWAYT     | Nway test register                              |

| 014Ch-014Dh | R/W  | CSCR      | CS confiiguration register                      |

| 014Eh-014Fh | R/W  | CRC0      | Power Management CRC register for wakeup frame0 |

| 0150h-0151h | R/W  | CRC1      | Power Management CRC register for wakeup frame1 |

| 0152h-0153h | R/W  | CRC2      | Power Management CRC register for wakeup frame2 |

| 0154h-0155h | R/W  | CRC3      | Power Management CRC register for wakeup frame3 |

| 0156h-0157h | R/W  | CRC4      | Power Management CRC register for wakeup frame4 |

| 0158h-015Fh | R/W  | BYEMASK0  | Power Management wakeup frame0(64bit) bytemask  |

| 0160h-0167h | R/W  | BYEMASK 1 | Power Management wakeup frame1(64bit) bytemask  |

| 0168h-016Fh | R/W  | BYEMASK 2 | Power Management wakeup frame2(64bit) bytemask  |

| 0170h-0177h | R/W  | BYEMASK 3 | Power Management wakeup frame3(64bit) bytemask  |

| 0178h-017Fh | R/W  | BYEMASK 4 | Power Management wakeup frame4(64bit) bytemask  |

| 0180h-0183h | R/W  | PHY1      | PHY parameter 1                                 |

| 0184h       | R/W  | PHY2      | PHY parameter 2                                 |

| 0186h-0189h | R/W  | TW1       | Twister parameter 1                             |

| 018Ah-01ff  |      | Reserved  |                                                 |

$<sup>\</sup>ast$ : denotes auto-loaded from 93C46 during chip initialization.

# 7. Register Descriptions

# 7.1 Command Register (Offset 012Eh, R/W)

| Bit | Symbol   | Description                                                           | Default/<br>Attribute |

|-----|----------|-----------------------------------------------------------------------|-----------------------|

| 7-6 | -        | Reserved                                                              | =                     |

| 5   | WEPROM   | 1:EEPROM write enable                                                 | 0,R/W                 |

|     |          | 0: disable                                                            |                       |

|     |          | The EEPROM map from 0x1200 to 127fh. Write 0x1200 equal to            |                       |

|     |          | program EEPROM offset 0x00. Write to EEPROM must use WORD             |                       |

|     |          | mode access at a time. The read EEPROM have not limit.                |                       |

| 4   | SOFT_RST | Reset: Setting to 1 forces the RTL8150L(M) to a software reset state  | 0,R/W                 |

|     |          | which disables the transmitter and receiver, reinitializes the FIFOs, |                       |

|     |          | resets the system buffer pointer to the initial value, Rx buffer is   |                       |

|     |          | empty). The values of IDR0-5 and MAR0-7 will have no changes.         |                       |

|     |          | This bit is 1 during the reset operation, and is cleared to 0 by the  |                       |

|     |          | RTL8150L(M) when the reset operation is complete.                     |                       |

| 3   | RE       | Ethernet 10/100M receive enable                                       | 0,R/W                 |

| 2   | TE       | Ethernet 10/100M transmit enable                                      | 0,R/W                 |

| 1   | EP3CLREN | 1: Enable clearing the performance counter of EP3 after EP3 access.   | 0,R/W                 |

|     |          | 0: Disable                                                            |                       |

| 0   | AUTOLOAD | 1: Auto-load the contents of 93c46 into RTL8150L(M)'s registers.      | 0,R/W                 |

|     |          | This bit is self clearing after load complete.                        |                       |

# 7.2 Transmit Configuration Register (Offset 012Fh, R/W)

| Bit  | Symbol   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Default/  |

|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|      |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Attribute |

| 7-6  | TXRR1, 0 | Tx Retry Count: These 2 bits are used to specify additional transmission retries in multiple of 16(IEEE 802.3 CSMA/CD retry count). If the TXRR is set to 0, the transmitter will re-transmit 16 times before aborting due to excessive collisions if the TXRR is set to a value greater than 0, the transmitter will re-transmit a number of times equals to the following formula before aborting:  Total retries = 16 + (TXRR * 16)  The ECOL bit in the TSR register will be set if transmit abort due to excessive collision. | 0,R/W     |

| 5    | Reserve  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -         |

| 4,3  | IFG1, 0  | Interframe Gap Time: This field allows the user to adjust the interframe gap time below the standard: 9.6 us for 10Mbps, 960 ns for 100Mbps. The time can be programmed from 9.6 us to .8.4 us (10Mbps) and 960ns to 840ns (100Mbps). The formula for the inter frame gap is: $10 \text{ Mbps} \qquad \qquad 8.4 \text{us} + 0.4 \text{(IFG(1:0))} \text{ us} \\ 100 \text{ Mbps} \qquad \qquad 840 \text{ns} + 40 \text{(IFG(1:0))} \text{ ns}$                                                                                   | 0,R/W     |

| 2, 1 | Reserved |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -         |

| 0    | NOCRC    | 1: There's no CRC appended at the end of a packet.  0: There's CRC appended at the end of a packet.                                                                                                                                                                                                                                                                                                                                                                                                                                | 0,R/W     |

# 7.3 Receive Configuration Register (Offset 0130h-0131h,

### **R/W**)

| Bit  | Symbol | Description                                                                                    | Default/<br>Attribute |

|------|--------|------------------------------------------------------------------------------------------------|-----------------------|

| 15-8 | -      | Reserved                                                                                       | -                     |

| 7    | TAIL   | 0: CRC field forward to HOST                                                                   | 0,R/W                 |

|      |        | 1: Rx Header forward to HOST. The first two bytes of CRC field are replaced by receive header. |                       |

| 6    | AER    | 1:Accept CRC error packet                                                                      | 0,R/W                 |

| 5    | AR     | 1: Accept RUNT packet (<64 bytes)                                                              | 0,R/W                 |

| 4    | AM     | 1: Accept all multicast packets enumerated in the driver's multicast                           | 0,R/W                 |

|      |        | address list.                                                                                  |                       |

|      |        | 0: Disabled.                                                                                   |                       |

| 3    | AB     | 1: Accept broadcast packets                                                                    | 0,R/W                 |

|      |        | 0: Reject broadcast packets.                                                                   |                       |

| 2    | AD     | 1: Packets received containing a destination address that match the                            | 0,R/W                 |

|      |        | MAC address of the networking device are accepted.                                             |                       |

|      |        | 0: Disabled.                                                                                   |                       |

| 1    | AAM    | 1: Accept all multicast frames received by the networking device,                              | 0,R/W                 |

|      |        | including the ones enumerated in the device's multicast address list,                          |                       |

|      |        | 0: Disable.                                                                                    |                       |

| 0    | AAP    | 1: Accept all physical frames                                                                  | 0,R/W                 |

|      |        | 0: Disable.                                                                                    |                       |

# 7.4Transmit Status Register(Offset 0132h)

| Bit | Symbol       | Description                       | Default/<br>Attribute |

|-----|--------------|-----------------------------------|-----------------------|

| 7-6 | -            | Reserved                          | -                     |

| 5   | ECOL         | 1: Excessive collision indication | R                     |

| 4   | LCOL         | 1: Late collision indication      | R                     |

| 3   | LOSS_CRS     | 1: Loss of carrier indication     | R                     |

| 2   | JBR          | 1: Jaber time out indication      | R                     |

| 1   | TX_BUF_EMPTY | 1: Tx buffer empty indication     | R                     |

| 0   | TX_BUF_FULL  | 1: Tx buffer full indication      | R                     |

Note: TSR register will be cleared to the default value after read or EP3 access.

### 7.5 Receive Status Register(Offset 0133h)

| Bit | Symbol      | Description               | Default/<br>Attribute |

|-----|-------------|---------------------------|-----------------------|

| 7   | WEVENT      | Wake Up Event indication: | R                     |

|     |             | 1: Wakeup event occurs    |                       |

| 6   | RX_BUF_FULL | Rx Buffer Full indication | R                     |

### RTL8150(M)

| 5 | LKCHG | Link Change indication                                              | R |

|---|-------|---------------------------------------------------------------------|---|

| 4 | RUNT  | Runt Packet indication                                              | R |

|   |       | 1: The received packet length is smaller than 64 bytes.             |   |

| 3 | LONG  | Long Packet indication                                              | R |

|   |       | 1: The size of the received packet exceeds 4k bytes.                |   |

| 2 | CRC   | CRC Error indication.                                               | R |

|   |       | 1: The received packet is checked with CRC error.                   |   |

| 1 | FAE   | Frame Alignment Error:                                              | R |

|   |       | 1: Indicates that a frame alignment error occurred on this received |   |

|   |       | packet.                                                             |   |

| 0 | ROK   | Receive OK indication.                                              | R |

|   |       | 1: Indicate that a packet is received without error.                |   |

Note: RSR register will be cleared to the default value after read or EP3 access.

# 7.6 Configuration Register 0(Offset 0135h, R/W)

| Bit | Symbol  | Description                                                                                                                                                                                                                                                                                                                                                                 | Default/<br>Attribute |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 7   | SUSLED  | 0: LED pins are driven high to turn off LED during suspend.                                                                                                                                                                                                                                                                                                                 | 0,R/W                 |

| 6   | PARM_EN | Parameter Enable: (These parameters are used in 100Mbps mode.)  1: PHY1_PARM, PHY2_PARM, TW_PARM can be modified through access to register 0180H~0189H.  0: Disable  Note: Each time 93C46 auto-load process is executed, the PHY1_PARM, PHY2_PARM, TW_PARM will be re-loaded the default value from 93C46.                                                                | 0,R/W                 |

| 4-5 | -       | Reserved                                                                                                                                                                                                                                                                                                                                                                    | -                     |

| 3   | LDPS    | Link Down Power Saving mode:  1: Disable.  0: Enable. When the ethernet cable is disconnected (Link Down), part of analog circuit will be powered down in order to save power. The other part of analog circuits relating to SD signal monitoring and 100M signal receiving are not powered down in case the cable is re-connected and link should be re-established again. | 0,R/W                 |

| 2   | MSEL    | Medium Select When write:  1:MII mode (disable internal PHY) 0:Auto-detect. The UTP mode will be the default. The RTL8150L(M) is switched to MII mode if the internal PHY is not link OK. When read  1:MII mode: The MAC MII is connected to the MII interface of the external PHY.  0:UTP mode: The MAC MII is connected to the internal PHY.                              | 0,R/W                 |

| 1-0 | LEDS1-0 | Refer to LED PIN definition. The default value is auto-loaded from 93C46.                                                                                                                                                                                                                                                                                                   | 0,R/W                 |

# 7.7 Configuration Register 1(Offset 0136h, R/W)

| Bit Symbol Description Default/ |

|---------------------------------|

|---------------------------------|

|     |         |                                                                                                                                                                                                                                                                                                                                | Attribute |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 7   | -       | Reserved.                                                                                                                                                                                                                                                                                                                      | -         |

| 6   | BWF     | Broadcast Wakeup Frame Function:  1: Enable Broadcast Wakeup Frame                                                                                                                                                                                                                                                             | 0,R/W     |

|     |         | If set_feature command with Feature Selector =DEVICE_REMOTE_WAKEUP is received from USB host and BWF=1, RTL8150L(M) will signal wakeup to the host when correctly receiving a packet with DID=FF FF FF FF FF (Broadcast packet),.  0: Disable.                                                                                 |           |

| 5   | MWF     | Multicast Wakeup Frame Function:  1: Enable Multicast Wakeup Frame  If set_feature command with Feature Selector  =DEVICE_REMOTE_WAKEUP is received from USB host and  MWF=1, RTL8150L(M) will signal wakeup to the host when  correctly receiving multicast packets (packets that survive the  multicast hash),.  0: Disable. | 0,R/W     |

| 4   | UWF     | Unicast Wakeup Frame Function:  1: Enable Unicast Wakeup Frame f set_feature command with Feature Selector =DEVICE_REMOTE_WAKEUP is received from USB host and UWF=1, RTL8150L(M) will signal wakeup to the host when correctly receiving a packet with DID=IDR0~5.  0: Disable.                                               | 0,R/W     |

| 2-3 | =       | Reserved                                                                                                                                                                                                                                                                                                                       | -         |

| 1   | LONGWF1 | 1: The Bytemask3 and Bytemask4 are cascaded to form a 128 byte long Bytemask for long wakeup frame 1, and long wakeup frame 1 use CRC3 as CRC check. When LONGWF1=1, wakeup frame 3 and wakeup frame 4 are disable.  0: Disable LOGNWF1.                                                                                       | 0,R/W     |

| 0   | LONGWF0 | 1: The Bytemask1 and Bytemask2 are cascaded to form a 128 byte long Bytemask for long wakeup frame 0, and long wakeup frame 0 use CRC1 as CRC check. When LONGWF0=1, wakeup frame 1 and wakeup frame 2 are disabled.  0: Disable LOGNWF0.                                                                                      | 0,R/W     |

# 7.8Media Status Register (Offset 0137h, R/W)

| Bit | Symbol            |                  | Description                                   |                                       | Default/<br>Attribute |

|-----|-------------------|------------------|-----------------------------------------------|---------------------------------------|-----------------------|

| 7   | TXFCE/<br>LdTXFCE |                  | le: The flow control<br>'s default value come | is valid in full-duplex s from 93C46. | R/W                   |

|     |                   | RTL8150L         | Remote                                        | TXFCE/LdTXFCE                         |                       |

|     |                   | ANE = 1          | NWAY FLY mode                                 | R/O                                   |                       |

|     |                   | ANE = 1          | NWAY mode only                                | R/W                                   |                       |

|     |                   | ANE = 1          | No NWAY                                       | R/W                                   |                       |

|     |                   | ANE = 0 &        | =                                             | R/W                                   |                       |

|     |                   | full-duplex mode |                                               |                                       |                       |

|     |                   | ANE = 0 &        | =                                             | Invalid                               |                       |

|     |                   | half-duplex      |                                               |                                       |                       |

|     |                   | mode             |                                               |                                       |                       |

|   |           | NWAY FLY mode: NWAY with flow control capability NWAY mode only: NWAY without flow control capability                                                           |     |

|---|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6 | RXFCE     | RX Flow control Enable: The flow control is enabled in full-duplex mode only. The default value comes from 93C46.                                               | R/W |

| 5 | Reserved  | -                                                                                                                                                               | -   |

| 4 | Duplex    | Indicate that the current link is full-duplex     Indicate that the current link is half-duplex                                                                 | R   |

| 3 | SPEED_100 | Indicate that the current link is in 100Mbps mode.     Indicate that the current link is in 10Mbps mode.                                                        | R   |

| 2 | LINK      | Link status. 1: Link OK. 0: Link Fail.                                                                                                                          | R   |

| 1 | TXPF      | Indicate that RTL8150L(M) sends pause packet.     Indicate that RTL8150L(M) has sent timer done packet to release remote station from pause Tx state.           | R   |

| 0 | RXPF      | Indicate that RTL8150L(M) is in Backoff state because a pause packet from remote station has been receipt.     Indicate that RTL8150L(M) is not in pause state. | R   |

# 7.9 MII PHY Address(Offset 0138h, R/W)

| Bit | Symbol   | Description            | Default/<br>Attribute |

|-----|----------|------------------------|-----------------------|

| 7-5 | Reserved |                        | -                     |

| 4-0 | PHYADD   | MII PHY Address select | R/W                   |

# 7.10 MII PHY DATA(Offset 0139h-013Ah, R/W)

| Bit  | Symbol | Description                                                      | Default/<br>Attribute |

|------|--------|------------------------------------------------------------------|-----------------------|

| 15-0 | MIIDAT | Data read from MII PHY or data that is to be written to MII PHY. | R/W                   |

# 7.11 MII PHY Access Control(Offset 013Bh, R/W)

| Bit | Symbol   | Description                                                                                                                                                     | Default/<br>Attribute |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 7   | Reserved |                                                                                                                                                                 | -                     |

| 6   | PHYOWN   | Own bit: RTL8150L(M) will initiate a MII management data transaction if this bit is set 1 by software. After transaction, this bit is auto cleared by RTL8150L. | 0,R/W                 |

| 5   | RWCR     | MII management data R/W control 1:write, 0: read                                                                                                                | R/W                   |

| 4-0 | PHYOFF   | PHY register offset                                                                                                                                             | R/W                   |

### 7.12 General Purpose Register(Offset 013Dh, R/W)

| Bit | Symbol    | Description/Usage                                                   | Default/<br>Attribute |

|-----|-----------|---------------------------------------------------------------------|-----------------------|

| 7-5 | GEPREG1~3 | Reserved                                                            | -                     |

| 4   | GEPREG0   | General purpose bit                                                 | RO                    |

|     |           | 1: Supports external Home PNA PHY                                   |                       |

| 3   | GEP1DAT   | If GEP1RW is set 1, the GEP1 pin will reflect the value of GEP1DAT, | R/W                   |

|     |           | else GEP1DAT will reflect the value of GEP1 pin.                    |                       |

| 2   | GEP1RW    | General purpose pin control bit:                                    | R/W                   |

|     |           | 0: The corresponding GEP1 pin is considered input                   |                       |

|     |           | 1: The corresponding GEP1 pin is considered output                  |                       |

| 1   | GEP0DAT   | If GEP0RW is set 1, the GEP0 pin will reflect the value of GEP0DAT, | R/W                   |

|     |           | else GEP0DAT will reflect the value of GEP0 pin.                    |                       |

| 0   | GEP0RW    | General purpose pin control bit:                                    | R/W                   |

|     |           | 0: The corresponding GEP0 pin is considered input                   |                       |

|     |           | 1: The corresponding GEP0 pin is considered output                  |                       |

If GEPRW=0, READ only

### 7.13 Wake Up Event Control(Offset 013E, R/W)

| Bit | Symbol   | Description/Usage           | Default/<br>Attribute |

|-----|----------|-----------------------------|-----------------------|

| 7   | Reserved |                             | -                     |

| 6   | LKWEN    | Link change wake-up enable  | 0, R/W                |

| 5   | MAGWEN   | Magic Packet wake-up enable | 0, R/W                |

| 4   | WUF4EN   | Wake up frame 4 enable      | 0, R/W                |

| 3   | WUF3EN   | Wake up frame 3 enable      | 0, R/W                |

| 2   | WUF2EN   | Wake up frame 2 enable      | 0, R/W                |

| 1   | WUF1EN   | Wake up frame 1 enable      | 0, R/W                |

| 0   | WUF0EN   | Wake up frame 0 enable      | 0, R/W                |

Note: RTL8150L(M) will signal wakeup to the host only when the following two conditions are met:

- 1. The host has send set\_feature\_device command.

- 2. One of the wakeup frame function has been enabled and triggered.

# 7.14 Basic Mode Control Register (Offset 0140h-0141h, R/W)

| Bit | Name     | Description/Usage                                                                                                            | Default/<br>Attribute |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 15  | Reset    | This bit, which is self clearing, will reset the control and status registers of PHY into the default states if it is set 1. | 0, RW                 |

| 14  | Reserved | -                                                                                                                            | -                     |

| 13  | Spd_Set  | Speed select.  1 = 100Mbps;  0 = 10Mbps.  Note: The initial value of this bit comes from 93C46                               | RW                    |

|       |                  | I                                                                        |       |

|-------|------------------|--------------------------------------------------------------------------|-------|

| 12    | Auto Negotiation | This bit enables/disables the NWay auto-negotiation function.            | 0, RW |

|       | Enable           | 1 = Enable auto-negotiation. If this bit is set, bit 8 and bit13 will be |       |

|       | (ANE)            | ignored, and the values of bit8 and bit 13 indicate the result of auto   |       |

|       |                  | negotiation process.                                                     |       |

|       |                  | 0 = Disable auto-negotiation.                                            |       |

|       |                  | Note: The initial value of this bit comes from 93C46                     |       |

| 11-10 | Reserved         | -                                                                        | -     |

| 9     | Restart Auto     | This bit allows the NWay auto-negotiation function to be re-initiated.   | 0, RW |

|       | Negotiation      | 1 = Re-start auto-negotiation                                            |       |

|       |                  | 0 = Normal operation.                                                    |       |

| 8     | Duplex Mode      | This bit sets the duplex mode.                                           | 0, RW |

|       |                  | 1 = full-duplex                                                          |       |

|       |                  | 0 = normal operation.                                                    |       |

|       |                  | Note: This bit's initial value comes from 93C46                          |       |

| 7-0   | Reserved         | -                                                                        | -     |

# 7.15 Basic Mode Status Register (Offset 0142h-0143h, R)

| Bit  | Name             | Description/Usage                                         | Default/<br>Attribute |

|------|------------------|-----------------------------------------------------------|-----------------------|

| 15   | 100Base-T4       | 100Base-T4 Capable:                                       | 0, RO                 |

|      | 100Dasc-14       | 0 = Device not able to perform 100Base-T4 mode            |                       |

| 14   | 100Base_TX_ FD   | 100Base-TX Full Duplex Capable:                           | 1, RO                 |

|      | 100base_1A_FD    | 1 = Device able to perform 100Base-TX in full duplex mode |                       |

| 13   | 100D TV IID      | 100Base-TX Half Duplex Capable:                           | 1, RO                 |

|      | 100Base_TX_HD    | 1 = Device able to perform 100Base-TX in half duplex mode |                       |

| 12   | 10D T. ED        | 10Base-T Full Duplex Capable:                             | 1, RO                 |

|      | 10Base_T_FD      | 1 = Device able to perform 10Base-T in full duplex mode   |                       |

| 11   | 10 D T IID       | 10Base-T Half Duplex Capable:                             | 1, RO                 |

|      | 10_Base_T_HD     | 1 = Device able to perform 10Base-T in half duplex mode   |                       |

| 10-6 | -                | Reserved                                                  | -                     |

| 5    | Auto Negotiation | 1 = Auto-negotiation process completed;                   | 0, RO                 |

|      | Complete         | 0 = Auto-negotiation process not completed.               |                       |

| 4    | D 1.             | 1 = Remote fault condition detected (clear on read);      | 0, RO                 |

|      | Remote Fault     | 0 = No remote fault condition detected.                   |                       |

| 3    | Auto Negotiation | 1 = Device is able to perform Auto-Negotiation.           | 1, RO                 |

|      | ability          | 0 = Device not able to perform Auto-Negotiation.          |                       |

| 2-1  |                  | Reserved                                                  |                       |

| 0    | Extended         | 1 = Extended register capabilities;                       | 1, RO                 |

|      | Capability       | 0 = Basic register set capabilities.                      |                       |

# 7.16 Auto-negotiation Advertisement Register (Offset

# 0144h-0145h, R/W)

| Bit | Name | Description/Usage                                                                   | Default/<br>Attribute |

|-----|------|-------------------------------------------------------------------------------------|-----------------------|

| 15  | NP   | Next Page capability.  0 = Advertise that NP capability not supported by local mode | 0, RO                 |

|       |          | 1 = Advertise NP exchange capability and desire to transfer next  |                    |

|-------|----------|-------------------------------------------------------------------|--------------------|

|       |          | page.                                                             |                    |

| 14    | ACK      | 1 = Acknowledge reception of link partner's capability data word. | 0, RO              |

| 13    | RF       | 1 = Advertise remote fault detection capability;                  | 0, RW              |

|       |          | 0 = Do not advertise remote fault detection capability.           |                    |

| 12-11 | -        | Reserved                                                          | -                  |

| 10    | PAUSE    | 1 = Advertise flow control supported by local node.               | The default        |

|       |          | 0 = Advertise flow control not supported by local mode.           | value comes        |

|       |          |                                                                   | from<br>EEPROM, RO |

| 9     | T4       | 1 = Advertise 100Base-T4 supported by local node;                 | 0, RO              |

|       |          | 0 = Advertise 100Base-T4 not supported by local node.             |                    |

| 8     | TXFD     | 1 = Advertise 100Base-TX full duplex supported by local node;     | 1, RW              |

|       |          | 0 = Advertise 100Base-TX full duplex not supported by local node. |                    |

| 7     | TX       | 1 = Advertise 100Base-TX supported by local node;                 | 1, RW              |

|       |          | 0 = Advertise 100Base-TX not supported by local node.             |                    |

| 6     | 10FD     | 1 = Advertise 10Base-T full duplex supported by local node;       | 1, RW              |

|       |          | 0 = Advertise 10Base-T full duplex not supported by local node.   |                    |

| 5     | 10       | 1 = Advertise 10Base-T supported by local node;                   | 1, RW              |

|       |          | 0 = Advertise 10Base-T not supported by local node.               |                    |

| 4-0   | Selector | Binary encoded selector supported by this node. Currently only    | <00001>,           |

|       |          | CSMA/ CD <00001> is specified. No other protocols are supported.  | RW                 |

# 7.17 Auto-Negotiation Link Partner Ability Register

# (Offset 0146h-0147h, R)

| Bit   | Name     | Description/Usage                                                    | Default/<br>Attribute |  |  |  |

|-------|----------|----------------------------------------------------------------------|-----------------------|--|--|--|

| 15    | NP       | NP Next Page Indication:                                             |                       |  |  |  |

|       |          | 0 = Link Partner does not desire Next Page Transfer                  |                       |  |  |  |

|       |          | 1 = Link Partner desires Next Page Transfer.                         |                       |  |  |  |

| 14    | ACK      | 1 = link partner acknowledges reception of the capability data word. | 0, RO                 |  |  |  |

|       |          | 0 = Not acknowledged                                                 |                       |  |  |  |

|       |          | The device's Auto-Negotiation state machine will automatically       |                       |  |  |  |

|       |          | control this bit based on the incoming FLP bursts.                   |                       |  |  |  |

| 13    | RF       | Remote Fault:                                                        | 0, RO                 |  |  |  |

|       |          | 1 = Remote Fault indicated by Link Partner                           |                       |  |  |  |

|       |          | 0 = No Remote Fault indicated by Link Partner.                       |                       |  |  |  |

| 12-11 | Reserved | -                                                                    | -                     |  |  |  |

| 10    | Pause    | 1 = Flow control is supported by link partner,                       | 0, RO                 |  |  |  |

|       |          | 0 = Flow control is not supported by link partner.                   |                       |  |  |  |

| 9     | T4       | 100BASE-T4 Support:                                                  | 0, RO                 |  |  |  |

|       |          | 1 = 100Base-T4 is supported by the link partner;                     |                       |  |  |  |

|       |          | 0 = 100Base-T4 not supported by the link partner.                    |                       |  |  |  |

| 8     | TXFD     | 100BASE-TX Full Duplex Support:                                      | 0, RO                 |  |  |  |

|       |          | 1 = 100Base-TX full duplex is supported by the link partner;         |                       |  |  |  |

|       |          | 0 = 100Base-TX full duplex not supported by the link partner.        |                       |  |  |  |

| 7     | TX       | 100BASE-TX Support:                                                  | 0, RO                 |  |  |  |

|       |          | 1 = 100Base-TX is supported by the link partner;                     |                       |  |  |  |

|       |          | 0 = 100Base-TX not supported by the link partner.                    |                       |  |  |  |

| 6     | 10FD     | 10BASE-T Full Duplex Support:                                        | 0, RO                 |  |  |  |

|       |          | 1 = 10Base-T full duplex is supported by the link partner;           |                       |  |  |  |

#### RTL8150(M)

|     |          | 0 = 10Base-T full duplex not supported by the link partner. |       |

|-----|----------|-------------------------------------------------------------|-------|

| 5   | 10       | 10BASE-T Support:                                           | 0, RO |

|     |          | 1 = 10Base-T is supported by the link partner;              |       |

|     |          | 0 = 10Base-T not supported by the link partner.             |       |

| 4-0 | Selector | Protocol Selection Bits:                                    | 0, RO |

|     |          | Link Partner's binary encoded protocol selector.            |       |

# 7.18 Auto-negotiation Expansion Register (Offset

### 0148h-0149h, R)

This register contains additional status for NWay auto-negotiation.

| Bit  | Name       | Description/Usage                                                                                                                                                                                   | Default/<br>Attribute |

|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 15-5 | -          | Reserved, This bit is always set to 0.                                                                                                                                                              | -                     |

| 4    | MLF        | Status indicating if a multiple link fault has occurred.<br>1 = fault occurred; 0 = no fault occurred.                                                                                              | 0, RO                 |

| 3    | LP_NP_ABLE | Status indicating if the link partner supports Next Page negotiation. 1 = supported; 0 = not supported.                                                                                             | 0, RO                 |

| 2    | NP_ABLE    | This bit indicates if the local node is able to send additional Next Pages.                                                                                                                         | 0, RO                 |

| 1    | PAGE_RX    | This bit is set when a new Link Code Word Page has been received. The bit is automatically cleared when the auto-negotiation link partner's ability register (register 146h) is read by management. | 0, RO                 |

| 0    | LP_NW_ABLE | 1 = link partner supports NWay auto-negotiation.                                                                                                                                                    | 0, RO                 |

# 7.19 NWay Test Register (Offset 014Ah-014Bh, R/W)

| Bit  | Name    | Description/Usage                                       | Default/<br>Attribute |