# System Reset (with built-in watchdog timer)

# Monolithic IC MM1145

### **Outline**

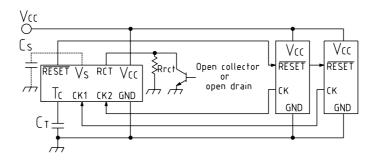

This IC has a built-in watchdog timer, with 2 channels for a clock monitoring function that monitors the microcomputer and outputs an intermittent reset signal if the microcomputer runs wild. Also, it has a power supply voltage monitoring function (system reset function) which generates a reset signal if power supply voltage is momentarily interrupted or drops, and performs power ON reset during normal power supply recovery and when power is turned on.

#### **Features**

- 1. Built-in edge trigger input watchdog timer

- 2. 2 clock pulse monitoring

- 3. Power ON reset time (Tpr) and watchdog timer monitoring time (Two) can be set individually with external elements (R, C)

4. Excellent watchdog timer monitoring time (Two) precision A type: ±20%

B type: ±30%

5. Watchdog function stop pin allows use as system reset IC

6. Accurate power supply voltage drop detection 4.2V±3.5%

7. Detection voltage has hysteresis 100mV typ. ±0.14%/°C

8. Low reset minimum voltage

9. Low current consumption 150μA typ.

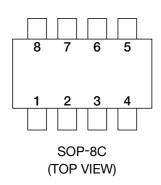

### **Package**

SOP-8C (MM1145AF, MM1145BF)

### **Applications**

Voltage detection for CPUs, microcomputers, etc. and clock pulse monitoring

### **Series Table**

| Model   | VsL | T <sub>PR</sub> | Two   | Twr  |

|---------|-----|-----------------|-------|------|

| MM1145A | 4.2 | 100ms           | 50ms  | 10ms |

| MM1145B | 4.2 | 40ms            | 110ms | 10ms |

\*C $\tau$ =0.02 $\mu$ F, RC $\tau$ =1M $\Omega$

VsL: Reset detection voltage

TPR: Reset hold time during Vcc rise

Two: Watchdog timer monitoring time

Twn: Reset time

## Pin Assignment

| 1 | TC    |

|---|-------|

| 2 | CK1   |

| 3 | CK2   |

| 4 | GND   |

| 5 | Vcc   |

| 6 | RCT   |

| 7 | Vs    |

| 8 | RESET |

## Pin Description

| Pin No. | Pin name | Function                                                                |

|---------|----------|-------------------------------------------------------------------------|

| 1       | TC       | Twd, Twr, Tpr time setting pins. Time determined by external capacitor. |

| 2       | CK1      | Clock input pin 1 Clock input from logic system                         |

| 3       | CK2      | Clock input pin 2 Clock input from logic system                         |

| 4       | GND      | GND pin                                                                 |

| 5       | Vcc      | Power supply pin Detection voltage 4.2V                                 |

|         |          | Watchdog timer stop pin and Two adjustment pin                          |

| 6       | RCT      | Operation modes : Operation $\rightarrow$ Vcc, Stop $\rightarrow$ GND   |

|         |          | Two time determined by external resistor RRCT and CT                    |

| 7       | Vs       | Detection voltage adjustment pin                                        |

| 8       | RESET    | Reset output pin (low output)                                           |

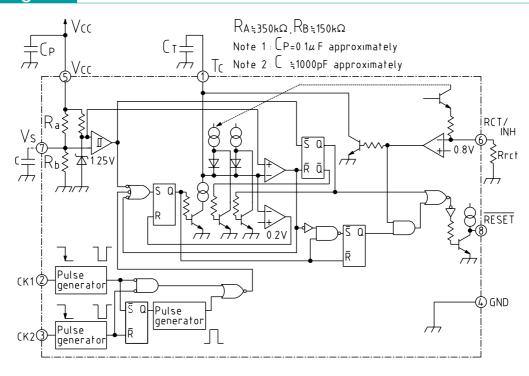

## Block Diagram

## Absolute Maximum Ratings

| Item                         | Symbol   | Rating                                 | Units          |

|------------------------------|----------|----------------------------------------|----------------|

| Power supply voltage         | Vcc max. | -0.3~+7.5                              | V              |

| CK pin input voltage         | Vck      | -0.3~Vcc+0.3 (≤+7.5)                   | V              |

| VS pin input voltage         | Vvs      | $-0.3 \sim V_{CC} + 0.3 \ ( \le +7.5)$ | V              |

| Voltage applied to RCT pin   | Vrct     | -0.3~Vcc+0.3 (≤+7.5)                   | V              |

| Voltage applied to RESET pin | Voh      | -0.3~Vcc+0.3 (≤+7.5)                   | V              |

| Allowable loss               | Pd       | 300                                    | mW             |

| Storage temperature          | Tstg     | <b>−</b> 40~+125                       | $^{\circ}\! C$ |

# **Recommended Operating Conditions**

| Item                                     | Symbol   | Rating     | Units |

|------------------------------------------|----------|------------|-------|

| Power supply voltage                     | Vcc      | +2.2~+7.0  | V     |

| RESET sync current                       | Iol      | 0~4.0      | mA    |

| Clock monitoring time setting            | Twd      | 1.95~10000 | ms    |

| Power supply voltage rise and fall times | tfv, trv | <300       | μs    |

| Clock rise and fall times                | trc, trc | <100       | μs    |

| C⊤ pin capacitance                       | Ст       | 0.002~2    | μF    |

| RCT pin resistance                       | Rrct     | 0.39~2     | MΩ    |

| Operating temperature                    | Тор      | -25~+75    | °C    |

# Electrical Characteristics (DC) (Except where noted otherwise, Ta=25°C, Vcc=5.0V)

| Item                           |                      | Symbol          | Measurement conditions          | Min.  | Тур.  | Max.  | Units    |  |

|--------------------------------|----------------------|-----------------|---------------------------------|-------|-------|-------|----------|--|

| Consumption current            |                      | Icc             | During watchdog timer operation |       | 150   | 180   | μΑ       |  |

| Detection voltage              |                      | Vsl             | Vs=OPEN, Vcc                    | 4.05  | 4.20  | 4.35  | V        |  |

|                                |                      | VsH             | Vs=OPEN, Vcc                    | 4.15  | 4.30  | 4.45  | V        |  |

| Detection                      | n voltage            | VS<br>⊿T        | Vsh-Vsl, Vcc                    |       | ±0.01 |       | %/°C     |  |

| temperature                    | e coefficient        |                 | VSH-VSL, VCC                    |       | ±0.01 |       | /0/ C    |  |

| Hysteresi                      | is voltage           | VHYS            |                                 | 50    | 100   | 150   | mV       |  |

| CK input                       | threshold            | V <sub>TH</sub> |                                 | 0.8   | 1.2   | 2     | V        |  |

| CK input                       | CK input current     |                 | Vck=5.0V                        |       | 0     | 1     | μА       |  |

| OK IIIpu                       |                      |                 | Vck=0V                          | -14.5 | -8.5  | -4.5  |          |  |

| Output vol                     | tage (High)          | Vон             | I RESET =-1μA, Vs=OPEN          | 4.0   | 4.5   |       | V        |  |

|                                |                      | Vol1            | I RESET =0.5mA, Vs=0V           |       | 0.10  | 0.20  |          |  |

| Output vol                     | Output voltage (Low) |                 | I RESET =2.0mA, Vs=0V           | 0.15  | 0.35  | V     |          |  |

|                                |                      |                 | Vol I RESET =2.0mA, Vs=0V       |       | 0.13  |       | 0.30     |  |

| Output sy                      | Output sync current  |                 | $V = 1.0V, V_S = 0V$            | 2     | 4     |       | mA       |  |

|                                | MM1145A              | Іст1            | During watchdog timer operation | -0.40 | -0.48 | -0.60 | μA       |  |

| C <sub>T</sub> charge          | C⊤ charge MM1145B    |                 | During watchdog umer operation  |       | -0.22 | -0.30 | μΑ       |  |

| current                        | MM1145A              | Іст2            | During power ON reset operation | -0.21 | -0.31 | -0.62 | μA       |  |

| MM1145B                        |                      | 1012            | During power On reset operation |       | -0.93 | -2.33 | μΑ       |  |

| Minimum operating power supply |                      | Vccl            | V RESET =0.4V                   |       | 0.8   | 1.0   | V        |  |

| voltage to ensure RESET        |                      | VCCL            | I RESET =0.1mA                  |       | 0.0   | 1.0   | <b>v</b> |  |

# Electrical Characteristics (DC) (Except where noted otherwise, Ta=25°C, Vcc=5.0V) (Except where noted otherwise, resistance unit is Ω)

| Item                          |         | Symbol         | Measurement conditions                       | Min. | Тур. | Max. | Units |

|-------------------------------|---------|----------------|----------------------------------------------|------|------|------|-------|

| Vcc input pulse width         |         | Ты             | Vcc 4.0V                                     | 8    |      |      | μs    |

| CK input pulse width          |         | Тскw1<br>Тскw2 | CK or                                        | 3    |      |      | μs    |

| CK input cycle *7             |         | Тск1<br>Тск2   | or                                           | 200  |      |      | μs    |

| Watchdog timer                | MM1145A | Twd            | Ст=0.02μF, Rrcт=1M                           | 40   | 50   | 60   | ms    |

| monitoring time *1            | MM1145B | IWD            | C1-0.02μΓ, RRC1-11VI                         | 80   | 110  | 140  |       |

| Watchdog timer                | MM1145A | Twr            | C <sub>T</sub> =0.02μF, R <sub>RCT</sub> =1M | 5    | 10   | 15   | ms    |

| reset time *2                 | MM1145B | IWK            | C1=0.02μ <b>Γ</b> , RRC1=1W                  | 5    | 10   | 15   |       |

| Reset hold time for           | MM1145A | Tpr            | C <sub>T</sub> =0.02µF                       | 50   | 100  | 150  | ma    |

| power supply rise *3          | MM1145B | 1 PK           | $R_{RCT}=1M$ $V_{CC}$                        | 20   | 40   | 60   | ms    |

| Output delay time from Vcc *4 |         | TPD            | RESET pin, RL=10k, CL=20pF                   |      | 2    | 10   | μs    |

| Output rise time *5           |         | tr             | RESET pin, RL=10k, CL=20pF                   |      | 2.0  | 4.0  | μs    |

| Output fall time *5           |         | tr             | RESET pin, RL=10k, CL=20pF                   |      | 0.2  | 1.0  | μs    |

#### Notes:

- \*1 Monitoring time is the time from the last pulse (negative edge) of the timer clear clock pulse until reset pulse output.

- In other words, reset output is output if a clock pulse is not input during this time.

- \*2 Reset time means reset pulse width. However, this does not apply to power ON reset.

- \*3 Reset hold time is the time from when Vcc exceeds detection voltage (Vshr) during power ON reset until reset release (RESET output high).

- \*4 Output delay time is the time from when power supply voltage drops below detection voltage (VsL) until reset state occurs (RESET output low).

- \*5 The voltage range when measuring output rise and fall time is 10~90%.

- \*7 1 Set CK1 and CK2 input cycles within the following range.

$T_{CK1} \le nT_{CK2} < T_{WD} (ms) (n \le 1)$

RESET output may go low even if CK1 and CK2 are input without these conditions being met. (Recommended use is for  $T_{CK1} \le nT_{CK2}$ )

2 Tcκ1, Tcκ2  $\leq$  200 μs results in the following operation.

Discharge switches to charging with the CK2 pulse (negative edge) that inputs 200 $\mu$ s after C<sub>T</sub> switches from charging to discharge by the CK2 pulse (negative edge).  $\overline{\text{RESET}}$  output stays high while this operation is being repeated. (However, Tck1, Tck2  $\geq$  20 $\mu$ s.)

## Formula for CT Pin External Constant

Watchdog timer monitoring time (TwD), watchdog timer reset time (TwR) and reset hold time (TPR) during power supply rise can be changed by varying CT capacitance. TwD also can be changed with RRCT.

The variable times are expressed by the following.

1. MM1145A

TPR (ms)  $= 5000 \times CT (\mu F)$

Two (ms) =  $2500 \times C_T (\mu F) \times R_{RCT} (M\Omega)$

Twr (ms)  $= 500 \times C_T (\mu F)$

Example : when C<sub>T</sub>=0.02 $\mu$ F, R<sub>RCT</sub>=1M $\Omega$

$T_{PR} = 100 ms$   $T_{WD} = 50 ms$   $T_{WR} = 10 ms$

2. MM1145B

Tpr (ms)  $= 2000 \times CT (\mu F)$

Two (ms)  $= 5500 \times C_T (\mu F) \times R_{RCT} (M\Omega)$

Twr (ms)  $= 500 \times C_T (\mu F)$

Example : when C<sub>T</sub>=0.02 $\mu$ F, R<sub>RCT</sub>=1M $\Omega$

T<sub>PR</sub> ≒ 40ms

T<sub>WD</sub> ≒ 110ms

T<sub>WR</sub> ≒ 10ms

## Formula for Watchdog Timer Monitoring Time (TwD) Adjustment

The ratio between TPR and TwD can be changed within the range below by adjusting TwD with RRCT.

1. MM1145A

Twd/Tpr  $= 2.0 \times Rrct (0.39 (M\Omega)) \le Rrct \le 2 (M\Omega)$

2. MM1145B

TwD/TPR  $= 2.75 \times RRCT (0.39 (M\Omega)) \le RRCT \le 2 (M\Omega)$

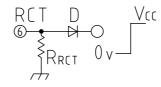

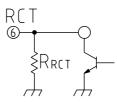

### How to Use RCT Pin

#### Example 1

### Example 2

- 1. Watchdog timer operates when RCT pin is open.

- 2. Watchdog timer stops operating when RCT pin is connected to ground.

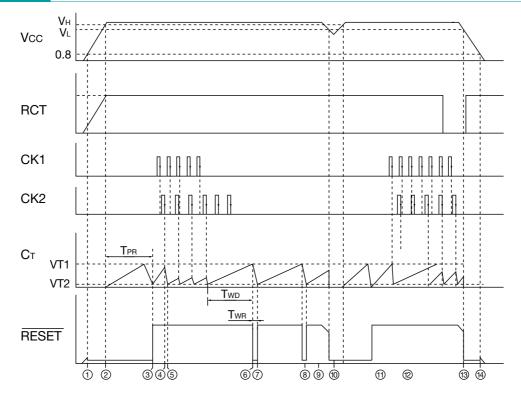

## **Description of Operation**

- RESET goes low when Vcc rises to approximately 0.8V.

Approximately 1µA (Vcc=0.8V) of pull up current is output from RESET.

- 2. Capacitor C<sub>T</sub> charging starts when V<sub>CC</sub> rises to V<sub>SH</sub> (≒ 4.3V). Output is in reset state at this time.

- 3. Output reset is released (RESET goes high) after a certain time (TPR), from when CT starts charging until discharge (the time from when CT voltage reaches a certain threshold value VT1 (≒ 1.4V) until CT voltage drops to a certain threshold value VT2 (≒ 0.2V).

Reset hold time: TPR is as follows.

TPR (ms)  $= 5000 \times CT (\mu F)$

C<sub>T</sub> charging starts again after reset release, and watchdog timer operation begins.

Clock input during power ON reset time (TPR) will cause mis-operation.

- 4. If CK1 and CK2 are input in that order (or simultaneously) during C<sub>T</sub> charging, CK2 negative edge trigger causes the TC pin to switch from charging to discharge.

- 5. Discharge switches to charging when C<sub>T</sub> voltage drops to threshold value VT2 (≒ 0.2V). Steps 4 and 5 are repeated while a normal clock is input from the logic system.

- Operation is as follows if either clock CK1 or CK2 ceases (the figure shows CK1).

Output goes to reset state (RESET goes low) when C<sub>T</sub> voltage reaches reset ON threshold value VT1 (≒ 1.4V).

- The formula for  $C_T$  charging time ( $T_{WD}$ : watchdog timer monitoring time) until reset is output is as follows.  $T_{WD}$  (ms)  $= 2500 \times C_T$  ( $\mu$ F)

- 7. Watchdog timer reset time TwR is the discharge time until C<sub>T</sub> voltage drops to reset OFF threshold value VT2 from reset ON threshold value VT1. The formula is as follows.

Twr (ms)  $= 500 \times C_T (\mu F)$

After reset OFF threshold value is reached, output reset is released and C<sub>T</sub> starts charging. Thereafter, steps 4 and 5 are repeated if a normal clock is input, and when one of the clocks ceases, 6 and 7 are repeated.

In the same way, 6 and 7 are repeated if both clocks CK1 and CK2 cease.

- 8. Reset is output when Vcc drops to VsL (≒ 4.2V). C⊤ is charged simultaneously.

- 9. C⊤ charging starts when Vcc rises to Vsн.

- When  $V_{CC}$  drops momentarily,  $C_T$  charging begins after the charge is first discharged, if the time from  $V_{CC}$  dropping below  $V_{SL}$  until it rises to  $V_{SH}$  is longer than the  $V_{CC}$  input pulse width standard value  $T_{PL}$ .

- 10. Output reset is released after Vcc goes above VsH and after TpB, and the watchdog timer starts.

- 11. Watchdog timer operation can be stopped by switching RcT voltage from high to low. (Clocks CK1 and CK2 are invalid. Regardless of status, TC pin voltage discharges quickly and goes to 0V.) This operation can be applied from any timing. In this state the IC functions as a reset IC with power ON reset.

- 12. Watchdog timer operation re-starts when RcT voltage switches to high.

- 13. When power is OFF, reset is output if Vcc goes below Vsl.

- 14. When Vcc drops to 0V, reset output is held until Vcc reaches 0.8V.

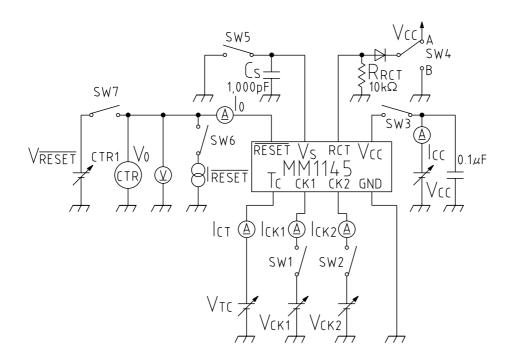

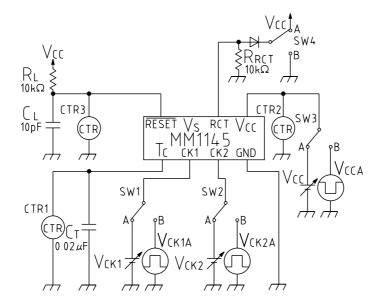

## **Measuring Circuit**

#### Measuring Circuit 1

### Measuring Circuit 2

## **Timing Chart**

## Basic Circuit Diagram