Preliminary

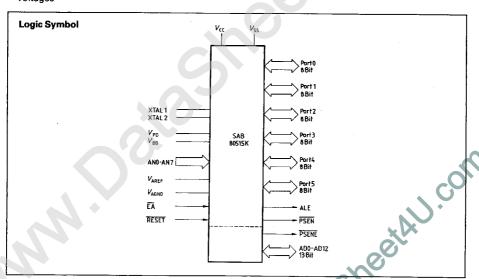

## SAB 80515K 8-Bit Single-Chip Microcontroller ROM-less Version

- Additional bus interface for external memory

- 256 × 8 RAM

- Six 8-bit ports

- Three 16-bit timer/event counters

- Highly flexible reload, capture, compare capabilities

- · Full-duplex serial channel

- Twelve interrupt sources, four priority levels

- 8-bit A/D converter with 8 multiplexed analog inputs and programmable internal reference voltages

- 16-bit watchdog timer.

- V<sub>PD</sub> provides standby current for 40 bytes of RAM

- Boolean processor

- 256 bit-addressable locations

- Most instructions execute in 1 us

- 4 μs multiply and divide

- External memory expandable to 128 Kbyte

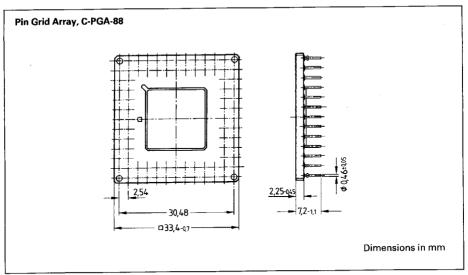

- Pin grid array package, 88 pins (C-PGA-88)

The SAB 80515K is a special ROM-less version of the 8-bit microcontroller SAB 80515. The SAB 80515K contains an additional bus interface to connect an external program memory in place of the SAB 80515's on-chip ROM. Thereby, the SAB 80515K maintains the full I/O capability of the single-chip SAB 80515 while it permits connection of an external program

memory. All other features of the SAB 80515K are identical with those of the SAB 80515. The SAB 80515K is fabricated in +5V advanced N-channel, silicon gate Siemens MYMOS technology, and supplied as pin grid array with 88 pins

T-49-19-61

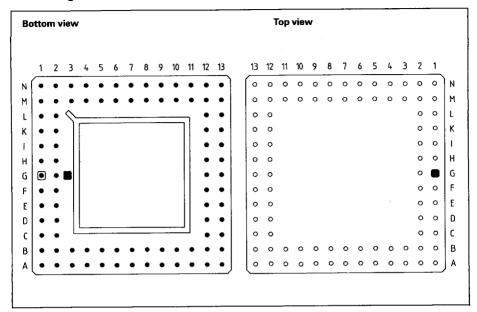

## **Pin Configuration**

**SAB 80515K**

T-49-19-61

## **Pin Definitions and Functions**

| Symbol                                                                                     | Pin                                                                                             | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD0<br>AD1<br>AD2<br>AD3<br>AD4<br>AD5<br>AD6<br>AD7<br>AD8<br>AD9<br>AD10<br>AD11<br>AD12 | J 13<br>J 12<br>K 13<br>K 12<br>L 13<br>M 13<br>L 12<br>N 13<br>N 8<br>M 7<br>N 7<br>M 6<br>N 6 | 1/0                     | Multiplexed address/data bus for the program memory. This bus is used for connecting an external memory in place of the 8-Kbyte internal ROM of the SAB 80515. Pins AD0 to AD12 can sink/source 5 LS-TTL loads.                                                                                                                                                                                   |

| AN0<br>AN1<br>AN2<br>AN3<br>AN4<br>AN5<br>AN6<br>AN7                                       | A8<br>B8<br>A7<br>B7<br>A6<br>B6<br>A5<br>B5                                                    | 1                       | Multiplexed analog inputs of the A/D converter.                                                                                                                                                                                                                                                                                                                                                   |

| P0.0<br>P0.1<br>P0.2<br>P0.3<br>P0.4<br>P0.5<br>P0.6<br>P0.7                               | N 1<br>M2<br>L 2<br>M1<br>K 2<br>L 1<br>K 1<br>J 2                                              | 1/0                     | Port 0 is an 8-bit open-drain bidirectional I/O port. It is also the multiplexed low-order address and data bus during accesses to external program and data memory. Port 0 can sink/source 8 LS-TTL loads.                                                                                                                                                                                       |

| P1.0<br>P1.1<br>P1.2<br>P1.3<br>P1.4<br>P1.5<br>P1.6<br>P1.7                               | F 13<br>F 12<br>E 13<br>E 12<br>D 13<br>C 13<br>D 12<br>B 13                                    | 1/0                     | Port 1 is an 8-bit quasi-bidirectional I/O port. It also contains the interrupt, timer, clock, capture and compare pins that are used by various options. The output latch must be programmed to a one (1) for that function to operate (except when used for the compare functions). Port 1 can sink/source 4 LS-TTL loads. The secondary functions are assigned to the port 1 pins, as follows: |

## Pin Definitions and Functions (cont'd)

T-49-19-61

| Symbol                                                       | Pin                                                        | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------|------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2.0<br>P2.1<br>P2.2<br>P2.3<br>P2.4<br>P2.5<br>P2.6<br>P2.7 | M 11<br>N 12<br>M 10<br>N 11<br>N 10<br>M 9<br>N 9<br>M 8  | 1/0                     | Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX@DPTR). In this application, port 2 employs strong internal pullup resistors when issuing 1 s. During accesses to external data memory that use 8-bit addresses (MOVX@RI), port 2 issues the contents of the P2 special function register. Port 2 can sink/source 4 LS-TTL loads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

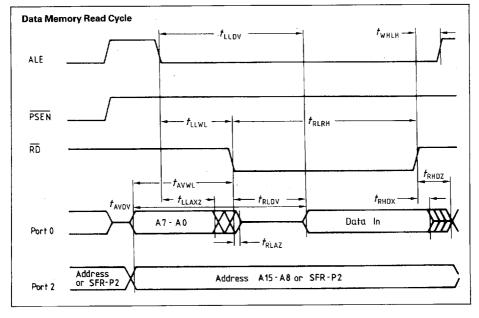

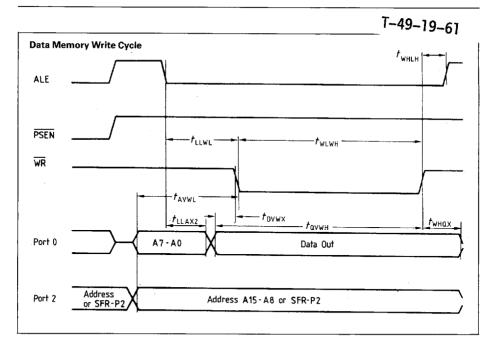

| P3.0<br>P3.1<br>P3.2<br>P3.3<br>P3.4<br>P3.5<br>P3.6<br>P3.7 | A 9<br>B 9<br>A 10<br>B 10<br>A 11<br>A 12<br>B 12<br>C 12 | 1/0                     | Port 3 is an 8-bit quasi-bidirectional I/O port. It also contains the interrupt, timer, serial port and external memory strobe pins that are used by various options. The output latch corresponding to a secondary function must be programmed to a one (1) for that function to operate. Port 3 can sink/source 4 LS-TTL loads. The secondary functions are assigned to the pins of port 3, as follows:  — RxD (P3.0): serial port's receiver data input (asynchronous) or data input/output (synchronous)  — TxD (P3.1): serial port's transmitter data output (asynchronous) or clock output (synchronous)  — INTO (P3.2): interrupt 0 input/timer 0 gate control input  — INT1 (P3.3): interrupt 1 input/timer 1 gate control input  — T1 (P3.5): counter 1 input  — T1 (P3.5): counter 1 input  — WR (P3.6): the write control signal latches the data byte from port 0 into the external data memory  — RD (P3.7): the read control signal enables the external data memory to port 0. |

| P4.0<br>P4.1<br>P4.2<br>P4.3<br>P4.4<br>P4.5<br>P4.6<br>P4.7 | D 1<br>D 2<br>C 1<br>C 2<br>A 1<br>B 2<br>B 3<br>A 2       | 1/0                     | Port 4 is an 8-bit quasi-bidirectional I/O port.<br>Port 4 can sink/source 4 LS-TTL loads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P5.0<br>P5.1<br>P5.2<br>P5.3<br>P5.4<br>P5.5<br>P5.6<br>P5.7 | E 1<br>F 1<br>F 2<br>G 1<br>G 2<br>H 1<br>H 2<br>J 1       | 1/0                     | Port 5 is an 8-bit quasi-bidirectional I/O port. Port 5 can sink/source 4 LS-TTL loads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

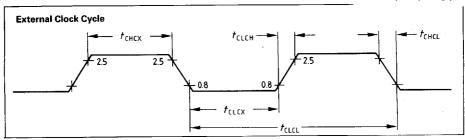

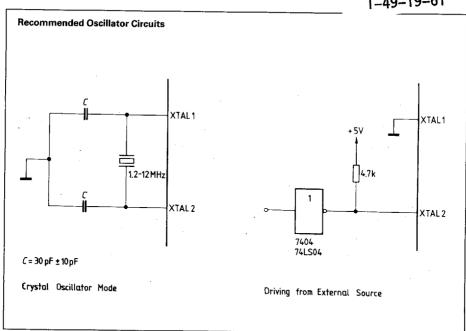

| XTAL2<br>XTAL1                                               | H 12<br>H 13                                               |                         | XTAL2 Output of the inverting oscillator amplifier. To drive the device from en external clock source, XTAL2 should be driven, while XTAL1 is pulled low. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is divided down by a divide-by-two flipflop. Minimum and maximum high and low times specified in the AC characteristics must be observed.  XTAL1 Input to the inverting oscillator amplifier. Required when a crystal or ceramic resonator is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

T-49-19-61

**SAB 80515K**

## Pin Definitions and Functions (cont'd)

| Symbol            | Pin                                      | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                   |  |

|-------------------|------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RESET             | B4                                       | I                       | A low level on this pin for the duration of two machine cycles while the oscillator is running resets the SAB 80515K. A small internal pullup resistor permits power-on reset using only a capacitor connected to $V_{\rm SS}$ .                                                                                           |  |

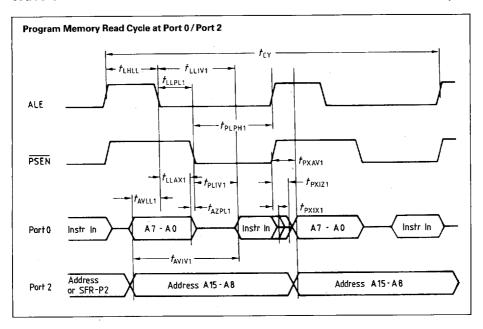

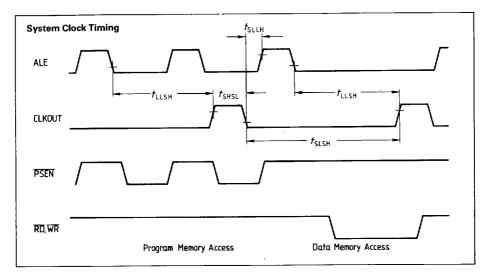

| ALE               | N 2                                      | 0                       | Provides ADDRESS LATCH ENABLE output used for latching the address into external memories at port 0 and 2, and AD0-AD12. It is activated every six oscillator periods except during external data memory accesses.                                                                                                         |  |

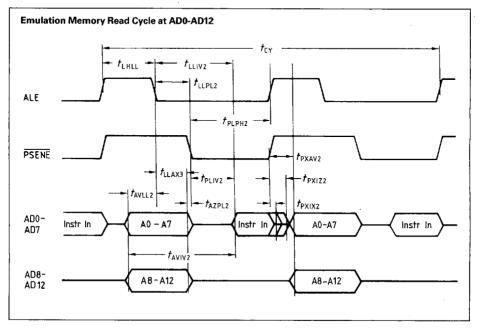

| PSEN              | N 3                                      | 0                       | The PROGRAM STORE ENABLE output is a control signal that enables the external program memory at port 0 and 2 to the bus during external fetch operations. It is activated every six oscillator periods except during external data memory accesses. Remains high during program execution from program memory at AD0-AD12. |  |

| PSENE             | M 12                                     | 0                       | This output is a control signal that enables the program memory at AD0-AD12 during instruction fetch operations. It is activated every six oscillator periods.                                                                                                                                                             |  |

| EA                | M 3                                      | 1                       | When EA is held at a TTL high level, the SAB 80515K execute instructions from the program memory that is connected to AD0-AD12 when the PC is less than 8192.  When EA is held at a TTL low level, the SAB 80515K executes all instructions from external program memory.                                                  |  |

| V <sub>AREF</sub> | A 3                                      |                         | Reference voltage for the A/D converter                                                                                                                                                                                                                                                                                    |  |

| V <sub>AGND</sub> | A 4                                      |                         | Reference ground for the A/D converter                                                                                                                                                                                                                                                                                     |  |

| V <sub>cc</sub>   | E 2                                      | į                       | POWER SUPPLY (+5V power supply during normal operation and program verification)                                                                                                                                                                                                                                           |  |

| V <sub>SS</sub>   | G 13                                     |                         | GROUND (0 V)                                                                                                                                                                                                                                                                                                               |  |

| V <sub>PD</sub>   | B 1                                      |                         | POWER DOWN SUPPLY. If $V_{\rm PD}$ is held within its specs while $V_{\rm CC}$ drops below specs, $V_{\rm PD}$ will provide standby power to 40 bytes of the internal RAM. When $V_{\rm PD}$ is low, the RAM's current is drawn from $V_{\rm CC}$ .                                                                        |  |

| V <sub>BB</sub>   | G 12                                     |                         | Substrate pin. Must be connected to V <sub>SS</sub> through a capacitor (47 to 1000 nF) for proper operation of the A/D converter.                                                                                                                                                                                         |  |

| NC                | A 13<br>B 11<br>M 4<br>M 5<br>N 4<br>N 5 |                         | No connection.                                                                                                                                                                                                                                                                                                             |  |

T-49-19-61 Figure 1 **Block Diagram**  $V_{PD}$ ALE EA RESET PSEN PSENE XTAL1 XTAL2 40×8 OSC RAM AD0-AD12 13 - AD0-AD12 216×8 Vcc 0  $V_{SS}$  o Port 0 CPU RESET Port 1 Watchdog Timer 0 Port 2 Timer 1 Port 3 Timer 2 Serial Port Port 4 AN0-AN7 8 S&H V88 0-VAREF O Programmable Port 5 Ref. Voltages VAGNO O

T-49-19-61

#### **Functional Description**

The members of the SAB 80515 family of microcontrollers are:

- SAB 80515 with factory mask-programmable 8 Kbyte on-chip ROM

- SAB 80535 ROM-less version of the SAB 80515

- SAB 80515K ROM-less version of the SAB 80515 with additional bus interface.

In this data sheet the term "SAB 80515" is used to refer generally to all members of the SAB 80515 family, except where specifically stated otherwise.

The architecture of the SAB 80515 is based on the SAB 8051 microcontroller family. The following features of the SAB 80515 are fully compatible with the SAB 8051 features:

- instruction set

- external memory expansion interface (port 0 and port 2)

- full-duplex serial port

- timer/counters 0 and 1

- alternate functions on port 3

- the lower 128 bytes of internal RAM and the lower 4 Kbytes of internal ROM

Different to the SAB 8051 are the RAM power-down supply, which supplies 40 byte with a typical current of 2 mA, and the powerful interrupt structure with 12 sources and 4 priority levels.

The SAB 80515 additionally contains 128 byte of internal RAM and 4 Kbyte of internal ROM, that means a total of 256 byte RAM and 8 Kbyte ROM (SAB 80515 only) on-chip. The SAB 80515 has a 16-bit timer/counter with a 2:1 prescaler, reload mode, compare and capture capability. It also contains a 16-bit watchdog timer, an 8-bit A/D converter with 8 analog inputs and programmable reference voltages, two additional quasi-bidirectional 8-bit ports, and a programmable clock output  $(f_{osc}/12)$ .

The SAB 80515K is a special ROM-less version of the SAB 80515. In place of the 8 Kbyte on-chip ROM there is an additional bus interface for an 8 Kbyte program memory which can be connected externally.

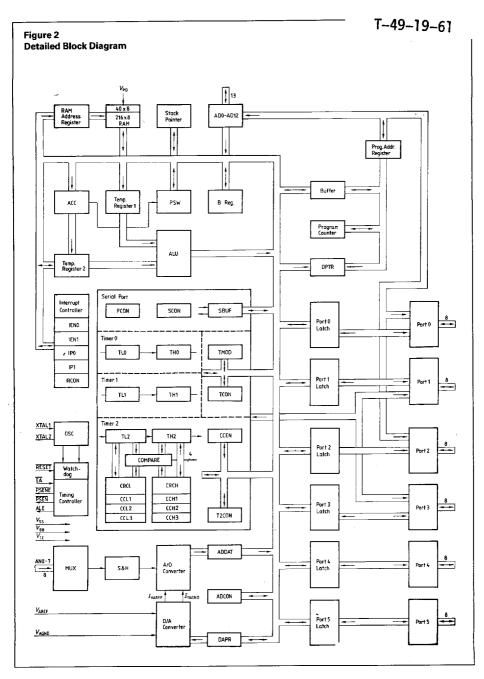

Figure 2 shows a detailed block diagram of the SAB 80515K.

#### **CPU**

The SAB 80515 is efficient both as a controller and as an arithmetic processor. It has extensive facilities of binary and BCD arithmetic and excels in bithandling capabilities. Efficient use of program memory results from an instruction set consisting of 44% one-byte, 41% two-byte, and 15% three-byte instructions. With a 12 MHz crystal, 58% of the instructions execute in 1.0 µs.

#### Memory Organization

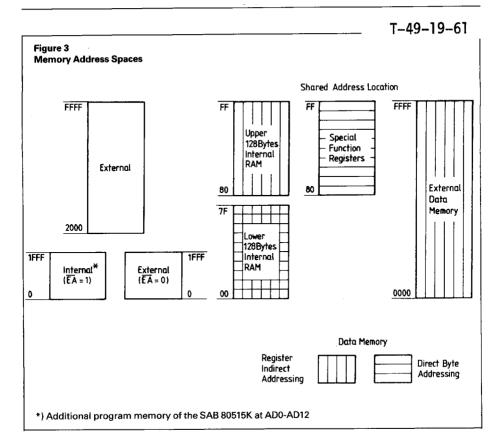

The SAB 80515 manipulates operands in the four memory address spaces described below.

#### Program memory

The SAB 80515 has 8 Kbyte of on-chip ROM, while the SAB 80535 has no internal ROM. The program memory can be externally expanded up to 64 Kbyte. If the EA pin is held high, the SAB 80515 executes out of internal ROM unless the address exceeds 1FFFH. Locations 2000H through 0FFFFH are then fetched from the external program memory. If the EA pin is held low, the SAB 80515 fetches all instructions from the external program memory. Since the SAB 80535 has no internal ROM, pin EA must be tied low when using this device.

The SAB 80515K has the same function as the SAB 80515: the difference is that fetches from the internal ROM are executed from a program memory via the additional bus interface (AD0-AD12).

#### Data memory

The data memory address space consists of an internal and an external memory space. The internal data memory is divided into three physically separate and distinct blocks: the lower 128 byte of RAM; the upper 128 byte of RAM; and the 128-byte special function register (SFR) area. While the upper 128 byte of data memory and the SFR area share the same address locations, they are accessed through different addressing modes. The lower 128 byte of data memory can be accessed through direct or register-indirect addressing; the upper 128 byte of RAM can be accessed through register-indirect addressing; and the special function registers are accessed through direct addressing.

Four 8-register banks occupy locations 0 through 1FH in the lower RAM area. The next 16 bytes. locations 20H through 2FH, contain 128 directly addressable bit locations. The stack can be located anywhere in the internal data memory address space, and the stack depths can be expanded up to 256 byte.

The external data memory can be expanded up to 64 Kbyte and can be accessed by instructions that use a 16-bit or an 8-bit address.

T-49-19-61

**SAB 80515K**

All registers, except the program counter and the four 8-register banks, reside in the special function register area. The 41 special function registers (SFR's) include arithmetic registers, pointers, and registers that provide an interface between the CPU

and the on-chip peripheral functions. There are also 128 directly addressable bits within the SFR area. The special function registers are listed in the following table:

| Sy | rmbol | Name                                       | Address |

|----|-------|--------------------------------------------|---------|

| *  | P0    | Port 0                                     | 80H     |

|    | SP    | Stack pointer                              | 81H     |

|    | DPL   | Data pointer, low byte                     | 82H     |

|    | DPH   | Data pointer, high byte                    | 83H     |

|    | PCON  | Power control register                     | 87H     |

| *  | TCON  | Timer control register                     | 88H     |

|    | TMOD  | Timer mode register                        | 89H     |

|    | TLO   | Timer 0, low byte                          | 8AH     |

|    | TL1   | Timer 1, low byte                          | 8BH     |

|    | THO   | Timer 0, high byte                         | 8CH     |

|    | TH1   | Timer 1, high byte                         | 8DH     |

| *  | P1    | Port 1                                     | 90H     |

| *  | SCON  | Serial port control register               | 98H     |

|    | SBUF  | Serial port buffer register                | 99H     |

| *  | P2    | Port 2                                     | OAOH    |

| *  | IEN0  | Interrupt enable register 0                | 0A8H    |

|    | IP0   | Interrupt priority register 0              | 0A9H    |

| *  | P3    | Port 3                                     | овон    |

| *  | IEN1  | Interrupt enable register 1                | ован    |

|    | IP1   | Interrupt priority register 1              | овен    |

| *  | IRCON | Interrupt request control register         | осон    |

|    | CCEN  | Compare/capture enable register            | 0C1H    |

|    | CCL1  | Compare/capture register 1, low byte       | 0C2H    |

|    | CCH1  | Compare/capture register 1, high byte      | осзн    |

|    | CCL2  | Compare/capture register 2, low byte       | 0C4H    |

|    | CCH2  | Compare/capture register 2, high byte      | 0C5H    |

|    | CCL3  | Compare/capture register 3, low byte       | 0C6H    |

|    | CCH3  | Compare/capture register 3, high byte      | 0C7H    |

| *  | T2CON | Timer 2 control register                   | освн    |

|    | CRCL  | Compare/reload/capture register, low byte  | 0CAH    |

|    | CRCH  | Compare/reload/capture register, high byte | освн    |

|    | TL2   | Timer 2, low byte                          | оссн    |

|    | TH2   | Timer 2, high byte                         | 0CDH    |

| •  | PSW   | Program status word register               | 0D0H    |

| ŧ  | ADCON | A/D converter control register             | 0D8H    |

|    | ADDAT | A/D converter data register                | 0D9H    |

|    | DAPR  | D/A converter program register             | 0DAH    |

| +  | ACC   | Accumulator                                | 0E0H    |

| *  | P4    | Port 4                                     | 0E8H    |

| ŧ  | В     | B register                                 | огон    |

| K- | P5    | Port 5                                     | 0F8H    |

The SFR's marked with an asterisk (\*) are both bit and byte-addressable.

Figure 3 illustrates the memory address spaces of the SAB 80515.

#### I/O Ports

The SAB 80515 has six 8-bit ports. Port 0 is an open-drain bidirectional I/O port, while ports 1 to 5 are quasi-bidirectional I/O ports with internal pullups. That means, when configured as inputs, ports 1 to 5 will pull high, and will source current when externally pulled low. Port 0 will float when configured as input.

Port 0 and port 2 can be used to expand the program and data memory externally. During access to external memory, port 0 emits the low-order address byte and reads/writes the data byte, while port 2 emits the high-order address byte. In this function, port 0 is not an open-drain port, but uses a strong internal pullup FET.

## SIEMENS AKTIENGESELLSCHAF SAB 80515K

T-49-19-61

Ports 1 and 3 are provided for several alternate functions, as listed below:

| Port | Symbol   | Function                                                      |

|------|----------|---------------------------------------------------------------|

| P1.0 | INT3/CC0 | External interrupt 3 input, compare 0 output, capture 0 input |

| P1.1 | INT4/CC1 | External interrupt 4 input, compare 1 output, capture 1 input |

| P1.2 | INT5/CC2 | External interrupt 5 input, compare 2 output, capture 2 input |

| P1.3 | INT6/CC3 | External interrupt 6 input, compare 3 output, capture 3 input |

| P1.4 | ĪNT2     | External interrupt 2 input                                    |

| P1.5 | T2EX     | Timer 2 external reload trigger input                         |

| P1.6 | CLKOUT   | System clock output                                           |

| P1.7 | T2       | Timer 2 external counter input                                |

| P3.0 | RXD      | Serial input port                                             |

| P3.1 | TXD      | Serial output port                                            |

| P3.2 | ĪNT0     | External interrupt 0 input, timer 0 gate control              |

| P3.3 | ĪNT1     | External interrupt 1 input, timer 1 gate control              |

| P3.4 | T0       | Timer 0 external counter input                                |

| P3.5 | T1       | Timer 1 external counter input                                |

| P3.6 | WR       | External data memory write strobe                             |

| P3.7 | RD       | External data memory read strobe                              |

#### Timer/Counters

The SAB 80515 contains three 16-bit timer/counters which are useful in many applications for timing and counting. The input clock for each timer/counter is 1/12 of the oscillator frequency in the timer operation or can be taken from an external clock source for the counter operation (maximum count rate is 1/24 of the oscillator frequency).

#### -Timer/counters 0 and 1

These timer/counters can operate in four modes:

Mode 0: 8-bit timer/counter with 32:1 prescaler

Mode 1: 16-bit timer/counter

Mode 2: 8-bit timer/counter with 8-bit auto-reload

Mode 3: Timer/counter 0 is configured as one 8-bit timer/counter and one 8-bit timer; timer/counter 1 in this mode holds its

count.

External inputs  $\overline{\text{INT0}}$  and  $\overline{\text{INT1}}$  can be programmed to function as a gate for timer/counters 0 and 1 to facilitate pulse width measurements.

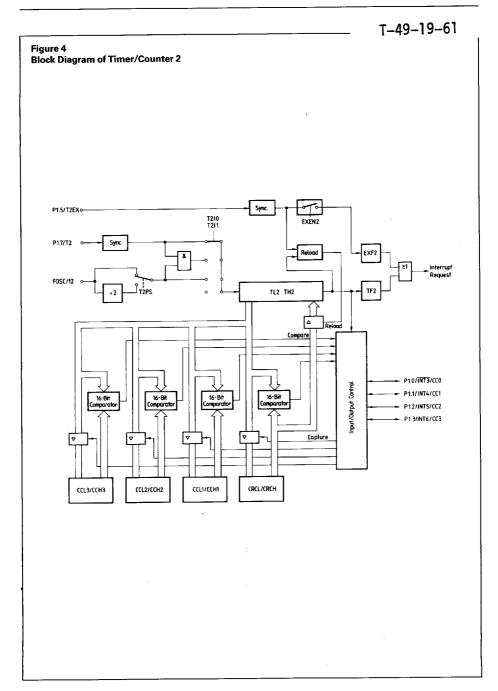

#### -Timer/counter 2

Timer/counter 2 of the SAB 80515 is a 16-bit timer/counter with several additional features. It offers a 2:1 prescaler, a selectable gate function, and compare, capture and reload functions. Corresponding to the 16-bit timer register there are four 16-bit capture/compare registers, one of them can be used to perform a 16-bit reload on a timer overflow or external event. Each of these registers corresponds to a pin on port 1 for capture input/compare output.

Figure 4 shows a block diagram of timer/counter 2.

**SAB 80515K**

#### SIEMENS AKTIENGESELLSCHAF

T-49-19-61

#### Reload

With the 16-bit CRC register, which is a concatenation of the 8-bit registers CRCL and CRCH, a 16-bit reload can be performed. There are two modes from which to select:

Mode 0: Reload is caused by a timer 2 overflow (auto-reload).

Mode 1: Reload is caused in response to a negative transition at pin T2EX (P1.5), which can also request an interrupt.

#### Compare

In the compare mode, the 16-bit values stored in the dedicated compare registers are compared to the contents of the timer 2 registers. If the count value in the timer 2 registers matches one of the stored values, an appropriate output signal is generated and an interrupt is requested. Two compare modes are provided:

Mode 0: Upon a match the output signal changes from low to high. It goes back to a low level when timer 2 overflows.

Mode 1: The transition of the output signal can be determined by software. A timer 2 overflow causes no output change.

#### Capture

This feature permits saving the actual timer/counter contents into a selected register upon an external event or a software write operation. Two modes are provided to latch the current 16-bit value in timer 2 registers into a dedicated capture register:

Mode 0: Capture is performed in response to a transition at the corresponding port 1 pins CC0 to CC3.

Mode 1: Write operation into the low-order byte of the dedicated capture register causes the timer 2 contents to be latched into this register.

#### Serial Port

The serial port of the SAB 80515 permits the full duplex communication between microcontrollers or between microcontrollers and peripheral devices. The serial port can operate in 4 modes:

Mode 0: Shift register mode. Serial data enters and exits through RxD. TxD outputs the shift clock. 8 bits are transmitted/received: 8 data bits (LSB first). The baud rate is fixed at 1/12 of the oscillator frequency.

Mode 1: 10 bits are transmitted (through RxD) or received (through TxD): a start bit (0), 8 data bits (LSB first), and a stop bit (1). The baud rate is variable.

Mode 2: 11 bits are transmitted (through RxD) or received (through TxD): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). The baud rate is programmable to either 1/32 or 1/64 of the oscillator frequency.

Mode 3: 11 bits are transmitted (through TxD) or received (through RxD): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). Mode 3 is the same as mode 2 in all respects except the baud rate. The baud rate in mode 3 is variable.

The variable baud rates can be generated by timer 1 or an internal baud rate generator.

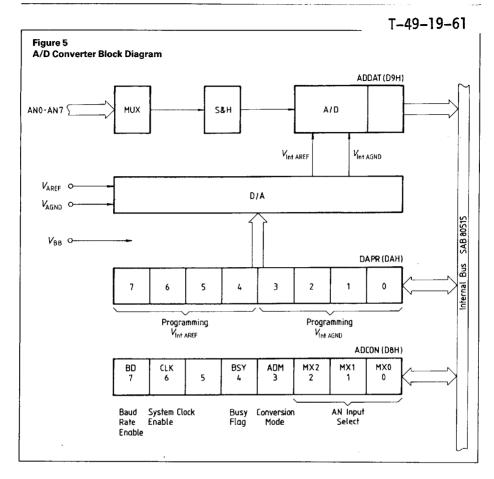

#### A/D Converter

The 8-bit A/D converter of the SAB 80515 has 8 multiplexed analog inputs and is using the successive approximation method. The sampling of an analog signal takes 5 machine cycles, the total conversion time is 15 machine cycles (15 µs at 12 MHz oscillator frequency). Conversion can be programmed to be single or continuous, at the end of a conversion an interrupt can be generated.

The internal reference voltages  $V_{\text{IntAREF}}$  and  $V_{\text{IntAGND}}$ for the A/D converter are programmable in 16 steps with respect to the external reference voltages. This feature permits a second conversion with changed internal reference voltages to gain a higher resolution. In addition, the internal reference voltages can easily be adapted by software to the desired analog voltage range. Takes 7 machine cycles each (7 µs at 12 MHz oscillator frequency).

Figure 5 shows a block diagram of the A/D converter of the SAB 80515.

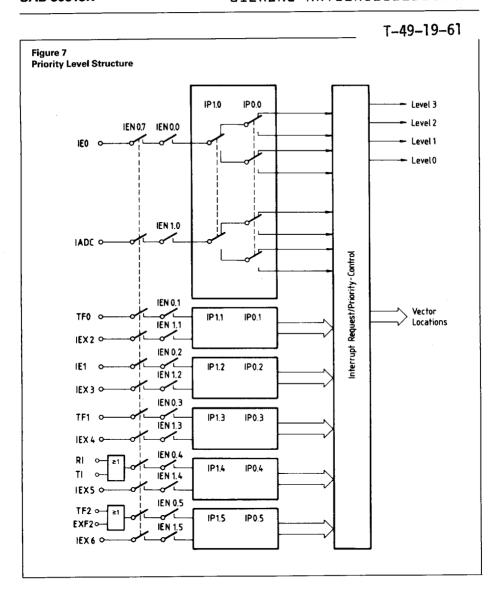

#### Interrupt Structure

The 12 interrupt sources of the SAB 80515 are organized in 6 pairs:

| External interrupt 0  | _ | A/D converter interrupt |

|-----------------------|---|-------------------------|

| Timer 0 interrupt     | _ | External interrupt 2    |

| External interrupt 1  | _ | External interrupt 3    |

| Timer 1 interrupt     | _ | External interrupt 4    |

| Serial port interrupt | _ | External interrupt 5    |

| Timer 2 interrupt     | _ | External interrupt 6    |

Each interrupt source has its own vector address. It can be programmed to one of four priority levels and can individually be enabled/disabled. The minimum interrupt response time is 3 to 8 machine cycles.

External interrupts 0 and 1 can be activated by a low-level or a negative transition (selectable) at their corresponding input pin, external interrupts 2 and 3 can be programmed to be activated by a negative or a positive transition. The external interrupts 4 to 6 are activated by a positive transition. The interrupts 3 to 6 can be combined with the corresponding alternate functions compare (output) and capture (input) on port 1.

Figure 6 shows the interrupt request sources, and figure 7 illustrates the priority level structure of the SAB 80515.

## SIEMENS AKTIENGESELLSCHAF SAB 80515K

T-49-19-61 Figure 6 **Interrupt Request Sources** P3.2/INT 0 IE0 TCON.O Timer 0 Overflow P3.3/INT1 TCON.1 Timer 1 Overflow Receiver Serial Port Transmitter Timer 2 Overflow P1.5/T2EX Interrupt Control A/D Converter P1.4/INT 2 T2CON.5 Compare 0 P1.0/INT3/CC0 IEX3 T2CON.6 Compare 1 P1.1/INT4/CC1 Compare 2 P1.2/INT5/CC2 IEXS Compare 3 P1.3/INT6/CC3

#### **Watchdog Timer**

This feature is provided as a means of graceful recovery from software upset. After a reset, the watchdog timer is cleared and stopped. It can be started and cleared by software, but it cannot be stopped. If the software fails to clear the watchdog timer at least every 65536 machine cycles (about 65 ms if a 12 MHz oscillator frequency is used), a

hardware reset will be initiated. The reset cause (external reset or reset caused by the watchdog) can be examined by software. To clear the watchdog, two bits in two different special function registers must be set by two consecutive instructions. This is done to prevent the watchdog from being cleared by unexpected op codes.

**SAB 80515K**

T-49-19-61

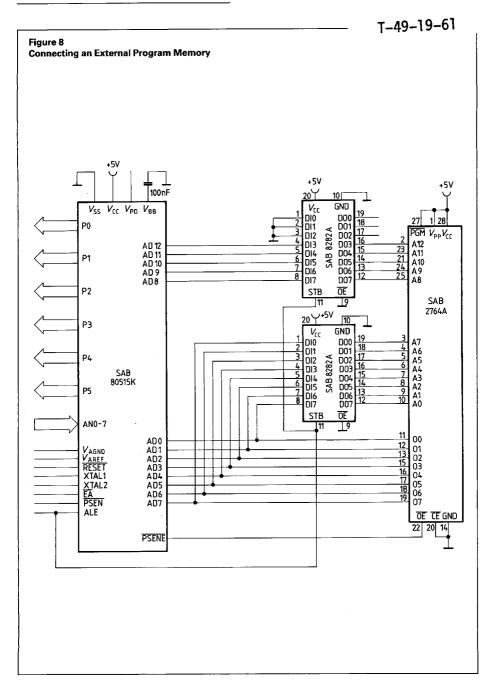

## Connecting an External Program Memory to the SAB 80515K

The ROM-less chip SAB 80515K allows emulating the SAB 80515's internal ROM via the additional bus interface. The multiplexed bus AD0 to AD12 emits the address and reads the instruction at pins AD0 to AD7. Observe that the higher address lines AD8 to AD12 are also multiplexed. The control signals for the emulation memory are ALE and PSENE.

When pin  $\overline{\text{EA}}$  is high, the SAB 80515K executes instructions read from AD0-AD12 if the PC is less than 8192, otherwise it will execute from external program memory at port 0 and 2. When pin  $\overline{\text{EA}}$  is low, the SAB 80515K executes all instructions from external program memory. Figure 8 shows a typical circuitry for connection of a program memory to AD0-AD12 of the SAB 80515K.

## 47E D 📟 8235605 0028588 5 📟 SIEG

## SIEMENS AKTIENGESELLSCHAF SAB 80515K

T-49-19-61

## **Instruction Set Summary**

| Mnemonic    |            | Description                                 | - In | Τ <u>α</u> . |

|-------------|------------|---------------------------------------------|------|--------------|

|             |            | Description                                 | Byte | Cycle        |

| Arithmetic  | operations |                                             |      |              |

| ADD         | A,Rn       | Add register to accumulator                 | 1    | 1            |

| ADD         | A,direct   | Add direct byte to accumulator              | 2    | 1            |

| ADD         | A,@Ri      | Add indirect RAM to accumulator             | 1    | 1            |

| ADD         | A,#data    | Add immediate data to accumulator           | 2    | 1            |

| ADDC        | A,Rn       | Add register to accumulator with carry flag | 1    | 1            |

| ADDC        | A,direct   | Add direct byte to A with carry flag        | 2    | 1            |

| ADDC        | A,@Ri      | Add indirect RAM to A with carry flag       | 1    | 1            |

| ADDC        | A,#data    | Add immediate data to A with carry flag     | 2    | 1            |

| SUBB        | A,Rn       | Subtract register from A with borrow        | 1    | 1            |

| SUBB        | A,direct   | Subtract direct byte from A with borrow     | 2    | 1            |

| SUBB        | A,@Ri      | Subtract indirect RAM from A with borrow    | 1    | 1            |

| SUBB        | A,#data    | Subtract immediate data from A with borrow  | 2    | 1            |

| INC         | Α          | Increment accumulator                       | 1    | 1            |

| INC         | Rn         | Increment register                          | 1    | 1            |

| INC         | direct     | Increment direct byte                       | 2    | 1            |

| INC         | @Ri        | Increment indirect RAM                      | 1    | 1            |

| DEC         | Α          | Decrement accumulator                       | 1    | 1            |

| DEC         | Rn         | Decrement register                          | 1    | 1            |

| DEC         | direct     | Decrement direct byte                       | 2    | 1            |

| DEC         | @Ri        | Decrement indirect RAM                      | 1    | 1            |

| INC         | DPTR       | Increment data pointer                      | 1    | 2            |

| MUL         | AB         | Multiply A and B                            | 1    | 4            |

| DIV         | АВ         | Divide A by B                               | 1    | 4            |

| DA          | Α          | Decimal adjust accumulator                  | 1    | 1            |

| Logical ope | rations    |                                             |      |              |

| ANL         | A,Rn       | AND register to accumulator                 | 1    | 1            |

| ANL         | A,direct   | AND direct byte to accumulator              | 2    | 1            |

| ANL         | A,@Ri      | AND indirect RAM to accumulator             | 1    | 1            |

| ANL         | A,#data    | AND immediate data to accumulator           | 2    | 1            |

| ANL         | direct,A   | AND accumulator to direct byte              | 2    | 1            |

|             |            |                                             |      | 1 .          |

## T-49-19-61

## Instruction Set Summary (cont'd)

| Mnemonic |              | Description                                 | Byte | Cycle |

|----------|--------------|---------------------------------------------|------|-------|

| ANL      | direct,#data | AND immediate data to direct byte           | 3    | 2     |

| ORL      | A,Rn         | OR register to accumulator                  | 1    | 1     |

| ORL      | A,direct     | OR direct byte to accumulator               | 2    | 1     |

| ORL      | A,@Ri        | OR indirect RAM to accumulator              | 1    | 1     |

| ORL      | A,#data      | OR immediate data to accumulator            | 2    | 2     |

| ORL      | direct,A     | OR accumulator to direct byte               | 2    | 1     |

| ORL      | direct,#data | OR immediate data to direct byte            | 3    | 2     |

| XRL      | A,Rn         | Exclusive OR register to accumulator        | 1    | 1     |

| XRL      | A,direct     | Exclusive OR direct byte to accumulator     | 2    | 1     |

| XRL      | A,@Ri        | Exclusive OR indirect RAM to accumulator    | 1    | 1     |

| XRL      | A,#data      | Exclusive OR immediate data to accumulator  | 2    | 1     |

| XRL      | direct,A     | Exclusive OR accumulator to direct byte     | 2    | 1     |

| XRL      | direct,#data | Exclusive OR immediate data to direct       | 3    | 2     |

| CLR      | Α            | Clear accumulator                           | 1    | 1     |

| CPL      | Α            | Complement accumulator                      | 1    | 1     |

| RL       | Α            | Rotate accumulator left                     | 1    | 1     |

| RLC      | Α            | Rotate A left through carry flag            | 1    | 1     |

| RR       | Α            | Rotate accumulator right                    | 1    | 1     |

| RRC      | A            | Rotate accumulator right through carry flag | 1    | 1     |

| SWAP     | A            | Swap nibbles within the accumulator         | 1    | 1     |

#### **Data transfer**

| MOV | A,Rn           | Move register to accumulator       | 1 | 1 |

|-----|----------------|------------------------------------|---|---|

| MOV | A,direct *)    | Move direct byte to accumulator    | 2 | 1 |

| MOV | A,@Ri          | Move indirect RAM to accumulator   | 1 | 1 |

| MOV | A,#data        | Move immediate data to accumulator | 2 | 1 |

| MOV | Rn,A           | Move accumulator to register       | 1 | 1 |

| MOV | Rn,direct      | Move direct byte to register       | 2 | 2 |

| MOV | Rn,#data       | Move immediate data to register    | 2 | 1 |

| MOV | direct,A       | Move accumulator to direct byte    | 2 | 1 |

| MOV | direct,Rn      | Move register to direct byte       | 2 | 2 |

| MOV | direct, direct | Move direct byte to direct         | 3 | 2 |

## SIEMENS AKTIENGESELLSCHAF SAB 80515K

## Instruction Set Summary (cont'd)

T-49-19-61

| Mnemonic |               | Description                                     | Byte | Cycle |

|----------|---------------|-------------------------------------------------|------|-------|

| MOV      | direct,@Ri    | Move indirect RAM to direct byte                | 2    | 2     |

| MOV      | direct,#data  | Move immediate data to direct byte              | 3    | 2     |

| MOV      | @Ri,A         | Move accumulator to indirect RAM                | 1    | 1     |

| MOV      | @Ri,direct    | Move direct byte to indirect RAM                | 2    | 2     |

| MOV      | @Ri,#data     | Move immediate data to indirect RAM             | 2    | 1     |

| MOV      | DPTR,#data 16 | Load data pointer with a 16-bit constant        | 3    | 2     |

| MOVC     | A,@A+DPTR     | Move code byte relative to DPTR to accumulator  | 1    | 2     |

| MOVC     | A,@A+PC       | Move code byte relative to PC to accumulator    | 1    | 2     |

| MOVX     | A,@Ri         | Move external RAM (8-bit addr.) to accumulator  | 1    | 2     |

| MOVX     | A,@DPTR       | Move external RAM (16-bit addr.) to accumulator | 1    | 2     |

| MOVX     | @Ri,A         | Move A to external RAM (8-bit addr.)            | 1    | 2     |

| MOVX     | @DPTR,A       | Move A to external RAM (16-bit addr.)           | 1    | 2     |

| PUSH     | direct        | Push direct byte onto stack                     | 2    | 2     |

| POP      | direct        | Pop direct byte from stack                      | 2    | 2     |

| ХСН      | A,Rn          | Exchange register with accumulator              | 1    | 1     |

| хсн      | A,direct      | Exchange direct byte with accumulator           | 2    | 1     |

| XCH      | A,@Ri         | Exchange indirect RAM with accumulator          | 1    | 1.    |

| XCHD     | A,@Ri         | Exchange low-order digit indirect RAM with A    | 1    | 1     |

#### Boolean variable manipulation

| CLD  |          |                                       |   | Т   |

|------|----------|---------------------------------------|---|-----|

| CLR  | <u>C</u> | Clear carry flag                      | 1 | 1   |

| CLR  | bit      | Clear direct bit                      | 2 | 1   |

| SETB | С        | Set carry flag                        | 1 | 1   |

| SETB | bit      | Set direct bit                        | 2 | 1   |

| CPL  | С        | Complement carry flag                 | 1 | 1   |

| CPL  | bit      | Complement direct bit                 | 2 | 1   |

| ANL  | C,bit    | AND direct bit to carry flag          | 2 | 2   |

| ANL  | C,/bit   | AND complement of direct bit to carry | 2 | 2   |

| ORL  | C,bit    | OR direct bit to carry flag           | 2 | 2   |

| ORL  | C,/bit   | OR complement of direct bit to carry  | 2 | . 2 |

| MOV  | C,bit    | Move direct bit to carry flag         | 2 | 1   |

| MOV  | bit,C    | Move carry flag to direct bit         | 2 | 2   |

T-49-19-61

## Instruction Set Summary (cont'd)

| Mnemonic   |                   | Description                                    | Byte | Cycle |

|------------|-------------------|------------------------------------------------|------|-------|

| Program an | d machine control |                                                |      |       |

| ACALL      | addr 11           | Absolute subroutine call                       | 2    | 2     |

| LCALL      | addr 16           | Long subroutine call                           | 3    | 2     |

| RET        |                   | Return from subroutine                         | 1    | 2     |

| RETI       |                   | Return from interrupt                          | 1    | 2     |

| AJMP       | addr 11           | Absolute jump                                  | 2    | 2     |

| LJMP       | addr 16           | Long jump                                      | 3    | 2     |

| SJMP       | rel               | Short jump (relative addr.)                    | 2    | 2     |

| JMP        | @A+DPTR           | Jump indirect relative to the DPTR             | 1    | 2     |

| JZ         | rel               | Jump if accumulator is zero                    | 2    | 2     |

| JNZ        | rel               | Jump if accumulator is not zero                | 2    | 2     |

| JC         | rel               | Jump if carry flag is set                      | 2    | 2     |

| JNC        | rel               | Jump if carry flag is not set                  | 2    | 2     |

| JB         | bit,rel           | Jump if direct bit is set                      | 3    | 2     |

| JNB        | bit,rel           | Jump if direct bit is not set                  | 3    | 2     |

| JBC        | bit,rel           | Jump if direct bit is set and clear bit        | 3    | 2     |

| CJNE       | A,direct,rel      | Compare direct byte to A and jump if not equal | 3    | 2     |

| CJNE       | A,#data,rel       | Comp. immed. to A and jump if not equal        | 3    | 2     |

| CJNE       | Rn,#data,rel      | Comp. immed. to reg. and jump if not equal     | 3    | 2     |

| CJNE       | @Ri,#data,rel     | Comp. immed. to ind. and jump if not equal     | 3    | 2     |

| DJNZ       | Rn,rel            | Decrement register and jump if not zero        | 2    | 2     |

| DJNZ       | direct,rel        | Decrement direct byte and jump if not zero     | 3    | 2     |

| NOP        |                   | No operation                                   | 1    | 1     |

#### Notes on data addressing modes:

Rn - Working register R0-R7

direct - 128 internal RAM locations, any I/O port,

control or status register

@Ri - Indirect internal or external RAM location addressed by register R0 or R1

#data - 8-bit constant included in instruction

#data 16 - 16-bit constant included as bytes 2 and 3 of instruction

bit - 128 software flags, any I/O pin, control

or status bit

Accumulator

#### Notes on program addressing modes:

addr 16 – Destination address for LCALL and LJMP may be anywhere within the 64-Kbyte program memory address space.

addr 11 — Destination address for ACALL and AJMP will be within the same 2-Kbyte page of program memory as the first byte of the following instruction.

SJMP and all conditional jumps include an 8-bit offset byte. Range is +127/-128 bytes relative to first byte of the following instruction.

All mnemonics copyrighted © Intel Corporation 1980

rel

## SIEMENS AKTIENGESELLSCHAF 3AB 80515K

T-49-19-61

## Instruction Op Codes in Hexadecimal Order

|             | T                  |          | · · · · · · · · · · · · · · · · · · · |             |                 | Г        |                 |

|-------------|--------------------|----------|---------------------------------------|-------------|-----------------|----------|-----------------|

| Hex<br>code | Number<br>of bytes | Mnemonic | Operands                              | Hex<br>code | Number of bytes | Mnemonic | Operands        |

| 00          | 1                  | NOP      |                                       | 34          | 2               | ADDC     | A,#data         |

| 01          | 2                  | AJMP     | code addr                             | 35          | 2               | ADDC     | A,data addr     |

| 02          | 3                  | LJMP     | code addr                             | 36          | 1               | ADDC     | A,@R0           |

| 03          | 1                  | RR       | A                                     | 37          | li              | ADDC     | A,@R1           |

| 04          | 1                  | INC      | l <sub>A</sub>                        | 38          | l i             | ADDC     | A,R0            |

| 05          | 2                  | INC      | data addr                             | 39          | 1               | ADDC     | A,R1            |

| 06          | 1                  | INC      | @R0                                   | 3A          | 1               | ADDC     | A,R2            |

| 07          | 1                  | INC      | @R1                                   | 3B          | 1               | ADDC     | A,R3            |

| 08          | 1                  | INC      | RO                                    | 3C          | 1               | ADDC     | A,R4            |

| 09          | J 1                | INC      | R1                                    | 3D          | l i             | ADDC     | A,R5            |

| 0A          | 1                  | INC      | R2                                    | 3E          | l i             | ADDC     | A,R7            |

| 0B          | 1                  | INC      | R3                                    | 3F          | l i             | ADDC     | A,R7            |

| 0C          | 1                  | INC      | R4                                    | 40          | 2               | JC       | code addr       |

| 0D          | 1                  | INC      | R5                                    | 41          | 2               | AJMP     | code addr       |

| 0E          | 1                  | INC      | R6                                    | 42          | 2               | ORL      | data addr,A     |

| 0F          | 1                  | INC      | R7                                    | 43          | 3               | ORL      | data addr.#data |

| 10          | 3                  | JBC      | bit addr. code addr                   | 44          | 2               | ORL      | A,#data         |

| 11          | 2                  | ACALL    | code addr                             | 45          | 2               | ORL      | A,data addr     |

| 12          | 3                  | LCALL    | code addr                             | 46          | 1               | ORL      | A,@R0           |

| 13          | 1                  | RRC      | A                                     | 47          | 1 1             | ORL      | A,@R1           |

| 14          | 1                  | DEC      | A                                     | 48          | i               | ORL      | A,R0            |

| 15          | 2                  | DEC      | data addr                             | 49          |                 | ORL      | A,R1            |

| 16          | 1                  | DEC      | @R0                                   | 4A          | l i             | ORL      | A,R2            |

| 17          | 1                  | DEC      | @R1                                   | 4B          | l i             | ORL      | A,R3            |

| 18          | 1                  | DEC      | R0                                    | 4C          | ] i             | ORL      | A,R4            |

| 19          | 1                  | DEC      | R1                                    | 4D          | 1               | ORL      | A,R5            |

| 1A          | 1                  | DEC      | R2                                    | 4E          | 1               | ORL      | A,R6            |

| 1B          | 1                  | DEC      | R3                                    | 4F          | 1               | ORL      | A,R7            |

| 1C          | 1                  | DEC      | R4                                    | 50          | 2               | JNC      | code addr       |

| 1D          | 1                  | DEC      | R5                                    | 51          | 2               | ACALL    | code addr       |

| 1E          | 1                  | DEC      | R6                                    | 52          | 2               | ANL      | data addr,A     |

| 1F          | 1                  | DEC      | R7                                    | 53          | 3               | ANL      | data addr.#data |

| 20          | 3                  | JB       | bit addr. code addr                   | 54          | 2               | ANL      | A.#data         |

| 21          | 2                  | AJMP     | code addr                             | 55          | 2               | ANL      | A,data addr     |

| 22          | 1                  | RET      |                                       | 56          | 1               | ANL      | A,@R0           |

| 23          | 1                  | RL       | Α                                     | 57          | i               | ANL      | A,@R1           |

| 24          | 2                  | ADD      | A,#data                               | 58          | i               | ANL      | A,R0            |

| 25          | 2                  | ADD      | A,data addr                           | 59          | i               | ANL      | A,R1            |

| 26          | 1                  | ADD      | A,@R0                                 | 5A          | i l             | ANL      | A,R2            |

| 27          | 1                  | ADD      | A,@R1                                 | 5B          | i l             | ANL      | A,R3            |

| 28          | 1                  | ADD      | A,R0                                  | 5C          | i               | ANL      | A,R4            |

| 29          | 1                  | ADD      | A,R1                                  | 5D          | i               | ANL      | A,R5            |

| 2A          | 1                  | ADD      | A,R2                                  | 5E          | 1               | ANL      | A,R6            |

| 2B          | 1                  | ADD      | A,R3                                  | 5F          | i [             | ANL      | A.R7            |

| 2C          | i l                | ADD      | A,R4                                  | 60          | 2               | JZ       | code addr       |

| 2D          | i                  | ADD      | A,R5                                  | 61          | 2               | AJMP     |                 |

| 2E          | i                  | ADD      | A,R6                                  | 62          | 2               | XRL      | code addr       |

| 2F          | i 1                | ADD      | A,R7                                  | 63          | 3               |          | data addr,A     |

| 30          | 3                  | 1        | bit addr, code addr                   | 64          | 2               |          | data addr,#data |

| 31          | 2                  | I        | code addr                             | 65          | 2               |          | A,#data         |

| 32          | 1                  | RETI     | 0000 4001                             | 66          | 1               |          | A,data addr     |

| 33          | i l                |          | Α                                     | 67          | 1               |          | A,@R0           |

|             | -                  |          | · · · · · · · · · · · · · · · · · · · | 07          | '               | ARL      | A,@R1           |

T-49-19-61

## Instruction Op Codes in Hexadecimal Order (cont'd)

| Hex<br>code | Number of bytes | Mnemonic   | Operands            | Hex<br>code | Number<br>of bytes | Mnemonic | Operands              |

|-------------|-----------------|------------|---------------------|-------------|--------------------|----------|-----------------------|

| 68          | 1               | XRL        | A.R0                | 9C          | 1                  | SUBB     | A,R4                  |

| 69          | 1               | XRL        | A,R1                | 9D          | 1                  | SUBB     | A,R5                  |

| 6A          | 1               | XRL        | A,R2                | 9E          | 1                  | SUBB     | A,R6                  |

| 6B          | l i             | XRL        | A,R3                | 9F          | 1                  | SUBB     | A,R7                  |

| 6C          | 1               | XRL        | A,R4                | A0          | 2                  | ORL      | C,/bit addr           |

| 6D          |                 | XRL        | A,R5                | A1          | 2                  | AJMP     | code addr             |

| 6E          | 1               | XRL        | A,R6                | A2          | 2                  | MOV      | C,bit addr            |

| 6F          |                 | XRL        | A,R7                | A3          | 1                  | INC      | DPTR                  |

| 70          | 2               | JNZ        | code addr           | A4          | l i                | MUL      | AB                    |

| 70<br>71    | 2               | ACALL      | code addr           | A5          | 1 .                | reserved |                       |

| 71          | 2               | ORL        | C.bit addr          | A6          | 2                  | MOV      | @R0,data addr         |

|             | 1               | JMP        | @A+DPTR             | A7          | 2                  | MOV      | @R1,data addr         |

| 73          |                 | 1          | A,#data             | A8          | 2                  | MOV      | R0,data addr          |

| 74          | 2               | MOV<br>MOV | data addr,#data     | A9          | 2                  | MOV      | R1,data addr          |

| 75          | 3               |            |                     | AA          | 2                  | MOV      | R2,data addr          |

| 76          | 2               | MOV        | @R0,#data           | AB          | 2                  | MOV      | R3.data addr          |

| 77          | 2               | MOV        | @R1,#data           | AC          | 2                  | MOV      | R4.data addr          |

| 78          | 2               | MOV        | R0,#data            |             | 2                  | MOV      | R5,data addr          |

| 79          | 2               | MOV        | R1,#data            | AD          | 2                  | MOV      | R6,data addr          |

| 7A          | 2               | MOV        | R2,#data            | ΑE          | 2                  | MOV      | R7,data addr          |

| 7B          | 2               | MOV        | R3,#data            | AF          |                    | 1        | C./bit addr           |

| 7C          | 2               | MOV        | R4,#data            | B0          | 2                  | ANL      |                       |

| 7D          | 2               | MOV        | R5,#data            | B1          | 2                  | ACALL    | code addr             |

| 7E          | 2               | MOV        | R6,#data            | B2          | 2                  | CPL      | bit addr              |

| 7F          | 2               | MOV        | R7,#data            | В3          | 1                  | CPL      | C                     |

| 80          | 2               | SJMP       | code addr           | B4          | 3                  | CJNE     | A,#data,code addr     |

| 81          | 2               | AJMP       | code addr           | B5          | 3                  | CJNE     | A,data addr,code addr |

| 82          | 2               | ANL        | C,bit addr          | B6          | 3                  | CJNE     | @R0,#data,code addr   |

| 83          | 1               | MOVC       | A,@A+PC             | В7          | 3                  | CJNE     | @R1,#data,code addr   |

| 84          | 1               | DIV        | AB                  | B8          | 3                  | CJNE     | R0,#data,code addr    |

| 85          | 3               | MOV        | data addr,data addr | B9          | 3                  | CJNE     | R1,#data,code addr    |

| 86          | 2               | MOV        | data addr,@R0       | BA          | 3                  | CJNE     | R2,#data,code addr    |

| 87          | 2               | MOV        | data addr,@R1       | BB          | 3                  | CJNE     | R3,#data,code addr    |

| 88          | 2               | MOV        | data addr,R0        | BC          | 3                  | CJNE     | R4,#data,code addr    |

| 89          | 2               | MOV        | data addr,R1        | BD          | 3                  | CJNE     | R5,#data,code addr    |

| 8A          | 2               | MOV        | data addr,R2        | BE          | 3                  | CJNE     | R6,#data,code addr    |

| 8B          | 2               | MOV        | data addr,R3        | BF          | 3                  | CJNE     | R7,#data,code addr    |

| 8C          | 2               | MOV        | data addr,R4        | C0          | 2                  | PUSH     | data addr             |

| 8D          | 2               | MOV        | data addr,R5        | C1          | 2                  | AJMP     | code addr             |

| 8E          | 2               | MOV        | data addr,R6        | C2          | 2                  | CLR      | bit addr              |

| 8F          | 2               | MOV        | data addr,R7        | C3          | 1                  | CLR      | C                     |

| 90          | 3               | MOV        | DPTR,#data          | C4          | 1                  | SWAP     | Α                     |

| 91          | 2               | ACALL      | code addr           | C5          | 2                  | XCH      | A,data addr           |

| 92          | 2               | MOV        | bit addr,C          | C6          | 1                  | XCH      | A,@R0                 |

| 93          | 1               | MOVC       | A,@A+DPTR           | C7          | 1                  | XCH      | A,@R1                 |

| 94          | 2               | SUBB       | A,#data             | C8          | 1                  | XCH      | A,R0                  |

| 95          | 2               | SUBB       | A,data addr         | C9          | 1                  | XCH      | A,R1                  |

| 96          | 1               | SUBB       | A,@R0               | CA          | 1                  | XCH      | A,R2                  |

| 97          | 1               | SUBB       | A,@R1               | CB          | 1                  | XCH      | A,R3                  |

| 98          | 1               | SUBB       | A,R0                | CC          | 1                  | XCH      | A,R4                  |

| 99          | 1               | SUBB       | A,R1                | CD          | 1                  | XCH      | A,R5                  |

| 9A          | 1               | SUBB       | A,R2                | CE          | 1                  | XCH      | A,R6                  |

| 9B          | 1               | SUBB       | A,R3                | CF          | 1                  | XCH      | A,R7                  |

T-49-19-61

## Instruction Op Codes in Hexadecimal Order (cont'd)

| Number code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |          | _        |                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------|----------|----------------|

| D1         2         ACALL         code addr           D2         2         SETB         bit addr           D3         1         SETB         C           D4         1         DA         A           D5         3         DJNZ         data addr, code addr           D6         1         XCHD         A,@R0           D7         1         XCHD         A,@R1           D8         2         DJNZ         R0, code addr           D9         2         DJNZ         R1, code addr           DA         2         DJNZ         R3, code addr           DB         2         DJNZ         R3, code addr           DC         2         DJNZ         R5, code addr           DD         2         DJNZ         R7, code addr           DE         2         DJNZ         R7, code addr           DF         2         MOVX         A,@R0 </td <td></td> <td></td> <td>Mnemonic</td> <td>Operands</td> |    |          | Mnemonic | Operands       |

| D1         2         ACALL         code addr           D2         2         SETB         bit addr           D3         1         SETB         C           D4         1         DA         A           D5         3         DJNZ         data addr,code addr           D6         1         XCHD         A,@R0           D7         1         XCHD         A,@R1           D8         2         DJNZ         R0,code addr           D9         2         DJNZ         R1,code addr           DA         2         DJNZ         R3,code addr           DB         2         DJNZ         R5,code addr           DC         2         DJNZ         R5,code addr           DF         2         DJNZ         R6,code addr           DF         2         DJNZ         R6,code addr           DF         2         DJNZ         R6,code addr           E0         1         MOVX         A,@R0           E3         1         MOVX         A,@R0           E3         1         MOVX         A,@R1           E4         1         CLR         A           E5<                                                                                      | D0 | 2        | POP      | data addr      |

| D2         2         SETB         bit addr           D3         1         SETB         C           D4         1         DA         A           D5         3         DJNZ         data addr,code addr           D6         1         XCHD         A,@R1           D7         1         XCHD         A,@R1           D8         2         DJNZ         R0,code addr           D9         2         DJNZ         R1,code addr           DA         2         DJNZ         R3,code addr           DB         2         DJNZ         R5,code addr           DC         2         DJNZ         R6,code addr           DD         2         DJNZ         R7,code addr           DF         2         DJNZ         R7,code addr           DF         2         DJNZ         R6,code addr           DF         2         DJNZ         R7,code addr           E1         2         AJMP         code addr           E2         DJNZ         R7,code addr           E3         1         MOVX         A,@R0           E3         1         MOVX         A,@R0           E4 </td <td>D1</td> <td>2</td> <td></td> <td></td>                               | D1 | 2        |          |                |

| D3         1         SETB         C           D4         1         DA         A           D5         3         DJNZ         data addr,code addr           D6         1         XCHD         A,@R1           D7         1         XCHD         A,@R1           D8         2         DJNZ         R0,code addr           D9         2         DJNZ         R1,code addr           DA         2         DJNZ         R3,code addr           DC         2         DJNZ         R4,code addr           DC         2         DJNZ         R6,code addr           DE         2         DJNZ         R7,code addr           DF         2         MOVX         A,@R0                                                                    | D2 | 2        |          |                |

| D4         1         DA         A           D5         3         DJNZ         data addr,code addr           D6         1         XCHD         A,@R1           D7         1         XCHD         A,@R1           D8         2         DJNZ         R0,code addr           D9         2         DJNZ         R1,code addr           DA         2         DJNZ         R3,code addr           DB         2         DJNZ         R4,code addr           DC         2         DJNZ         R5,code addr           DE         2         DJNZ         R7,code addr           DF         2         MOVX         A,                                                            | D3 | 1        |          |                |

| D5         3         DJNZ         data addr,code addr           D6         1         XCHD         A,@R0           D7         1         XCHD         A,@R1           D8         2         DJNZ         R0,code addr           D9         2         DJNZ         R1,code addr           DA         2         DJNZ         R3,code addr           DB         2         DJNZ         R3,code addr           DC         2         DJNZ         R5,code addr           DD         2         DJNZ         R6,code addr           DF         2         DJNZ         R7,code addr           E0         1         MOVX         A,@DPTR           E1         2         DJNZ         R7,code addr           E0         1         MOVX         A,@R1           E2         1         MOVX         A,@R1           E3         1         MOVX         A,@R1           E4         1         CLR         A           E5         2         MOV         A,RR1           E6         1         MOV         A,R0           E9         1         MOV         A,R3           EC </td <td></td> <td>1</td> <td></td> <td></td>                                          |    | 1        |          |                |

| D6         1         XCHD         A,@R0           D7         1         XCHD         A,@R1           D8         2         DJNZ         R0,code addr           D9         2         DJNZ         R1,code addr           DA         2         DJNZ         R2,code addr           DB         2         DJNZ         R3,code addr           DC         2         DJNZ         R5,code addr           DD         2         DJNZ         R6,code addr           DF         2         DJNZ         R6,code addr           E0         1         MOVX         A,@DPTR           E1         2         DJNZ         R3,code addr           E0         1         MOVX         A,@DPTR           E1         2         DJNZ         R6,code addr           E0         1         MOVX         A,@R0           E3         1         MOVX         A,@R0           E3         1         MOVX         A,@R1           E4         1         CLR         A           E5         2         MOV         A,RR1           E8         1         MOV         A,R1           EA                                                                                           | D5 | 3        | DJNZ     |                |

| D7         1         XCHD         A,@R1           D8         2         DJNZ         R0,code addr           D9         2         DJNZ         R1,code addr           DA         2         DJNZ         R2,code addr           DB         2         DJNZ         R3,code addr           DC         2         DJNZ         R5,code addr           DD         2         DJNZ         R6,code addr           DF         2         DJNZ         R7,code addr           E0         1         MOVX         A,@PDTTR           E1         2         AJMP         Code addr           E2         1         MOVX         A,@R0           E3         1         MOVX         A,@R0           E3         1         MOV         A,@R1           E4         1         CLR         A           E5         2         MOV         A,@R1           E6         1         MOV         A,RR1           E8         1         MOV         A,R1           E8         1         MOV         A,R3           EC         1         MOV         A,R5           EE         1 <td>D6</td> <td>1</td> <td></td> <td></td>                                                       | D6 | 1        |          |                |