**An Infineon Technologies Company**

# ADM7001 Single Ethernet 10/100M PHY

Datasheet Version 1.07

# Infineon-ADMtek Co Ltd

Information in this document is provided in connection with Infineon-ADMtek Co Ltd products. Infineon-ADMtek Co Ltd may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Infineon-ADMtek Co Ltd reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them

The products may contain design defects or errors know as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request. To obtain latest documentation please contact you local Infineon-ADMtek Co Ltd sales office or visit Infineon-ADMtek Co Ltd's website at

http://www.ADMtek.com.tw

\*Third-party brands and names are the property of their respective owners.

Infineon-ADMtek Co Ltd V1.07

## **About this Manual**

#### **Intended Audience**

#### Structure

This Data sheet contains 6 chapters

Chapter 1. Product Overview

Chapter 2. Interface Description

Chapter 3. Function Description

Chapter 4. Register Description

Chapter 5. Electrical Specification

Chapter 6. Packaging

## **Revision History**

| Date              | Version | Change                                                          |

|-------------------|---------|-----------------------------------------------------------------|

| 05 March 2003     | 1.0     | First release of ADM7001                                        |

| 08 April 2003     | 1.01    | Register Modifications and Pin updates.                         |

| 24 July 2003      | 1.02    | The following sections were updated:                            |

|                   |         | 1.2, 1.3, 2.1, 2.2.1, 2.2.5, 2.2.7, 2.2.8, 2.2.8, 4.1, 4.2.3-4, |

|                   |         | 4.2.11-12, 4.3.4, 4.3.9, 4.3.11, 4.3.12, & 4.3.16               |

| 30 July 2003      | 1.03    | Updated section 6.2                                             |

| 15 September 2003 | 1.04    | Updated Section 2.2.5, 2.2.8, & 4.2.11                          |

| 19 February 2004  | 1.05    | Updated table 5.3                                               |

| 16 April 2004     | 1.06    | Removed TQFP packaging                                          |

| 28 April 2004     | 1.07    | Updated Infineon-Infineon-ADMtek Co Ltd logo                    |

| D : '1 1 ' '      |         |                                                                 |

Detailed revision information is available on request.

# **Customer Support**

Infineon-ADMtek Co Ltd, 2F, No.2, Li-Hsin Rd., Science-based Industrial Park, Hsinchu, 300, Taiwan, R.O.C.

#### **Sales Information**

Tel + 886-3-5788879 Fax + 886-3-5788871

# **Table of Contents**

| Chapter 1 Pr                                                                                                                         | oduct Overview                                                                                                                                                                                                                                                                                                                                                                                   | 1-1                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 1.1 Ove                                                                                                                              | rview                                                                                                                                                                                                                                                                                                                                                                                            | 1-1                                                                         |

| 1.1.1                                                                                                                                | Product Order Information                                                                                                                                                                                                                                                                                                                                                                        | 1-1                                                                         |

| 1.2 Feat                                                                                                                             | tures                                                                                                                                                                                                                                                                                                                                                                                            | 1-1                                                                         |

| 1.3 Bloo                                                                                                                             | ck Diagram                                                                                                                                                                                                                                                                                                                                                                                       | 1-2                                                                         |

| 1.4 Abb                                                                                                                              | previations and Acronyms                                                                                                                                                                                                                                                                                                                                                                         | 1-3                                                                         |

| 1.5 Con                                                                                                                              | ventions                                                                                                                                                                                                                                                                                                                                                                                         | 1-4                                                                         |

| 1.5.1                                                                                                                                | Data Lengths                                                                                                                                                                                                                                                                                                                                                                                     | 1-4                                                                         |

| 1.5.2                                                                                                                                | Register Type Descriptions                                                                                                                                                                                                                                                                                                                                                                       | 1-4                                                                         |

| 1.5.3                                                                                                                                | Pin Type Descriptions                                                                                                                                                                                                                                                                                                                                                                            | 1-5                                                                         |

| -                                                                                                                                    | terface Description                                                                                                                                                                                                                                                                                                                                                                              |                                                                             |

|                                                                                                                                      | Diagram                                                                                                                                                                                                                                                                                                                                                                                          |                                                                             |

| 2.2 Pin                                                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                      |                                                                             |

| 2.2.1                                                                                                                                | Twisted Pair Interface, 5 pins                                                                                                                                                                                                                                                                                                                                                                   | 2-2                                                                         |

| 2.2.2                                                                                                                                | Digital Power/Ground, 7 pins                                                                                                                                                                                                                                                                                                                                                                     |                                                                             |

| 2.2.3                                                                                                                                | Ground and Power, 5 pins                                                                                                                                                                                                                                                                                                                                                                         | 2-2                                                                         |

| 2.2.4                                                                                                                                | Clock Input, 2 pins                                                                                                                                                                                                                                                                                                                                                                              | 2-3                                                                         |

| 2.2.5                                                                                                                                | MII/RMII/GPSI Interface, 16 pins                                                                                                                                                                                                                                                                                                                                                                 | 2-3                                                                         |

| 2.2.6                                                                                                                                | Reset Pin                                                                                                                                                                                                                                                                                                                                                                                        | 2-6                                                                         |

| 2.2.7                                                                                                                                | Control Signals, 6 pins                                                                                                                                                                                                                                                                                                                                                                          | 2-6                                                                         |

| 2.2.8                                                                                                                                | LED Interface, 4 pins                                                                                                                                                                                                                                                                                                                                                                            | 2-7                                                                         |

| 2.2.9                                                                                                                                | Regulator Control                                                                                                                                                                                                                                                                                                                                                                                | 2-8                                                                         |

| CI / 2.E                                                                                                                             | =                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |

| Chapter 3 Fu                                                                                                                         | inction Description                                                                                                                                                                                                                                                                                                                                                                              | 3-1                                                                         |

| -                                                                                                                                    | 100M PHY Block                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |

| -                                                                                                                                    | •                                                                                                                                                                                                                                                                                                                                                                                                | 3-1                                                                         |

| 3.1 10/1                                                                                                                             | 100M PHY Block                                                                                                                                                                                                                                                                                                                                                                                   | 3-1<br>3-1                                                                  |

| 3.1 10/1<br>3.1.1                                                                                                                    | 100M PHY Block                                                                                                                                                                                                                                                                                                                                                                                   | 3-1<br>3-1<br>3-2                                                           |

| 3.1 10/1<br>3.1.1<br>3.1.2                                                                                                           | 100M PHY Block<br>100Base-X Module<br>100Base-TX Receiver                                                                                                                                                                                                                                                                                                                                        | 3-1<br>3-1<br>3-2<br>3-7                                                    |

| 3.1 10/1<br>3.1.1<br>3.1.2<br>3.1.3                                                                                                  | 100M PHY Block<br>100Base-X Module<br>100Base-TX Receiver<br>100Base-TX Transmitter                                                                                                                                                                                                                                                                                                              | 3-1<br>3-1<br>3-2<br>3-7                                                    |

| 3.1 10/1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                                                                         | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-TX Transmitter 100Base-FX Receiver 100Base-FX Transmitter                                                                                                                                                                                                                                                                            | 3-1<br>3-1<br>3-2<br>3-7<br>3-7                                             |

| 3.1 10/1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5                                                                                | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-TX Transmitter 100Base-FX Receiver                                                                                                                                                                                                                                                                                                   | 3-1<br>3-2<br>3-7<br>3-7<br>3-7                                             |

| 3.1 10/1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6                                                                       | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-TX Transmitter 100Base-FX Receiver 100Base-FX Transmitter 100Base-FX Transmitter 10Base-T Module Operation Modes                                                                                                                                                                                                                     | 3-1<br>3-2<br>3-7<br>3-7<br>3-7<br>3-7<br>3-7                               |

| 3.1 10/1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7                                                              | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-TX Transmitter 100Base-FX Receiver 100Base-FX Transmitter 100Base-FX Transmitter                                                                                                                                                                                                                                                     | 3-1<br>3-2<br>3-7<br>3-7<br>3-7<br>3-7<br>3-7<br>3-8                        |

| 3.1 10/1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8                                                     | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-TX Transmitter 100Base-FX Receiver 100Base-FX Transmitter 10Base-T Module Operation Modes Manchester Encoder/Decoder Transmit Driver and Receiver                                                                                                                                                                                    | 3-1<br>3-2<br>3-7<br>3-7<br>3-7<br>3-7<br>3-8<br>3-8                        |

| 3.1 10/1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>3.1.9                                            | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-TX Transmitter 100Base-FX Receiver 100Base-FX Transmitter 100Base-FX Transmitter 10Base-T Module Operation Modes Manchester Encoder/Decoder                                                                                                                                                                                          | 3-1<br>3-2<br>3-7<br>3-7<br>3-7<br>3-7<br>3-8<br>3-8                        |

| 3.1 10/1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>3.1.9<br>3.1.10                                  | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-TX Transmitter 100Base-FX Receiver 100Base-FX Transmitter 10Base-T Module Operation Modes Manchester Encoder/Decoder Transmit Driver and Receiver Smart Squelch Carrier Sense                                                                                                                                                        | 3-1<br>3-2<br>3-7<br>3-7<br>3-7<br>3-7<br>3-8<br>3-8<br>3-8                 |

| 3.1 10/1 3.1.1 3.1.2 3.1.3 3.1.4 3.1.5 3.1.6 3.1.7 3.1.8 3.1.9 3.1.10 3.1.11                                                         | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-TX Transmitter 100Base-FX Receiver 100Base-FX Transmitter 10Base-T Module Operation Modes Manchester Encoder/Decoder Transmit Driver and Receiver Smart Squelch Carrier Sense Collision Detection                                                                                                                                    | 3-1<br>3-2<br>3-7<br>3-7<br>3-7<br>3-7<br>3-8<br>3-8<br>3-8<br>3-8<br>3-8   |

| 3.1 10/1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>3.1.9<br>3.1.10<br>3.1.11<br>3.1.12              | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-TX Transmitter 100Base-FX Receiver 100Base-FX Transmitter 10Base-T Module Operation Modes Manchester Encoder/Decoder Transmit Driver and Receiver Smart Squelch Carrier Sense Collision Detection Jabber Function                                                                                                                    | 3-1 3-1 3-1 3-2 3-7 3-7 3-7 3-7 3-7 3-8 3-8 3-8 3-9 3-9                     |

| 3.1 10/1 3.1.1 3.1.2 3.1.3 3.1.4 3.1.5 3.1.6 3.1.7 3.1.8 3.1.9 3.1.10 3.1.11 3.1.12 3.1.13                                           | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-TX Transmitter 100Base-FX Receiver 100Base-FX Transmitter 10Base-T Module Operation Modes Manchester Encoder/Decoder Transmit Driver and Receiver Smart Squelch Carrier Sense Collision Detection Jabber Function                                                                                                                    | 3-1 3-1 3-1 3-1 3-7 3-7 3-7 3-7 3-8 3-8 3-8 3-9 3-9 3-9 3-10                |

| 3.1 10/1 3.1.1 3.1.2 3.1.3 3.1.4 3.1.5 3.1.6 3.1.7 3.1.8 3.1.9 3.1.10 3.1.11 3.1.12 3.1.13 3.1.14                                    | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-TX Transmitter 100Base-FX Receiver 100Base-FX Transmitter 10Base-T Module Operation Modes Manchester Encoder/Decoder Transmit Driver and Receiver Smart Squelch Carrier Sense Collision Detection Jabber Function Link Test Function Automatic Link Polarity Detection                                                               | 3-1 3-1 3-1 3-1 3-7 3-7 3-7 3-7 3-7 3-8 3-8 3-8 3-9 3-9 3-10 3-10           |

| 3.1 10/1 3.1.1 3.1.2 3.1.3 3.1.4 3.1.5 3.1.6 3.1.7 3.1.8 3.1.9 3.1.10 3.1.11 3.1.12 3.1.13 3.1.14 3.1.15                             | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-TX Transmitter 100Base-FX Receiver 100Base-FX Transmitter 10Base-T Module Operation Modes Manchester Encoder/Decoder Transmit Driver and Receiver Smart Squelch Carrier Sense Collision Detection Jabber Function Link Test Function Automatic Link Polarity Detection Clock Synthesizer                                             | 3-1 3-1 3-1 3-1 3-7 3-7 3-7 3-7 3-7 3-8 3-8 3-9 3-9 3-10 3-10               |

| 3.1 10/1 3.1.1 3.1.2 3.1.3 3.1.4 3.1.5 3.1.6 3.1.7 3.1.8 3.1.9 3.1.10 3.1.11 3.1.12 3.1.13 3.1.14 3.1.15 3.1.16                      | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-TX Transmitter 100Base-FX Receiver 100Base-FX Transmitter 10Base-T Module Operation Modes Manchester Encoder/Decoder Transmit Driver and Receiver Smart Squelch Carrier Sense Collision Detection Jabber Function Link Test Function Automatic Link Polarity Detection Clock Synthesizer Auto Negotiation                            | 3-1 3-1 3-1 3-1 3-7 3-7 3-7 3-7 3-8 3-8 3-8 3-9 3-10 3-10 3-10              |

| 3.1 10/1 3.1.1 3.1.2 3.1.3 3.1.4 3.1.5 3.1.6 3.1.7 3.1.8 3.1.9 3.1.10 3.1.11 3.1.12 3.1.13 3.1.14 3.1.15 3.1.15 3.1.16 3.1.17 3.1.18 | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-FX Transmitter 100Base-FX Transmitter 100Base-FX Transmitter 10Base-T Module Operation Modes Manchester Encoder/Decoder Transmit Driver and Receiver Smart Squelch Carrier Sense Collision Detection Jabber Function Link Test Function Automatic Link Polarity Detection Clock Synthesizer Auto Negotiation and Speed Configuration | 3-1 3-1 3-1 3-1 3-7 3-7 3-7 3-7 3-7 3-8 3-8 3-8 3-9 3-9 3-10 3-10 3-10 3-10 |

| 3.1 10/1 3.1.1 3.1.2 3.1.3 3.1.4 3.1.5 3.1.6 3.1.7 3.1.8 3.1.9 3.1.10 3.1.11 3.1.12 3.1.13 3.1.14 3.1.15 3.1.15 3.1.16 3.1.17 3.1.18 | 100M PHY Block 100Base-X Module 100Base-TX Receiver 100Base-FX Transmitter 100Base-FX Transmitter 100Base-FX Transmitter 10Base-T Module Operation Modes Manchester Encoder/Decoder Transmit Driver and Receiver Smart Squelch Carrier Sense Collision Detection Jabber Function Link Test Function Automatic Link Polarity Detection Clock Synthesizer Auto Negotiation and Speed Configuration | 3-1 3-1 3-1 3-1 3-2 3-7 3-7 3-7 3-7 3-7 3-8 3-8 3-9 3-10 3-10 3-11 3-11     |

# Infineon-ADMtek Co Ltd

| 3.2.3        | Receive Path for 10M                                | 3-13 |

|--------------|-----------------------------------------------------|------|

| 3.2.4        | Transmit Path for 100M                              |      |

| 3.2.5        | Transmit Path for 10M                               | 3-14 |

| 3.2.6        | Media Independent Interface (MII)                   | 3-15 |

| 3.2.7        | Receive Path for MII                                | 3-15 |

| 3.2.8        | Transmit Path For MII                               | 3-17 |

| 3.2.9        | General Purpose Serial Interface (GPSI)             | 3-17 |

| 3.2.10       | Receive Path for GPSI                               |      |

| 3.2.11       | Transmit Path for GPSI                              | 3-18 |

| 3.3 LEI      | D Display                                           | 3-18 |

|              | nagement Register Access                            |      |

| 3.4.1        | Preamble Suppression                                |      |

| 3.4.2        | Reset Operation                                     | 3-20 |

| 3.5 Pov      | ver Management                                      | 3-21 |

| 3.6 Vol      | tage Regulator                                      | 3-22 |

| Chapter 4 Re | egister Description                                 | 4-1  |

| 4.1 Reg      | gister Mapping                                      | 4-1  |

| 4.2 Reg      | gister Bit Mapping                                  | 4-2  |

| 4.2.1        | Register #0h Control Register                       | 4-2  |

| 4.2.2        | Register #1h – Status Register                      |      |

| 4.2.3        | Register #2h – PHY ID Register (002E)               | 4-2  |

| 4.2.4        | Register #3h – PHY ID Register (CC62)               |      |

| 4.2.5        | Register #4h – Advertisement Register               |      |

| 4.2.6        | Register #5h – Link Partner Ability Register        |      |

| 4.2.7        | Register #6h – Auto Negotiation Expansion Register  |      |

| 4.2.8        | Register #7h – # Fh Reserved                        |      |

| 4.2.9        | Register #10h – PHY Configuration Register          |      |

| 4.2.10       | Register #11h – 10M Configuration Register          |      |

| 4.2.11       | Register #12h – 100M Configuration Register         |      |

| 4.2.12       | Register #13h – LED Configuration Register          |      |

| 4.2.13       | Register #14h – Interrupt Enable Register           |      |

| 4.2.14       | Register #16h – PHY Generic Status Register         |      |

| 4.2.15       | Register #17h – PHY Specific Status Register        |      |

| 4.2.16       | Register #18h – Recommend Value Storage Register    |      |

| 4.2.17       | Register #19h – Interrupt Status Register           |      |

| 4.2.18       | Register #1dh – Receive Error Counter               |      |

| 4.2.19       | Register #1fh – Chip ID (8125)                      |      |

| 4.3 Reg      | gister Description                                  |      |

| 4.3.1        | Control (Register 0h)                               |      |

| 4.3.2        | Status (Register 1h)                                |      |

| 4.3.3        | PHY Identifier Register (Register 2h)               |      |

| 4.3.4        | PHY Identifier Register (Register 3h)               |      |

| 4.3.5        | Advertisement (Register 4h)                         |      |

| 4.3.6        | Auto Negotiation Link Partner Ability (Register 5h) |      |

| 4.3.7        | Auto Negotiation Expansion Register (Register 6h)   |      |

| 4.3.8        | Register Reserved (Register 7h-Fh)                  |      |

|              |                                                     |      |

ADM7001 ii

## Infineon-ADMtek Co Ltd

| 4.3.9       | Generic PHY Configuration Register (Register 10h)    | 4-11 |

|-------------|------------------------------------------------------|------|

| 4.3.10      | PHY 10M Module Configuration Register (Register 11h) | 4-12 |

| 4.3.11      | PHY 100M Module Control Register (Register 12h)      |      |

| 4.3.12      | LED Configuration Register (Register 13h)            |      |

| 4.3.13      | Interrupt Enable Register (Register 14h)             | 4-15 |

| 4.3.14      | PHY Generic Status Register (Register 16h)           |      |

| 4.3.15      | PHY Specific Status Register (Register 17h)          | 4-17 |

| 4.3.16      | PHY Recommend Value Status Register (Register 18h)   |      |

| 4.3.17      | Interrupt Status Register (Register 19h)             |      |

| 4.3.18      | Receive Error Counter Register (Register 1Dh)        |      |

| 4.3.19      | Chip ID Register (Register 1Fh)                      |      |

| Chapter 5 E | lectrical Specification                              |      |

|             | Characterization                                     |      |

| 5.1.1       | Absolute Maximum Rating                              |      |

| 5.1.2       | Recommended Operating Conditions                     | 5-1  |

| 5.1.3       | DC Electrical Characteristics for 2.5V Operation     |      |

| 5.2 AC      | C Characterization.                                  |      |

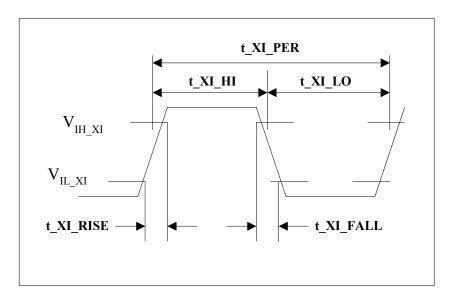

| 5.2.1       | XI/OSCI (Crystal/Oscillator) Timing (In MII Mode)    | 5-2  |

| 5.3 RN      | AII Timing                                           |      |

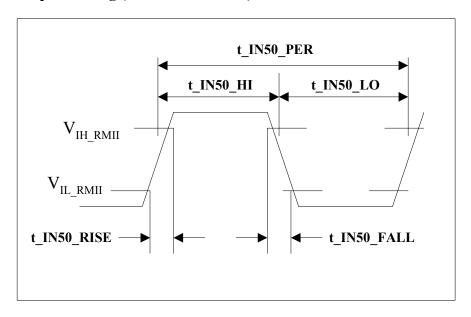

| 5.3.1       | REFCLK Input Timing (XI in RMII Mode)                | 5-3  |

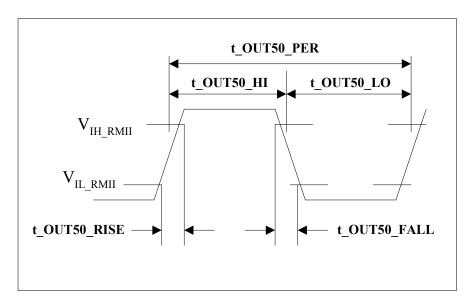

| 5.3.2       | REFCLK Output Timing (CLKO50 in RMII Mode)           |      |

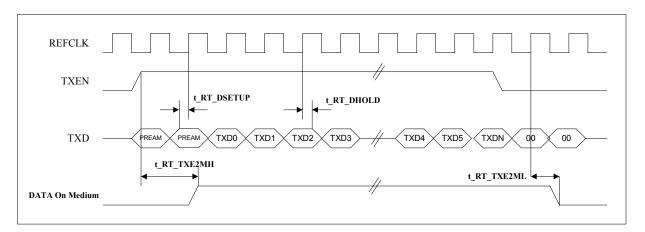

| 5.3.3       | RMII Transmit Timing                                 |      |

| 5.3.4       | RMII Receive Timing                                  | 5-6  |

| 5.4 MI      | I Timing                                             | 5-7  |

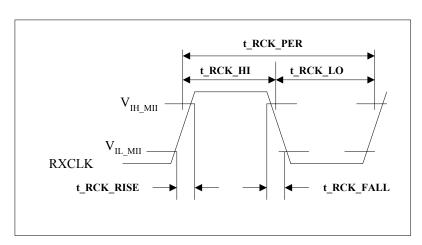

| 5.4.1       | RXCLK Clock Timing                                   | 5-7  |

| 5.4.2       | MII Receive Timing                                   | 5-8  |

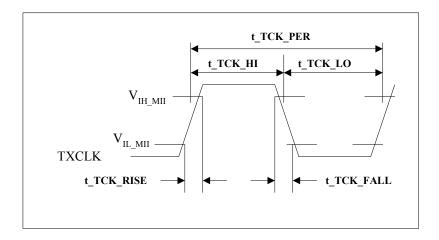

| 5.4.3       | TXCLK Output Timing                                  | 5-9  |

| 5.4.4       | MII Transmit Timing                                  | 5-10 |

| 5.5 GF      | SI Timing                                            | 5-11 |

| 5.5.1       | GPSI Receive Timing                                  | 5-11 |

| 5.5.2       | GPSI Transmit Timing                                 | 5-12 |

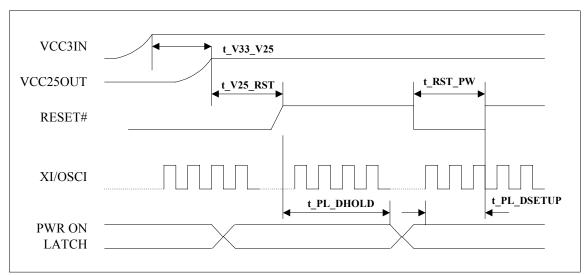

|             | wer On Configuration Timing                          |      |

|             | ackaging                                             |      |

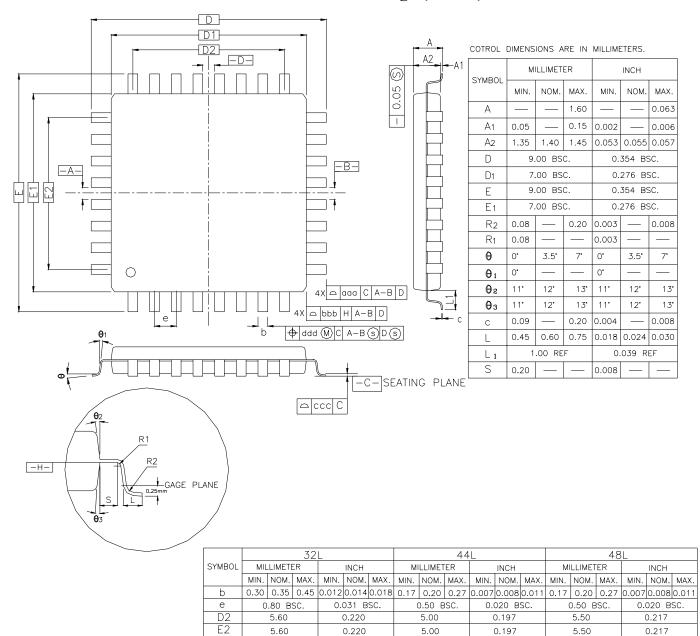

| 6.1 AI      | DM7001 Low Profile Quad Flat Package (LQFP) 48 Pin   | 6-1  |

|             |                                                      |      |

ADM7001 iii

Infineon-ADMtek Co Ltd V1.07

# **List of Figures**

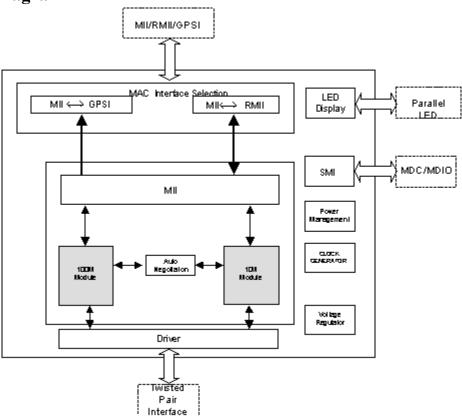

| Figure 1-1 ADM7001 Block Diagram                           | 1-2  |

|------------------------------------------------------------|------|

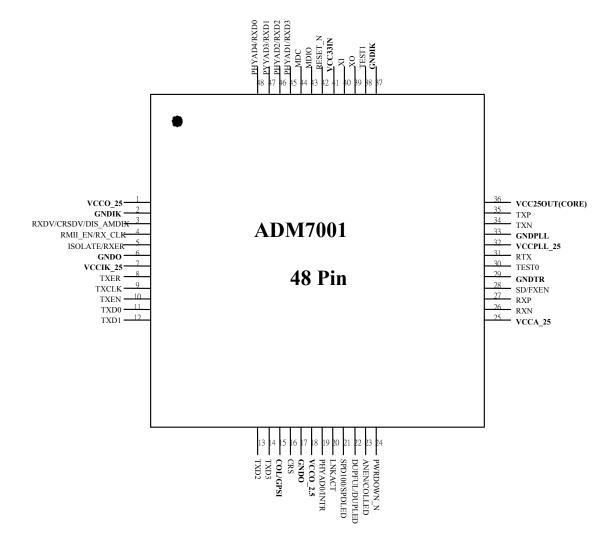

| Figure 2-1 ADM7001 48 Pin Diagram                          |      |

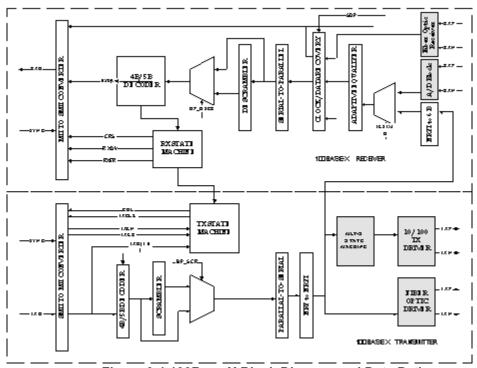

| Figure 3-1 100Base-X Block Diagram and Data Path           | 3-2  |

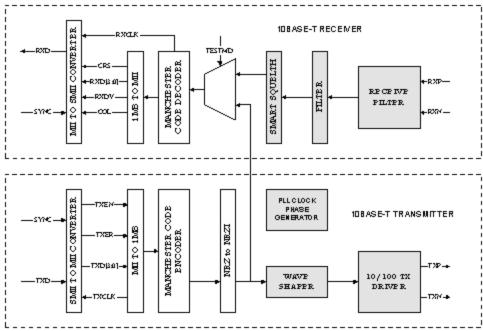

| Figure 3-2 10Base-T Block Diagram and Data Path            | 3-9  |

| Figure 3-3 RMII Signal Diagram                             | 3-12 |

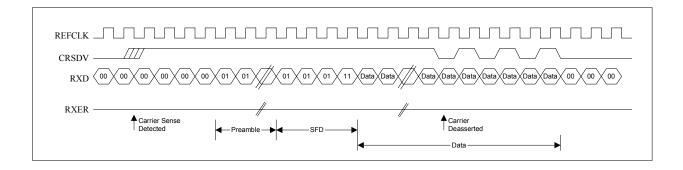

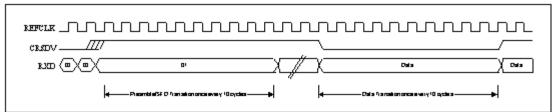

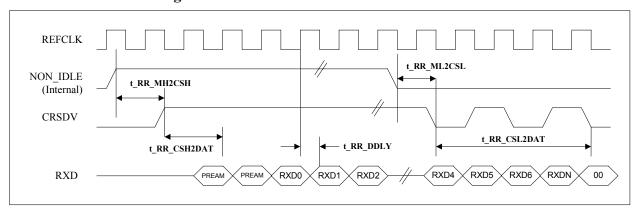

| Figure 3-4 RMII Reception Without Error                    | 3-13 |

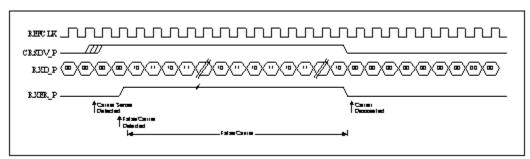

| Figure 3-5 RMII Reception with False Carrier (100M Only)   | 3-13 |

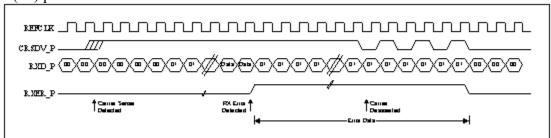

| Figure 3-6 RMII Reception with Symbol Error                | 3-13 |

| Figure 3-7 10M RMII Receive Diagram                        | 3-13 |

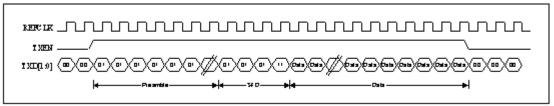

| Figure 3-8 100M RMII Transmit Diagram                      | 3-14 |

| Figure 3-9 10M RMII Transmit Diagram                       | 3-14 |

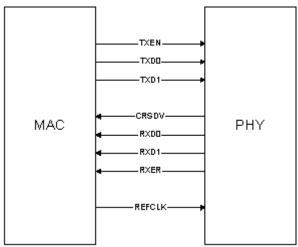

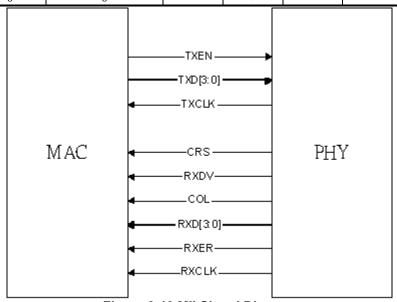

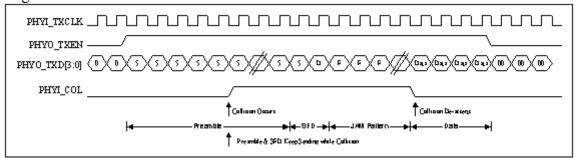

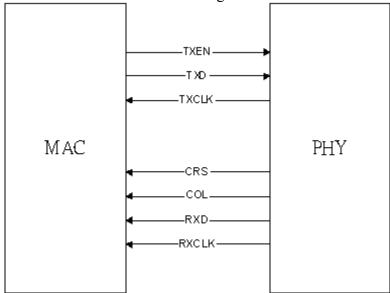

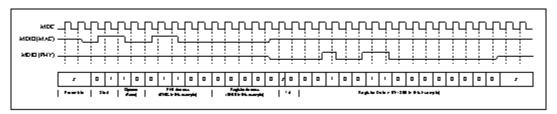

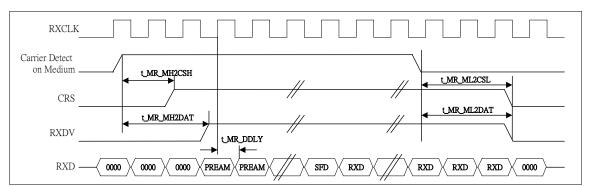

| Figure 3-10 MII Signal Diagram                             | 3-15 |

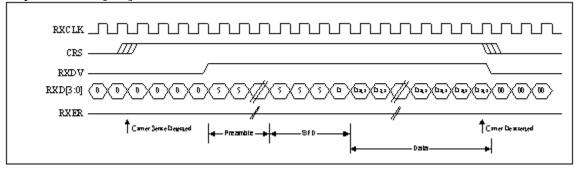

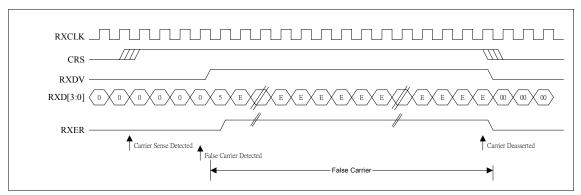

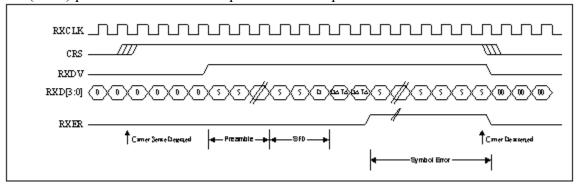

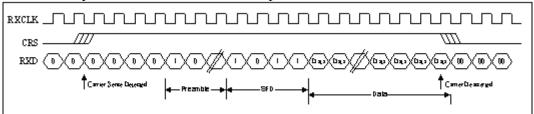

| Figure 3-11 MII Receive Without Error                      | 3-16 |

| Figure 3-12 MII Receive With False Carrier                 | 3-16 |

| Figure 3-13 MII Receive With Symbol Error (100M Only)      | 3-16 |

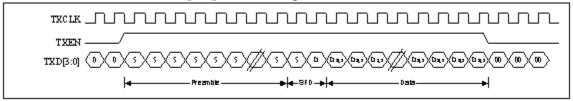

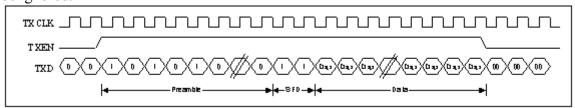

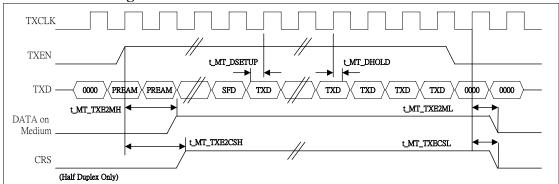

| Figure 3-14 MII Transmission                               | 3-17 |

| Figure 3-15 MII Transmit with Collision (Half Duplex Only) | 3-17 |

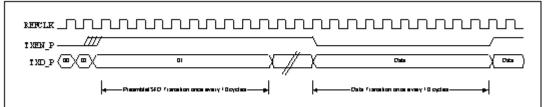

| Figure 3-16 GPSI Signal Diagram                            | 3-17 |

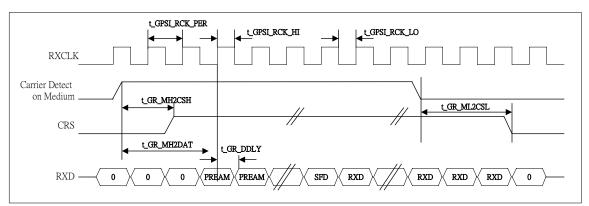

| Figure 3-17 GPSI Receive Diagram                           | 3-18 |

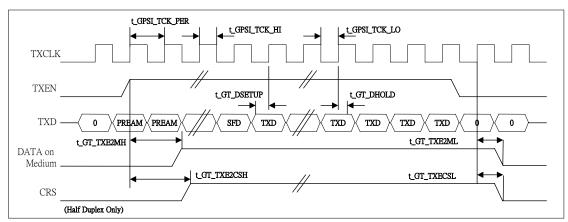

| Figure 3-18 GPSI Transmit Diagram                          | 3-18 |

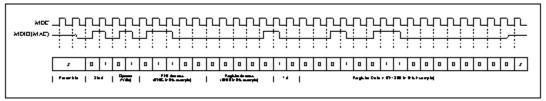

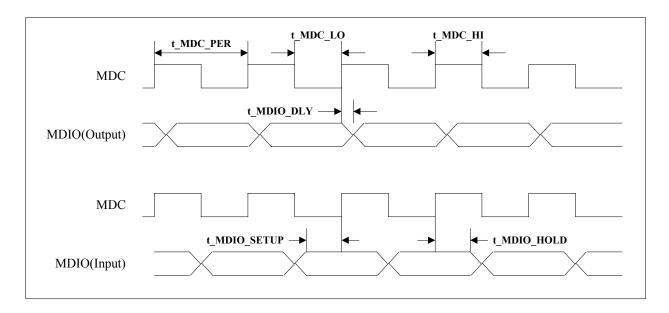

| Figure 3-19 SMI Read Operation                             | 3-20 |

| Figure 3-20 SMI Write Operation                            | 3-21 |

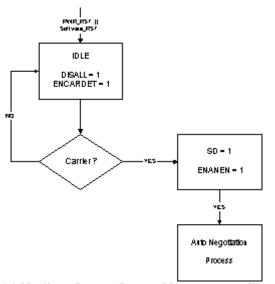

| Figure 3-21 Medium Detect Power Management Flow Chart      | 3-22 |

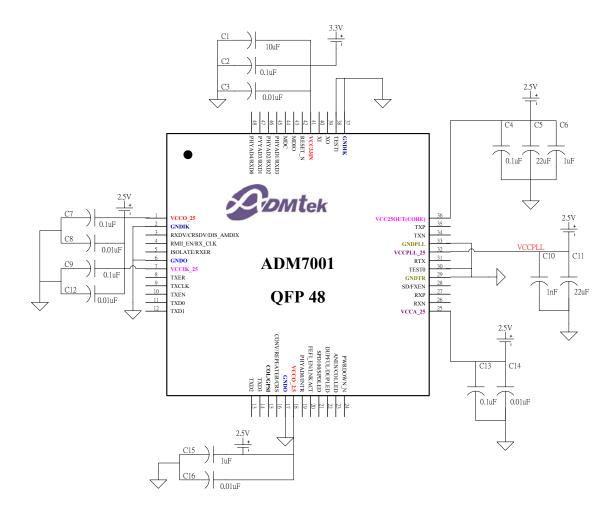

| Figure 3-22 Power and Ground Filtering                     | 3-23 |

| Figure 5-1 Crystal/Oscillator Timing                       | 5-2  |

| Figure 5-2 REFCLK Input Timing                             | 5-3  |

| Figure 5-3 REFCLK Output Timing                            | 5-4  |

| Figure 5-4 RMII Transmit Timing.                           | 5-5  |

| Figure 5-5 RMII Receive Timing                             | 5-6  |

ADM7001 iv

Infineon-ADMtek Co Ltd V1.07

# **List of Tables**

| Table 3-1 Look-up Table for translating 5B Symbols into 4B Nibbles | 3-5  |

|--------------------------------------------------------------------|------|

| Table 3-2 Channel Configuration                                    | 3-15 |

| Table 3-3 Speed LED Display                                        |      |

| Table 3-4 Duplex LED Display                                       |      |

| Table 3-5 Activity/Link LED Display                                |      |

| Table 3-6 Cable Distance LED Display                               | 3-19 |

| Table 5-1 Electrical Absolute Maximum Rating                       | 5-1  |

| Table 5-2 Recommended Operating Conditions                         | 5-1  |

| Table 5-3 DC Electrical Characteristics for 3.3V Operation         | 5-1  |

| Table 5-4 Crystal/Oscillator Timing                                | 5-2  |

| Table 5-5 REFCLK Input Timing                                      | 5-3  |

| Table 5-6 REFCLK Output Timing                                     | 5-4  |

| Table 5-7 RMII Transmit Timing                                     | 5-5  |

| Table 5-8 RMII Receive Timing                                      | 5-6  |

|                                                                    |      |

ADM7001 v

# **Chapter 1 Product Overview**

#### 1.1 Overview

ADM7001, is a single chip one port 10/100M PHY, designed for today's low cost and low power dual speed application. It supports auto sensing 10/100 Mbps ports with on-chip clock recovery and base line wander correction including integrated MLT-3 functionality for 100 Mbps operation and also supports Manchester Code Converter with on chip clock recovery circuitry for 10 Mbps functionality. Meanwhile, it provides Medium Independent Interface (MII), Reduced Medium Independent Interface (RMII) and General Purpose Serial Interface (GPSI), three different interfaces different application.

For today's IA (Information Application), ADM7001 supports "Auto Cross Over Detection" function to eliminate the technical barrier between networking and end user. With the aid of this auto cross over detection function, Plug-n-Play feature can be easily applied to IA relative products.

The major design target for ADM7001 is to reduce the power consumption and system radiation for the whole system. With the aid of this low power consumption and low radiation chip, the fan and on-system power supply can be removed to save the total manufacture cost and make SOHO application achievable.

#### 1.1.1 Product Order Information

The ADM7001 comes in two packaging formats as follows:

6.1 ADM7001 Low Profile Quad Flat Package (LOFP)

#### 1.2 Features

- IEEE 802.3 compatible 10BASE-T and 100BASE-T physical layer interface and ANSI X3.263 TP-PMD compatible transceiver

- Single chip, integrated physical layer and transceivers for 10BASE-T and 100BASE-TX function.

- Medium Independent Interface (MII), Reduced MII (RMII) and General Purpose Serial Interface (GPSI) for high port count switch

- Built-in 10Mbit transmit filter

- 10Mbit PLL, exceeding tolerances for both preamble and data jitter

- 100Mbit PLL, combined with the digital adaptive equalizer and performance up to 120 meters for UTP 5.

- 125MHz Clock Generator and Timing Recovery

- Integrated Base Line Wander Correction

- Carrier Integrity Monitor function supported

- Support FEFI when Auto Negotiation disabled

- Support Auto MDIX function for Plug-and-Play

• IEEE 802.3u Clause 28 compliant auto negotiation for full 10 Mbps and 100 Mbps control.

- Supports programmable LED For different Switch Application and Power On LED Self Test

- Supports Cable Length Indication both in MII Register and LED (Programmable)

- Supports PECL interface for fiber connection

- Supports TP vs. FX Medium Converter function

- Supports Fault Propagation function for medium converter

- Supports 10K Bytes Jumbo Packet with Clock Skew 150 ppm

- Built-in Clock Generator and Power On Reset Signal to save system cost

- 48 LQFP without regulator

- Support Power saving function

- Support Parallel LED output

#### 1.3 Block Diagram

Figure 1-1 ADM7001 Block Diagram

### 1.4 Abbreviations and Acronyms

ANSI American National Standards Institute

BER Bit Error Rate

COL Collision

CRS Carrier Sense

CRSDV Carrier Sense and Data Valid

CTL Crystal

DSP Digital Signal Processor

DUPCOL Duplex and Collision

ESD End of Stream Delimiter

FEFI Far End Fault Indication

FIFO First In First Out FLP Fast Link Pulse

FX Fiber

GPSI General Purpose Serial Interface

TP Twisted Pair TX Transmit RX Receive

IA Information Application

LFSR Linear Feedback Shifter Register

LNKACT Link and Activity

LQFP Low Profile Quad Flat Package

LVTTL Low Voltage TTL Level MAC Media Access Controller

MD Medium Detect

MDC Management Data Clock

MDIO Management Data Input/Output

NRZ None Return to Zero

NRZI None Return to Zero Inverter

OP Operation Code

PCS Physical Coding Sub-layer PECL Pseudo Emitter Couple Logic

PHY Physical Layer PHYADDR PHY Address

PMA Physical Medium Attachment PMD Physical Medium Dependent

PNP A type of Transistor

PQFP Plastic Quad Flat Pack

REFCLK Reference Clock

RF Remote Fault

MII Media Independent Interface

RMII Reduced Media Independent Interface

RXCLK Receive Clock

RXD Receive Data

RXDV Receive Data Valid

RXER Receive Data Error

RXN Receive Negative (Analog receive differential signal)

RXP Receive Positive (Analog receive differential signal)

SDN Signal Detect Negative (Fiber signal detect)

SDP Signal Detect Positive (Fiber signal detect)

SELFX Select Fiber

SMI Serial Management Interface SOHO Small Office and Home Office

SQE Signal Quality Error SSD Start of Stream Delimiter

GPSI General Purpose Serial Interface

TA Turn Around

TDR Time Domain Reflectometry

TP-PMD Twisted Pair Physical Medium Dependent

TTL Transistor Transistor Logic

TXCLK MII Transmission Clock

TXD Transmission Data

TXEN Transmission Enable

TXER Transmission Error

TXN Transmission Negative

TXP Transmission Positive

/J/K 5B signal to detect the start of a frame /T/R 5B signal to detect the end of a frame

PHYDIG Internal Digital Block to Handle PHY relative functions

TRXANA Internal Analog Block contains both TX and RX Function

#### 1.5 Conventions

#### 1.5.1 Data Lengths

| qword  | 64-bits |

|--------|---------|

| dword  | 32-bits |

| word   | 16-bits |

| byte   | 8 bits  |

| nibble | 4 bits  |

#### 1.5.2 Register Type Descriptions

| Register Type | Description |

|---------------|-------------|

| RO            | Read Only   |

R/W Read and Write capable

SC Self-clearing

LL Latching low, unlatch on read LH Latching high, unlatch on read

COR Clear On Read

# **1.5.3 Pin Type Descriptions** *Pin Type*

Pin Type Description

I: Input

O: Output

I/O: Bi-directional

OD: Open drain

SCHE: Schmitt Trigger

PU: Pull Up PD: Pull Down

# **Chapter 2 Interface Description**

# 2.1 Pin Diagram

Figure 2-1 ADM7001 48 Pin Diagram

# 2.2 Pin Description

#### Note:

For those pins, which have multiple functions, pin name is separated by slash ("/").

If not specified, all signals are default to digital signals.

Please refer to section '1.5.3 Pin Type Descriptions' for an explanation of pin abbreviations.

2.2.1 Twisted Pair Interface, 5 pins

| .2.1 I Wisteu | .1 I wisted I all Interface, 5 pins |           |                                                                                                                                                                                                                             |  |  |

|---------------|-------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin #         | Pin Name                            | Type      | Description                                                                                                                                                                                                                 |  |  |

| 35            | TXP                                 | I/O,      | Twisted Pair Transmit Output Positive.                                                                                                                                                                                      |  |  |

|               |                                     | Analog    | ·                                                                                                                                                                                                                           |  |  |

| 34            | TXN                                 | I/O,      | Twisted Pair Transmit Output Negative.                                                                                                                                                                                      |  |  |

|               |                                     | Analog    |                                                                                                                                                                                                                             |  |  |

| 27            | RXP                                 | I/O,      | Twisted Pair Receive Input Positive.                                                                                                                                                                                        |  |  |

|               |                                     | Analog    |                                                                                                                                                                                                                             |  |  |

| 26            | RXN                                 | I/O,      | Twisted Pair Receive Input Negative.                                                                                                                                                                                        |  |  |

|               |                                     | Analog    |                                                                                                                                                                                                                             |  |  |

| 28            | Power On<br>Setting<br>FXEN         | I, Analog | Fiber Enable. Value on this pin will be latched by ADM7001 during power on reset as fiber select signal. 0: Twisted Pair Mode 1: Fiber Optic Mode                                                                           |  |  |

|               | Fiber Mode<br>SDP                   |           | 100BASE-FX Signal Detect. After power on reset stage, this pin acts as signal detect signal from external fiber optic transceiver in case FXEN is detected as high during power on reset.  0: No signal detected  1: Signal |  |  |

2.2.2 Digital Power/Ground, 7 pins

|   | Pin#  | Pin Name | Type    | Pin Description                     |

|---|-------|----------|---------|-------------------------------------|

|   | 6, 17 | GNDO     | Digital | Ground used by 3.3V I/O.            |

|   |       |          | Ground  |                                     |

|   | 2, 37 | GNDIK    | Digital | Ground used by Core.                |

|   |       |          | Ground  |                                     |

|   | 1, 18 | VCCO_25  | Digital | 2.5V Power Used by Digital I/O Pad. |

|   |       |          | Power   |                                     |

|   | 7     | VCCIK_25 | Digital | 2.5V Power used by Core             |

| L |       |          | Power   |                                     |

2.2.3 Ground and Power, 5 pins

| 2.2.5 | .5 Ground and rower, 5 pins |          |        |                                                               |

|-------|-----------------------------|----------|--------|---------------------------------------------------------------|

|       | Pin #                       | Pin Name | Type   | Description                                                   |

|       | 41                          | VCC3IN   | Analog | 3.3V Power input to ADM7001 and used by built-in 3.3V to 2.5V |

|       |                             |          | Power  | regulator.                                                    |

|       | 36                          | VCC25OUT | Analog | 2.5V Power output by ADM7001. Maximum Supply current          |

|       |                             |          | Power  | from this pin is 200 mA.                                      |

|       | 29                          | GNDTR    | Analog | Analog Ground Pad                                             |

|       |                             |          | Ground |                                                               |

|       | 25                          | VCCA_25  | Analog | Analog 2.5V Power                                             |

|       |                             |          | Power  |                                                               |

| 32 | VCCPLL_25 | Analog | Analog 2.5V Power used by Clock Generator module |

|----|-----------|--------|--------------------------------------------------|

|    |           | Power  |                                                  |

2.2.4 Clock Input, 2 pins

| Pin # | Pin Name | Type   | Pin Description                                                |

|-------|----------|--------|----------------------------------------------------------------|

| 40    | XI/OSCI  | I, CTL | Crystal/Oscillator input. 25M Crystal/Oscillator Input in MII  |

|       |          |        | mode and 50M Clock input in RMII mode (Also called REFCLK      |

|       |          |        | in RMII Mode)                                                  |

| 39    | XO       | O, CTL | Crystal output. When 25M Oscillator is used, this pin should   |

|       |          |        | left unconnected. Capable of driving one XI input for multiple |

|       |          |        | port application.                                              |

2.2.5 MII/RMII/GPSI Interface, 16 pins

| Pin #          | Pin Name              | Type             | Pin Description                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|-----------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9              | MII Mode<br>TXCLK     | O,<br>16mA       | MII Transmit Clock. 25M Clock output in 100BASE-X mode and 2.5M Clock output for 10BASE-T mode. This clock is continuously driven output and generated from XI. Before Speed is recognized, this pin drives out continuous 25M clock.                                                                                                                                                                      |

|                | RMII Mode<br>TXCLK    |                  | N/A.                                                                                                                                                                                                                                                                                                                                                                                                       |

|                | GPSI Mode<br>TXCLK    |                  | GPSI Transmit Clock. 10M Clock output in 10BASE-T mode.                                                                                                                                                                                                                                                                                                                                                    |

| 14, 13, 12, 11 | MII Mode<br>TXD[3:0]  | I,<br>TTL,<br>PD | <b>Transmit Data.</b> Nibble-wide transmit data stream in MII mode. These four bits are synchronous to the rising edge of TXCLK and TXD[3] is the most significant bit.                                                                                                                                                                                                                                    |

|                | RMII Mode<br>TXD[1:0] |                  | <b>Di-bits Transmit Data.</b> TXD0 and TXD1 for the di-bits that are transmitted and are driven synchronously to REFCLK. TXD[1] is the MSB. Note that in 100Mb/s mode, TXD can change once per REFCLK cycle, whereas in 10Mb/s mode, TXD must be held steady for 10 consecutive REFCLK cycles. TXD[3] and TXD[2] are not used in RMII Mode, left unconnected or pull down externally for normal operation. |

|                | GPSI Mode<br>TXD      |                  | Serial Transmit Data. TXD0 for the designated port inputs the data that is transmitted and is driven synchronously to TXCLK in 10Mb/s mode. When ADM7001 is programmed into GPSI mode, TXD[3:1] should be left unconnected or pull down externally for normal operation.                                                                                                                                   |

| 10             | MII Mode<br>TXEN      | I,<br>TTL,<br>PD | <b>Transmit Enable.</b> Transmit Enable to indicate that the data on TXD[3:0] is valid.                                                                                                                                                                                                                                                                                                                    |

|                | RMII Mode<br>TXEN     |                  | <b>Transmit Enable.</b> TXEN indicates that the di-bit on TXD is valid and it is driven synchronously to REFCLK.                                                                                                                                                                                                                                                                                           |

|                | GPSI Mode<br>TXEN     |                  | <b>Transmit Enable.</b> Transmit Enable to indicate that the data on TXD0 is valid.                                                                                                                                                                                                                                                                                                                        |

| 8              | MII Mode<br>TXER      | I, TTL,<br>PD    | <b>Transmit Error.</b> Active high signal to indicate that there is error condition requested by MAC.                                                                                                                                                                                                                                                                                                      |

|                | RMII Mode<br>TXER     |                  | <b>Transmit Error.</b> Active high signal to indicate that there is error condition requested by MAC.                                                                                                                                                                                                                                                                                                      |

| Pin # | Pin Name                            | Туре               | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|-------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | GPSI Mode<br>LOW                    |                    | Keep Low in GPSI Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4     | Power On<br>Setting<br>RMII_EN      | I,<br>LVTTL,<br>PD | RMII Enable. Used to select MII or RMII operation. The default value during power on reset is 0 (Before RMII_EN and GPSI value is determined) 0: MII mode 1: RMII Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       | MII Mode<br>RX_CLK                  | O,<br>16mA         | MII Receive Clock. 25M Clock output in 100BASE-X mode, 2.5M Clock output for 10BASE-T MII mode. This clock is recovered from the received data on the cable input. Due to recovered from incoming receive data, it is possible that RXCLK starts running yet RXDV keeps low for a while. During power on reset, there is no receiving clock driven by ADM7001.                                                                                                                                                                                                                                                                                                           |

|       | RMII Mode<br>CLKO50                 |                    | RMII 50M Clock Output. This pin outputs continuous 50M clock in RMII mode. To reduce the BOM cost for system application, user can connect this pin directly to REFCLK to proper RMII operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | GPSI Mode<br>RX_CLK                 |                    | GPSI Receive Clock. 10M clock for 10BASE-T GPSI mode. This clock is recovered from the received data on the cable input. Due to recovered from incoming receive data, it is possible that RXCLK starts running yet CRS keeps low for a while. During power on reset, there is no receiving clock driven by ADM7001.                                                                                                                                                                                                                                                                                                                                                      |

|       |                                     |                    | <b>Note:</b> that clock on this pin will not be active during power on reset due to power on setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3     | Power On<br>Setting<br>DIS_AMDIX_EN | I, LVTTL,<br>PD    | Disable Auto Crossover Function. Value on this pin will be latched by ADM7001 to select Auto Cross-Over Function.  0: Enable Auto Crossover.  1: Disable Auto Crossover.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | MII Mode<br>RXDV                    | O,<br>8mA          | MII Receive Data Valid. Active high signal to indicate that the data on RXD[3:0] is valid. Synchronous to the rising edge of RXCLK in MII mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | RMII Mode<br>CRSDV                  | O,<br>8mA          | RMII Carrier Sense/Receive Data Value. Represents Receive Carrier Sense and Data Valid in RMII mode. CRSDV asserts when the receive medium is non-idle. The assertion of CRSDV is asynchronous to REFCLK. At the de-assertion of carrier, CRSDV de-asserts synchronously to REFCLK only on the first di-bit of RXD. If there is still data in the FIFO not yet presented onto RXD, then on the second di-bit of RXD, CRSDV is asserted synchronously to REFCLK. The toggling of CRSDV_P on the first and second di-bit continues until all the data in the FIFO is presented onto RXD. CRSDV is asserted for the duration of carrier activity for a false carrier event. |

|       | GPSI Mode<br>LOW                    |                    | Keep Low in GPSI Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Pin #          | Pin Name                          | Type          | Pin Description                                                                                                                                                                                                                                                                                                              |

|----------------|-----------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 45, 46, 47, 48 | Power On<br>Setting<br>PHYAD[1:4] | I, TTL,<br>PD | PHY Address Select. Value on these 4 pins combined with PHYAD0 will be stored into ADM7001 as PHY physical address during power on reset. After power on reset, these 4 pins are output.                                                                                                                                     |

|                | MII Mode<br>RXD[3:0]              | O,<br>8mA     | MII Receive Data. Nibble-wide receive data stream in MII mode. These four bits are synchronous to the rising edge of RX_CLK and RXD[3] is the most significant bit.                                                                                                                                                          |

|                | RMII Mode<br>RXD[1:0]             | O,<br>8mA     | <b>RMII Receive Data.</b> RXD0 and RXD1 for the di-bits that are received and are driven synchronously to REFCLK. RXD[1] is the MSB. Note that in 100Mb/s mode, RXD can change once per REFCLK cycle, whereas in 10Mb/s mode, RXD must be held steady for 10 consecutive REFCLK cycles. RXD[3:2] have not used in this mode. |

|                | GPSI Mode<br>RXD                  | O,<br>8mA     | <b>GPSI Receive Data.</b> RXD0 for the designated port inputs the data that is transmitted and is driven synchronously to RX_CLK in 10Mb/s mode. RXD[3:1] have not used in this mode.                                                                                                                                        |

| 5              | Power On<br>Setting<br>ISOLATE    | I, TTL<br>PD  | ISOLATE. Value on this pin will be latched by ADM7001 during power on reset. 0: Normal Operation 1: All MII outputs are tri-stated. All MII Inputs(TXD, TXEN, TXER) are ignored.                                                                                                                                             |

|                | MII Mode<br>RXER                  | O,<br>4mA     | MII Receive Error. Active high signal to indicate that there is error condition detected by ADM7001. When error is detected, RXER will be high and maintains high until RXDV is deasserted.                                                                                                                                  |

|                | RMII Mode,<br>RXER                | O,<br>4mA     | <b>RMII Receive Error.</b> Active high signal to indicate that there is error condition detected by ADM7001. When error is detected, RXER will be high and maintains high until CRSDV is deasserted.                                                                                                                         |

|                | GPSI Mode,<br>N/A                 |               | No operation in GPSI Mode.                                                                                                                                                                                                                                                                                                   |

| 15             | Power On<br>Setting<br>GPSI       | I<br>PD       | GPSI Mode Select. Value on this pin will be sampled by ADM7001 during power on reset to form GPSI internal control signal. Together with RMII_EN, these two pins form three possible internal supported by ADM7001 RMII_EN GPSI Interface  0 0 MII  0 1 GPSI (1M8)  1 x RMII                                                 |

|                | GPSI/MII Mode<br>COL              | O,<br>8mA     | GPSI/MII Collision. In half duplex mode, active high to indicate that there is collision on the medium. In full duplex mode, this pin will keep low all the time.                                                                                                                                                            |

|                | RMII Mode<br>N/A                  |               | Not Available.                                                                                                                                                                                                                                                                                                               |

| 16             | Power On<br>Setting               | I,<br>LVTTL,  | <b>Repeater Mode.</b> Value on this pin will be latched by ADM7001 during power on reset as repeater mode                                                                                                                                                                                                                    |

| Pin# | Pin Name         | Type      | Pin Description                                                                                                                                                                                                                                |

|------|------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | REPEATER         | PD        | 0: SW/NIC mode, CRS will be asserted according to RX/TX in half duplex mode 1: REPEATER mode. CRS will be asserted only in RX mode in half duplex operation.                                                                                   |

|      | MII Mode<br>CRS  | O,<br>8mA | <b>MII Carrier Sense.</b> This bit indicates that there is carrier sense presented on the medium. Note that in half duplex mode, this pin will also be asserted high by ADM7001 under transmit condition. This pin is asynchronous to RX_CLK.  |

|      | RMII Mode<br>N/A |           | Not Available                                                                                                                                                                                                                                  |

|      | GPSI Mode<br>CRS |           | <b>GPSI Carrier Sense.</b> This bit indicates that there is carrier sense presented on the medium. Note that in half duplex mode, this pin will also be asserted high by ADM7001 under transmit condition. This pin is asynchronous to RX_CLK. |

### 2.2.6 Reset Pin

| Pin# | Pin Name | Type | Description                                              |

|------|----------|------|----------------------------------------------------------|

| 42   | RESET#   | I,   | Reset Signal. Active low to bring ADM7001 into reset     |

|      |          | SCHE | condition. Recommend keeping low for at least 200 ms to  |

|      |          |      | ensure the stability of the system after power on reset. |

2.2.7 Control Signals, 6 pins

| 2.2.1 | Control Signals, o pins |                                |                      |                                                                                                                                                                                                                                                |  |  |

|-------|-------------------------|--------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|       | Pin#                    | Pin Name                       | Type                 | Pin Description                                                                                                                                                                                                                                |  |  |

|       | 43                      | MDIO                           | I/O,<br>LVTTL,<br>PU | <b>Management Data.</b> MDIO transfers management data in and out of the device synchronous to MDC.                                                                                                                                            |  |  |