# Preliminary Information

# **Full-Bridge PWM Motor Driver**

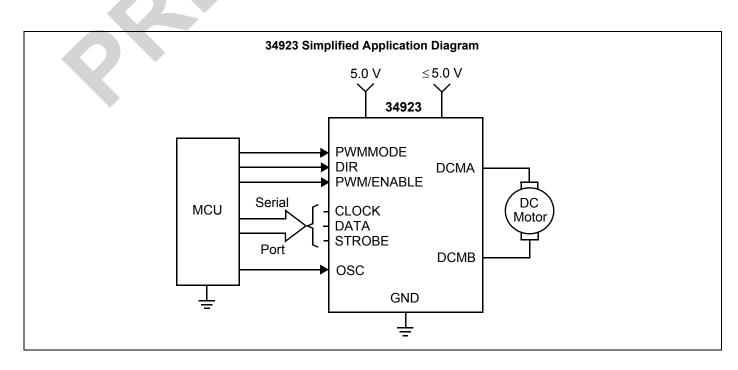

Designed with Motorola's advanced SMARTMOS, the 34923 is designed for pulse-width modulated (PWM) current control of DC motors. It is capable of continuous output currents up to 2.0 A and operating voltages of up to 45 V. Internal fixed off-time PWM current-control timing circuitry can be programmed via a serial interface to operate in slow, fast, and mixed current-decay modes.

DIR and PWM/ENABLE input pins are provided for use in controlling the speed and direction of a DC motor with externally applied PWM-control signals. The PWM/ENABLE input can be programmed via the serial port to PWM the bridge in fast or slow current decay. Internal synchronous rectification control circuitry is provided to reduce power dissipation during PWM operation.

Internal circuit protection includes thermal shutdown with hysteresis and crossover-current protection. A special power-up sequencing is not required.

#### **Features**

- ±2.0 A, 45 V Continuous Output Rating

- Low R<sub>DS(ON)</sub> Outputs (270 mΩ, typical)

- · Programmable Mixed, Fast, and Slow Current-Decay Modes

- Serial Interface Controls Chip Functions

- Synchronous Rectification for Low Power Dissipation

- Internal Undervoltage Lockout Thermal Shutdown Circuitry

- Crossover-Current Protection

34923

## **FULL-BRIDGE PWM MOTOR** DRIVER

#### **ORDERING INFORMATION**

| Device       | Temperature<br>Range (T <sub>A</sub> ) | Package  |  |

|--------------|----------------------------------------|----------|--|

| MC34923DW/R2 | -40 to 125°C                           | 24 SOICW |  |

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

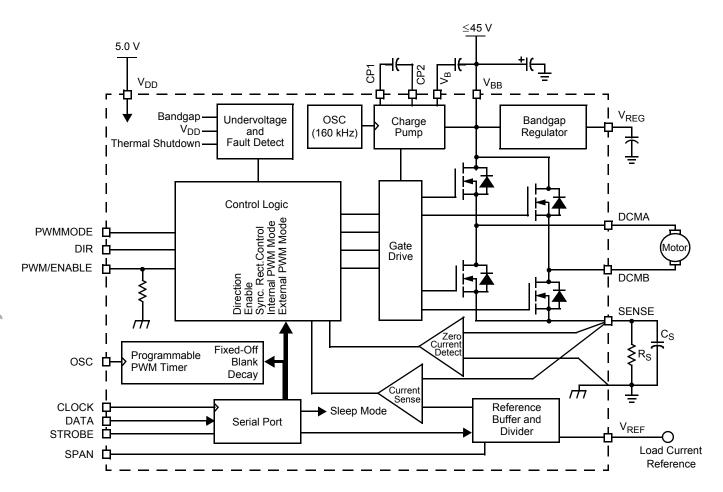

Figure 1. 34923 Simplified Block Diagram

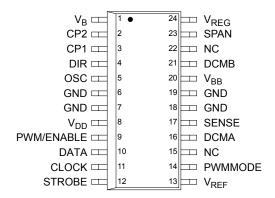

#### **PIN FUNCTION DESCRIPTION**

| Pin          | Pin Name                    | Formal Name                        | Definition                                                          |

|--------------|-----------------------------|------------------------------------|---------------------------------------------------------------------|

| 1            | V <sub>B</sub>              | Boost Voltage                      | Boost voltage storage node.                                         |

| 2            | CP2                         | Switching Capacitor 2              | Charge pump capacitor connection 2.                                 |

| 3            | 3 CP1 Switching Capacitor 1 |                                    | Charge pump capacitor connection 1.                                 |

| 4            | DIR                         | Direction                          | Logic-level input for direction control.                            |

| 5            | OSC                         | Oscillator                         | Logic-level oscillator (square wave) input.                         |

| 6, 7, 18, 19 | GND                         | Ground                             | Ground.                                                             |

| 8            | V <sub>DD</sub>             | Logic Voltage                      | Low voltage (typically 5.0 V) logic supply.                         |

| 9            | PWM/ENABLE                  | H-Bridge Enable                    | Logic-level input for enabling the H-bridge driver.                 |

| 10           | DATA                        | Serial Data                        | Logic-level input for serial interface.                             |

| 11           | CLOCK                       | Serial Data Clock                  | Logic-level input for serial port (data is entered on rising edge). |

| 12           | STROBE                      | Serial Data Latch Strobe           | Logic-level input for serial port (active on rising edge).          |

| 13           | V <sub>REF</sub>            | Current Limit Reference<br>Voltage | Load current reference input voltage.                               |

| 14           | PWMMODE                     | PWM Mode Control                   | Logic-level input for PWM mode control when in internal PWM mode.   |

| 15, 22       | NC                          | No Connect                         | No internal connection to this pin.                                 |

| 16           | DCMA                        | H-Bridge Output A                  | One of two bridge outputs to the motor.                             |

| 17           | SENSE                       | Current Sense                      | Sense resistor.                                                     |

| 20           | $V_{BB}$                    | H-Bridge Voltage Supply            | High-current (20 V to 45 V) load supply.                            |

| 21           | DCMB                        | H-Bridge Output B                  | One of two bridge outputs to the motor.                             |

| 23           | SPAN                        | Current Limit Reference Range      | Logic-level input for V <sub>REF</sub> range control.               |

| 24           | V <sub>REG</sub>            | Bandgap Voltage                    | Bandgap decoupling capacitor.                                       |

#### **MAXIMUM RATINGS**

All voltages are with respect to ground unless otherwise noted.

| Rating                                                       | Symbol                                 | Value                         | Unit |

|--------------------------------------------------------------|----------------------------------------|-------------------------------|------|

| Load Supply Voltage                                          | V <sub>BB</sub>                        | 48                            | V    |

| Logic Supply Voltage                                         | V <sub>DD</sub>                        | 7.0                           | V    |

| Input Voltage                                                | V <sub>IN</sub>                        | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Sense Voltage                                                | V <sub>S</sub>                         | 0.5                           | V    |

| Reference Voltage                                            | V <sub>REF</sub>                       | 2.7                           | V    |

| Output Current (Note 1)                                      | I <sub>OUT</sub>                       | ±2.0                          | А    |

| Storage Temperature                                          | T <sub>S</sub>                         | -55 to 150                    | °C   |

| Ambient Temperature                                          | T <sub>A</sub>                         | -20 to 85                     | °C   |

| Operating Junction Temperature                               | TJ                                     | -40 to 150                    | °C   |

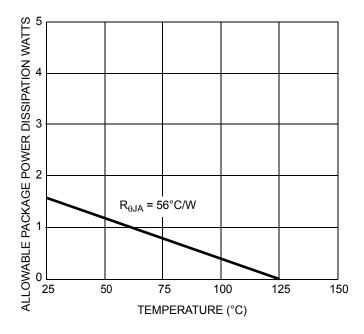

| Power Dissipation (T <sub>A</sub> = 25°C) (Note 2)           | P <sub>D</sub>                         | 1.6 (Note 3)                  | W    |

| ESD Voltage Human Body Model (Note 4) Machine Model (Note 5) | V <sub>ESD1</sub><br>V <sub>ESD2</sub> | ±2000<br>±200                 | V    |

| Lead Soldering Temperature (Note 6)                          | T <sub>SOLDER</sub>                    | 260                           | °C   |

| Thermal Resistance Junction-to-Ambient (Note 2)              | $R_{	heta JA}$                         | 56                            | °C/W |

#### Notes

- Output current rating may be limited by duty cycle, ambient temperature, and heatsinking. Under any set of conditions, do not exceed the specified current rating or a junction temperature of 150°C.

- 2. Maximum power dissipation at indicated ambient temperature in free air with no heatsink used.

- 3. Per SEMI G42-88 specification.

- 4. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ).

- 5. ESD2 testing is performed in accordance with the Machine Model ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ).

- Lead soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

### STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions  $T_A = 25$ °C,  $V_{BB} = 45$  V,  $V_{DD} = 5.0$  V,  $V_{SENSE} = 0.5$  V, and  $f_{PWM} < 50$  kHz unless otherwise noted.

| Characteristic                                   | Symbol                 | Min | Тур   | Max      | Unit |

|--------------------------------------------------|------------------------|-----|-------|----------|------|

| OUTPUT DRIVERS                                   |                        |     |       |          |      |

| Load Supply Voltage Range                        | V <sub>BB</sub>        |     |       |          | V    |

| Operating                                        |                        | 20  | -     | 45       |      |

| During Sleep Mode                                |                        | 0   | -     | 45       |      |

| Output Leakage Current                           | I <sub>DSS</sub>       |     |       |          | μΑ   |

| $V_{OUT} = V_{BB}$                               |                        | _   | <1.0  | 20       |      |

| V <sub>OUT</sub> = 0 V                           |                        | -   | <-1.0 | -20      |      |

| Output On Resistance                             | R <sub>DS(ON)</sub>    |     |       |          | mΩ   |

| Source Driver, I <sub>OUT</sub> = -2.0 A @ 25°C  |                        | _   | 300   | 450      |      |

| Source Driver, I <sub>OUT</sub> = -2.0 A @ 150°C |                        | _   | _     | 700      |      |

| Sink Driver, I <sub>OUT</sub> = 2.0 A @ 25°C     |                        | _   | 300   | 450      |      |

| Sink Driver, I <sub>OUT</sub> = 2.0 A @ 150°C    |                        | -   | -     | 700      |      |

| Body Diode Forward Voltage                       | V <sub>F</sub>         |     |       |          | V    |

| Source Diode, I <sub>F</sub> = -2.0 A            | , F                    | _   | 1.2   | 1.6      |      |

| Sink Diode, I <sub>F</sub> = 2.0 A               |                        | _   | 1.2   | 1.6      |      |

| ·                                                | 1                      |     |       |          |      |

| Load Supply Current                              | I <sub>BB</sub>        |     | 4.0   | 7.0      | mA   |

| f <sub>PWM</sub> < 50 kHz                        |                        | _   | 2.0   | 5.0      |      |

| Charge Pump On, Outputs Disabled                 |                        | _   |       | 20       | mA   |

| Sleep Mode                                       |                        | _   | _     | 20       | μА   |

| CONTROL LOGIC                                    | <u> </u>               |     | T .   | <u> </u> | 1    |

| Logic Supply Voltage Range (Operating)           | $V_{DD}$               | 4.5 | 5.0   | 5.5      | V    |

| Logic Input Voltage                              |                        |     |       |          | V    |

|                                                  | V <sub>IN(1)</sub>     | 2.0 | _     | _        |      |

|                                                  | V <sub>IN(0)</sub>     | ı   | _     | 0.8      |      |

| Input Current                                    |                        |     |       |          | μΑ   |

| All Logic Inputs Except PWM/ENABLE               |                        |     |       |          |      |

| V <sub>IN</sub> = 2.0 V                          | I <sub>IN(1)</sub>     | -   | <1.0  | 20       |      |

| V <sub>IN</sub> = 0.8 V                          | I <sub>IN(0)</sub>     | _   | <-2.0 | -20      |      |

| PWM/ENABLE Only                                  |                        |     |       |          |      |

| V <sub>IN</sub> = 2.0 V                          | I <sub>IN(1)</sub>     | _   | 40    | 100      |      |

| V <sub>IN</sub> = 0.8 V                          | I <sub>IN(0)</sub>     | _   | 16    | 40       |      |

| Input Hysteresis                                 |                        |     |       |          | mV   |

| All Digital Inputs Except OSC                    | $\Delta V_{IN(LOGIC)}$ | 50  | _     | 100      |      |

| OSC (Operating)                                  | $\Delta V_{IN(OSC)}$   | 200 | -     | 400      |      |

| Reference Input Voltage Range (Operating)        | V <sub>REF</sub>       | 0   | _     | 2.6      | V    |

| Reference Input Current                          | I <sub>REF</sub>       |     |       |          | μА   |

| V <sub>REF</sub> = 2.5 V                         | 'KEF                   | _   | _     | ±0.5     |      |

| Input Offset Voltage                             | V <sub>IO</sub>        |     |       |          | mV   |

| Comparator V <sub>REF</sub> = 0 V                | *10                    | _   | 0     | ±5.0     | •    |

|                                                  |                        | _   | 0     | ±15      |      |

| Buffer                                           |                        | _   |       | -10      |      |

## STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions  $T_A = 25$  °C,  $V_{BB} = 45$  V,  $V_{DD} = 5.0$  V,  $V_{SENSE} = 0.5$  V, and  $f_{PWM} < 50$  kHz unless otherwise noted

| Characteristic                        | Symbol          | Min  | Тур  | Max  | Unit |

|---------------------------------------|-----------------|------|------|------|------|

| CONTROL LOGIC (continued)             |                 |      |      |      |      |

| Reference Divider Ratio               | _               |      |      |      | -    |

| Bit D14 = High                        |                 | 9.9  | 10   | 10.2 |      |

| Bit D14 = Low                         |                 | 4.95 | 5.0  | 5.05 |      |

| Thermal Shutdown Temperature          | T <sub>J</sub>  | -    | 165  | -    | °C   |

| Thermal Shutdown Hysteresis           | $\DeltaT_J$     | -    | 15   | -    | °C   |

| Undervoltage Lockout Enable Threshold | UVLO            |      |      |      | V    |

| Increasing V <sub>DD</sub>            |                 | 3.90 | 4.2  | 4.45 |      |

| Undervoltage Lockout Hysteresis       | ΔUVLO           | 0.05 | 0.10 | -    | V    |

| Logic Supply Current                  | I <sub>DD</sub> |      |      |      | mA   |

| f <sub>PMW</sub> < 50 kHz             |                 | -    | 6.0  | 10   |      |

| Sleep Mode, Inputs <0.5 V             |                 | _    | -    | 2.0  |      |

### **DYNAMIC ELECTRICAL CHARACTERISTICS**

Characteristics noted under conditions  $T_A = 25$ °C,  $V_{BB} = 45$  V,  $V_{DD} = 5.0$  V,  $V_{SENSE} = 0.5$  V, and  $f_{PWM} < 50$  kHz unless otherwise noted.

| Symbol            | Min                   | Тур                                           | Max                                                                                     | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-------------------|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CONTROL LOGIC     |                       |                                               |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| f <sub>OSC</sub>  | 2.9                   | -                                             | 6.1                                                                                     | MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| dc <sub>OSC</sub> | 40                    | _                                             | 60                                                                                      | %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| <sup>t</sup> pd   | -<br>-<br>-<br>-<br>- | 600<br>100<br>600<br>100<br>600<br>100<br>600 | -<br>-<br>-<br>-<br>-                                                                   | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                   | dc <sub>OSC</sub>     | dc <sub>OSC</sub> 40                          | fosc 2.9 -  dcosc 40 -  t <sub>pd</sub> - 600 - 100 - 600 - 100 - 600 - 100 - 600 - 100 | fosc 2.9 - 6.1  dc <sub>OSC</sub> 40 - 60  t <sub>pd</sub> - 600 -  - 100 -  - 600 -  - 100 -  - 100 -  - 100 -  - 600 -  - 100 -  - 600 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 600 -  - 100 -  - 100 -  - 600 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 -  - 100 - |  |

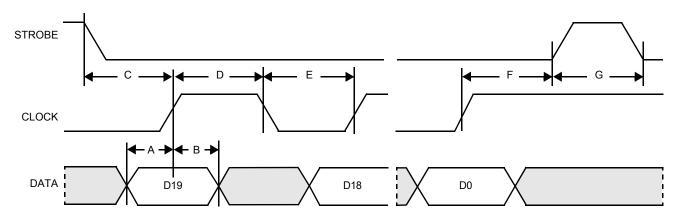

# **Timing Diagram**

## Legend

| ID | Description                       | Value (ns) | ID | Description                       | Value (ns) |

|----|-----------------------------------|------------|----|-----------------------------------|------------|

| Α  | DATA Setup Time                   | 15         | Е  | CLOCK Low Pulse Width             | 50         |

| В  | DATA Hold Time                    | 10         | F  | Setup CLOCK Rising Edge-to-STROBE | 50         |

| С  | Setup STROBE-to-CLOCK Rising Edge | 50         | G  | STROBE Pulse Width                | 50         |

| D  | CLOCK High Pulse Width            | 50         |    |                                   |            |

Figure 2. Serial Port Write Timing

#### SYSTEM/APPLICATION INFORMATION

#### INTRODUCTION

The 34923 is designed for pulse-width modulated (PWM) current control of DC motors. It is capable of continuous output currents up to 2.0 A and operating voltages of up to 45 V. Internal fixed off-time PWM current-control timing circuitry can be programmed via a serial interface to operate in slow, fast, and mixed current decay modes.

DIR and PWM/ENABLE input pins are provided for use in controlling the speed and direction of a DC motor with externally

applied PWM-control signals. The PWM/ENABLE input can be programmed via the serial port to PWM the bridge in fast or slow current decay. Internal synchronous rectification control circuitry is provided to reduce power dissipation during PWM operation.

Internal circuit protection includes thermal shutdown with hysteresis and crossover-current protection. Special power-up sequencing is not required.

#### **FUNCTIONAL PIN DESCRIPTION**

#### $V_{B}$

This pin provides a node for charge storage at the boost voltage. Internal circuitry will draw  $V_B$  current from this node, and the charge pump will deliver charge to this node.

#### CP1 and CP2

These pins are the connections to the switching capacitor in the charge pump. These pins swing between ground and  $V_B$ , drawing charge from  $V_{BB}$  and delivering it to the  $V_B$  node.

#### **DIR**

This is the direction input for the H-bridge driver.

#### **PWM/ENABLE**

This pin is the enable input for the H-bridge driver. When asserted this will bring the H-bridge out of tri-state mode so that it can drive a load.

#### **PWMMODE**

This logic input controls the H-bridge output mode when the PWM is deasserted. The H-bridge can have an active or passive output state when the PWM input is deasserted.

#### **OSC**

This logic input is the clock for the on-board decay time generator used only when in internal PWM mode. The decay time can be slow or mixed fast and slow.

# $V_{DD}$

This is the power supply input for the internal logic and several other functions.

#### **DATA**

This logic input is the serial data used by the serial interface.

#### **CLOCK**

This logic input is the clock for the serial interface. Data is shifted in synchronously with this clock.

#### **STROBE**

This logic input is used to latch data from the serial interface into the internal logic.

#### $V_{REF}$

This input provides a reference voltage for the current limit comparator threshold.

### **DCMA** and **DCMB**

These are the high-current, high-voltage drive signals for the motor.

#### $V_{BB}$

This is the motor drive voltage input. The H-bridge will deliver this voltage to the motor.

#### **SPAN**

This logic-level input controls the current limit comparator threshold that is generated from  $V_{\text{RFF}}$ .

#### $V_{RFG}$

This output is a decoupling node for the internal bandgap reference voltage generator.

#### **FUNCTIONAL DESCRIPTION**

#### **Serial Interface**

The 34923 is controlled via a 3-wire (clock, data, strobe) serial port. The programmable functions allow maximum flexibility in configuring the PWM to the motor drive requirements. The serial data is clocked in starting with bit D19.

| Bit | Function                         |  |  |

|-----|----------------------------------|--|--|

| D0  | Blank Time LSB                   |  |  |

| D1  | Blank Time MSB                   |  |  |

| D2  | Fixed Off-Time LSB               |  |  |

| D3  | Fixed Off-Time Bit 1             |  |  |

| D4  | Fixed Off-Time Bit 2             |  |  |

| D5  | Fixed Off-Time Bit 3             |  |  |

| D6  | Fixed Off-Time MSB               |  |  |

| D7  | Fast Decay Time LSB              |  |  |

| D8  | Fast Decay Time Bit 1            |  |  |

| D9  | Fast Decay Time Bit 2            |  |  |

| D10 | Fast Decay Time MSB              |  |  |

| D11 | Synchronous Rectification Mode   |  |  |

| D12 | Synchronous Rectification Enable |  |  |

| D13 | External PWM Decay Mode          |  |  |

| D14 | Enable Logic                     |  |  |

| D15 | Direction Logic                  |  |  |

| D16 | Divisor SPAN Select              |  |  |

| D17 | Internal PWM Mode                |  |  |

| D18 | Test Mode                        |  |  |

| D19 | Sleep Mode                       |  |  |

### D0-D1, Blank Time

The current-sense comparator is blanked when any output driver is switched on in accordance with the table below.  $f_{\rm osc}$  is the oscillator input frequency.

| D0 | D1 | Blank Time          |

|----|----|---------------------|

| 0  | 0  | 4/f <sub>osc</sub>  |

| 1  | 0  | 6/f <sub>osc</sub>  |

| 0  | 1  | 12/f <sub>osc</sub> |

| 1  | 1  | 24/f <sub>osc</sub> |

#### D2-D6, Fixed Off-Time

A five-bit word sets the fixed off-time for internal PWM current control. The off time is defined as follows:

$$t_{off} = (8[1 + N]/f_{osc}) - 1/f_{osc}$$

where N = 0 to 31.

For example, with an oscillator frequency of 4.0 MHz, the off-time is adjusted from 1.75  $\mu s$  to 63.75  $\mu s$  in increments of 2.0  $\mu s$ .

### D7-D10, Fast Decay Time

A four-bit word sets the fast decay portion of the fixed off-time for the internal PWM control circuitry. This will only have impact if the mixed current decay mode is selected (via bit D17 and the PWMMODE input pin). For  $t_{\rm fd} > t_{\rm off}$ , the device will effectively operate in the fast decay mode. The fast decay portion is defined as follows:

$$t_{fd} = (8[1 + N]/f_{osc}) - 1/f_{osc}$$

where N = 0 to 15.

For example, with an oscillator frequency of 4.0 MHz, the fast decay time is adjusted from 1.75  $\mu s$  to 31.75  $\mu s$  in increments of 2.0  $\mu s$ .

### D11-D12, Synchronous Rectification Control

The active mode prevents reversal of load current by turning off synchronous rectification when a zero current level is detected. The passive mode will allow reversal of current but will turn off the synchronous rectifier circuit if the load current inversion ramps up to the current limit set by  $V_{RFF}/R_S$ .

| D11 | D12 | Synchronous<br>Rect. Control |

|-----|-----|------------------------------|

| 0   | 0   | Disabled                     |

| 0   | 1   | Active                       |

| 1   | 0   | Disabled                     |

| 1   | 1   | Passive                      |

#### D13, External PWM Decay Mode

Bit D13 determines the current decay mode when using PWM/ENABLE chopping for external PWM current control.

| D13 | Current<br>Decay Mode |

|-----|-----------------------|

| 0   | Fast                  |

| 1   | Slow                  |

#### D14, Enable Logic

Bit D14, in conjunction with the PWM/ENABLE pin, determines if the output drivers are in the chopped (OFF) or ON state.

| PWM/<br>ENABLE | D14 | Operating<br>Mode |

|----------------|-----|-------------------|

| 0              | 0   | Chopped           |

| 1              | 1   | Chopped           |

| 1              | 0   | ON                |

| 0              | 1   |                   |

## D15, Direction Logic

Bit D15, in conjunction with the DIR pin, determines if the device is operating in the forward or reverse state.

| State   | DIR | D15 | DCMA   | DCMB |

|---------|-----|-----|--------|------|

| Reverse | 0   | 0   | Low    | High |

|         | 1   | 1   | LOW    |      |

| Forward | 1   | 0   | High   | Low  |

| Torward | 0   | 1   | riigii |      |

#### **D16, Divisor SPAN Select**

Bit D16, in conjunction with the SPAN pin, determines if  $V_{\text{REF}}$  is divided by 5 or 10.

| Divisor | SPAN | D16 |

|---------|------|-----|

| ÷5      | 1    | 0   |

|         | 0    | 1   |

| ÷10     | 0    | 0   |

|         | 1    | 1   |

#### D17, Internal PWM Mode

Bit D17, in conjunction with the PWMMODE pin, selects mixed or slow current decay.

| PWMMODE | D17 | Current<br>Decay Mode |  |

|---------|-----|-----------------------|--|

| 0       | 0   | Mixed                 |  |

| 1       | 1   | IVIIXEU               |  |

| 1       | 0   | Slow                  |  |

| 0       | 1   | Siow                  |  |

#### D18, Test Mode

Bit D18 low (default) operates the device in normal mode. D18 is only used for testing purposes. The user should never change this bit.

#### D19, Sleep Mode

Bit D19 selects a Sleep mode to minimize power consumption when not in use. This disables much of the internal circuitry, including the regulator and charge pump. On power-up the serial port is initialized to all zeros. Bit D19 should be programmed high for 1.0 ms before attempting to enable any output driver.

| D19 | Sleep Mode |

|-----|------------|

| 0   | Sleep      |

| 1   | Normal     |

## **Serial Port Write Timing Operations**

Data is clocked into the shift register on the rising edge of the CLOCK signal. Normally STROBE will be held high, only brought low to initiate a write cycle. Refer to Figure 2, Serial Port Write Timing, page 8, for the minimum timing requirements.

### **V<sub>REG</sub>**

This internally generated voltage is used to operate the sink-side outputs. The  $V_{REG}$  pin should be decoupled with a 0.22  $\mu F$  capacitor to ground.  $V_{REG}$  is internally monitored and, in the case of a fault condition, the outputs of the device are disabled.

#### **Charge Pump**

The charge pump is used to generate a gate supply voltage greater than  $V_{BB}$  to drive the source-side gates. A 0.22  $\mu F$  ceramic capacitor should be connected between CP1 and CP2 for pumping purposes. A 0.22  $\mu F$  ceramic capacitor should be connected between  $V_B$  and  $V_{BB}$  to act as a reservoir to operate the high-side devices. The  $V_B$  voltage is internally monitored and, in the case of a fault condition, the source outputs of the device are disabled.

### **Shutdown**

In the event of a fault (excessive junction temperature or low voltage on  $V_B$  or  $V_{REG}$ ), the outputs of the device are disabled until the fault condition is removed. At power-up, and in the event of low  $V_{DD}$ , the Undervoltage Lockout circuit disables the drivers and resets the data in the serial port to all zeros.

#### **PWM Timer Function**

The PWM timer is programmable via the serial port (bits D2–D10) to provide off-time PWM signals to the control circuitry. In the mixed current-decay mode, the first portion of the off time operates in fast decay, until the fast decay time count (serial bits D7–D10) is reached, followed by slow decay for the rest of the off-time period (bits D2–D6). If the fast decay time is set longer than the off time, the device effectively operates in fast decay mode. Bit D17, in conjunction with PWMMODE, selects mixed or slow decay.

#### **PWM Blank Timer**

When a source driver turns on, a current spike occurs owing to the reverse recovery currents of the clamp diodes and/or switching transients related to distributed capacitance in the load. To prevent this current spike from erroneously resetting the source-enable latch, the sense comparator is blanked. The blank timer runs after the off-time counter (see bits D2–D6) to provide the programmable blanking function. The blank timer is reset when PWM/ENABLE is chopped or DIR is changed. For external PWM control, a DIR change or PWM/ENABLE on will trigger the blanking function.

### **Synchronous Rectification**

When a PWM off cycle is triggered, either by an PWM/ ENABLE chop command or internal fixed off-time cycle, load current will recirculate according to the decay mode selected by the control logic. The 34923 synchronous rectification feature will turn on the opposite pair of outputs during the current decay and effectively short out the body diodes with the low  $R_{\text{DS}(\text{ON})}$  driver. This will reduce power dissipation significantly and can eliminate the need for external Schottky diodes.

Synchronous rectification can be configured in active mode, passive mode, or disabled via the serial port (bits D11 and D12).

The active or passive mode selection has no impact in slowdecay mode. With synchronous rectification enabled, the slowdecay mode serves as an effective brake mode.

#### **Current Regulation**

Load current is regulated by an internal fixed off-time PWM control circuit. When the outputs of the H-bridge are turned on, the current increases in the motor winding until it reaches a trip value determined by the external sense resistor ( $R_S$ ), the applied analog reference voltage ( $V_{REF}$ ), the SPAN logic level, and serial data bit D16:

When SPAN = D16,

$$I_{TRIP} = V_{REF}/10R_S$$

When SPAN  $\neq$  D16,  $I_{TRIP} = V_{REF}/5R_S$

At the trip point, the sense comparator resets the sourceenable latch, turning off the source driver. The load inductance then causes the current to recirculate for the serial-portprogrammed fixed off-time period. The current path during recirculation is determined by the configuration of slow/mixed current-decay mode (D17) and the synchronous rectification control bits (D11 and D12).

## **Internal PWM (Current Mode) PWM Frequency**

The internal PWM opeating frequency is set by the sum of "Off Time", as determined by bits D2 through D6, "Blank Time", as determined by bits D0 and D1, and the time constant of the motor.

#### **APPLICATIONS**

### **Current Sensing**

To minimize inaccuracies in sensing the  $I_{TRIP}$  current level, which may be caused by ground trace IR drops, the sense resistor should have an independent ground return to the ground pin of the device. For low-value sense resistors, the IR drops in the PCB sense resistor's traces can be significant and should be taken into account. The use of sockets should be avoided because they can introduce variation in  $R_S$  owing to their contact resistance.

The maximum value of  $R_S$  is given as  $R_S \le 0.5/I_{TRIP}$ .

#### **Braking**

The braking function is implemented by driving the device in slow-decay mode via serial port bit D13, enabling synchronous rectification via bit D12, and chopping with the combination of D14 and the PWM/ENABLE input pin. Because it is possible to drive current in either direction through the drivers, this configuration effectively shorts out the motor-generated back EMF (BEMF) as long as the PWM/ENABLE chop mode is asserted. It is important to note that the internal PWM current-control circuit will not limit the current when braking, because the current does not flow through the sense resistor. The maximum brake current can be approximated by  $V_{\rm BEMF}/R_{\rm L}.$  Care should be taken to ensure that the maximum ratings of the device are not exceeded in worst-case braking situations of high-speed and high-inertial loads.

### **Thermal Protection**

Circuitry turns off all drivers when the junction temperature reaches 165°C typically. It is intended only to protect the device from failures owing to excessive junction temperatures and should not imply that output short circuits are permitted. Thermal shutdown has a hysteresis of approximately 15°C.

#### Layout

The printed wiring board should use a heavy ground plane. For optimum electrical and thermal performance (see following Note), the driver should be soldered directly onto the board. The ground side of  $R_{\rm S}$  should have an individual path to the ground pins of the device. This path should be as short as is possible physically and should not have any other components connected to it. It is recommended that a 0.1  $\mu F$  capacitor be placed between SENSE and ground as close to the device as possible; the load supply pin,  $V_{BB}$ , should be decoupled with an electrolytic capacitor (>47  $\mu F$  is recommended) placed as close to the device as is possible.

**Note** The thermal resistance and absolute maximum allowable package power dissipation specified in the MAXIMUM RATINGS table, page 4, is measured on typical two-sided PCB with minimal copper ground area. For the 34923,  $R_{\theta JA}$  can be reduced to 56°C/W with 3.57-in<sup>2</sup> copper ground area, as shown in Figure 3.

Figure 3. Package Dissipation Temperature Derating

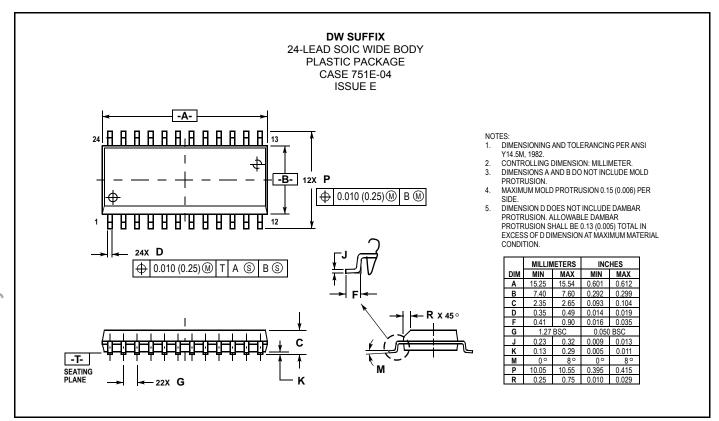

## **PACKAGE DIMENSIONS**

**NOTES**

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

MOTOROLA and the Stylized M Logo are registered in the US Patent and Trademark Office. All other product or service names are the property of their respective owners.

© Motorola, Inc. 2003

#### **HOW TO REACH US:**

**USA/EUROPE/LOCATIONS NOT LISTED:** Motorola Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-800-521-6274 or 480-768-2130

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center 3-20-1 Minami-Azabu. Minato-ku, Tokyo 106-8573, Japan 81-3-3440-3569

**ASIA/PACIFIC:** Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong 852-26668334

HOME PAGE: http://motorola.com/semiconductors