# intel® PXA270 Processor

### Electrical, Mechanical, and Thermal Specification

### Data Sheet

- High-performance processor:

—Intel XScale® microarchitecture with Intel® Wireless MMX<sup>™</sup> Technology

- —7 Stage pipeline

- —32 KB instruction cache

- —32 KB data cache

- -2 KB "mini" data cache

- -Extensive data buffering

- 256 Kbytes of internal SRAM for high speed code or data storage preserved during low-power states

- High-speed baseband processor interface (Mobile Scalable Link)

- Rich serial peripheral set:

- —AC'97 audio port

- —I<sup>2</sup>S audio port

- -USB Client controller

- —USB Host controller

- -USB On-The-Go controller

- Three high-speed UARTs (two with hardware flow control)

- -FIR and SIR infrared communications port

- Hardware debug features IEEE JTAG interface with boundary scan

- Hardware performance-monitoring features with on-chip trace buffer

- Real-time clock

- Operating-system timers

- LCD Controller

- Universal Subscriber Identity Module interface

- Low power:

- —Wireless Intel Speedstep  $\ensuremath{\mathbb{R}}$  Technology

- Less than 500 mW typical internal dissipation

- —Supply voltage may be reduced to 0.85 V

- -Four low-power modes

- -Dynamic voltage and frequency management

- High-performance memory controller:

- Four banks of SDRAM: up to 104 MHz @ 2.5V, 3.0V, and 3.3V I/O interface

- —Six static chip selects

- ---Support for PCMCIA and Compact Flash

- -Companion chip interface

- Flexible clocking:

- -CPU clock from 104 to 624 MHz

- -Flexible memory clock ratios

- -Frequency changes

- -Functional clock gating

- Additional peripherals for system connectivity:

- —SD Card / MMC Controller (with SPI mode support)

- -Memory Stick card controller

- -Three SSP controllers

- —Two I<sup>2</sup>C controllers

- -Four pulse-width modulators (PWMs)

- -Keypad interface with both direct and matrix keys support

- -Most peripheral pins double as GPIOs

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined. Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The PXA270 processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the license. The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document. Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AlertVIEW, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel XScale, IPLInk, Itanium, LANDesk, LanRover, MCS, MMX logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium III Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, Trillium, VoiceBrick, Vtune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation, 2005. All Rights Reserved.

# int<sub>el®</sub> Contents

| 1 | Intro      | oduction                                                                                             | 1-1        |

|---|------------|------------------------------------------------------------------------------------------------------|------------|

|   | 1.1        | About This Document1.1.1Number Representation1.1.2Typographical Conventions1.1.3Applicable Documents | 1-1<br>1-1 |

| 2 | Fund       | ctional Overview                                                                                     | 2-1        |

| 3 | Pack       | kage Information                                                                                     | 3-1        |

|   | 3.1        | Package Information                                                                                  |            |

|   | 3.2<br>3.3 | Processor Materials Junction To Case Temperature Thermal Resistance                                  |            |

|   | 3.4        | Processor Markings                                                                                   |            |

|   | 3.5        | Tray Drawing                                                                                         |            |

| 4 | Pin I      | Listing and Signal Definitions                                                                       | 4-1        |

|   | 4.1        | Ball Map View                                                                                        | 4-2        |

|   |            | 4.1.1 13x13 mm VF-BGA Ball map                                                                       |            |

|   |            | 4.1.2 23x23 mm PBGA Ball map                                                                         |            |

|   | 4.2<br>4.3 | Pin Use                                                                                              |            |

|   | 4.3<br>4.4 | Signal Types<br>Memory Controller Reset and Initialization                                           |            |

|   | 4.5        | Power-Supply Pins                                                                                    |            |

| 5 | Elec       | trical Specifications                                                                                | 5-1        |

|   | 5.1        | Absolute Maximum Ratings                                                                             | 5-1        |

|   | 5.2        | Operating Conditions                                                                                 |            |

|   |            | 5.2.1 Internal Power Domains                                                                         |            |

|   | 5.3        | Power-Consumption Specifications                                                                     |            |

|   | 5.4<br>5.5 | DC Specification<br>Oscillator Electrical Specifications                                             |            |

|   | 5.5        | 5.5.1 32.768-kHz Oscillator Specifications                                                           |            |

|   |            | 5.5.2 13.000-MHz Oscillator Specifications                                                           |            |

|   | 5.6        | CLK_PIO and CLK_TOUT Specifications                                                                  |            |

|   | 5.7        | 48 MHz Output Specifications                                                                         | 5-13       |

| 6 | AC 1       | Timing Specifications                                                                                | 6-1        |

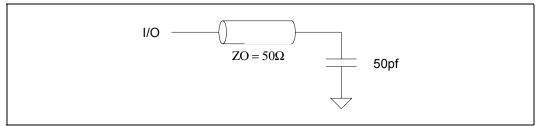

|   | 6.1        | AC Test Load Specifications                                                                          |            |

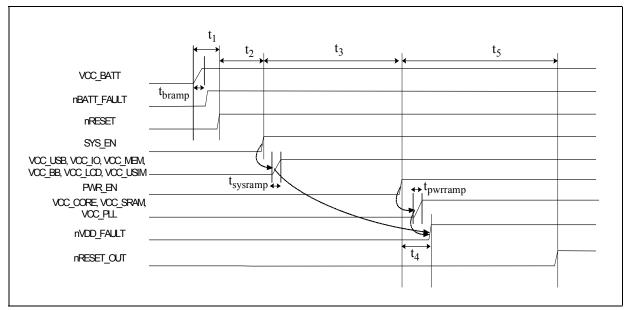

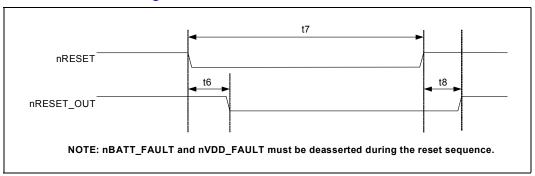

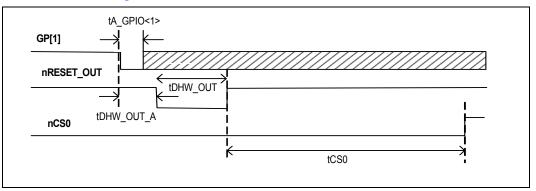

|   | 6.2        | Reset and Power Manager Timing Specifications                                                        |            |

|   |            | 6.2.1 Power-On Timing Specifications                                                                 |            |

|   |            | <ul><li>6.2.2 Hardware Reset Timing</li><li>6.2.3 Watchdog Reset Timing</li></ul>                    |            |

|   |            | 6.2.4 GPIO Reset Timing                                                                              |            |

|   |            | 6.2.5 Sleep Mode Timing                                                                              |            |

|   |            | 6.2.6 Deep-Sleep Mode Timing                                                                         |            |

|     | 6.2.7  | Standby-Mode Timing                                    | 6-10   |

|-----|--------|--------------------------------------------------------|--------|

|     | 6.2.8  | Idle-Mode Timing                                       | 6-10   |

|     | 6.2.9  | Frequency-Change Timing                                | 6-10   |

|     | 6.2.10 | Voltage-Change Timing                                  | 6-11   |

| 6.3 | GPIO T | iming Specifications                                   | 6-11   |

| 6.4 | Memor  | y and Expansion-Card Timing Specifications             | 6-12   |

|     | 6.4.1  | Internal SRAM Read/Write Timing Specifications         | 6-12   |

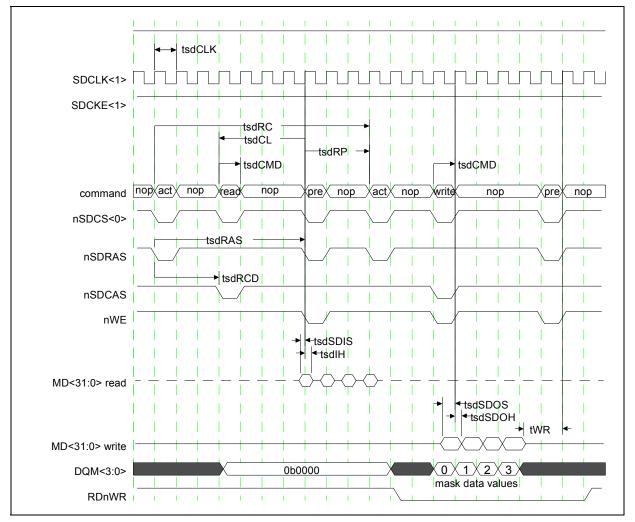

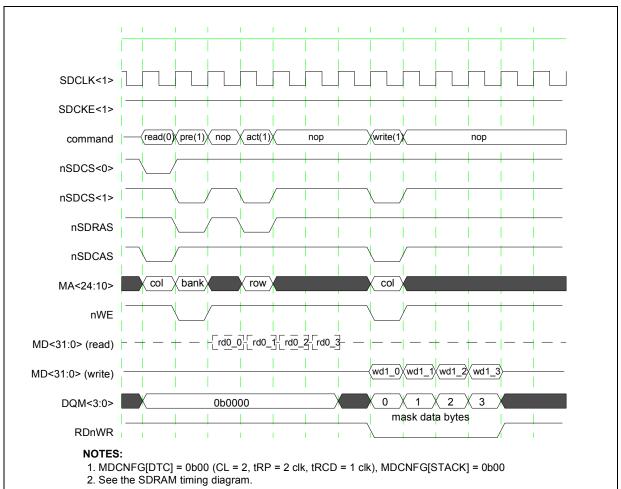

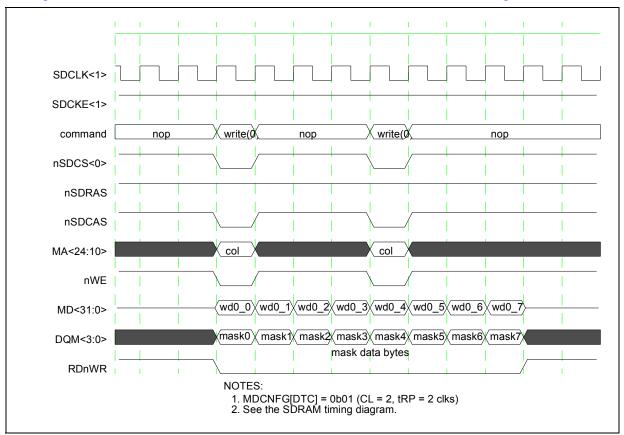

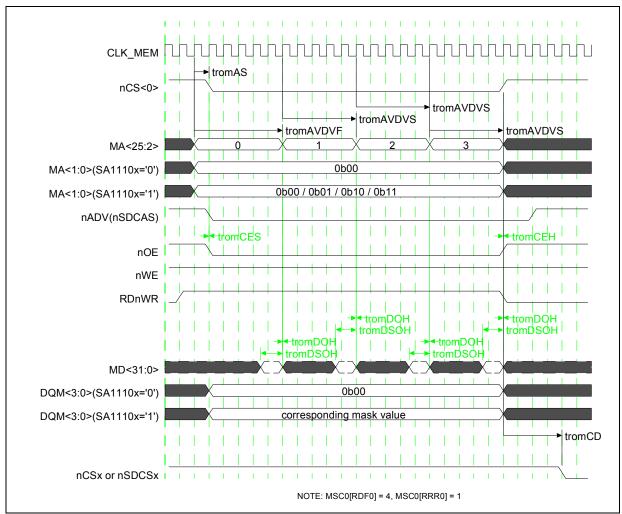

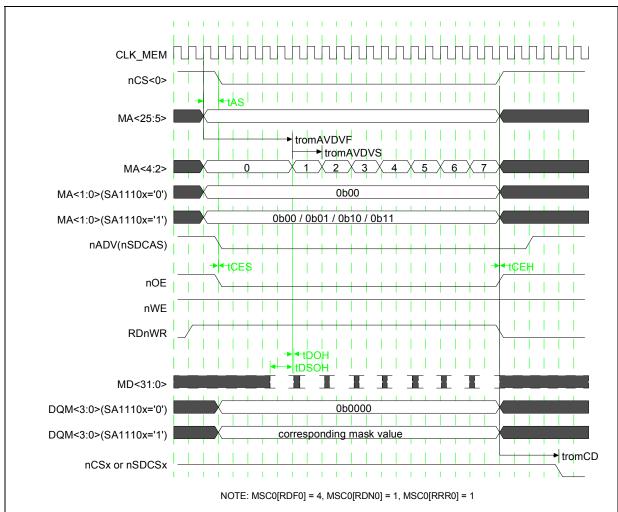

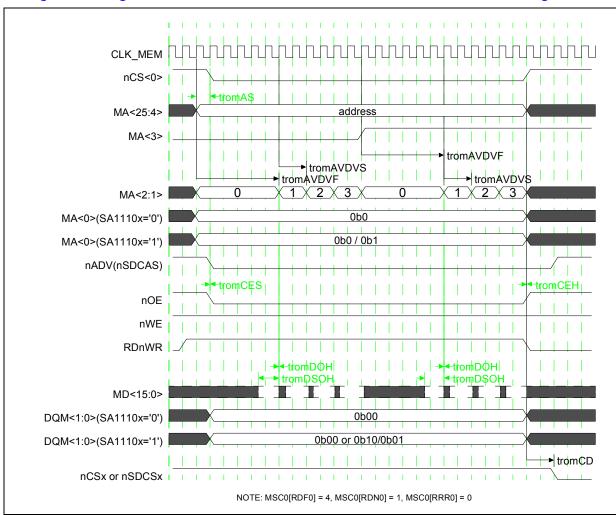

|     | 6.4.2  | SDRAM Parameters and Timing Diagrams                   | 6-12   |

|     | 6.4.3  | ROM Parameters and Timing Diagrams                     | 6-18   |

|     | 6.4.4  | Flash Memory Parameters and Timing Diagrams            | 6-23   |

|     | 6.4.5  | SRAM Parameters and Timing Diagrams                    | 6-33   |

|     | 6.4.6  | Variable-Latency I/O Parameters and Timing Diagrams    | 6-36   |

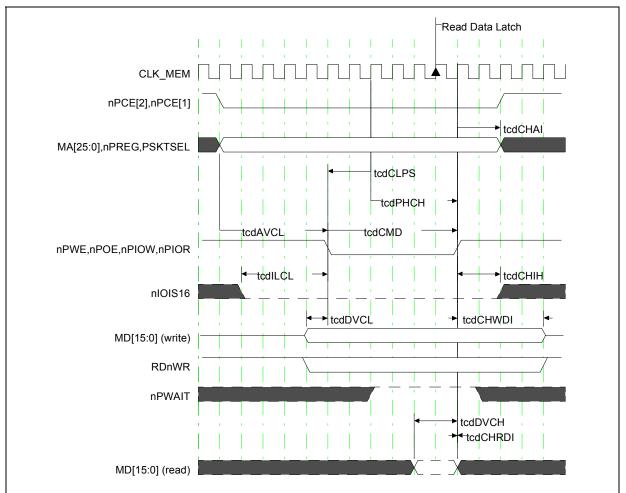

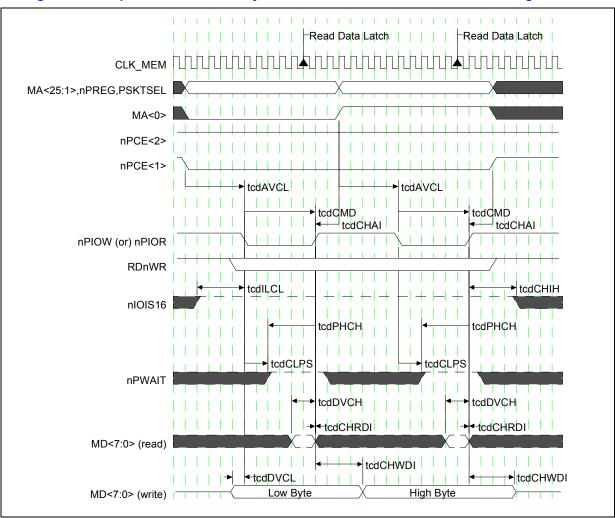

|     | 6.4.7  | Expansion-Card Interface Parameters and Timing Diagram | ns6-40 |

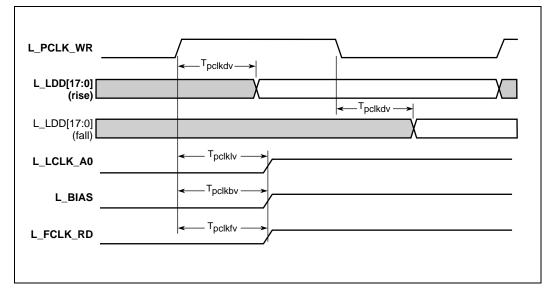

| 6.5 | LCD Ti | ming Specifications                                    | 6-43   |

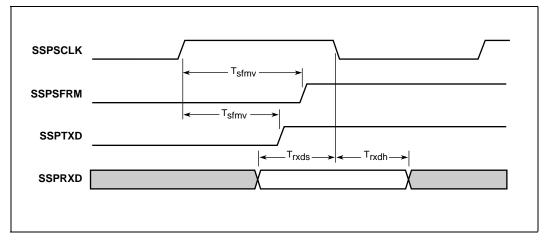

| 6.6 | SSP Ti | ming Specifications                                    | 6-44   |

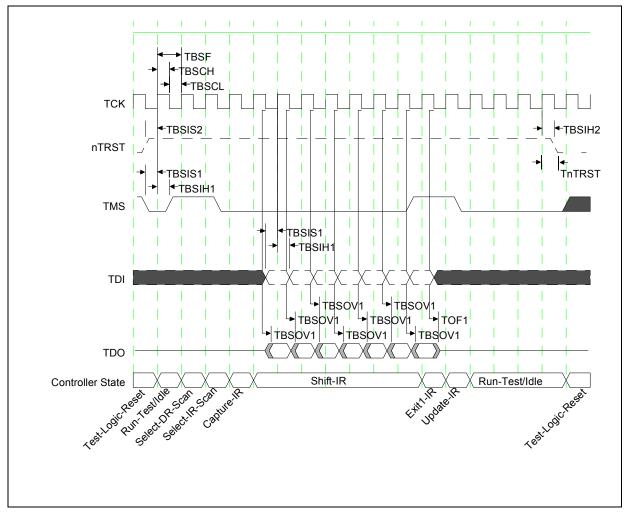

| 6.7 | JTAG E | Boundary Scan Timing Specifications                    | 6-45   |

|     |        |                                                        |        |

# **Figures**

| 2-1 Intel® PXA270 Processor Block Diagram, Typical System                 | 2-2  |

|---------------------------------------------------------------------------|------|

| 3-1 13x13mm VF-BGA Intel® PXA270 Processor Package, top view              | 3-1  |

| 3-2 13x13mm VF-BGA Intel® PXA270 Processor Package, bottom view           | 3-2  |

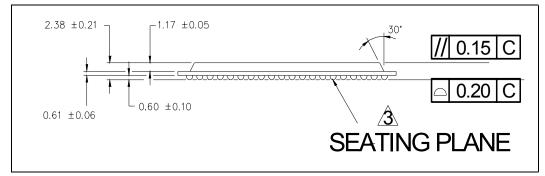

| 3-3 13x13mm VF-BGA Intel® PXA270 Processor Package, side view             | 3-3  |

| 3-4 VF-BGA Product Information Decoder                                    | 3-3  |

| 3-5 23x23 mm PBGA Intel® PXA270 Processor Package (Top View)              | 3-4  |

| 3-6 23x23 mm PBGA Intel® PXA270 Processor Package (Bottom View)           | 3-4  |

| 3-7 23x23 mm PBGA Intel® PXA270 Processor Package (Side View)             | 3-5  |

| 3-8 PBGA Product Information Decoder                                      | 3-5  |

| 3-9 13x13mm VF-BGA Intel® PXA270 Processor Package, bottom view           | 3-6  |

| 3-10 Intel® PXA270 Processor Production Markings, (Laser Mark on Top Side | )3-7 |

| 4-1 13x13 mm VF-BGA Ball Map, Top View (upper left quarter)               | 4-2  |

| 4-2 13x13 mm VF-BGA Ball Map, Top View (upper right quarter)              | 4-3  |

| 4-3 13x13 mm VF-BGA Ball Map, Top View (bottom left quarter)              | 4-4  |

| 4-4 13x13 mm VF-BGA Ball Map, Top View (bottom right quarter)             | 4-5  |

| 4-5 23x23 mm PBGA Ball Map, Top View (Upper Left Quarter)                 | 4-6  |

| 4-6 23x23 mm PBGA Ball Map, Top View (Upper Right Quarter)                | 4-7  |

| 4-7 23x23 mm PBGA Ball Map, Top View (Lower Left Quarter)                 | 4-8  |

| 4-8 23x23 mm PBGA Ball Map, Top View (Lower Right Quarter)                | 4-9  |

| 6-1 AC Test Load                                                          | 6-2  |

| 6-2 Power On Reset Timing                                                 | 6-3  |

| 6-3 Hardware Reset Timing                                                 | 6-4  |

| 6-4 GPIO Reset Timing                                                     | 6-5  |

| 6-5 Sleep Mode Timing                                                     | 6-7  |

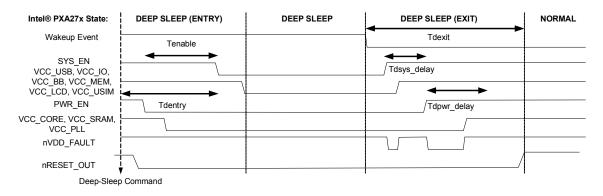

| 6-6 Deep-Sleep-Mode Timing                                                | 6-8  |

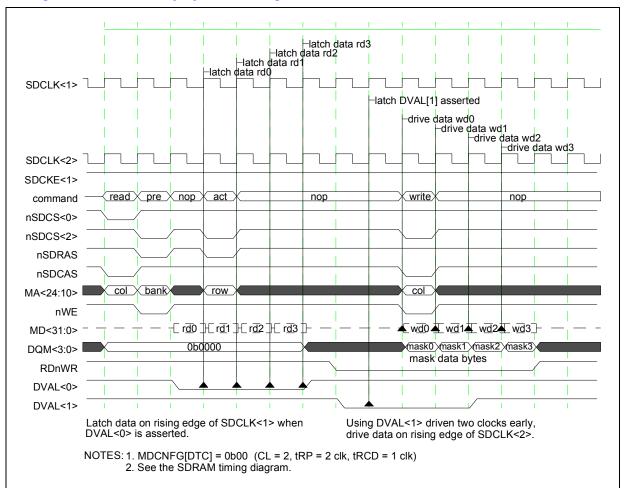

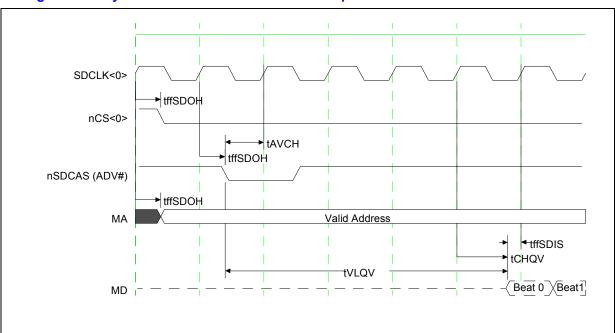

| 6-7 SDRAM Timing                                                          |      |

| 6-8 SDRAM 4-Beat Read/4-Beat Write, Different Banks Timing                | 6-16 |

| 6-9 SDRAM 4-Beat Write/4-Beat Write, Same Bank-Same Row Timing            | 6-17 |

| 6-10SDRAM Fly-by DMA Timing                                               | 6-18 |

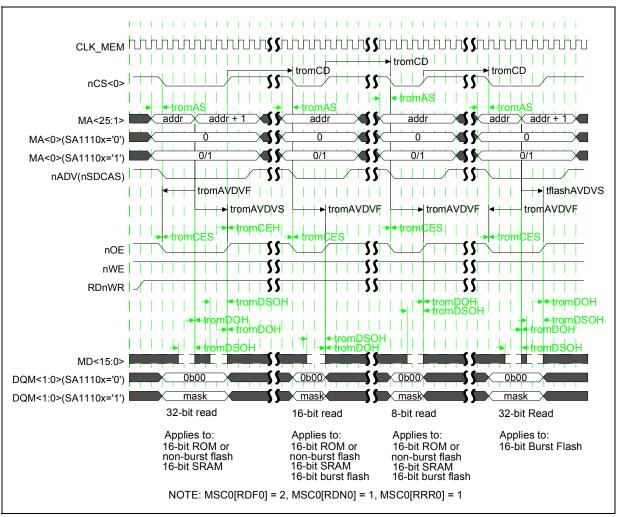

| 6-1132-Bit Non-burst ROM, SRAM, or Flash Read Timing                      | 6-20 |

| 6-1232-Bit Burst-of-Eight ROM or Flash Read Timing                  | 6-21     |

|---------------------------------------------------------------------|----------|

| 6-13 Eight-Beat Burst Read from 16-Bit Burst-of-Four ROM or Flash T |          |

| 6-14 16-bit ROM/Flash/SRAM Read for 4/2/1 Bytes Timing              | 6-23     |

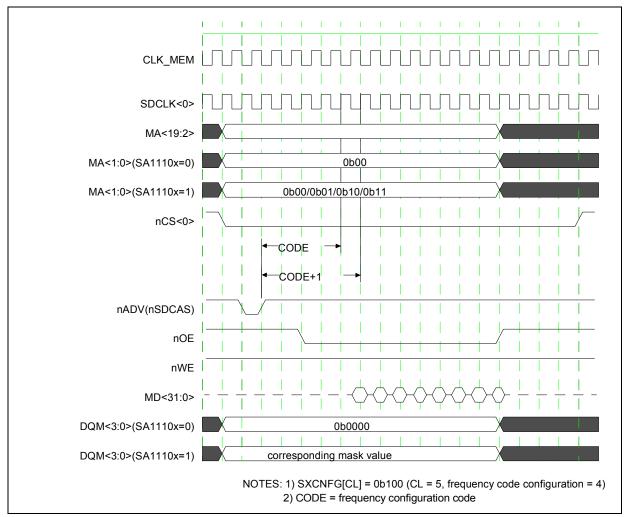

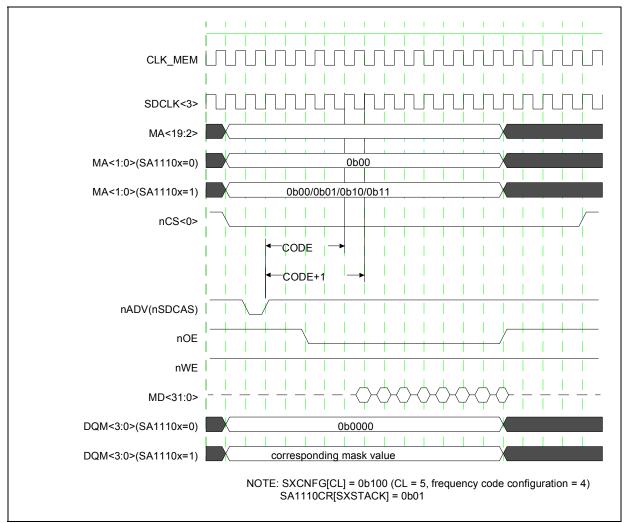

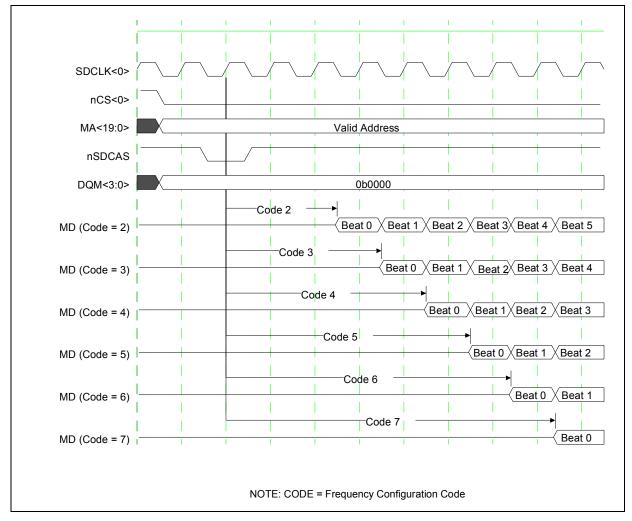

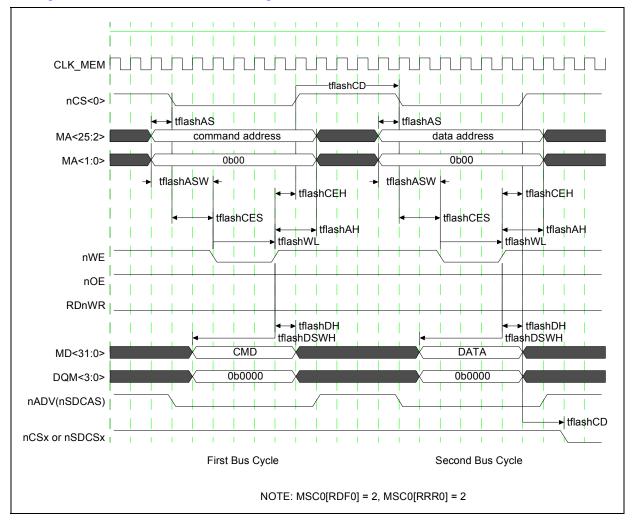

| 6-15 Synchronous Flash Burst-of-Eight Read Timing                   | 6-26     |

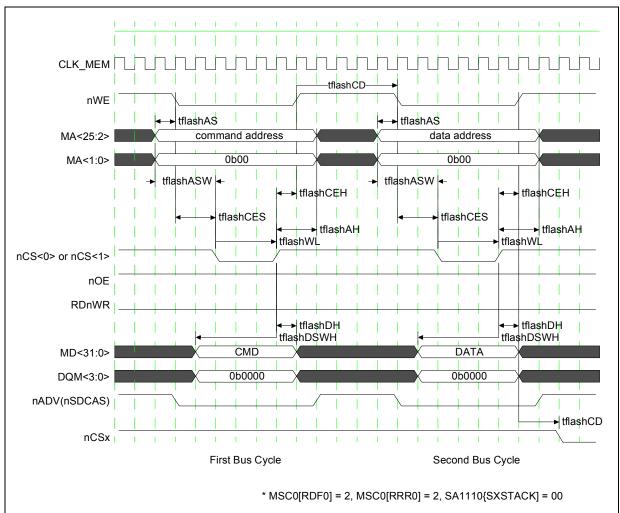

| 6-16 Synchronous Flash Stacked Burst-of-Eight Read Timing           | 6-27     |

| 6-17 First-Access Latency Configuration Timing                      | 6-28     |

| 6-18 Synchronous Flash Burst Read Example                           | 6-30     |

| 6-1932-Bit Flash Write Timing                                       | 6-31     |

| 6-2032-Bit Stacked Flash Write Timing                               | 6-32     |

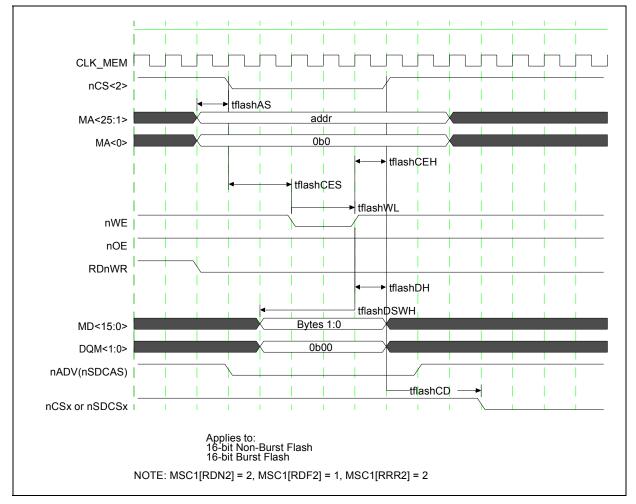

| 6-2116-Bit Flash Write Timing                                       | 6-33     |

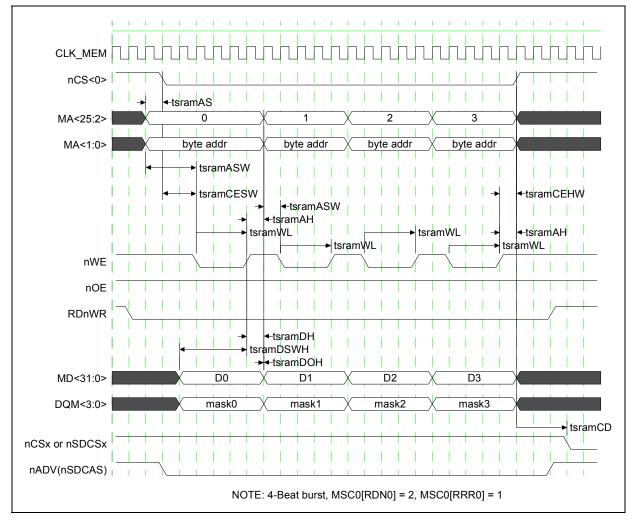

| 6-2232-Bit SRAM Write Timing                                        | 6-35     |

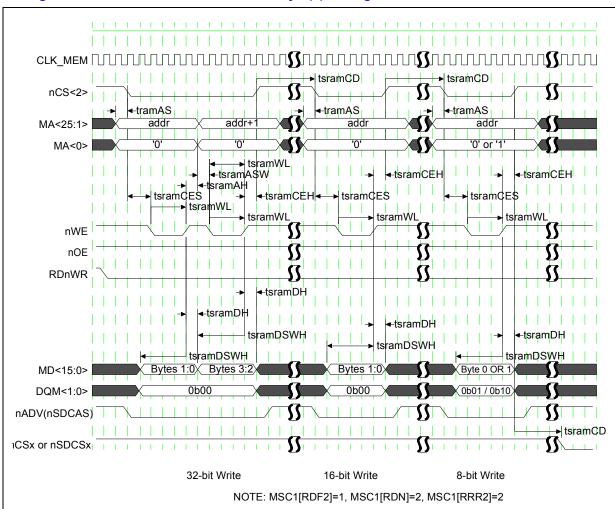

| 6-2316-bit SRAM Write for 4/2/1 Byte(s) Timing                      | 6-36     |

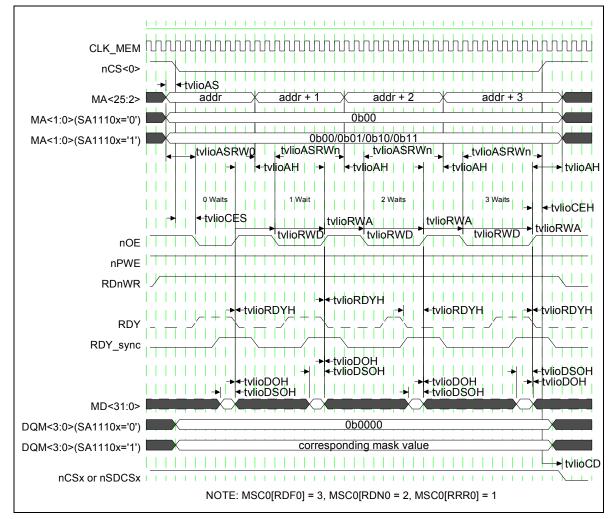

| 6-2432-Bit VLIO Read Timing                                         | 6-38     |

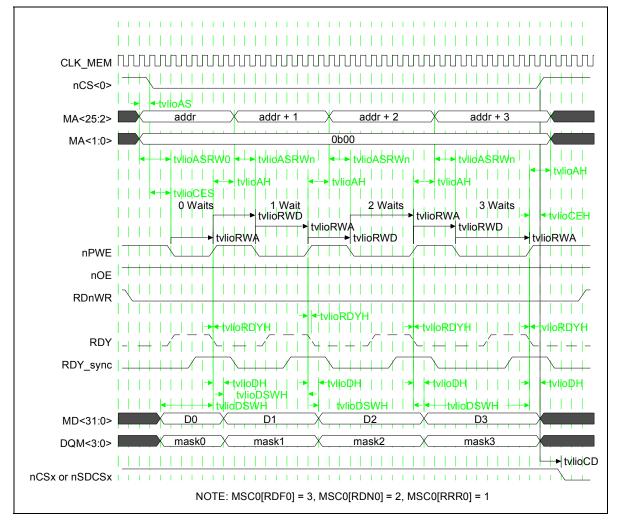

| 6-2532-Bit VLIO Write Timing                                        | 6-39     |

| 6-26 Expansion-Card Memory or I/O 16-Bit Access Timing              | 6-41     |

| 6-27 Expansion-Card Memory or I/O 16-Bit Access to 8-Bit Device Tir | ning6-42 |

| 6-28LCD Timing Definitions                                          | 6-43     |

| 6-29SSP Master Mode Timing Definitions                              | 6-44     |

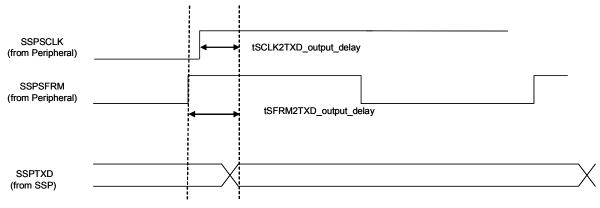

| 6-30 Timing Diagram for SSP Slave Mode Transmitting Data to an Ex   |          |

| Peripheral                                                          | 6-44     |

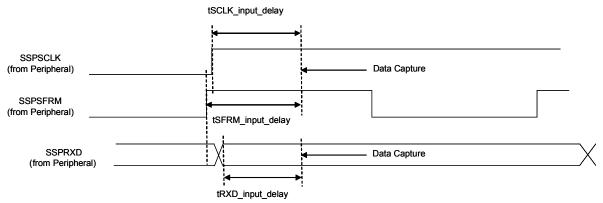

| 6-31 Timing Diagram for SSP Slave Mode Receiving Data from Extern   |          |

| Peripheral                                                          |          |

| 6-32 JTAG Boundary-Scan Timing                                      | 6-46     |

|                                                                     |          |

# **Tables**

| 1-1 Supplemental Documentation                                     | 1-2  |

|--------------------------------------------------------------------|------|

| 3-1 Processor Material Properties                                  | 3-7  |

| 4-1 Pin Use Summary                                                | 4-10 |

| 4-2 Pin Use and Mapping Notes                                      | 4-27 |

| 4-3 Signal Types                                                   |      |

| 4-4 Memory Controller Pin Reset Values                             | 4-28 |

| 4-5 Discrete (13x13 VF-BGA) Power Supply Pin Summary               | 4-29 |

| 5-1 Absolute Maximum Ratings                                       | 5-1  |

| 5-2 Voltage, Temperature, and Frequency Electrical Specifications. | 5-2  |

| 5-3 Memory Voltage and Frequency Electrical Specifications         | 5-4  |

| 5-4 Core Voltage and Frequency Electrical Specifications           | 5-4  |

| 5-5 Internally Generated Power Domain Descriptions                 | 5-6  |

| 5-6 Core Voltage Specifications For Lower Power Modes              | 5-6  |

| 5-7 Power-Consumption Specifications                               |      |

| 5-8 Standard Input, Output, and I/O Pin DC Operating Conditions    |      |

| 5-9 Typical 32.768-kHz Crystal Requirements                        |      |

| 5-10 Typical External 32.768-kHz Oscillator Requirements           |      |

| 5-11 Typical 13.000-MHz Crystal Requirements                       |      |

| 5-12 Typical External 13.000-MHz Oscillator Requirements           |      |

| 5-13CLK_PIO Specifications                                         |      |

| 5-14 CLK_TOUT Specifications                                       |      |

| 5-1548 MHz Output Specifications                                   |      |

| 6-1 Standard Input, Output, and I/O-Pin AC Operating Conditions    |      |

| 6-2 Power-On Timing Specifications(OSCC[CRI] = 0)                  |      |

| 6-3 Hardware Reset Timing Specifications (OSCC[CRI] = 0)           | 6-4  |

| 6-4 Hardware Reset Timing Specifications (OSCC[CRI] = 1)                  | 6-5  |

|---------------------------------------------------------------------------|------|

| 6-5 GPIO Reset Timing Specifications                                      |      |

| 6-6 Sleep-Mode Timing Specifications                                      |      |

| 6-7 Deep-Sleep Mode Timing Specifications                                 |      |

| 6-8 GPIO Pu/Pd Timing Specifications for Deep-Sleep Mode                  |      |

| 6-9 Standby-Mode Timing Specifications                                    |      |

| 6-10 Idle-Mode Timing Specifications                                      | 6-10 |

| 6-11 Frequency-Change Timing Specifications                               | 6-10 |

| 6-12 Voltage-Change Timing Specification for a 1-Byte Command             | 6-11 |

| 6-13 GPIO Timing Specifications                                           | 6-11 |

| 6-14 SRAM Read/Write AC Specification                                     | 6-12 |

| 6-15 SDRAM Interface AC Specifications                                    | 6-13 |

| 6-16 ROM AC Specification                                                 | 6-18 |

| 6-17 Synchronous Flash Read AC Specifications                             | 6-24 |

| 6-18 Flash Memory AC Specification                                        | 6-30 |

| 6-19SRAM Write AC Specification                                           | 6-34 |

| 6-20 VLIO Timing                                                          | 6-37 |

| 6-21 Expansion-Card Interface AC Specifications                           | 6-40 |

| 6-22LCD Timing Specifications                                             | 6-43 |

| 6-23 SSP Master Mode Timing Specifications                                | 6-44 |

| 6-24 Timing Specification SSP Slave Mode Transmitting Data to External    |      |

| Peripheral                                                                | 6-45 |

| 6-25 Timing Specification for SSP Slave Mode Receiving Data from External |      |

| Peripheral                                                                |      |

| 6-26 Boundary Scan Timing Specifications                                  | 6-45 |

# **Revision History**

| Date         | Revision | Description                                                                                                |

|--------------|----------|------------------------------------------------------------------------------------------------------------|

| April 2004   | -001     | First public release of the EMTS                                                                           |

| June 2004    | -002     | Added 23x23 mm 360-ball PBGA package                                                                       |

| June 2004    | -003     | Added 624-MHz active and idle power consumption values to Table 5-7.                                       |

|              |          | Modified Power Consumption introduction in Chapter 5, "Power-<br>Consumption Specifications"               |

| October 2004 | -004     | Modified Watchdog Reset timing description Chapter 6, "Reset<br>and Power Manager Timing Specifications"   |

|              |          | Corrected 13 MHz Oscillator slew rate specification Section 5.5,<br>"Oscillator Electrical Specifications" |

|              |          | Added note to VCC_BB voltage specifications, Chapter 5,<br>"Electrical Specifications"                     |

| April 2005   | -005     | Modified Core Voltage and Frequency Electrial Specifications,<br>Chapter 5, "Electrical Specifications"    |

| April 2005   |          | Modified SDRAM Parameters and Timing Diagrams, Chapter 6,<br>"AC Timing Specifications"                    |

|              |          | Modified Processor Material Properties, Chapter 3, "Package Information"                                   |

**§§**

Intel® PXA270 Processor Contents

# intel®

### Documentation Feedback Form for the Intel® PXA270 Processor Electrical, Mechanical, Thermal Specification

Your input allows us to create documentation that better meets your needs. Please print out and fax this completed form to:

Cellular and Handheld Group/Application Processors Business Unit (APBU) Smart Handheld Platforms Attn: Technical Publications Intel Corporation Fax: 512-314-1108

Please do NOT address technical questions on this form. Contact your Intel representative. Rating Scale: 5 = Excellent; 4 = Above Average; 3 = Average; 2 = Below Average; 1 = Poor/NA

| 1. | Overall organization of the manual:                 | 5 🗆     | 4 🗆      | 3    | 2 🗆     | 1 🗆    |

|----|-----------------------------------------------------|---------|----------|------|---------|--------|

| 2. | Ease of navigation throughout the manual:           | 5 🗆     | 4 🗆      | 3    | 2 🗆     | 1 🗆    |

| 3. | Overall organization of content within chapters:    | 5 🗆     | 4 🗆      | 3    | 2 🗆     | 1 🗆    |

| 4. | Accuracy of the content:                            | 5 🗆     | 4 🗆      | 3    | 2 🗆     | 1 🗆    |

| 5. | Sufficient level of detail to the content:          | 5 🗆     | 4 🗆      | 3    | 2 🗆     | 1 🗆    |

| 6. | Readability/comprehension of the content:           | 5 🗆     | 4 🗆      | 3    | 2 🗆     | 1 🗆    |

| 7. | Accuracy/Usefulness of tables and figures:          | 5 🗆     | 4 🗆      | 3    | 2 🗆     | 1 🗆    |

| 8. | Accuracy/functionality of cross-references:         | 5 🗆     | 4 🗆      | 3    | 2 🗆     | 1 🗆    |

| 9. | Accuracy/usefulness of lists (index, TOC, etc.):    | 5 🗆     | 4 🗆      | 3    | 2 🗆     | 1 🗆    |

| 10 | . Which of these do you use most often to initially | ,       |          |      |         |        |

|    | locate information in a manual? Table of co         | ontents | s 🗆 Inde | ex D | Rev His | tory 🛛 |

|    |                                                     |         |          |      |         |        |

11. This manual needs to have more of:

12. This manual needs to have less of:

13. The thing(s) I liked best about this manual:

14. The thing(s) I liked least about this manual:

15. Any other comments about the quality, accuracy, usability of this document:

Intel® PXA270 Processor Contents

# int<sub>el</sub>®

# Introduction

The Intel® PXA270 processor (PXA270 processor) provides industry-leading multimedia performance, low-power capabilities, rich peripheral integration and second generation memory stacking. Designed from the ground up for wireless clients, it incorporates the latest Intel advances in mobile technology over its predecessor, the Intel® PXA255 processor. These same attributes and features also make the PXA270 processor ideal for embedded applications. The PXA270 processor redefines scalability by operating from 104 MHz up to 624 MHz, providing enough performance for the most demanding mobile applications.

The PXA270 processor is the first Intel processor to include Intel® Wireless MMX<sup>™</sup> technology, enabling high-performance, low-power multimedia acceleration with a general-purpose instruction set. Intel® Quick Capture technology provides a flexible and powerful camera interface for capturing digital images and video. While performance is key in the PXA270 processor, power consumption is also a critical component. The new capabilities of Wireless Intel SpeedStep® technology set the standard for low-power consumption.

The PXA270 processor is offered in two packages: 13x13 mm VFBGA and 23x23 mm PBGA.

## 1.1 About This Document

This document constitutes the electrical, mechanical, and thermal specifications for the PXA270 processor. It contains a functional overview, mechanical data, package signal locations, targeted electrical specifications, and functional bus waveforms. For detailed functional descriptions other than parametric performance, refer to the *Intel*® *PXA27x Processor Family Developers Manual*.

### 1.1.1 Number Representation

All numbers in this document are **base 10** unless designated otherwise. Hexadecimal numbers have a prefix of 0x, and binary numbers have a prefix of 0b. For example, 107 is represented as 0x6B in hexadecimal and 0b110\_1011 in binary.

### 1.1.2 Typographical Conventions

All signal and register-bit names appear in uppercase. Active low items are prefixed with a lowercase "n".

Bits within a signal name are enclosed in angle brackets:

EXTERNAL\_ADDRESS<31:0> nCS<1>

Bits within a register bit field are enclosed in square brackets: REGISTER\_BITFIELD[3:0] REGISTER\_BIT[0]

Single-bit items have either of two states:

- clear the item contains the value 0b0. To clear a bit, write 0b0 to it.

- set the item contains the value 0b1. To set a bit, write 0b1 to it.

### 1.1.3 Applicable Documents

Table 1-1 lists supplemental information sources for the PXA270 processor. Contact an Intel representative for the latest document revisions and ordering instructions.

#### **Table 1-1. Supplemental Documentation**

| Intel® PXA27x Processor F                                          | Family Developers Manual                                                                                                              |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| ARM <sup>®</sup> Architecture Version<br>Architecture Reference Ma | <i>5T Specification</i> (Document number ARM* DDI 0100D-10), and <i>ARM</i> <sup>®</sup> <i>nual</i> (Document number ARM* DDI 0100B) |

| Intel <sup>®</sup> XScale™ Core Deve                               | loper's Manual                                                                                                                        |

| Intel® Wireless MMX™ Teo                                           | chnology Developer's Guide                                                                                                            |

| Intel® PXA27x Processor L                                          | Design Guide                                                                                                                          |

| Intel® PXA27x Processor F                                          | Power Supply Requirements Application Note                                                                                            |

**§§**

The Intel® PXA270 processor is an integrated system-on-a-chip microprocessor for high performance, dynamic, low-power portable handheld and hand-set devices as well as embedded platforms. It incorporates the Intel XScale® technology which complies with the ARM\* version 5TE instruction set (excluding floating-point instructions) and follows the ARM\* programmer's model. The PXA270 processor also provides Intel® Wireless MMX<sup>TM</sup> media enhancement technology, which supports integer instructions to accelerate audio and video processing. In addition, it incorporates Wireless Intel Speedstep® Technology, which provides sophisticated power management capabilities enabling excellent MIPs/mW performance.

The PXA270 processor provides a scalable, bi-directional data interface to a cellular baseband processor, supporting seven logical channels and other features. The operating-system (OS) timer channels and synchronous serial ports (SSPs) also accept an external network clock input so that they can be synchronized to the cellular network. The processor also provides a Universal Subscriber Identity Module\* (USIM) card interface.

The PXA270 processor memory interface gives designers flexibility as it supports a variety of external memory types. The processor also provides four 64 kilobyte banks of on-chip SRAM, which can be used for program code or multimedia data. Each bank can be configured independently to retain its contents when the processor enters a low-power mode. An integrated LCD panel controller supports displays up to 800 by 600 pixels, permitting 1-, 2-, 4-, and 8-bit gray scale and 1-, 2-, 4-, 8-, 16-, 18-, and 24-bit color pixels. A 256-byte palette RAM provides flexible color mapping.

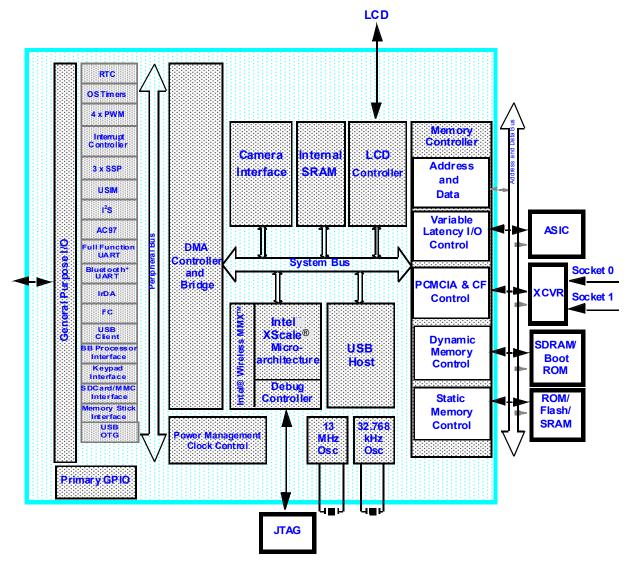

A set of serial devices and general-system resources offers computational and connectivity capability for a variety of applications. Figure 2-1 shows the block diagram for a typical PXA270 processor system.

#### Figure 2-1. Intel® PXA270 Processor Block Diagram, Typical System

**§§**

This chapter provides the mechanical specifications for the PXA270 processor.

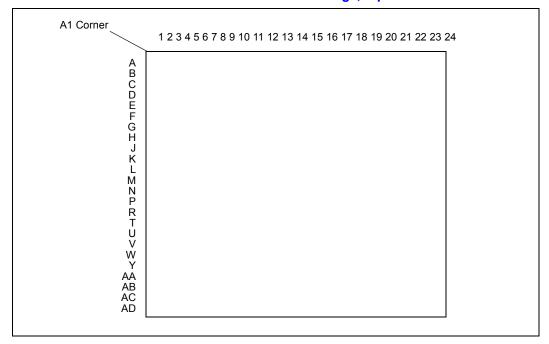

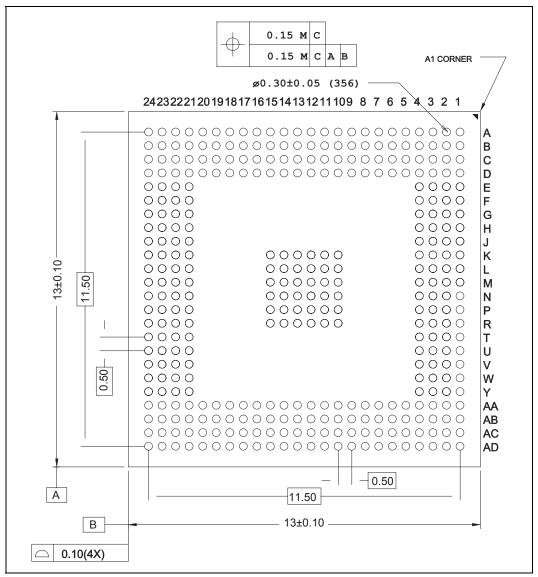

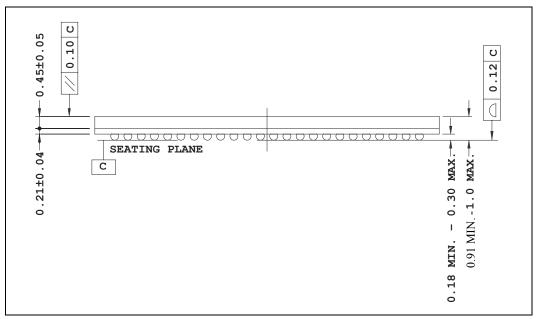

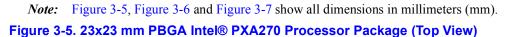

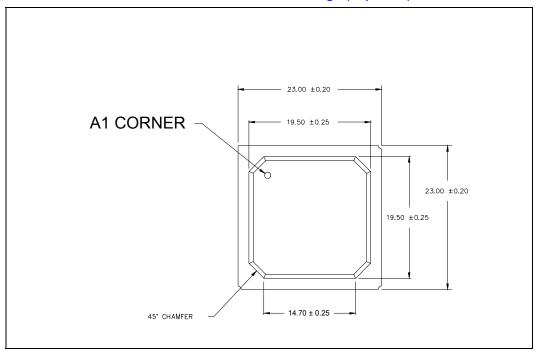

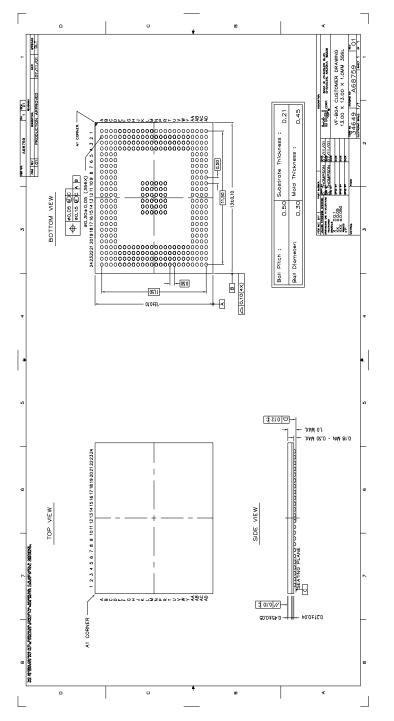

The PXA270 processor is offered in two packages. The 13- by 13-mm, 356-ball, 0.50-mm VF-BGA molded matrix array package is shown in Figure 3-1, Figure 3-2, and Figure 3-3. The 23- by 23-mm, 360-ball, 1.0-mm PBGA molded matrix array package is shown in Figure 3-5, Figure 3-6, and Figure 3-7.

# 3.1 Package Information

#### Figure 3-1. 13x13mm VF-BGA Intel® PXA270 Processor Package, top view

*Note:* Figure 3-2 and Figure 3-3 show all dimensions in millimeters (mm).

#### Figure 3-2. 13x13mm VF-BGA Intel® PXA270 Processor Package, bottom view

#### Figure 3-3. 13x13mm VF-BGA Intel® PXA270 Processor Package, side view

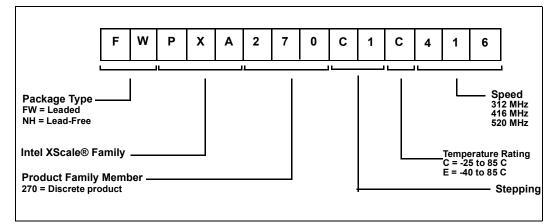

#### Figure 3-4. VF-BGA Product Information Decoder

Figure 3-6. 23x23 mm PBGA Intel® PXA270 Processor Package (Bottom View)

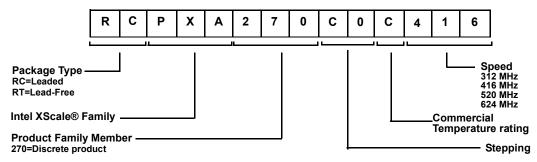

#### Figure 3-8. PBGA Product Information Decoder

## 3.2 **Processor Materials**

Table 3-1 describes the basic material properties of the processor components.

#### **Table 3-1. Processor Material Properties**

| Component             | VF-BGA Material              | PBGA Material                |

|-----------------------|------------------------------|------------------------------|

| Mold compound         | ShinEtsu KMC 2500 VAT1       | Sumitomo G770LE              |

| Solder balls(Leaded)  | 63% Sn/37% Pb                | 63% Sn/37% Pb                |

| Solder balls(Pb-free) | 94.5% Sn / 5.0% Ag / 0.5% Cu | 94.5% Sn / 5.0% Ag / 0.5% Cu |

# 3.3 Junction To Case Temperature Thermal Resistance

| Parameter | VF-BGA Value and Units | PBGA Value and Units |

|-----------|------------------------|----------------------|

| Theta Jc  | 2 degrees C / watt     | 1.4 degrees C / watt |

# 3.4 **Processor Markings**

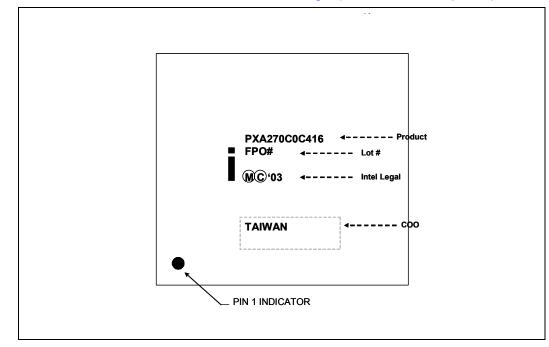

The diagram in this section details the processor's top markings, which identify the PXA270 processor in the 356-ball VF-BGA and 360-ball PBGA package. Refer to Figure 3-4 for product information. A Pb-Free (lead-free) package is indicated by the letter "E" on the 3rd line of information (Intel legal line). The "E" appears after the date stamp.

#### Figure 3-10. Intel® PXA270 Processor Production Markings, (Laser Mark on Top Side)

# 3.5 Tray Drawing

For tray drawing information, refer to the Intel Developer website for the Intel® Wireless Communications and Computing Package Users Guide.

**§§**

# **Pin Listing and Signal Definitions**

This chapter describes the signals and pins for the Intel® PXA270 processor.

For descriptions of all PXA270 processor signals, refer to the "System Architecture" chapter in the *Intel*® *PXA27x Processor Family Developer's Manual*.

Table 4-2 lists the mapping of signals to specific package pins. Many of the package pins are multiplexed so that they can be configured for use as a general-purpose I/O signal or as one of two or three alternate functions using the GPIO alternate-function select registers. Some signals can be configured to appear on one of several different package pins.

4

# 4.1 Ball Map View

*Note:* In the following ball map figures the lowercase letter "n", which normally indicates negation, appears as uppercase "N".

### 4.1.1 13x13 mm VF-BGA Ball map

Figure 4-1 through Figure 4-4 shows the ball map for the VF-BGA PXA270 processor.

#### Figure 4-1. 13x13 mm VF-BGA Ball Map, Top View (upper left quarter)

|   | 1        | 2        | 3        | 4        | 5        | 6        | 7        | 8        | 9        | 10       | 11       | 12       |

|---|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| А | VSS_CORE | VSS_CORE | GPIO<15> | VCC_MEM  | VCC_SRAM | MA<1>    | VCC_CORE | VCC_SRAM | VCC_SRAM | GPIO<49> | GPI0<47> | VCC_IO   |

| в | VSS_CORE | VSS_CORE | NCS<0>   | VCC_SRAM | VSS_CORE | GPIO<33> | GPIO<78> | VCC_MEM  | GPIO<18> | GPIO<12> | GPIO<46> | VCC_CORE |

| С | MA<18>   | MA<22>   | VCC_MEM  | MA<24>   | VSS_MEM  | MA<0>    | GPIO<80> | GPIO<79> | RDNWR    | GPIO<13> | GPIO<11> | GPIO<31> |

| D | MA<17>   | MA<21>   | VCC_CORE | MA<23>   | VSS_MEM  | MA<25>   | VSS_CORE | VSS_CORE | VSS_MEM  | VSS_CORE | VSS_IO   | VSS_CORE |

| E | MA<13>   | VCC_MEM  | MA<19>   | MA<20>   |          |          |          |          |          |          |          |          |

| F | VCC_MEM  | MA<14>   | MA<16>   | VSS_MEM  |          |          |          |          |          |          |          |          |

| G | MA<8>    | MA<11>   | MA<12>   | MA<15>   |          |          |          |          |          |          |          |          |

| н | VCC_MEM  | MA<9>    | MA<10>   | VSS_MEM  |          |          |          |          |          |          |          |          |

| J | MA<3>    | MA<6>    | MA<7>    | VSS_MEM  |          |          |          |          |          |          |          |          |

| к | MD<15>   | MA<4>    | MA<5>    | MA<2>    |          |          |          |          |          | VSS_CORE | VSS_CORE | VSS_CORE |

| L | MD<14>   | MD<31>   | VCC_MEM  | VSS_MEM  |          |          |          |          |          | VSS_CORE | VSS_CORE | VSS_CORE |

| м | VCC_MEM  | MD<30>   | MD<29>   | MD<13>   |          |          |          |          |          | VSS_CORE | VSS_CORE | VSS_CORE |

### Figure 4-2. 13x13 mm VF-BGA Ball Map, Top View (upper right quarter)

| 13        | 14       | 15       | 16       | 17        | 18        | 19       | 20        | 21        | 22        | 23        | 24        |   |

|-----------|----------|----------|----------|-----------|-----------|----------|-----------|-----------|-----------|-----------|-----------|---|

| GPIO<113> | GPIO<28> | GPIO<37> | VCC_IO   | GP10<24>  | GPIO<16>  | GPIO<92> | GPIO<32>  | GPIO<34>  | GPIO<118> | VCC_USB   | VCC_USB   | А |

| GPIO<29>  | GPIO<38> | GPIO<26> | GPIO<23> | GPIO<110> | GPIO<112> | GPIO<35> | GPIO<44>  | VCC_CORE  | USBC_P    | VCC_USB   | VCC_USB   | в |

| GPIO<30>  | GPIO<36> | GPIO<27> | GPI0<17> | GPIO<111> | GPIO<41>  | GPIO<45> | USBC_N    | GPI0<42>  | GPIO<43>  | GPIO<88>  | GPIO<116> | с |

| GPIO<22>  | GPIO<40> | VSS_IO   | GPIO<25> | GPIO<109> | VSS_IO    | GPIO<39> | GPIO<117> | VSS_CORE  | GPIO<89>  | USBH_N<1> | GPIO<114> | D |

|           |          |          |          |           |           |          |           | GPIO<115> | USBH_P<1> | UIO       | VCC_USIM  | E |

|           |          |          |          |           |           |          |           | VSS_IO    | GPIO<90>  | GPIO<91>  | VCC_CORE  | F |

|           |          |          |          |           |           |          |           | VSS_CORE  | GPIO<59>  | GPIO<60>  | GPIO<58>  | G |

|           |          |          |          |           |           |          |           | VSS_IO    | GPIO<62>  | GPIO<63>  | GPIO<61>  | н |

|           |          |          |          |           |           |          |           | VSS_CORE  | GPIO<64>  | VCC_CORE  | VCC_LCD   | J |

| VSS_CORE  | VSS_CORE | VSS_CORE |          |           |           |          |           | VSS_CORE  | GPIO<66>  | GPIO<67>  | GPIO<65>  | к |

| VSS_CORE  | VSS_CORE | VSS_CORE |          |           |           |          |           | GPIO<68>  | GPI0<71>  | GPIO<69>  | VCC_CORE  | L |

| VSS_CORE  | VSS_CORE | VSS_CORE |          |           |           |          |           | VSS_CORE  | GPIO<73>  | VCC_CORE  | GPIO<70>  | М |

### Figure 4-3. 13x13 mm VF-BGA Ball Map, Top View (bottom left quarter)

| N  | MD<27>  | MD<28>   | MD<12>   | VSS_MEM  |          |          |          |          |          | VSS_CORE | VSS_CORE | VSS_CORE |

|----|---------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Р  | VCC_MEM | MD<11>   | MD<26>   | MD<10>   |          |          |          |          |          | VSS_CORE | VSS_CORE | VSS_CORE |

| R  | MD<24>  | VSS_MEM  | MD<25>   | MD<9>    |          |          |          |          |          | VSS_CORE | VSS_CORE | VSS_CORE |

| т  | MD<23>  | VCC_CORE | MD<8>    | VSS_MEM  |          |          |          |          |          |          |          |          |

| U  | MD<7>   | VCC_MEM  | VSS_CORE | MD<5>    |          |          |          |          |          |          |          |          |

| v  | MD<21>  | MD<22>   | MD<6>    | VSS_MEM  |          |          |          |          |          |          |          |          |

| w  | MD<20>  | VCC_MEM  | VCC_CORE | VSS_CORE |          |          |          |          |          |          |          |          |

| Y  | MD<19>  | MD<4>    | MD<3>    | VSS_MEM  |          |          |          |          |          |          |          |          |

| AA | MD<18>  | VCC_MEM  | MD<2>    | MD<16>   | VSS_MEM  | NSDCAS   | VSS_CORE | VSS_MEM  | VSS_MEM  | GPIO<55> | GPIO<84> | VSS_CORE |

| АВ | MD<1>   | VSS_MEM  | MD<17>   | MD<0>    | NWE      | GPIO<20> | NSDCS<0> | NSDCS<1> | DQM<0>   | DQM<1>   | GPIO<56> | GPIO<81> |

| AC | VCC_MEM | VCC_MEM  | VSS_MEM  | SDCLK<0> | NOE      | VCC_MEM  | NSDRAS   | VCC_MEM  | DQM<2>   | DQM<3>   | GPIO<57> | GPIO<85> |

| AD | VCC_MEM | VCC_MEM  | SDCLK<2> | VCC_CORE | GPIO<21> | SDCKE    | SDCLK<1> | VCC_MEM  | GPIO<82> | GPIO<83> | VCC_CORE | VCC_BB   |

|    | 1       | 2        | 3        | 4        | 5        | 6        | 7        | 8        | 9        | 10       | 11       | 12       |

| VSS_CORE | VSS_CORE  | VSS_CORE  |           |           |           |          |                | VSS_IO         | GPIO<86>       | GPIO<87>  | GPI0<72>        | N  |

|----------|-----------|-----------|-----------|-----------|-----------|----------|----------------|----------------|----------------|-----------|-----------------|----|

| VSS_CORE | VSS_CORE  | VSS_CORE  |           |           |           |          |                | VSS_CORE       | GPIO<76>       | GPIO<75>  | VCC_LCD         | Ρ  |

| VSS_CORE | VSS_CORE  | VSS_CORE  |           |           |           |          |                | GPIO<77>       | GPIO<19>       | GPI0<74>  | VCC_CORE        | R  |

|          |           |           |           |           |           |          |                | TMS            | тск            | TESTCLK   | GPIO<14>        | т  |

|          |           |           |           |           |           |          |                | NTRST          | GPIO<9>        | TDI       | VSS_IO          | U  |

|          |           |           |           |           |           |          |                | VSS            | GPIO<0>        | GPIO<10>  | TDO             | v  |

|          |           |           |           |           |           |          |                | GPIO<3>        | NVDD_FAUL<br>T | GPIO<4>   | CLK_REQ         | w  |

|          |           |           |           |           |           |          |                | NRESET_O<br>UT | NRESET         | PWR_EN    | GPIO<1>         | Y  |

| VSS_BB   | GPIO<54>  | VSS_CORE  | VSS_IO    | GPIO<97>  | GPIO<95>  | VSS_IO   | PWR_CAP<<br>3> | VSS            | TXTAL_IN       | TXTAL_OUT | SYS_EN          | АА |

| GPIO<50> | GPIO<53>  | GPIO<106> | GPIO<105> | GPIO<102> | GPIO<99>  | GPIO<93> | VCC_BATT       | PWR_CAP<<br>0> | PWR_OUT        | BOOT_SEL  | NBATT_FAU<br>LT | АВ |

| GPIO<48> | GPIO<52>  | GPIO<107> | GPIO<103> | GPIO<101> | GPIO<100> | GPIO<96> | VCC_PLL        | PXTAL_IN       | PWR_CAP<<br>2> | VSS       | VSS             | AC |

| GPIO<51> | GPIO<108> | GPIO<104> | VCC_CORE  | VCC_IO    | GPIO<98>  | GPIO<94> | VSS_PLL        | PXTAL_OUT      | PWR_CAP<<br>1> | VSS       | VSS             | AD |

| 13       | 14        | 15        | 16        | 17        | 18        | 19       | 20             | 21             | 22             | 23        | 24              |    |

### Figure 4-4. 13x13 mm VF-BGA Ball Map, Top View (bottom right quarter)

# 4.1.2 23x23 mm PBGA Ball map

| Figure 4-5 | . 23x23 mm PBGA Ball Map, Top View (Upper Left Quarter) |

|------------|---------------------------------------------------------|

|            |                                                         |

|   | 1       | 2       | 3       | 4        | 5        | 6        | 7        | 8        | 9        | 10        | 11       |

|---|---------|---------|---------|----------|----------|----------|----------|----------|----------|-----------|----------|

| A | VSS_MEM | VSS_MEM | MA[25]  | GPIO[15] | GPIO[79] | GPIO[13] | GPIO[12] | GPIO[11] | GPIO[46] | GPIO[113] | GPI0[29] |

| в | VSS_MEM | VCC_MEM | VSS_MEM | VCC_RAM  | MA[1]    | VSS_MEM  | VCC_RAM  | VCC_RAM  | VSS_MEM  | VCC_IO    | GPIO[30] |

| с | MA[16]  | MA[17]  | VCC_MEM | MA[24]   | VCC_RAM  | VCC_MEM  | GPIO[33] | RDNWR    | VCC_MEM  | GPIO[47]  | GPIO[31] |

| D | MA[14]  | MA[15]  | MA[19]  | MA[22]   | MA[0]    | NCS_0    | GPIO[80] | GPIO[78] | GPIO[18] | GPIO[49]  | VCC_CORE |

| E | MA[11]  | MA[12]  | MA[21]  | MA[23]   | VSS_CORE | VCC_CORE | VSS_CORE | VCC_CORE | VSS_CORE |           |          |

| F | MA[9]   | VSS_MEM | VCC_MEM | MA[20]   | VCC_CORE |          |          |          |          |           |          |

| G | MA[7]   | MA[8]   | MA[13]  | MA[18]   | VSS_CORE |          |          |          |          |           |          |

| н | MA[4]   | VSS_MEM | VCC_MEM | MA[10]   | VCC_CORE |          |          |          |          |           |          |

| J | MA[3]   | MA[2]   | MA[6]   | MA[5]    | VSS_CORE |          |          |          | VSS_CORE | VSS_CORE  | VSS_CORE |

| к | MD[15]  | MD[30]  | VCC_MEM | MD[31]   |          |          |          |          | VSS_CORE | VSS_CORE  | VSS_CORE |

| L | MD[14]  | VSS_MEM | MD[29]  | VCC_CORE |          |          |          |          | VSS_CORE | VSS_CORE  | VSS_CORE |

| 12       | 13       | 14       | 15        | 16        | 17        | 18        | 19        | 20        | 21        | 22        |   |

|----------|----------|----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|---|

| GPIO[22] | GPIO[38] | GPIO[26] | GPIO[25]  | GPIO[23]  | GPIO[111] | GPIO[92]  | GPIO[41]  | GPIO[44]  | VCC_USB   | VCC_USB   | А |

| VSS_IO   | GPIO[36] | GPIO[24] | VSS_IO    | GPIO[112] | GPI0[39]  | VSS_IO    | GPIO[34]  | GPIO[118] | GPIO[43]  | VCC_USB   | в |

| GPIO[40] | GPIO[27] | GPIO[16] | GPIO[110] | GPIO[32]  | GPIO[45]  | GPIO[117] | NC        | NC        | GPIO[89]  | GPIO[88]  | с |

| GPIO[28] | GPI0[37] | VCC_IO   | GPIO[17]  | GPIO[109] | GPIO[35]  | USBC_P    | VCC_USB   | GPIO[42]  | VSS_IO    | USBH_N[1] | D |

|          |          | VSS_CORE | VCC_CORE  | VSS_CORE  | VCC_CORE  | VSS_CORE  | USBC_N    | GPIO[116] | GPIO[115] | USBH_P[1] | E |

|          |          |          |           |           |           | VCC_CORE  | GPIO[114] | UIO       | VCC_USIM  | GPIO[61]  | F |

|          |          |          |           |           |           | VSS_CORE  | GPIO[91]  | GPIO[58]  | GPIO[60]  | GPIO[62]  | G |

|          |          |          |           |           |           | VCC_CORE  | GPIO[90]  | GPIO[59]  | VSS_IO    | GPIO[64]  | н |

| /SS_CORE | VSS_CORE | VSS_CORE |           |           |           | VSS_CORE  | GPIO[66]  | GPIO[63]  | VCC_LCD   | GPIO[69]  | J |

| /SS_CORE | VSS_CORE | VSS_CORE |           |           |           |           | GPIO[67]  | GPIO[65]  | GPI0[68]  | GPIO[70]  | к |

| SS_CORE  | VSS_CORE | VSS_CORE |           |           |           |           | VCC_CORE  | GPIO[71]  | GPI0[72]  | GPIO[73]  | L |

### Figure 4-6. 23x23 mm PBGA Ball Map, Top View (Upper Right Quarter)

| м  | MD[13]  | MD[11]  | VCC_MEM  | MD[12]   |          |          |          |          | VSS_CORE | VSS_CORE | VSS_CORE |

|----|---------|---------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| N  | MD[28]  | MD[26]  | MD[24]   | MD[25]   |          |          |          |          | VSS_CORE | VSS_CORE | VSS_CORE |

| Р  | MD[27]  | VSS_MEM | VCC_MEM  | MD[8]    | VSS_CORE |          |          |          | VSS_CORE | VSS_CORE | VSS_CORE |

| R  | MD[10]  | MD[23]  | MD[21]   | MD[7]    | VCC_CORE |          |          |          |          |          |          |

| т  | MD[9]   | VSS_MEM | VCC_MEM  | MD[5]    | VSS_CORE |          |          |          |          |          |          |

| U  | MD[22]  | MD[6]   | MD[4]    | MD[2]    | VCC_CORE |          |          |          |          |          |          |

| v  | MD[20]  | VSS_MEM | VCC_MEM  | MD[16]   | VSS_CORE | VCC_CORE | VSS_CORE | VCC_CORE | VSS_CORE |          |          |

| w  | MD[19]  | MD[18]  | MD[1]    | MD[0]    | GPIO[20] | NSDRAS   | SDCKE    | DQM[0]   | GPIO[55] | GPIO[81] | VCC_CORE |

| Y  | MD[3]   | MD[17]  | VCC_MEM  | NSDCAS   | VCC_MEM  | GPIO[21] | VCC_MEM  | NSDCS[1] | VCC_MEM  | GPIO[84] | GPIO[48] |

| АА | VSS_MEM | VCC_MEM | NWE      | NOE      | NSDCS[0] | VSS_MEM  | DQM[1]   | GPIO[82] | VSS_MEM  | GPIO[85] | VCC_BB   |

| AB | VSS_MEM | VSS_MEM | SDCLK[0] | SDCLK[2] | SDCLK[1] | DQM[2]   | DQM[3]   | GPIO[56] | GPIO[57] | GPIO[83] | VSS_BB   |

|    | 1       | 2       | 3        | 4        | 5        | 6        | 7        | 8        | 9        | 10       | 11       |

### Figure 4-7. 23x23 mm PBGA Ball Map, Top View (Lower Left Quarter)

| S <b>AB</b>   |

|---------------|

| 5 <b>AA</b>   |

| _out <b>Y</b> |

| en W          |

| [3] <b>V</b>  |

| [10] <b>U</b> |

| [9] <b>T</b>  |

| R             |

| CLK P         |

| [74] <b>N</b> |

| [87] <b>M</b> |

| PIO           |

#### Figure 4-8. 23x23 mm PBGA Ball Map, Top View (Lower Right Quarter)

# 4.2 Pin Use

The pin-use summary shown in Table 4-1 does not include the 36 center balls identified as K10 through R15 (VF-BGA) or J9 through P14 (PBGA), all of which function as VSS\_CORE (see the recommendations for connecting the 36 center balls in the *Intel*® *PXA27x Processor Family Design Guide*).

Each signal's alternate function inputs are shown in the upper section of each signal row and the outputs are shown in the lower section of each signal row. For example, GPIO<48> has a primary input function of CIF\_DD<5> and a secondary output function of nPOE.

| VF-BGA<br>Ball#<br>(13x13) | PBGA<br>Ball#<br>(23x23) | Name   | Туре      | Function<br>After<br>Reset | Primary<br>Function | Secondary<br>Alternate<br>Function | Third<br>Alternate<br>Function | Reset<br>State | Sleep<br>State |

|----------------------------|--------------------------|--------|-----------|----------------------------|---------------------|------------------------------------|--------------------------------|----------------|----------------|

| VCC_MEI                    | М                        |        | 11        |                            |                     | L                                  |                                |                | •              |

| D6                         | A3                       | MA<25> | OCZ       | MA<25>                     | MA<25>              | —                                  | —                              | Refer to T     | able 4-4       |

| C4                         | C4                       | MA<24> | OCZ       | MA<24>                     | MA<24>              |                                    | _                              | Refer to T     | able 4-4       |

| D4                         | E4                       | MA<23> | OCZ       | MA<23>                     | MA<23>              |                                    | —                              | Refer to T     | able 4-4       |

| C2                         | D4                       | MA<22> | OCZ       | MA<22>                     | MA<22>              |                                    | _                              | Refer to T     | able 4-4       |

| D2                         | E3                       | MA<21> | OCZ       | MA<21>                     | MA<21>              |                                    | —                              | Refer to T     | able 4-4       |

| E4                         | F4                       | MA<20> | OCZ       | MA<20>                     | MA<20>              |                                    | _                              | Refer to T     | able 4-4       |

| E3                         | D3                       | MA<19> | OCZ       | MA<19>                     | MA<19>              |                                    | —                              | Refer to T     | able 4-4       |

| C1                         | G4                       | MA<18> | OCZ       | MA<18>                     | MA<18>              |                                    | _                              | Refer to T     | able 4-4       |

| D1                         | C2                       | MA<17> | OCZ       | MA<17>                     | MA<17>              |                                    | _                              | Refer to T     | able 4-4       |

| F3                         | C1                       | MA<16> | OCZ       | MA<16>                     | MA<16>              |                                    | _                              | Refer to T     | able 4-4       |

| G4                         | D2                       | MA<15> | OCZ       | MA<15>                     | MA<15>              |                                    | _                              | Refer to T     | able 4-4       |

| F2                         | D1                       | MA<14> | OCZ       | MA<14>                     | MA<14>              |                                    | _                              | Refer to T     | able 4-4       |

| E1                         | G3                       | MA<13> | OCZ       | MA<13>                     | MA<13>              | —                                  | _                              | Refer to T     | able 4-4       |

| G3                         | E2                       | MA<12> | OCZ       | MA<12>                     | MA<12>              |                                    | _                              | Refer to T     | able 4-4       |

| G2                         | E1                       | MA<11> | OCZ       | MA<11>                     | MA<11>              |                                    | _                              | Refer to T     | able 4-4       |

| H3                         | H4                       | MA<10> | OCZ       | MA<10>                     | MA<10>              |                                    | _                              | Refer to T     | able 4-4       |

| H2                         | F1                       | MA<9>  | OCZ       | MA<9>                      | MA<9>               |                                    | _                              | Refer to T     | able 4-4       |

| G1                         | G2                       | MA<8>  | OCZ       | MA<8>                      | MA<8>               |                                    | _                              | Refer to T     | able 4-4       |

| J3                         | G1                       | MA<7>  | OCZ       | MA<7>                      | MA<7>               |                                    | _                              | Refer to T     | able 4-4       |

| J2                         | J3                       | MA<6>  | OCZ       | MA<6>                      | MA<6>               |                                    | _                              | Refer to T     | able 4-4       |

| K3                         | J4                       | MA<5>  | OCZ       | MA<5>                      | MA<5>               |                                    | —                              | Refer to T     | able 4-4       |

| K2                         | H1                       | MA<4>  | OCZ       | MA<4>                      | MA<4>               |                                    | _                              | Refer to T     | able 4-4       |

| J1                         | J1                       | MA<3>  | OCZ       | MA<3>                      | MA<3>               |                                    | _                              | Refer to T     | able 4-4       |

| K4                         | J2                       | MA<2>  | OCZ       | MA<2>                      | MA<2>               | —                                  | —                              | Refer to T     | able 4-4       |

| A6                         | B5                       | MA<1>  | OCZ       | MA<1>                      | MA<1>               | —                                  | _                              | Refer to T     | able 4-4       |

| C6                         | D5                       | MA<0>  | OCZ       | MA<0>                      | MA<0>               | —                                  | _                              | Refer to T     | able 4-4       |

| L2                         | K4                       | MD<31> | ICOC<br>Z | MD<31>                     | MD<31>              | —                                  | _                              | Refer to T     | able 4-4       |

| M2                         | K2                       | MD<30> | ICOC<br>Z | MD<30>                     | MD<30>              | —                                  | _                              | Refer to T     | able 4-4       |

| М3                         | L3                       | MD<29> | ICOC<br>Z | MD<29>                     | MD<29>              | —                                  | _                              | Refer to T     | able 4-4       |

| N2                         | N1                       | MD<28> | ICOC<br>Z | MD<28>                     | MD<28>              | _                                  | _                              | Refer to T     | able 4-4       |

#### Table 4-1. Pin Use Summary (Sheet 1 of 17)

| VF-BGA<br>Ball#<br>(13x13) | PBGA<br>Ball#<br>(23x23) | Name   | Туре      | Function<br>After<br>Reset | Primary<br>Function | Secondary<br>Alternate<br>Function | Third<br>Alternate<br>Function | Reset<br>State | Sleep<br>State |

|----------------------------|--------------------------|--------|-----------|----------------------------|---------------------|------------------------------------|--------------------------------|----------------|----------------|

| N1                         | P1                       | MD<27> | ICOC<br>Z | MD<27>                     | MD<27>              | —                                  | _                              | Refer to T     | able 4-4       |

| P3                         | N2                       | MD<26> | ICOC<br>Z | MD<26>                     | MD<26>              | —                                  | _                              | Refer to T     | able 4-4       |

| R3                         | N4                       | MD<25> | ICOC<br>Z | MD<25>                     | MD<25>              | —                                  | _                              | Refer to T     | able 4-4       |

| R1                         | N3                       | MD<24> | ICOC<br>Z | MD<24>                     | MD<24>              | —                                  | —                              | Refer to T     | able 4-4       |

| T1                         | R2                       | MD<23> | ICOC<br>Z | MD<23>                     | MD<23>              | —                                  | _                              | Refer to T     | able 4-4       |

| V2                         | U1                       | MD<22> | ICOC<br>Z | MD<22>                     | MD<22>              | —                                  | _                              | Refer to T     | able 4-4       |

| V1                         | R3                       | MD<21> | ICOC<br>Z | MD<21>                     | MD<21>              | —                                  | _                              | Refer to T     | able 4-4       |

| W1                         | V1                       | MD<20> | ICOC<br>Z | MD<20>                     | MD<20>              | —                                  | _                              | Refer to T     | able 4-4       |

| Y1                         | W1                       | MD<19> | ICOC<br>Z | MD<19>                     | MD<19>              | —                                  | _                              | Refer to T     | able 4-4       |

| AA1                        | W2                       | MD<18> | ICOC<br>Z | MD<18>                     | MD<18>              | —                                  | —                              | Refer to T     | able 4-4       |

| AB3                        | Y2                       | MD<17> | ICOC<br>Z | MD<17>                     | MD<17>              | —                                  | _                              | Refer to T     | able 4-4       |

| AA4                        | V4                       | MD<16> | ICOC<br>Z | MD<16>                     | MD<16>              | —                                  | _                              | Refer to T     | able 4-4       |

| K1                         | K1                       | MD<15> | ICOC<br>Z | MD<15>                     | MD<15>              | —                                  | —                              | Refer to T     | able 4-4       |

| L1                         | L1                       | MD<14> | ICOC<br>Z | MD<14>                     | MD<14>              | —                                  | _                              | Refer to T     | able 4-4       |

| M4                         | M1                       | MD<13> | ICOC<br>Z | MD<13>                     | MD<13>              | —                                  | _                              | Refer to T     | able 4-4       |

| N3                         | M4                       | MD<12> | ICOC<br>Z | MD<12>                     | MD<12>              | —                                  | —                              | Refer to T     | able 4-4       |

| P2                         | M2                       | MD<11> | ICOC<br>Z | MD<11>                     | MD<11>              | —                                  | _                              | Refer to T     | able 4-4       |

| P4                         | R1                       | MD<10> | ICOC<br>Z | MD<10>                     | MD<10>              | —                                  | _                              | Refer to T     | able 4-4       |

| R4                         | T1                       | MD<9>  | ICOC<br>Z | MD<9>                      | MD<9>               | —                                  | _                              | Refer to T     | able 4-4       |

| Т3                         | P4                       | MD<8>  | ICOC<br>Z | MD<8>                      | MD<8>               | —                                  | _                              | Refer to T     | able 4-4       |

| U1                         | R4                       | MD<7>  | ICOC<br>Z | MD<7>                      | MD<7>               | —                                  | _                              | Refer to T     | able 4-4       |

| V3                         | U2                       | MD<6>  | ICOC<br>Z | MD<6>                      | MD<6>               | _                                  | -                              | Refer to T     | able 4-4       |

### Table 4-1. Pin Use Summary (Sheet 2 of 17)

| VF-BGA<br>Ball#<br>(13x13) | PBGA<br>Ball#<br>(23x23) | Name         | Туре      | Function<br>After<br>Reset | Primary<br>Function | Secondary<br>Alternate<br>Function | Third<br>Alternate<br>Function | Reset<br>State  | Sleep<br>State |

|----------------------------|--------------------------|--------------|-----------|----------------------------|---------------------|------------------------------------|--------------------------------|-----------------|----------------|

| U4                         | T4                       | MD<5>        | ICOC<br>Z | MD<5>                      | MD<5>               | —                                  | _                              | Refer to T      | able 4-4       |

| Y2                         | U3                       | MD<4>        | ICOC<br>Z | MD<4>                      | MD<4>               | —                                  | —                              | Refer to T      | able 4-4       |

| Y3                         | Y1                       | MD<3>        | ICOC<br>Z | MD<3>                      | MD<3>               | —                                  | _                              | Refer to T      | able 4-4       |

| AA3                        | U4                       | MD<2>        | ICOC<br>Z | MD<2>                      | MD<2>               | —                                  | _                              | Refer to T      | able 4-4       |

| AB1                        | W3                       | MD<1>        | ICOC<br>Z | MD<1>                      | MD<1>               | —                                  | _                              | Refer to T      | able 4-4       |

| AB4                        | W4                       | MD<0>        | ICOC<br>Z | MD<0>                      | MD<0>               | —                                  | _                              | Refer to T      | able 4-4       |

| AC5                        | AA4                      | NOE          | OCZ       | nOE                        | nOE                 |                                    | —                              | Refer to T      | able 4-4       |

| AB5                        | AA3                      | NWE          | OCZ       | nWE                        | nWE                 |                                    | —                              | Refer to T      | able 4-4       |

| AC7                        | W6                       | NSDRAS       | OCZ       | nSDRAS                     | nSDRAS              |                                    | —                              | Refer to T      | able 4-4       |

| AA6                        | Y4                       | NSDCAS       | OCZ       | nSDCAS                     | nSDCAS              | —                                  | _                              | Refer to T      | able 4-4       |

| AB9                        | W8                       | DQM<0>       | OCZ       | DQM<0>                     | DQM<0>              | —                                  | _                              | Refer to T      | able 4-4       |

| AB10                       | AA7                      | DQM<1>       | OCZ       | DQM<1>                     | DQM<1>              | —                                  | _                              | Refer to T      | able 4-4       |

| AC9                        | AB6                      | DQM<2>       | OCZ       | DQM<2>                     | DQM<2>              | —                                  | _                              | Refer to T      | able 4-4       |

| AC10                       | AB7                      | DQM<3>       | OCZ       | DQM<3>                     | DQM<3>              | —                                  | _                              | Refer to T      | able 4-4       |

| AB7                        | AA5                      | NSDCS<<br>0> | OCZ       | nSDCS<0>                   | nSDCS<0>            | —                                  | _                              | Refer to T      | able 4-4       |

| AB8                        | Y8                       | NSDCS<<br>1> | OC        | nSDCS<1>                   | nSDCS<1>            | —                                  | _                              | Refer to T      | able 4-4       |

| AD6                        | W7                       | SDCKE        | OC        | SDCKE                      | SDCKE               | —                                  | —                              | Refer to T      | able 4-4       |

| AC4                        | AB3                      | SDCLK<0<br>> | OC        | SDCLK<0>                   | SDCLK<0>            | —                                  | _                              | Refer to T      | able 4-4       |

| AD7                        | AB5                      | SDCLK<1<br>> | OCZ       | SDCLK<1>                   | SDCLK<1>            | —                                  | _                              | Refer to T      | able 4-4       |

| AD3                        | AB4                      | SDCLK<2<br>> | OC        | SDCLK<2>                   | SDCLK<2>            | —                                  | _                              | Refer to T      | able 4-4       |

| C9                         | C8                       | RDNWR        | OCZ       | RDnWR                      | RDnWR               | —                                  | —                              | Refer to T      | able 4-4       |

| B3                         | D6                       | NCS<0>       | OCZ       | nCS<0>                     | nCS<0>              | —                                  | —                              | Refer to T      | able 4-4       |

|                            |                          |              |           |                            | _                   | —                                  | —                              |                 |                |

| A3                         | A4                       | GPIO<15<br>> | ICOC<br>Z | GPIO<15>                   | nPCE<1>             | nCS<1><br>Refer to<br>Table 4-4    | _                              | Pu-1<br>Note[1] | Note[4         |

| B9                         | D9                       | GPIO<18      | ICOC      | GPIO<18>                   | RDY                 | —                                  | —                              | Pd-0            | Noto I         |

| DЭ                         | Da                       | >            | Z         |                            | _                   | —                                  | —                              | Note[1]         | Note [3        |

### Table 4-1. Pin Use Summary (Sheet 3 of 17)

| VF-BGA<br>Ball#<br>(13x13) | PBGA<br>Ball#<br>(23x23) | Name         | Туре      | Function<br>After<br>Reset | Primary<br>Function               | Secondary<br>Alternate<br>Function | Third<br>Alternate<br>Function | Reset<br>State  | Sleep<br>State |

|----------------------------|--------------------------|--------------|-----------|----------------------------|-----------------------------------|------------------------------------|--------------------------------|-----------------|----------------|

|                            |                          |              |           |                            | DREQ<0>                           | MBREQ                              | —                              |                 |                |

| AB6                        | W5                       | GPIO<20<br>> | ICOC<br>Z | GPIO<20>                   | nSDCS<2><br>Refer to<br>Table 4-4 | _                                  | _                              | Pu-1<br>Note[1] | Note[3]        |

|                            |                          |              |           |                            | —                                 |                                    | —                              |                 |                |

| AD5                        | Y6                       | GPIO<21<br>> | ICOC<br>Z | GPIO<21>                   | nSDCS<3><br>Refer to<br>Table 4-4 | DVAL<0>                            | MBGNT                          | Pu-1<br>Note[1] | Note[3]        |

|                            |                          |              |           |                            | FFRXD <sup>19</sup>               | FFDSR <sup>19</sup>                | _                              |                 |                |

| B6                         | C7                       | GPIO<33<br>> | ICOC<br>Z | GPIO<33>                   | DVAL<1>                           | nCS<5><br>Refer to<br>Table 4-4    | MBGNT                          | Pu-1<br>Note[1] | Note [4]       |

|                            |                          |              |           |                            | —                                 | _                                  | —                              |                 |                |

| A10                        | D10                      | GPIO<49<br>> | ICOC<br>Z | GPIO<49>                   | —                                 | nPWE<br>Refer to<br>Table 4-4      | _                              | Pu-1<br>Note[1] | Note [5]       |

|                            |                          |              |           |                            | —                                 | —                                  | —                              |                 |                |

| В7                         | D8                       | GPIO<78<br>> | ICOC<br>Z | GPIO<78>                   | nPCE<2>                           | nCS<2><br>Refer to<br>Table 4-4    | _                              | Pu-1<br>Note[1] | Note[4]        |

|                            |                          |              |           |                            | —                                 |                                    | —                              |                 |                |

| C8                         | A5                       | GPIO<79<br>> | ICOC<br>Z | GPIO<79>                   | PSKTSEL                           | nCS<3><br>Refer to<br>Table 4-4    | PWM_OUT<br><2>                 | Pu-1<br>Note[1] | Note[4]        |

|                            |                          |              |           |                            | DREQ<1>                           | MBREQ                              | —                              |                 |                |

| C7                         | D7                       | GPIO<80<br>> | ICOC<br>Z | GPIO<80>                   | _                                 | nCS<4><br>Refer to<br>Table 4-4    | PWM_OUT<br><3>                 | Pu-1<br>Note[1] | Note[4]        |

| VCC_BB                     |                          |              |           |                            |                                   |                                    |                                |                 |                |

|                            |                          |              |           |                            | CIF_DD<5>                         |                                    | —                              |                 |                |

| AC13                       | Y11                      | GPIO<48<br>> | ICOC<br>Z | GPIO<48>                   | BB_OB_DAT<1<br>>                  | nPOE<br>Refer to<br>Table 4-4      | _                              | Pu-1<br>Note[1] | Note [5]       |

|                            |                          |              | 1000      |                            | CIF_DD<3>                         | _                                  | SSPSCLK<<br>2>                 | Du 1            |                |

| AB13                       | W12                      | GPIO<50<br>> | ICOC<br>Z | GPIO<50>                   | BB_OB_DAT<2                       | nPIOIR<br>Refer to<br>Table 4-4    | SSPSCLK<<br>2>                 | Pu-1<br>Note[1] | Note [5]       |

|                            |                          |              |           |                            | CIF_DD<2>                         | —                                  | —                              |                 |                |

| AD13                       | AB12                     | GPIO<51<br>> | ICOC<br>Z | GPIO<51>                   | BB_OB_DAT<3<br>>                  | nPIOIW<br>Refer to<br>Table 4-4    | _                              | Pu-1<br>Note[1] | Note [5]       |

### Table 4-1. Pin Use Summary (Sheet 4 of 17)

| VF-BGA<br>Ball#<br>(13x13) | PBGA<br>Ball#<br>(23x23) | Name          | Туре      | Function<br>After<br>Reset | Primary<br>Function | Secondary<br>Alternate<br>Function | Third<br>Alternate<br>Function | Reset<br>State  | Sleep<br>State |

|----------------------------|--------------------------|---------------|-----------|----------------------------|---------------------|------------------------------------|--------------------------------|-----------------|----------------|

| AC14                       | Y12                      | GPIO<52<br>>  | ICOC<br>Z | GPIO<52>                   | CIF_DD<4>           | SSPSCLK<3>                         | —                              | Pd-0<br>Note[1] | Note [3]       |

|                            |                          |               |           |                            | BB_OB_CLK           | SSPSCLK<3>                         | —                              |                 |                |

| AB14                       | AA12                     | GPIO<53<br>>  | ICOC<br>Z | GPIO<53>                   | FFRXD               | USB_P2_3                           | —                              | Pd-0<br>Note[1] | Note [3]       |

|                            |                          |               |           |                            | BB_OB_STB           | CIF_MCLK                           | SSPSYSCL<br>K                  |                 |                |

| AA14                       | AB13                     | GPIO<54<br>>  | ICOC<br>Z | GPIO<54>                   | _                   | BB_OB_WAIT                         | CIF_PCLK                       | Pd-0<br>Note[1] | Note [3]       |