# **DATA SHEET**

# MOS INTEGRATED CIRCUIT $\mu$ PD161660

# POWER SUPPLY FOR TFT-LCD DRIVER

#### **DESCRIPTION**

The  $\mu$ PD161660 is a power supply IC for TFT-LCD driver. This ICs can generate the levels which TFT-LCD driver need, from 2.7 V.

#### **FEATURES**

- To generate 3 levels from single voltage input

- To integrate regulator circuit for source and gate driver

#### **ORDERING INFORMATION**

|   | Part number | Package |

|---|-------------|---------|

| * | μPD161660P  | Chip    |

**Remark** Purchasing the above chip entails the exchange of documents such as a separate memorandum or product quality, so please contact one of our sales representative.

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

*μ*PD161660

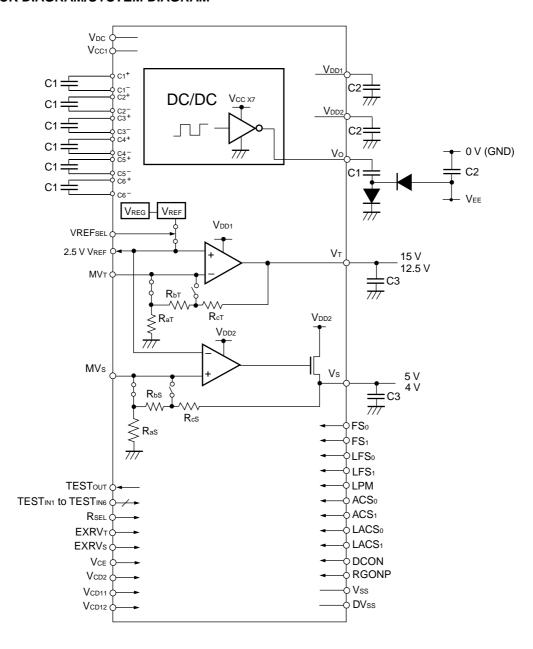

## 1. BLOCK DIAGRAM/SYSTEM DIAGRAM

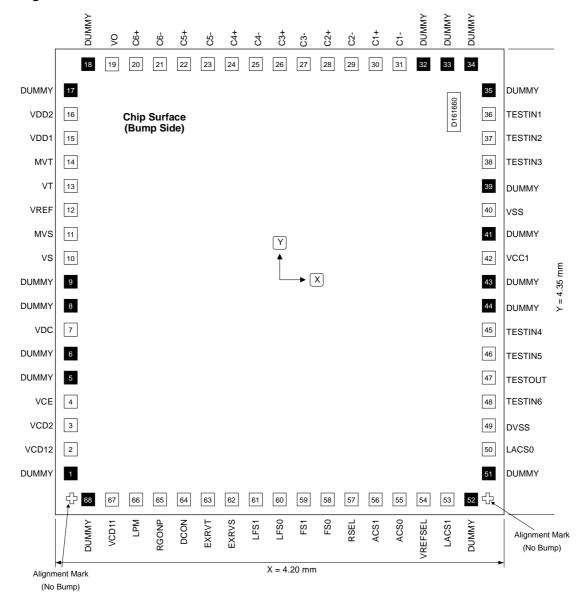

## 2. PIN CONFIGURATION (Pad Layout)

Chip size: X = 4.20 mm, Y = 4.35 mm

Pad size :  $100 \times 100 \, \mu \text{m}^2$

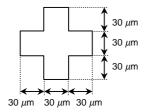

#### (1) Alignment mark

## (2) Arrangement

$\mu$ PD161660

Table 2-1. Pad Layout

| Pad No. | Pad name        | X[mm] | Y[mm] |

|---------|-----------------|-------|-------|

| 1       | DUMMY           | -1950 | -1800 |

| 2       | VCD12           | -1950 | -1575 |

| 3       | VCD2            | -1950 | -1350 |

| 4       | VCE             | -1950 | -1125 |

| 5       | DUMMY           | -1950 | -900  |

| 6       | DUMMY           | -1950 | -675  |

| 7       | VDC             | -1950 | -450  |

| 8       | DUMMY           | -1950 | -225  |

| 9       | DUMMY           | -1950 | 0     |

| 10      | Vs              | -1950 | 225   |

| 11      | MVs             | -1950 | 450   |

| 12      | VREF            | -1950 | 675   |

| 13      | VT              | -1950 | 900   |

| 14      | MVT             | -1950 | 1125  |

| 15      | VDD1            | -1950 | 1350  |

| 16      | VDD2            | -1950 | 1575  |

| 17      | DUMMY           | -1950 | 1800  |

| 18      | DUMMY           | -1800 | 2025  |

| 19      | Vo              | -1575 | 2025  |

| 20      | C6 <sup>+</sup> | -1350 | 2025  |

| 21      | C6 <sup>-</sup> | -1125 | 2025  |

| 22      | C5 <sup>+</sup> | -900  | 2025  |

| 23      | C5 <sup>-</sup> | -675  | 2025  |

| 24      | C4 <sup>+</sup> | -450  | 2025  |

| 25      | C4 <sup>-</sup> | -225  | 2025  |

| 26      | C3 <sup>+</sup> | 0     | 2025  |

| 27      | C3 <sup>-</sup> | 225   | 2025  |

| 28      | C2 <sup>+</sup> | 450   | 2025  |

| 29      | C2 <sup>-</sup> | 675   | 2025  |

| 30      | C1 <sup>+</sup> | 900   | 2025  |

| 31      | C1 <sup>-</sup> | 1125  | 2025  |

| 32      | DUMMY           | 1350  | 2025  |

| 33      | DUMMY           | 1575  | 2025  |

| 34      | DUMMY           | 1800  | 2025  |

| 35      | DUMMY           | 1950  | 1800  |

| 36      | TESTIN1         | 1950  | 1575  |

| 37      | TESTIN2         | 1950  | 1350  |

| 38      | TESTIN3         | 1950  | 1125  |

| 39      | DUMMY           | 1950  | 900   |

| 40      | Vss             | 1950  | 675   |

| Pad No. | Pad name          | X[mm] | Y[mm] |

|---------|-------------------|-------|-------|

| 41      | DUMMY             | 1950  | 450   |

| 42      | Vcc1              | 1950  | 225   |

| 43      | DUMMY             | 1950  | 0     |

| 44      | DUMMY             | 1950  | -225  |

| 45      | TESTIN4           | 1950  | -450  |

| 46      | TESTIN5           | 1950  | -675  |

| 47      | TESTout           | 1950  | -900  |

| 48      | TESTIN6           | 1950  | -1125 |

| 49      | DVss              | 1950  | -1350 |

| 50      | LACS <sub>0</sub> | 1950  | -1575 |

| 51      | DUMMY             | 1950  | -1800 |

| 52      | DUMMY             | 1800  | -2025 |

| 53      | LACS1             | 1575  | -2025 |

| 54      | VREFSEL           | 1350  | -2025 |

| 55      | ACS <sub>0</sub>  | 1125  | -2025 |

| 56      | ACS <sub>1</sub>  | 900   | -2025 |

| 57      | RSEL              | 675   | -2025 |

| 58      | FS <sub>0</sub>   | 450   | -2025 |

| 59      | FS <sub>1</sub>   | 225   | -2025 |

| 60      | LFS <sub>0</sub>  | 0     | -2025 |

| 61      | LFS1              | -225  | -2025 |

| 62      | EXRVS             | -450  | -2025 |

| 63      | EXRVT             | -675  | -2025 |

| 64      | DCON              | -900  | -2025 |

| 65      | RGONP             | -1125 | -2025 |

| 66      | LPM               | -1350 | -2025 |

| 67      | VCD11             | -1575 | -2025 |

| 68      | DUMMY             | -1800 | -2025 |

|         | Alignment mark    | -1950 | -2025 |

|         | Alignment mark    | 1950  | -2025 |

# 3. PIN FUNCTIONS

(1/2)

| Symbol                                | Pin Name                    | Pad No. | I/O | Description                                                                    |

|---------------------------------------|-----------------------------|---------|-----|--------------------------------------------------------------------------------|

| VDC                                   | Power supply                | 7       | -   | Power supply for DC/DC converter.                                              |

| Vcc1                                  | Power supply                | 42      | _   | Power supply for logic circuit.                                                |

| Vss                                   | Ground                      | 40      | -   | Ground.                                                                        |

| DVss                                  | Ground                      | 49      | _   | Ground (for control pin pull-down)                                             |

| V <sub>DD1</sub>                      | DC/DC converter output      | 15      |     | Boost voltage of DC/DC converter (x4, x5, x6 or x7).                           |

|                                       |                             |         |     | The capacitors required for each boost level are shown                         |

|                                       |                             |         |     | below.                                                                         |

|                                       |                             |         |     | • x4 boost: C1, C2, C6 (C3, C4, and C5 are not required)                       |

|                                       |                             |         |     | • x5 boost: C1, C2, C3, C6 (C4, and C5 are not required)                       |

|                                       |                             |         |     | • x6 boost: C1, C2, C3, C4, C6 (C5 is not required)                            |

|                                       |                             |         |     | • x7 boost: C1, C2, C3, C4, C5, C6                                             |

| V <sub>DD2</sub>                      | DC/DC converter output      | 16      | -   | Boost voltage of DC/DC converter (x2 or x3). The boost                         |

|                                       |                             |         |     | steps for V <sub>DD2</sub> is selected by V <sub>CD2</sub> pin. The capacitors |

|                                       |                             |         |     | required for each boost level are shown below.                                 |

|                                       |                             |         |     | • x2 boost: C1                                                                 |

|                                       |                             |         |     | • x3 boost: C1, C2,                                                            |

| Vo                                    | Rectangle signal output for | 19      | -   | Rectangle signal output for negative boost. The Vo voltage                     |

|                                       | negative boost              |         |     | range is selected by VcE pin. The capacitors required for                      |

|                                       |                             |         |     | each boost level are shown below.                                              |

|                                       |                             |         |     | <vce =="" l=""></vce>                                                          |

|                                       |                             |         |     | • x3 boost: C1, C2                                                             |

|                                       |                             |         |     | • x4 boost: C1, C2, C3                                                         |

|                                       |                             |         |     | • x5 boost: C1, C2, C3, C4                                                     |

|                                       |                             |         |     | • x6 boost: C1, C2, C3, C4, C5                                                 |

|                                       |                             |         |     | <vce =="" h=""></vce>                                                          |

|                                       |                             |         |     | • x4 boost: C1, C2, C6                                                         |

|                                       |                             |         |     | • x5 boost: C1, C2, C3, C6                                                     |

|                                       |                             |         |     | • x6 boost: C1, C2, C3, C4, C6                                                 |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Da sudata a autaut          | 40      |     | • x7 boost: C1, C2, C3, C4, C5, C6                                             |

| VT                                    | Regulator output            | 13      | _   | 15 V/12.5 V regulator output for gate driver.                                  |

| Vs                                    | Regulator output            | 10      | -   | 5 V/4 V regulator output for source driver.                                    |

| VREF                                  | Reference voltage           | 12      | I/O | The gate driver includes reference voltage for V <sub>B</sub> regulator.       |

|                                       | input/output                |         |     | When VREF <sub>SEL</sub> = H, external reference voltage can be                |

|                                       |                             |         |     | input. Reference voltage input/output pin of Vτ, Vs                            |

| DCON                                  | DC/DC convertor control     | 64      | ı   | regulator.                                                                     |

| DCON                                  | DC/DC converter control     | 64      | I   | DC/DC converter ON/OFF control. Connect to DCON pin of source driver.          |

| RGONP                                 | Pagulator control           | 65      | 1   | Regulator ON/OFF control. Connect to RGONP pin of                              |

| NGOINE                                | Regulator control           | US      | '   | source driver.                                                                 |

| EXRV⊤                                 | V⊤ regulating resistor      | 63      | 1   | To select internal/external resistor for V⊤ regulator.                         |

|                                       | selection                   | US      | '   | 10 Select Internal external resistor for VT regulator.                         |

| EXRVs                                 | Vs regulating resistor      | 62      | 1   | To select internal/external resistor for Vs regulator.                         |

| LVII V S                              | vs regulating resistor      | 02      | '   | 10 301001 IIII on all enternal resistor for vs regulator.                      |

Data Sheet S14799E1V0DS

(2/2)

| Symbol                                                    | Pin Name                           | Pad No.    | I/O | Description                                                                                       |

|-----------------------------------------------------------|------------------------------------|------------|-----|---------------------------------------------------------------------------------------------------|

| V <sub>CD11</sub>                                         | V <sub>DD1</sub> booster selection | 67         | ı   | To select x4/x5/x6/x7 boost for V <sub>DD1</sub> . Connect to                                     |

|                                                           |                                    |            |     | V <sub>CD11</sub> pin of source driver.                                                           |

| V <sub>CD12</sub>                                         | V <sub>DD1</sub> booster selection | 2          | I   | To select x4/x5/x6/x7 boost for V <sub>DD1</sub> . Connect to                                     |

|                                                           |                                    |            |     | V <sub>CD12</sub> pin of source driver.                                                           |

| V <sub>CD2</sub>                                          | V <sub>DD2</sub> booster selection | 3          | 1   | To select x2/x3 boost for VDD2. Connect to VCD2 pin                                               |

|                                                           |                                    |            |     | of source driver.                                                                                 |

| Vce                                                       | Vo level selection                 | 4          | 1   | To select x3/x4/x5/x6/x7 boost for Vo top voltage                                                 |

|                                                           |                                    |            |     | level. Connect to VcE pin of source driver.                                                       |

| LPM                                                       | Low power mode signal              | 66         | 1   | Control signal for low power mode.                                                                |

|                                                           |                                    |            |     | When this pin is high level, it comes to be low power                                             |

|                                                           |                                    |            |     | mode.                                                                                             |

|                                                           |                                    |            |     | LPM = H: LACS <sub>0</sub> , LACS <sub>1</sub> , LFS <sub>0</sub> , LFS <sub>1</sub> are enabled. |

|                                                           |                                    |            |     | LPM = L : ACS <sub>0</sub> , ACS <sub>1</sub> , FS <sub>0</sub> , FS <sub>1</sub> are enabled.    |

|                                                           |                                    |            |     | Connect to LPMP pin of source driver.                                                             |

| ACS <sub>0</sub> ,                                        | Amp. current selection             | 55,        | I   | To select Amp. current when in scanning.                                                          |

| ACS <sub>1</sub>                                          |                                    | 56         |     |                                                                                                   |

| LACS <sub>0</sub> ,                                       | Amp. current selection             | 50,        | I   | To select Amp. current in low power mode.                                                         |

| LACS <sub>1</sub>                                         |                                    | 53         |     |                                                                                                   |

| $MV_{T}$                                                  | V⊤ regulator input                 | 14         | _   | EXRV <sub>T</sub> = H: Connect to external resistor.                                              |

|                                                           |                                    |            |     | EXRV <sub>T</sub> = L: Leave it open.                                                             |

| MVs                                                       | Vs regulator input                 | 11         | _   | EXRVs = H: Connect to external resistor.                                                          |

|                                                           |                                    |            |     | EXRVs = L: Leave it open.                                                                         |

| TESTIN1-                                                  | Test                               | 36-38,     | I   | Test pins. Normally leave it open.                                                                |

| TEST <sub>IN6</sub>                                       |                                    | 45, 46, 48 |     |                                                                                                   |

| TESTout                                                   | Test output                        | 47         | 0   | Test pin. Normally leave them open.                                                               |

| FS <sub>0</sub> , FS <sub>1</sub>                         | OSC frequency selection            | 58, 59     | 1   | To select OSC frequency for DC/DC converter when                                                  |

|                                                           |                                    |            |     | in scanning.                                                                                      |

| LFS <sub>0</sub> , LFS <sub>1</sub>                       | OSC frequency selection            | 60, 61     | 1   | To select OSC frequency for DC/DC capacitor when                                                  |

|                                                           |                                    |            |     | in scanning.                                                                                      |

| RSEL                                                      | Internal resistor selection for    | 57         | 1   | To select internal resistor for regulator.                                                        |

|                                                           | regulator                          |            |     |                                                                                                   |

| VREFSEL                                                   | Regulator reference voltage input  | 54         | 1   | To select external or internal reference voltage of                                               |

|                                                           | selection                          |            |     | V⊤, Vs regulator.                                                                                 |

| C <sub>1</sub> <sup>+</sup> , C <sub>1</sub> <sup>-</sup> | Capacitor connect pin for boost    | 30, 31     | _   | To connect external capacitor for DC/DC converter.                                                |

| $C_2^+, C_2^-$                                            | ·                                  | 28, 29     |     | The capacitance and tolerance of each capacitor are                                               |

| C <sub>3</sub> <sup>+</sup> , C <sub>3</sub> <sup>-</sup> |                                    | 26, 27     |     | shown below.                                                                                      |

| C <sub>4</sub> <sup>+</sup> , C <sub>4</sub> <sup>-</sup> |                                    | 24, 25     |     | Capacitance : 1 μF                                                                                |

| C <sub>5</sub> <sup>+</sup> , C <sub>5</sub> <sup>-</sup> |                                    |            |     | , ,                                                                                               |

|                                                           |                                    | 22, 23     |     | Withstanding voltage: 10 V                                                                        |

| C <sub>6</sub> <sup>+</sup> , C <sub>6</sub> <sup>-</sup> |                                    | 20, 21     |     |                                                                                                   |

## 4. MODE DESCRIPTION

# (1) DC/DC converter control

| DCON | Н | DC/DC converter ON  |

|------|---|---------------------|

|      | L | DC/DC converter OFF |

# (2) Regulator control

| RGONP | Н | Regulator ON                                                     |

|-------|---|------------------------------------------------------------------|

|       | L | Regulator OFF (V <sub>T</sub> , V <sub>S</sub> = High impedance) |

# (3) V<sub>T</sub> regulating resistor

| EXRV⊤ | Н | External resistor |

|-------|---|-------------------|

|       | L | Internal resistor |

# (4) Vs regulating resistor

| EXRVs | Н | External resistor |

|-------|---|-------------------|

|       | L | Internal resistor |

# (5) VDD2 booster selection

| V <sub>CD2</sub> | Н | x3 booster |

|------------------|---|------------|

|                  | L | x2 booster |

# (6) V<sub>T</sub>, V<sub>S</sub> regulator selection

|      |   | VT     | Vs    |

|------|---|--------|-------|

| Rsel | Н | 15.0 V | 5.0 V |

|      | L | 12.5 V | 4.0 V |

# (7) Regulator reference voltage input selection

| VREFSEL | Н | V <sub>REF</sub> : External reference voltage input  |

|---------|---|------------------------------------------------------|

|         | Ц | V <sub>REF</sub> : Internal reference voltage output |

# (8) VDD1 and Vo high-level booster selection

| V <sub>CD12</sub> | V <sub>CD11</sub> | Vce | V <sub>DD1</sub> booster | Vo high level      |

|-------------------|-------------------|-----|--------------------------|--------------------|

| Н                 | Н                 | Н   | x7 V <sub>DC</sub>       | x7 V <sub>DC</sub> |

| Н                 | Н                 | L   | x7 V <sub>DC</sub>       | x6 V <sub>DC</sub> |

| Н                 | L                 | Н   | x6 V <sub>DC</sub>       | x6 V <sub>DC</sub> |

| Н                 | L                 | L   | x6 V <sub>DC</sub>       | x5 V <sub>DC</sub> |

| L                 | Н                 | Н   | x5 V <sub>DC</sub>       | x5 V <sub>DC</sub> |

| L                 | Н                 | L   | x5 V <sub>DC</sub>       | x4 V <sub>DC</sub> |

| L                 | L                 | Н   | x4 V <sub>DC</sub>       | x4 V <sub>DC</sub> |

| L                 | L                 | L   | x4 V <sub>DC</sub>       | x3 V <sub>DC</sub> |

## (9) Amp. current selection

|                       |                       | Vт             |                |               | Vs             |                |               |  |

|-----------------------|-----------------------|----------------|----------------|---------------|----------------|----------------|---------------|--|

| ACS <sub>0</sub> Note | ACS <sub>1</sub> Note | Source current | Sink current   | Amp. current  | Source current | Sink current   | Amp. current  |  |

| (LACS <sub>0</sub> )  | (LACS <sub>1</sub> )  |                |                |               |                |                |               |  |

| L                     | L                     | 1 mA >         | 0.5 <i>μ</i> A | 1 <i>μ</i> Α  | 3 mA >         | 0.5 <i>μ</i> A | 1 μΑ          |  |

| L                     | Н                     | 1 mA >         | 1 μΑ           | 2 μΑ          | 3 mA >         | 1 μΑ           | 2 μΑ          |  |

| Н                     | L                     | 1 mA >         | 2.5 μΑ         | 5 μΑ          | 3 mA >         | 2.5 μΑ         | 5 μΑ          |  |

| Н                     | Н                     | 1 mA >         | 5 μΑ           | 10 <i>μ</i> A | 3 mA >         | 5 μΑ           | 10 <i>μ</i> Α |  |

Note ACS0, ACS1 : Current selection in scanning time LACS0, LACS1: Current selection in low power mode

## (10) OSC frequency selection

| FS <sub>1</sub> , LFS <sub>1</sub> Note | FS <sub>0</sub> , LFS <sub>0</sub> Note | osc      |

|-----------------------------------------|-----------------------------------------|----------|

| L                                       | L                                       | fosc/8   |

| L                                       | Н                                       | fosc/2   |

| Н                                       | L                                       | fosc/32  |

| Н                                       | Н                                       | fosc/256 |

Note FS<sub>0</sub>, FS<sub>1</sub> : Current selection when in scanning LFS<sub>0</sub>, LFS<sub>1</sub>: Current selection in low power mode

# (11) Low power mode selection

| LPM | Н | Low power mode                                                                          |

|-----|---|-----------------------------------------------------------------------------------------|

|     |   | LACS <sub>0</sub> , LACS <sub>1</sub> , LFS <sub>0</sub> , LFS <sub>1</sub> are enable. |

|     | L | Normal mode                                                                             |

|     |   | ACS <sub>0</sub> , ACS <sub>1</sub> , FS <sub>0</sub> , FS <sub>1</sub> are enable.     |

NEC  $\mu$ PD161660

Figure 4-1. Example of Internal/External resistor for the regulator

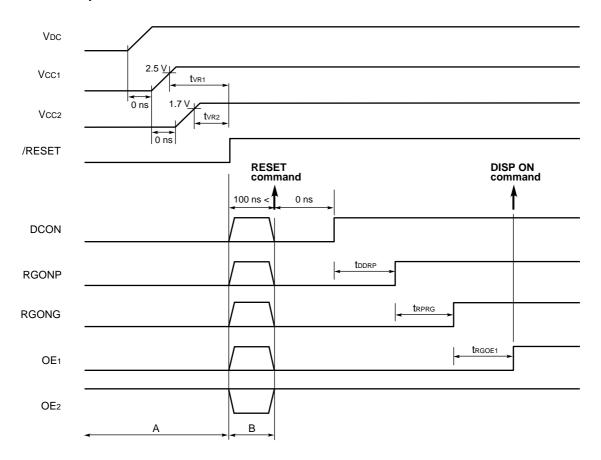

#### 5. POWER ON/OFF SEQUENCE

#### 5.1 Power ON sequence

$t_{VR1}$ ,  $t_{VR2} = 100$  ns MIN.

Remarks 1. /xxx indicates active low signal.

- 2. OE1, OE2, /RESET, RGONG, RGONP, Vcc2 are signals from source driver.

- ① All three power supplies, VDC, VCC1, and VCC2, can be on at the same time.

- @ The pins are fixed to the following levels by the source driver during the period of /RESET = L (A period).

Note that the gate output is fixed to the  $V_B$  level, and the DC/DC converter and the regulators are off.

DCON, RGONG, RGONP, OE1: L (low level)

OE2: H (high level)

- ③ The /RESET pin can be made high at the end of both tvR1, which starts from the rising edge of Vcc1, and tvR2, which starts from the rising edge of Vcc2.

- The wait time between when the /RESET signal rises and when the RESET command is acknowledged must be at least 100 ns.

- ⑤ The logical status of the DCON, RGONG, RGONP, OE₁, and OE₂ pins in the period between when the /RESET signal rises and when the RESET command (↑part) is acknowledged (B period) is undefined. Be aware, therefore,

NEC  $\mu$ PD161660

that the gate output may be undefined and the DC/DC converter and the regulators may be on. If the B period is sufficiently short however, it is unlikely that the display will be affected. Note that the gate output MAX value in the B period must be determined separately as a specification of the LCD module.

The pins are re-fixed to the following levels by the source driver when the RESET command is input.

Note that the gate output is fixed to the V<sub>B</sub> level, and the DC/DC converter and the regulators are off.

DCON, RGONG, RGONP, OE1: L (low level)

OE2: H (high level)

- The set a timing that ensures the DCON, RGONP, and RGONG pins are shifted to high level in that order after the RESET command is input. At this time, the DC/DC converter and the regulators are on. Before that, the booster level must have been set up (by BGRS, VCE, VCD2, PVCOM of R32 register and R34 register of the  $\mu$ PD161620). Note that the target timing of tddrp and trprg (while the DC/DC converter output and regulator output is stable) is tddrp = approx. 50 ms and trprg = approx. 20 ms, but users are requested to set the final timing after sufficiently evaluating the  $\mu$ PD161660 in the LCD module.

- § Input the DISPON command (↑part) after ensuring that all the power supplies are high level.

The source driver will start display with  $OE_1 = H$ .

The target is tregoe1 = approx. 1 ms, but users are requested to set the final timing after sufficiently evaluating the  $\mu$ PD161660 in the LCD module.

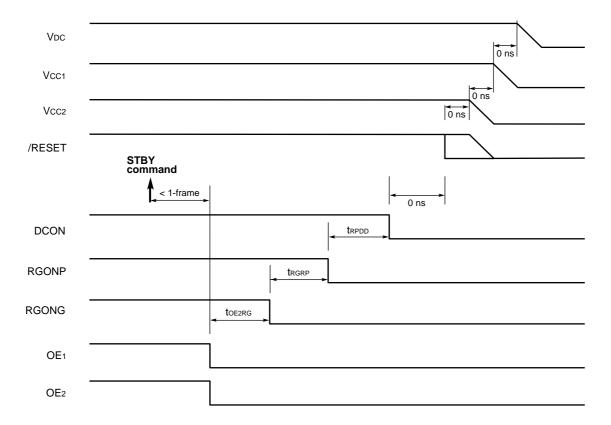

#### 5.2 Power OFF sequence

$\textbf{Remark} \ \ \mathsf{OE_{1}}, \ \mathsf{OE_{2}}, \ \mathsf{/RESET}, \ \mathsf{RGONG}, \ \mathsf{RGONP}, \ \mathsf{Vcc_{2}} \ \mathsf{are} \ \mathsf{the} \ \mathsf{signals} \ \mathsf{from} \ \mathsf{driver}.$

- Input the STBY command (↑part).

- The source driver sets the status of the OE1 and OE2 pins to low level within one frame.

- The gate output is fixed to  $V_T$ .

- ② Set a timing that ensures the RGONG, RGONP, and DCON pins are shifted to low level in that order after the panel load has been sufficiently discharged (toezre timing; Secure an amount of time equivalent to one frame after executing the standby command). At this time, the DC/DC converter and the regulators are off.

- Note that a timing of 0 ns for trgrP and trPDD causes no problems on the device side, but users are requested to set the final timing after sufficiently evaluating the  $\mu$ PD161660 in the LCD module.

- ③ Although it is unnecessary to input the RESET command to the source driver, for designs in which the system is reset when the power supply is turned off, make settings that ensure /RESET = L at DCON = L and subsequent timings.

- 4 All three power supplies, VDC, VCC1, and VCC2, can be off at the same time.

## 6. ELECTRICAL SPECIFICATIONS

## Absolute Maximum Ratings (TA = 25°C, Vss = 0 V)

| Parameter                     | Symbol           | Rating             | Unit |

|-------------------------------|------------------|--------------------|------|

| Supply voltage                | Vcc1             | -0.5 to +6.0       | V    |

| Supply voltage                | V <sub>DC</sub>  | -0.5 to + 6.0      | V    |

| Input voltage                 | Vı               | −0.5 to Vcc₁ + 0.5 | V    |

| Input current                 | h                | ±10                | mA   |

| Output voltage                | V <sub>DD1</sub> | -0.5 to +40        | V    |

| Output current                | lo               | ±10                | mA   |

| Output current                | l <sub>02</sub>  | ±10                | mA   |

| Operating ambient temperature | TA               | -40 to +85         | °C   |

| Storage temperature           | T <sub>stg</sub> | -55 to +125        | °C   |

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

## Recommended Operating Conditions (T<sub>A</sub> = -40 to +85°C, Vss = 0 V)

| Parameter      | Symbol | MIN. | TYP. | MAX.             | Unit |

|----------------|--------|------|------|------------------|------|

| Supply voltage | Vcc1   | 2.5  | 2.7  | 3.6              | V    |

| Supply voltage | VDC    | 2.5  |      | 3.6              | V    |

| Input voltage  | Vı     | 0    |      | Vcc <sub>1</sub> | V    |

# Electrical Characteristics (Unless otherwise specified, $T_A = -40$ to +85°C, $V_{CC1} = 2.5$ to 3.6 V, $V_{SS} = 0$ V)

| Parameter                      | Symbol           | Condition                               | MIN.     | TYP. | MAX.     | Unit |

|--------------------------------|------------------|-----------------------------------------|----------|------|----------|------|

| High level input voltage       | VIH              |                                         | 0.8 Vcc1 |      |          | V    |

| Low level input voltage        | VIL              |                                         |          |      | 0.2 Vcc1 | V    |

| Boost voltage                  | V <sub>DD1</sub> | IDD1 = 300 $\mu$ A, 7 x Boost           | 6 VDC    |      | 7 VDC    | V    |

| Boost voltage                  | V <sub>DD1</sub> | IDD1 = 300 $\mu$ A, 6 x Boost           | 5 VDC    |      | 6 VDC    | V    |

| Boost voltage                  | V <sub>DD1</sub> | IDD1 = 300 $\mu$ A, 5 x Boost           | 4 VDC    |      | 5 VDC    | V    |

| Boost voltage                  | V <sub>DD1</sub> | IDD1 = 300 $\mu$ A, 4 x Boost           | 3 VDC    |      | 4 VDC    | V    |

| Boost voltage                  | V <sub>DD2</sub> | VcD2 = L, IDD2 = 1 mA                   | 1.8 Vpc  |      | 2 VDC    | V    |

| Boost voltage                  | V <sub>DD2</sub> | VcD2 = H, IDD2 = 1 mA                   | 2.7 VDC  |      | 3 VDC    | V    |

| Output voltage                 | VT               | Rsel = H                                | 13.5     | 15   | 16.5     | V    |

| Output voltage                 | VT               | Rsel = L                                | 11.25    | 12.5 | 13.75    | V    |

| Output voltage                 | Vs               | Rsel = H                                | 4.5      | 5    | 5.5      | V    |

| Output voltage                 | Vs               | Rsel = L                                | 3.6      | 4    | 4.4      | V    |

| Vcc1 static current            | lvcc1d           | Vcc1 = 2.7 V,<br>DCON, RGONG, RGONP = L |          |      | 5        | μΑ   |

| V <sub>DC</sub> static current | lvdcd            | VDC = 2.5 V,<br>DCON, RGONG, RGONP = L  |          |      | 5        | μΑ   |

| V <sub>REF</sub> voltage       |                  |                                         | 2.25     | 2.5  | 2.75     | V    |

\*

NEC  $\mu$ PD161660

[MEMO]

#### **NOTES FOR CMOS DEVICES -**

#### (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

# 2 HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.