# 262,144-words $\times$ 18-bits Synchronous Fast Static RAM

# HITACHI

ADE-203-661A(Z) Product Preview Rev. 1 Feb. 21, 1997

#### Features

- $3.3V \pm 5\%$  Operation

- LVCMOS Compatible Input and Output

- Synchronous Operation

- Internal self-timed Late Write

- Asynchronous G Output Control

- Byte Write Control (2 byte write selects, one for each 9 bits)

- Power down mode is provided

- Differential PECL Clock Inputs

- Boundary Scan

- Protocol Single Clock Resister-Latch Mode

## **Ordering Information**

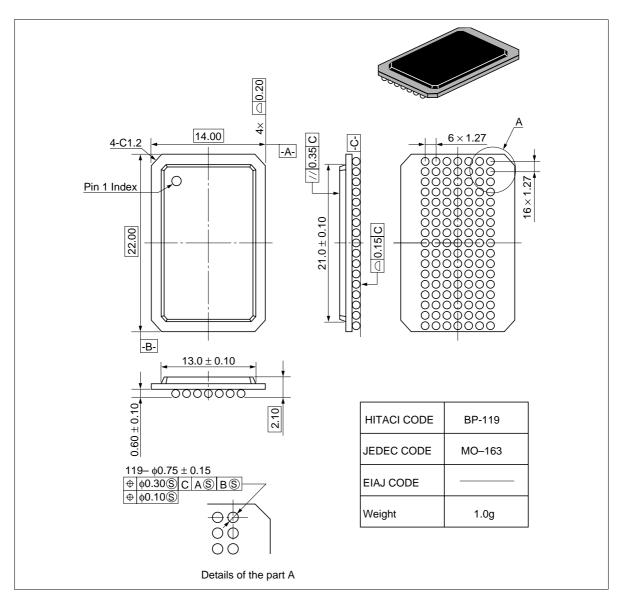

| Type Number    | Cycle Time | Package                                         |

|----------------|------------|-------------------------------------------------|

| HM67S18258BP-7 | 7.0 ns     | 119 Bump 1. 27 mm<br>14 mm × 22 mm BGA (BP-119) |

Il power supply and ground pins must be connected for proper operation of the device. This document contains information on a new product. Specifications and information contained herein are subject to change without notice.

## **Pin Arrangement**

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

|--------------------------------------------------------|

| (TOP VIEW)                                             |

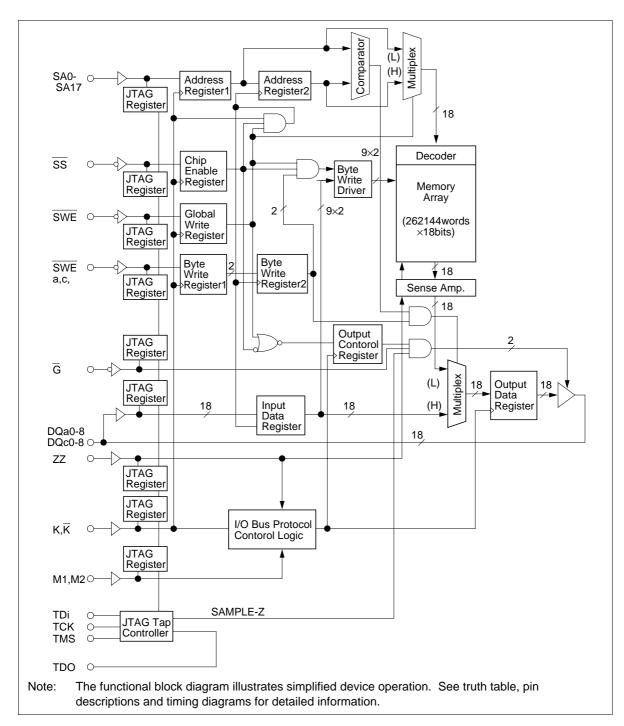

#### **Block Diagram**

#### **Pin Descriptions**

| Name             | I/O Type | Descriptions                   | Note                    |

|------------------|----------|--------------------------------|-------------------------|

| V <sub>DD</sub>  |          | Power Supply                   |                         |

| V <sub>ss</sub>  |          | Ground                         |                         |

| V <sub>DDQ</sub> |          | Output Power Supply            |                         |

| K                | Input    | Input Clock                    |                         |

| K                | Input    | Input Clock                    |                         |

| SS               | Input    | Synchronous Chip Select        |                         |

| SWE              | Input    | Synchronous Write Enable       |                         |

| SAn              | Input    | Synchronous Address            | n = 0, 1, 2, 17         |

| SWEx             | Input    | Synchronous Byte Select        | x = a, c                |

| G                | Input    | Asynchronous Output Enables    |                         |

| ZZ               | Input    | Power Down Mode Select         |                         |

| DQxm             | I/O      | Synchronous Data Input/Output  | x = a, c m = 0, 1, 2, 8 |

| M1, M2           | Input    | Output Protocol Mode Select    | 1                       |

| TMS              | Input    | Boundary Scan Test Mode Select |                         |

| ТСК              | Input    | Boundary Scan Test Clock       |                         |

| TDI              | Input    | Boundary Scan Test Data In     |                         |

| TDO              | Output   | Boundary Scan Test Data Out    |                         |

| NC               |          | No Connection                  |                         |

Notes: 1. There is 1 protocol with using mode pins. Mode control pins (M1, M2) are to be tied to either V<sub>DD</sub> or V<sub>SS</sub>. The state of the Mode control inputs must be set before power-up and must not change during device operation. Mode control inputs are not standard inputs and may not meet V<sub>IH</sub> or V<sub>IL</sub> specifications.

| M1              | M2              | Protocol                    |

|-----------------|-----------------|-----------------------------|

| V <sub>DD</sub> | V <sub>ss</sub> | Single Clock Register Latch |

#### **Truth Table**

| SS | G | SWE | SWEa | SWEc | к   | К   | Operation           | DQa    | DQc    |

|----|---|-----|------|------|-----|-----|---------------------|--------|--------|

| Н  | Х | Х   | Х    | Х    | L-H | H-L | Dead (not selected) | High-Z | High-Z |

| L  | Н | Н   | Х    | Х    | L-H | H-L | Dead (Dummy read)   | High-Z | High-Z |

| L  | L | Н   | Х    | Х    | L-H | H-L | Read                | Dout   | Dout   |

| L  | Х | L   | L    | L    | L-H | H-L | Write               | Din    | Din    |

| L  | Х | L   | Н    | L    | L-H | H-L | Write               | High-Z | Din    |

| L  | Х | L   | L    | Н    | L-H | H-L | Write               | Din    | High-Z |

Notes: 1. X means don't care for synchronous inputs, and H or L for asynchronous inputs.

2. SWE, SS, SWEa, SWEc, SA are sampled at the rising edge of K clock.

#### **Absolute Maximum Ratings**

| Parameter              | Symbol           | Value                        | Unit | Note |

|------------------------|------------------|------------------------------|------|------|

| Supply voltage         | V <sub>DD</sub>  | –0.5 to +4.6                 | V    | 1    |

| Output Supply Voltage  | V <sub>ddq</sub> | –0.5 to V <sub>DD</sub> +0.5 | V    | 1, 4 |

| Voltage on any pin     | V <sub>IN</sub>  | –0.5 to V <sub>DD</sub> +0.5 | V    | 1, 4 |

| Operating Temperature  | Та               | 0 to 70 (Tj max = 110)       | °C   |      |

| Storage Temperature    | Tstg (bias)      | –55 to 125                   | °C   |      |

| Input Latchup Current  | l <sub>u</sub>   | ±200                         | mA   |      |

| Output Current per pin | lout             | ±25                          | mA   |      |

Notes: 1. All voltage are referenced to  $V_{ss}$ .

Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be restricted the Operation Conditions. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

- 3. These Bi-CMOS memory circuits have been designed to meet the DC and AC specifications shown in the tables after thermal equilibrium has been established.

- 4. Not exceed 4.6 V

- 5. Power Up Initialization

The following supply voltage application sequence is recommended:  $V_{SS}$ ,  $V_{DD}$  then  $V_{DDQ}$ .

Remember according to the Absolute Maximum Ratings table,  $V_{DDQ}$  is not to exceed  $V_{DD}$  + 0.5 V, whatever the instantaneous value of  $V_{DD}$ .

## **Recommended DC Operating Conditions** (Ta = 0 to 70°C [Tj max = 110°C])

| Parameter                      | Symbol                 | Min   | Тур | Мах                    | Unit | Notes |

|--------------------------------|------------------------|-------|-----|------------------------|------|-------|

| Supply voltage                 | V <sub>DD</sub>        | 3.135 | 3.3 | 3.465                  | V    |       |

| Output Supply voltage          | V <sub>DDQ</sub>       | 3.135 | 3.3 | 3.465                  | V    | 1     |

|                                |                        | 2.375 | 2.5 | 2.75                   | V    | 2     |

| Input voltage Logic High Level | V <sub>IH</sub>        | 2.0   | _   | V <sub>DDQ</sub> + 0.3 | V    | 1     |

| Logic Low Level                | V <sub>IL</sub>        | -0.5  |     | 0.8                    | V    | 1     |

| Logic High Level               | V <sub>IH</sub>        | 1.85  | _   | V <sub>DDQ</sub> + 0.3 | V    | 2     |

| Logic Low Level                | V <sub>IL</sub>        | -0.5  | _   | 1.15                   | V    | 2     |

| PECL Logic High Level          | V <sub>IH</sub> (PECL) | 2.135 |     | 2.420                  | V    |       |

| PECL Logic Low Level           | V <sub>IL</sub> (PECL) | 1.490 | _   | 1.825                  | V    |       |

Note: 1. For  $V_{DDQ} = 3.3$  V supply.

2. For  $V_{DDQ} = 2.5$  V supply.

#### **DC Characteristics** (Ta = 0 to 70°C [Tj max 110°C], $V_{DD} = 3.3V \pm 5\%$ )

| Parameter                                 |                      | Symbol                 | Min                          | Тур | Мах                                  | Unit   | Note         |

|-------------------------------------------|----------------------|------------------------|------------------------------|-----|--------------------------------------|--------|--------------|

| Input Leakage Curr                        | ent                  | I <sub>LI</sub>        | -1                           | _   | 1                                    | μΑ     | 1            |

| Output Leakage Cu                         | ırrent               | I <sub>LO</sub>        | -1                           |     | 1                                    | μΑ     | 2            |

| PECL Input Leakag                         | ge Current Low       | I <sub>LI</sub> (PECL) |                              | _   | 50                                   | μΑ     |              |

| PECL Input Leakag                         | ge Current High      | I <sub>LI</sub> (PECL) |                              | _   | 150                                  | μA     |              |

| V <sub>DD</sub> Operating Curr<br>drivers | ent excluding output | I <sub>DD</sub>        | _                            | —   | 600                                  | mA     | 3            |

| Power Dissipation i drivers               | ncluding output      | P <sub>d</sub>         | _                            | —   | 2.7                                  | W      | 3, 8         |

| Standby Current (P                        | ower down mode)      | I <sub>SB</sub>        | _                            |     | 100                                  | mA     | 5            |

| Output Voltage                            | Logic Low            | V <sub>OL</sub>        | 0                            | _   | 0.4                                  | V      | 4            |

|                                           | Logic High           | V <sub>OH</sub>        | 2.4<br>V <sub>DDQ</sub> -0.4 | _   | V <sub>ddq</sub><br>V <sub>ddq</sub> | V<br>V | 4, 6<br>4, 7 |

Note: 1.  $0 \le Vin \le V_{DD}$

- 2.  $0 \le VI/O \le V_{DD}$ , Tristate I/O

- 3. I(I/O) = 0 mA, Address increment read 50% / write 50%,  $V_{DD} = V_{DD}$  max, Frequency = 125 MHz

- 4.  $I_{OH} = -2 \text{ mA or } I_{OL} = 2 \text{ mA}$

- 5. All inputs (except clock) are held at either  $V_{\text{SS}}$  or  $V_{\text{DDQ}}$ , and ZZ is held at  $V_{\text{DDQ}}$

- 6. for  $V_{DDQ} = 3.3 \text{ V}$  supply

- 7. for  $V_{DDQ} = 2.5 \text{ V supply}$

- 8. Output Load Capacitance = 29 pF

#### **Input Capacitance** (Ta = $25^{\circ}$ C, f = 1 MHz)

| Parameter                 | Symbol | Min | Max | Unit | Pin Name           | Note |

|---------------------------|--------|-----|-----|------|--------------------|------|

| Address Input Capacitance | CINA   | _   | 5   | pF   | SAn, SS, SWE, SWEx | 1    |

| Clock Input Capacitance   | CINC   |     | 8   | pF   | K, K, G            | 1    |

| I/O Capacitance           | CINIO  | —   | 7   | pF   | DQxm               | 1    |

Note: 1. This value is measured by sampling and not 100% tested.

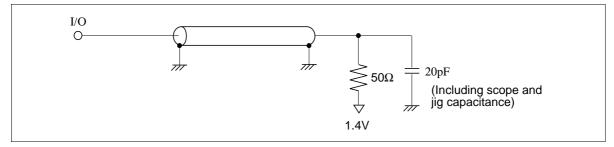

#### **AC Test Conditions**

- Temperature

- Input Reference Point for Differential Signals

- Input pulse levels

- Clock Input pulse levels

- Input Rise/Fall Time

- Clock input Rise/Fall Time

- Output timing reference (vih/vil)

- Output load

$0^{\circ}C \le Ta \le 70^{\circ}C (Tj max = 110^{\circ}C)$ Differential Cross-Over Point 0 to 2.5 V 1.8 to 2.1 V 0.5 to 1.5 ns (10% to 90%) 0.3 to 1.0 ns (10% to 90%) 2.0 V/0.8 V for V<sub>DDQ</sub> = 3.3 V 1 1.65 V/1.15 V for V<sub>DDQ</sub> = 2.5 V 1 See figures

Note

Note: 1. These levels are efficent under open termination load condition. These vih/vil levels under termination load will be determined by correlation between open load and termination load.

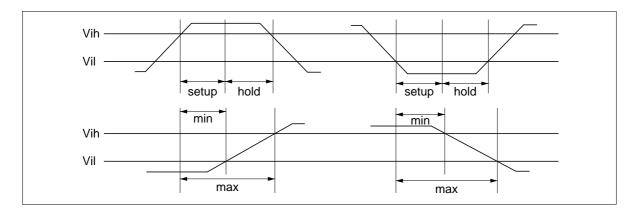

## **AC Timing Measurement**

## AC Characteristics (Ta = 0° to 70°C [Tj max = 110°C], $V_{DD}$ =3.3V± 5%)

|                        |                    |     | -7  |      |              |

|------------------------|--------------------|-----|-----|------|--------------|

| Parameter              | Symbol             | Min | Мах | Unit | Notes        |

| Clock Control          |                    |     |     |      |              |

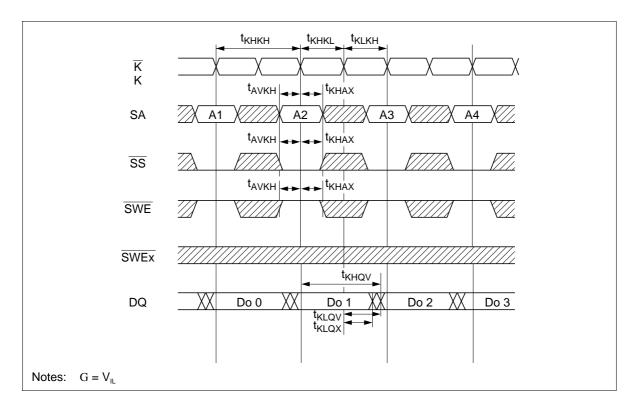

| Clock Cycle            | t <sub>кнкн</sub>  | 8.0 | _   | ns   |              |

| Clock High Width       | t <sub>KHKL</sub>  | 2.0 | _   | ns   |              |

| Clock Low Width        | t <sub>KLKH</sub>  | 2.0 | —   | ns   |              |

| Read Control           |                    |     |     |      |              |

| K Clock Access         | t <sub>KHQV</sub>  | _   | 7.0 | ns   |              |

| K Clock Access         | t <sub>KLQV</sub>  | _   | 3.0 | ns   |              |

| Output Enable Access   | t <sub>GLQV</sub>  | _   | 3.5 | ns   |              |

| K Low to Q Change      | t <sub>KLQX</sub>  | 1.0 | _   | ns   |              |

| Output Buffer Control  |                    |     |     |      |              |

| K Low to Low-Z         | t <sub>KLQX2</sub> | 1.0 | _   | ns   | 1            |

| Output Enable to Low-Z | t <sub>GLQX</sub>  | 1.0 | _   | ns   | 1            |

| K Clock High to Hi-Z   | t <sub>khqz</sub>  | 1.0 | 3.5 | ns   | 2            |

| Output Enable to Hi-Z  | t <sub>GHQZ</sub>  | 0.0 | 3.5 | ns   | 2            |

| Setup Times            |                    |     |     |      |              |

| Address Setup Time     | t <sub>avkh</sub>  | 0.5 | —   | ns   | SA, SS, SWE, |

| Data Setup Time        | t <sub>dvkh</sub>  | 0.5 | _   | ns   | SWEa, SWEc   |

| Hold Times             |                    |     |     |      |              |

| Address Hold Time      | t <sub>KHAX</sub>  | 1.0 | _   | ns   | SA, SS, SWE, |

| Data Hold Time         | t <sub>KHDX</sub>  | 1.0 | _   | ns   | SWEa, SWEc   |

Single Differential Clock Register-Latch Mode (M1 =  $V_{DD}$ , M2 =  $V_{SS}$ )

Notes: 1. Transition is measured ±200 mV from steady voltage with specified loading in Test Load.

2. Transition is measured start point of output high impedance from output Low impedance.

#### **Timing Waveforms**

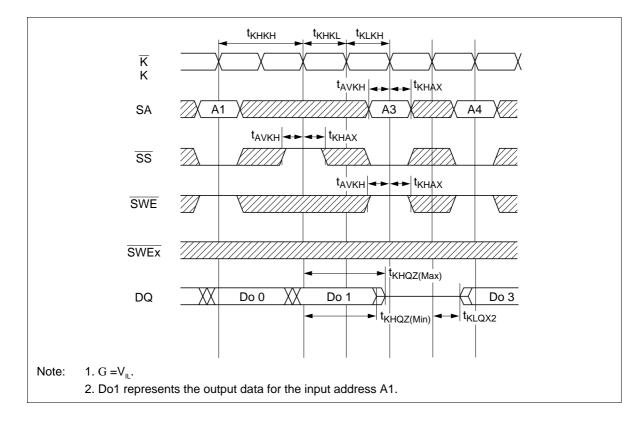

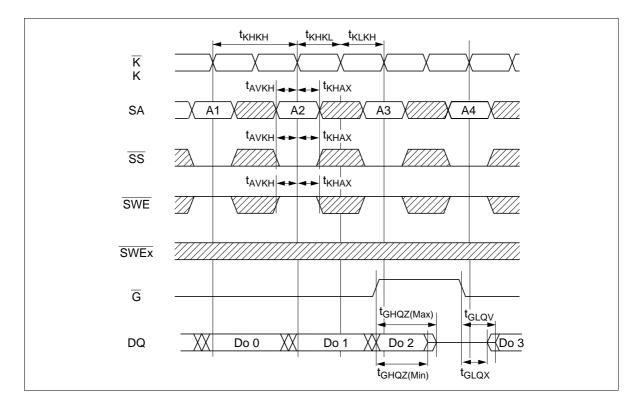

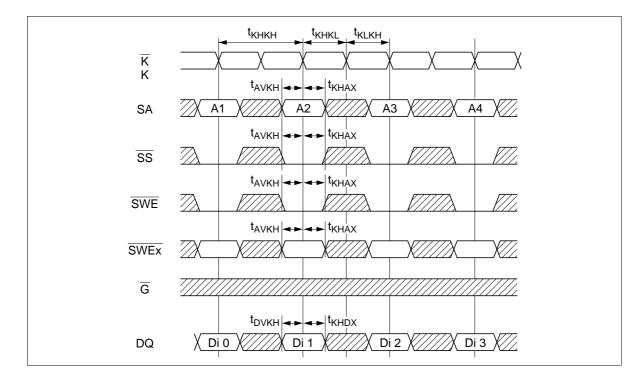

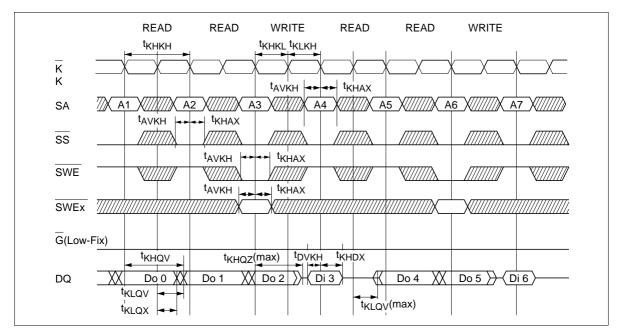

Single Clock Register Latch Mode

#### Read Cycle 1

#### Read Cycle 2 ( $\overline{SS}$ Controlled)

#### Read Cycle 3 ( $\overline{G}$ Controlled)

#### Write Cycle

#### **Read-Write Cycle**

(1) During this period DQ pins are in the output state so that the input signal of opposite phase to the outputs must not be applied.

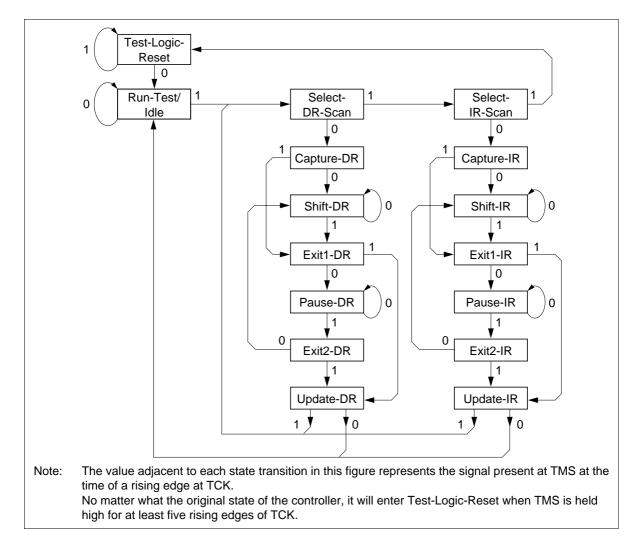

#### **Boundary Scan Test Access Port Operations**

#### overview

In order to perform the interconnect testing of the modules that include this SRAM, the serial boundary access port (TAP) is designed to operate in a manner consistent with IEEE Standard 1149.1 - 1990. But does not implement all of the functions required for 1149.1. the HM67S18258 contains a TAP controller. Instruction resister, Boundary scan resister, Bypass and ID resister.

#### **Test Access Port Pins**

| Symbol I/O | Name             |  |

|------------|------------------|--|

| ТСК        | Test Clock       |  |

| TMS        | Test Mode Select |  |

| TDI        | Test Data In     |  |

| TDO        | Test Data Out    |  |

Notes: This Device does not have a TRST (TAP Reset) pin. TRST is optional in IEEE 1149.1. To disable the TAP, TCK must be connected to  $V_{ss}$ . TDO should be left unconnected.

#### **TAP DC Operating Characteristics** ( $Ta = 0^{\circ}C$ to $70^{\circ}C$ [Tj max = $110^{\circ}C$ ])

| Parameter                           | Symbol          | Min    | Max                     | Note |

|-------------------------------------|-----------------|--------|-------------------------|------|

| Boundary scan Input High voltage    | V <sub>IH</sub> | 2.0 V  | $V_{\text{DD}}$ + 0.3 V |      |

| Boundary scan Input Low voltage     | V <sub>IL</sub> | –0.5 V | 0.8 V                   |      |

| Boundary scan Input Leakage Current | l <sub>u</sub>  | –1μΑ   | +1μA                    | 1    |

| Boundary scan Output Low voltage    | V <sub>oL</sub> |        | 0.4 V                   | 2    |

| Boundary scan Output High voltage   | V <sub>OH</sub> | 2.4 V  |                         | 3    |

Notes: 1.  $0 \le Vin \le V_{DD}$

2. I<sub>oL</sub> = 2 mA

3. I<sub>OH</sub> = -2 mA

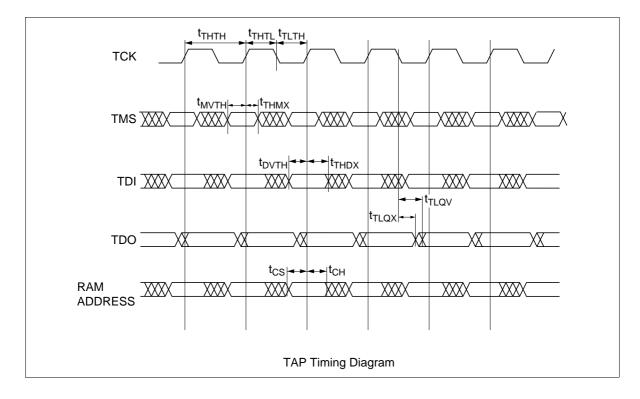

## **TAP AC Operating Characteristics** (Ta = 0°C to 70°C [Tj max = 110 °C])

| Parameter                   | Symbol            | Min | Мах | Unit |

|-----------------------------|-------------------|-----|-----|------|

| Test Clock Cycle Time       | t <sub>тнтн</sub> | 67  | _   | ns   |

| Test Clock High Pulse Width | t <sub>THTL</sub> | 30  | —   | ns   |

| Test Clock Low Pulse Width  | t <sub>TLTH</sub> | 30  | —   | ns   |

| Test Mode Select Setup      | t <sub>MVTH</sub> | 10  | —   | ns   |

| Test Mode Select Hold       | t <sub>THMX</sub> | 10  | _   | ns   |

| Capture Setup               | t <sub>cs</sub>   | 10  | —   | ns   |

| Capture Hold                | t <sub>cH</sub>   | 10  | —   | ns   |

| TDI Valid to TCK High       | t <sub>DVTH</sub> | 10  | _   | ns   |

| TCK High to TDI Don't Care  | t <sub>THDX</sub> | 10  | —   | ns   |

| TCK Low to TDO Unknown      | t <sub>TLQX</sub> | 0   | —   | ns   |

| TCK Low to TDO Valid        | $t_{\text{TLQV}}$ | _   | 20  | ns   |

Notes: 1.  $t_{CS} + t_{CH}$  defines the minimum pause in RAM I/O pad transitions to assure pad data capture.

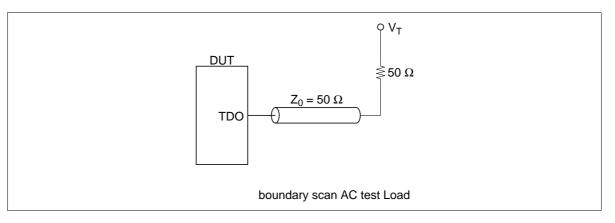

#### **TAP AC Test Conditions**

- Temperature

- Input Reference Point for Single-Ended Signals

- Input pulse levels

- Input Rise/Fall Time

- Output timing reference

- Test load termination supply voltage  $(V_T)$

- Output Load

0°C ≤ Ta ≤ 70°C [Tj max = 110°C] 1.5 V 0 to 2.5 V 2.0 ns typical (10% to 90%) 1.5 V 1.5 V

See figures

#### **TAP Timing Diagram**

## **Test Access Port Registers**

| Register Name          | Length  | Symbol    | Note |

|------------------------|---------|-----------|------|

| Instruction Register   | 3 bits  | IR [0;2]  |      |

| Bypass Register        | 1 bits  | BP        |      |

| ID Register            | 32 bits | ID [0;31] |      |

| Boundary Scan Register | 51 bits | BS [1;51] |      |

## **TAP Controller Instruction Set**

| IR2 | IR1 | IR0 | Instruction | Operation                                           |

|-----|-----|-----|-------------|-----------------------------------------------------|

| 0   | 0   | 0   | SAMPLE-Z    | Tristate all data drivers and capture the pad value |

| 0   | 0   | 1   | IDCODE      |                                                     |

| 0   | 1   | 0   | SAMPLE-Z    | Tristate all data drivers and capture the pad value |

| 0   | 1   | 1   | BYPASS      |                                                     |

| 1   | 0   | 0   | SAMPLE      |                                                     |

| 1   | 0   | 1   | BYPASS      |                                                     |

| 1   | 1   | 0   | BYPASS      |                                                     |

| 1   | 1   | 1   | BYPASS      |                                                     |

|     |     |     |             |                                                     |

Note: This Device does not perform EXTEST, INTEST or the preload portion of the PRELOAD command in IEEE 1149.1.

#### **Boundary Scan Order**

| Bit # | Bump ID | Signal Name | Bit # | Bump ID | Signal Name |

|-------|---------|-------------|-------|---------|-------------|

| 1     | 5R      | M2          | 27    | 2B      | NC          |

| 2     | 6T      | SA4         | 28    | ЗA      | SA14        |

| 3     | 4P      | SA5         | 29    | 3C      | SA15        |

| 4     | 6R      | SA6         | 30    | 2C      | SA16        |

| 5     | 5T      | SA7         | 31    | 2A      | SA17        |

| 6     | 7T      | ZZ          | 32    | 1D      | DQc0        |

| 7     | 7P      | DQa0        | 33    | 2E      | DQc1        |

| 8     | 6N      | DQa1        | 34    | 2G      | DQc2        |

| 9     | 6L      | DQa2        | 35    | 1H      | DQc3        |

| 10    | 7K      | DQa3        | 36    | 3G      | SWEc        |

| 11    | 5L      | SWEa        | 37    | 4D      | NC          |

| 12    | 4L      | K           | 38    | 4E      | SS          |

| 13    | 4K      | К           | 39    | 4G      | NC          |

| 14    | 4F      | G           | 40    | 4H      | NC          |

| 15    | 6H      | DQa4        | 41    | 4M      | SWE         |

| 16    | 7G      | DQa5        | 42    | 2K      | DQc4        |

| 17    | 6F      | DQa6        | 43    | 1L      | DQc5        |

| 18    | 7E      | DQa7        | 44    | 2M      | DQc6        |

| 19    | 6D      | DQa8        | 45    | 1N      | DQc7        |

| 20    | 6A      | SA8         | 46    | 2P      | DQc8        |

| 21    | 6C      | SA9         | 47    | 3T      | SA0         |

| 22    | 5C      | SA10        | 48    | 2R      | SA1         |

| 23    | 5A      | SA11        | 49    | 4N      | SA2         |

| 24    | 6B      | NC          | 50    | 2T      | SA3         |

| 25    | 5B      | SA12        | 51    | 3R      | M1          |

| 26    | 3B      | SA13        |       |         |             |

|       |         |             |       |         |             |

Notes: 1. Bit#1 is the first scan bit to exit the chip.

2. NC pads listed in the TABLE are represented in the Boundary Scan Register by a Place Holder. Place Holder registers are internally connected to  $V_{ss}$ .

3. The clock pins (K and K) are needed as PECL differential levels. And, clock reciever generated single clock signal. This signal and its inverted signal are used for Boundary Scan Register input signal.

## **ID** register

| Bit#  | 31 | 30            | 29         | 28  | 27              | 26 | 25 | 24   | 23 | 22             | 21 | 20 | 19    | 18 | 17 | 16  | 15    | 14    | 13   | 12 | 11 | 10 | 9 | 8 | 7    | 6     | 5    | 4  | 3 | 2 | 1 | 0   |

|-------|----|---------------|------------|-----|-----------------|----|----|------|----|----------------|----|----|-------|----|----|-----|-------|-------|------|----|----|----|---|---|------|-------|------|----|---|---|---|-----|

| Value | Х  | Х             | Х          | Х   | 0               | 1  | 1  | 1    | 0  | 0              | 1  | 0  | 1     | 1  | 0  | 0   | 0     | 0     | 0    | 0  | 0  | 0  | 0 | 0 | 0    | 0     | 0    | 0  | 1 | 1 | 1 | 1   |

|       |    | endo<br>evisi | or<br>on N | lo. | 4M<br>16I<br>De | ,  | C  | Dept | h  | 4N<br>16<br>Wi | ,  | W  | /idth |    |    | Use | in th | ie fu | ture |    |    |    |   | V | /end | or II | ) No | ). |   |   |   | Fix |

## **TAP Controller State Diagram**

#### **Package Outline**

#### HM67S18256BP (BP-119)

Unit : mm

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

# HITACHI

#### Hitachi, Ltd.

Semiconductor & IC Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109

#### For further information write to:

Hitachi America, Ltd. Semiconductor & IC Div. 2000 Sierra Point Parkway Brisbane, CA. 94005-1835 U S A Tel: 415-589-8300 Fax: 415-583-4207 Hitachi Europe GmbH Electronic Components Group Continental Europe Dornacher Straße 3 D-85622 Feldkirchen München Tel: 089-9 91 80-0 Fax: 089-9 29 30 00 Hitachi Europe Ltd. Electronic Components Div. Northern Europe Headquarters Whitebrook Park Lower Cookham Road Maidenhead Berkshire SL6 8YA United Kingdom Tel: 0628-585000 Fax: 0628-778322 Hitachi Asia Pte. Ltd. 16 Collyer Quay #20-00 Hitachi Tower Singapore 0104 Tel: 535-2100 Fax: 535-1533

Hitachi Asia (Hong Kong) Ltd. Unit 706, North Tower, World Finance Centre, Harbour City, Canton Road Tsim Sha Tsui, Kowloon Hong Kong Tel: 27359218 Fax: 27306071

## **Revision Record**

| Rev. | Date          | Contents of Modification                                  | Drawn by    | Approved by |

|------|---------------|-----------------------------------------------------------|-------------|-------------|

| 0.0  | Oct. 1, 1996  | Initial issue                                             | _           | K.Mitsumoto |

| 1    | Feb. 21, 1997 | P1. 3.3V $\pm$ 0.1V Operatiion to 3.3V $\pm$ 5% Operation | (Y. Matsui) | S.Nakazato  |

|      |               | Change HM67S18258BP-7H to HM67S18258BP-7                  |             |             |

|      |               | V <sub>DD</sub> min 3.2 to 3.135                          |             |             |

|      |               | V <sub>DD</sub> max 3.4 to 3.465                          |             |             |

|      |               | V <sub>DDQ</sub> min 3.2/.6 to 3.135/2.375                |             |             |

|      |               | V <sub>DDQ</sub> max 3.4/2.6 to 3.465/2.75                |             |             |

|      |               | I <sub>DD</sub> max 500 to 600                            |             |             |

|      |               | I <sub>он</sub> 2mA to - 2mA                              |             |             |

|      |               | I <sub>oL</sub> - 2mA to 2mA                              |             |             |

|      |               | P.7 Change termination load                               |             |             |

|      |               | t <sub>кнк⊥</sub> 3.2 to 2.0                              |             |             |

|      |               | t <sub>KLKH</sub> 3.2 to 2.0                              |             |             |

|      |               | Add t <sub>KHOZ</sub> min                                 |             |             |

|      |               | Add Note 2                                                |             |             |

|      |               | Delete Soft Error Rate                                    |             |             |