#### **PM6685**

# DUAL STEP-DOWN CONTROLLER WITH AUXILARY VOLTAGES FOR NOTEBOOK SYSTEM POWER

**Preliminary Data**

#### **Features**

- CONSTANT ON TIME TOPOLOGY ALLOWS VERY FAST LOAD TRANSIENTS

- 6V TO 28V INPUT VOLTAGE RANGE

- FIXED 5V-3.3V OUTPUT VOLTAGES

- 5V AND 3.3V ALWAYS VOLTAGES AVAILABLE DELIVER 100mA PEAK CURRENT

- 1.23V ± 1% REFERENCE VOLTAGE AVAILABLE

- NO R<sub>SENSE</sub> CURRENT SENSING USING LOW SIDE MOSFETs' R<sub>DS(on)</sub>

- ACCURATE CURRENT SENSE WITH R<sub>SENSE</sub>

- NEGATIVE CURRENT LIMIT

- SOFT START INTERNALLY FIXED AT 2ms

- SOFT OFF FOR OUTPUT DISCHARGE

- LATCHED OVP AND UVP

- SELECTABLE PULSE SKIPPING AT LIGHT LOADS

- SELECTABLE MINIMUM FREQUECY (25kHz) IN PULSE SKIP MODE

- 4 mW MAXIMUM QUIESCENT POWER

- INDIPENDENT POWER GOOD SIGNALs

- OUTPUT VOLTAGE RIPPLE COMPENSATION

#### **Description**

PM6685 is a dual step-down controller specifically designed to provide extremely high efficiency conversion, with lossless current sensing technique. The constant on-time architecture assures fast load transient response and the embedded voltage feed-forward provides nearly constant switching frequency operation. An embedded integrator control loop compensates the DC voltage error due to the output ripple. Pulse skipping technique increases efficiency at very light load. Moreover a minimum switching frequency of 25kHz is selectable to avoid audio noise issues. The PM6685 provides a selectable switching frequency, allowing either 200kHz/ 300kHz, 300kHz/400Khz or 400kHz/500kHz operation of the 5V/3.3V switching sections...

### **Applications**

- NOTEBOOK COMPUTERS

- TABLET PC OR SLATES

- MOBILE SYSTEM POWER SUPPLY

- 3-4 CELLS Li+ BATTERY POWERED DEVICES

#### Order codes

| Part number | Marking | Package       | Packing     |

|-------------|---------|---------------|-------------|

| PM6685      | PM6685  | VFQFPN-32 5X5 | TAPE & REEL |

|             |         |               | Rev 1       |

September 2005

1/16

### **Contents**

| 1 | Typical application circuit     | . 3 |

|---|---------------------------------|-----|

| 2 | Electrical ratings              | . 4 |

| 3 | Block & pin connection diagrams | . 5 |

| 4 | Electrical characteristics      | . 8 |

| 5 | Functional & block diagram      | 12  |

| 6 | Package Mechanical Data         | 13  |

| 7 | Pavision history                | 15  |

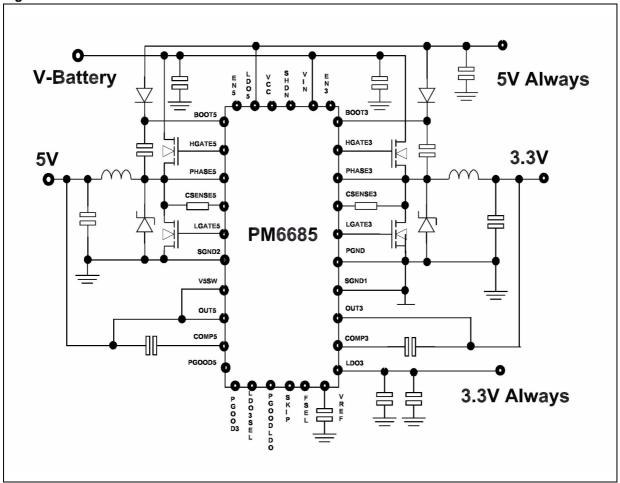

### 1 Typical application circuit

Figure 1. Circuit

**5**//

2 Electrical ratings PM6685

# 2 Electrical ratings

Table 1. Absolute maximum ratings

| Symbol | Parameter                                                           | Value                         | Unit |

|--------|---------------------------------------------------------------------|-------------------------------|------|

|        | SGND1 to SGND2                                                      | Shorted                       |      |

|        | COMPx, FSEL, LDO3_SEL, VREF, SKIP to SGND1, SGND2                   | -0.3 to V <sub>CC</sub> + 0.3 | V    |

|        | Enx, SHDN, PGOD_LDO3, OUTx, PGOODx, V <sub>CC</sub> to SGND1, SGND2 | -0.3 to 6                     |      |

|        | LDO3 to SGND1, SGND2                                                | -0.3 to LDO5 + 0.3            | V    |

|        | LGATEx to PGND                                                      | -0.3 to LDO5 + 0.3            | V    |

|        | HGATEx and BOOTx, to PHASEx                                         | -0.3 to 6                     | V    |

|        | PHASEx to PGND                                                      | -0.6 to 36                    | V    |

|        | CSENSEx, to PGND                                                    | -0.6 to 42                    | V    |

|        | CSENSEx to BOOTx                                                    | -6 to 0.3                     | V    |

|        | V5SW, LDO5 to PGND                                                  | -0.3 to 0.6                   | V    |

|        | VIN to PGND                                                         | -0.3 to 36                    | V    |

|        | PGND to SGND1, SGND2                                                | -0.3 to 0.3                   | V    |

|        | Power dissipation at T <sub>amb</sub> = 25°C                        | 2                             | W    |

Table 2. Thermal data

| Symbol            | Description                                                   | Value      | Unit |

|-------------------|---------------------------------------------------------------|------------|------|

| R <sub>thJA</sub> | Thermal Resistance Junction to ambient (mounted on demoboard) | 45         | °C/W |

| T <sub>STG</sub>  | Storage temperature range                                     | -40 to 150 | °C   |

| TJ                | Junction operating temperature range                          | -10 to 125 | °C   |

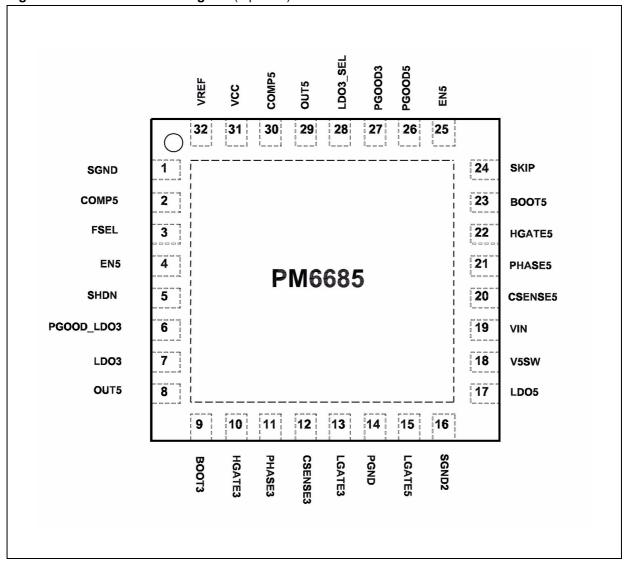

### 3 Block & pin connection diagrams

Figure 2. Pin connection diagram (top view)

Table 3. Pin description

| Pin No | PM6685     | Function                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | SGND       | Signal ground. Reference for internal logic circuitry.                                                                                                                                                                                                                                                                                                                                                                           |

| 2      | COMP3      | DC voltage error compensation pin for the 3.3V switching section.                                                                                                                                                                                                                                                                                                                                                                |

| 3      | FSEL       | Frequency selection pin. It provides a selectable switching frequency, allowing either 200kHz/300kHz, 300kHz/400kHz or 400kHz/500kz operation of the 5V/3.3V switching sections.                                                                                                                                                                                                                                                 |

| 4      | EN3        | 3.3V SMPS enable input. The 3.3V section is enabled appling a high logic level (>2.4V) to this pin, while is disabled appling a low logic level (<0.8V). When the section is disabled the High Side gate driver goes low and Low Side gate driver goes high. If both EN3 and EN5 pins are low and SHDN pin is high the device enters in standby mode.                                                                            |

| 5      | SHDN       | Shutdown control input. The device enters its shutdown mode with $9\mu A$ of supply current if VSHDN is less than the device off threshold voltage and doesn't restart until VSHDN is greater than the device on threshold voltage. The SHDN pin can be connected to Vbatt through a voltage divider to program an undervoltage lockout. In shutdown mode, the gate drivers of the two switching sections are in high impedance. |

| 6      | PGOOD LDO3 | Power Good ouput signal for the 3.3V linear regulator. This pin is an open drain output. It is shorted to GND if LDO3_SEL pin is at its low level or if the ouput voltage on LDO3 pin is lower than 2.6V.                                                                                                                                                                                                                        |

| 7      | LDO3       | 3.3V Linear regulator output. LDO3 can provide 100mA peak current. If LDO3_SEL pin is connected to VREF and OUT3 is greater than the LDO3 bootstrap switch threshold, the LDO3 regulator shuts down and the LDO3 pin will be directly connected to OUT3 through a 3 (max) switch.  If LDO3_SEL pin is at its low level the LDO3 is always OFF.  If LDO3_SEL pin is at its high level the LDO3 is always ON.                      |

| 8      | OUT3       | Output voltage sense for the 3.3V switching section. This pin must be directly connected to the output voltage of the switching section.                                                                                                                                                                                                                                                                                         |

| 9      | воот3      | Bootstrap capacitor connection for the switching 3.3V section. It supplies the high-side gate driver.                                                                                                                                                                                                                                                                                                                            |

| 10     | HGATE3     | High-side gate driver ouput for the 3.3V section.                                                                                                                                                                                                                                                                                                                                                                                |

| 11     | PHASE3     | Switch node connection and return path for the high side driver for the 3.3V section.                                                                                                                                                                                                                                                                                                                                            |

| 12     | CSENSE3    | Current sense input for the switching 3.3V section. This pin must be connected through a resistor to the drain of the synchronous rectifier (RDSON sensing) or to the source of the synchronous rectifier (RSENSE sensing) to set the current limit threshold.                                                                                                                                                                   |

| 13     | LGATE3     | Low-side gate driver output for the 3.3V section.                                                                                                                                                                                                                                                                                                                                                                                |

| 14     | PGND       | Power ground.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15     | LGATE5     | Low-side gate driver output for the 5V section.                                                                                                                                                                                                                                                                                                                                                                                  |

| 16     | SGND2      | Signal ground for analog circuitry.                                                                                                                                                                                                                                                                                                                                                                                              |

| 17     | V5SW       | Internal 5V regulator bypass connection. When the main 5V ouput voltage is greater than the boostrap switch threshold, the LDO5 regulator shuts down and the LDO5 pin will be directly connected to OUT5 through a 3 (max) switch. If not used, it must be tied to ground.                                                                                                                                                       |

**577**

Table 3. Pin description

| Table 3. | Pin description |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18       | LDO5            | 5V internal regulator output. LDO5 pin supplies all gate drivers, the internal circuitry and an external load. It can provide up to 100mA peak current.                                                                                                                                                                                                                                                                                              |

| 19       | VIN             | Device input supply voltage. A bypass filter (4 $\Omega$ and 4.7 $\mu F)$ between the battery and this pin is recommended.                                                                                                                                                                                                                                                                                                                           |

| 20       | CSENSE5         | Current sense input for the switching 5V section. This pin must be connected through a resistor to the drain of the synchronous rectifier ( $R_{DSON}$ sensing) or to the source of the synchronous rectifier ( $R_{SENSE}$ sensing) to set the current limit threshold.                                                                                                                                                                             |

| 21       | PHASE5          | Switch node connection and return path for the high side driver for the 5V section.                                                                                                                                                                                                                                                                                                                                                                  |

| 22       | HGATE5          | High-side gate driver ouput for the 5V section.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 23       | BOOT5           | Bootstrap capacitor connection for the switching 5V section. It supplies the high-side gate driver.                                                                                                                                                                                                                                                                                                                                                  |

| 24       | SKIP            | Pulse skipping mode control input. It is a three states pin.  If the pin is at its high level(e.g. cnnected to LDO5) the PWM mode is enabled.  If the pin is at its low level (e.g. connected to GND), the pulse skip mode is enabled.  If the pin is at its middle level (e.g. connected to Vref) the pulse skip mode is enabled but limiting the min frequency to 25KHz.                                                                           |

| 25       | EN5             | 5V SMPS enable input. The 5V section is enabled appling a high logic level (>2.4V) to this pin, while is disabled appling a low logic level (<0.8V). When the section is disabled the High Side gate driver goes low and Low Side gate driver goes high. If both EN3 and EN5 pins are low and SHDN pin is high the device enters in standby mode.                                                                                                    |

| 26       | PGOOD5          | Power Good ouput signal for the 5V section. This pin is an open drain ouput. The pin is pulled low if the output is disabled or is out of the specified window (approximately +/- 10% of its nominal value).                                                                                                                                                                                                                                         |

| 27       | PGOOD3          | Power Good ouput signal for the 3.3V section. This pin is an open drain ouput. The pin is pulled low if the output is disabled or is out of the specified window (approximately +/- 10% of its nominal value).                                                                                                                                                                                                                                       |

| 28       | LDP3SEL         | Control pin for the 3.3V internal linear regulator. This pin determines three operative modes for the LDO3.  If LDO3_SEL pin is at its low level the LDO3 is always OFF.  If LDO3_SEL pin is at its high level the LDO3 is always ON  If LDO3_SEL pin is connected to VREF and OUT3 is greater than the LDO3 bootstrap switch threshold, the LDO3 regulator shuts down and the LDO3 pin will be directly connected to OUT3 through a 3 (max) switch. |

| 29       | OUT5            | Output voltage sense for the 5V switching section. This pin must be directly connected to the output voltage of the switching section.                                                                                                                                                                                                                                                                                                               |

| 30       | COMP5           | DC voltage error compensation pin for the 5V switching section.                                                                                                                                                                                                                                                                                                                                                                                      |

| 31       | V <sub>CC</sub> | Device Supply Voltage pin. Connect this pin to LDO5                                                                                                                                                                                                                                                                                                                                                                                                  |

| 32       | VREF            | High accuracy output voltage reference (1.237V). It can deliver 50uA. Bypass to SGND with a 100nF capacitor.                                                                                                                                                                                                                                                                                                                                         |

4 Electrical characteristics PM6685

### 4 Electrical characteristics

( $V_{IN} = 12V$ ;  $T_{amb} = 0$ °C to 85°C unless otherwise specified)

Table 4. Supply section

| Simbol              | Parameter                                                            | Test Condition                                             | Min. | Тур. | Max. | Unit |

|---------------------|----------------------------------------------------------------------|------------------------------------------------------------|------|------|------|------|

| V <sub>IN</sub>     | Input voltage range                                                  | V <sub>out</sub> =V <sub>ref</sub> , LDO5 in regulation    | 6    |      | 28   | V    |

| V <sub>CC</sub>     | IC supply voltage                                                    |                                                            | 4.5  |      | 5.5  | V    |

|                     | Turn-on voltage threshold                                            |                                                            |      | 4.8  | 4.9  | V    |

| $V_{V5SW}$          | Turn-off voltage threshold                                           |                                                            | 4.6  | 4.75 |      | V    |

|                     | Hysteresis                                                           |                                                            |      | 50   |      | mV   |

| $V_{V5SW}$          | Maximum operating range                                              |                                                            |      |      | 5.5  | V    |

| R <sub>DS(on)</sub> | LDO5 Internal Bootstrap<br>Switch Resistance                         | V5SW >4.9V                                                 |      | 1.8  | 3    | Ω    |

|                     | LDO3 Internal Bootstrap<br>Switch Resistance                         | VOUT3 = 3.3V                                               |      | 1.8  | 3    | Ω    |

| R <sub>DS(on)</sub> | OUT_ Discharge-Mode<br>On-resistance                                 |                                                            |      | 12   | 25   | Ω    |

|                     | OUT3, OUT5_ Discharge-Mode<br>Synchronuos Rectifier<br>Turn-on level |                                                            | 0.2  | 0.35 | 0.5  | V    |

| Pin                 | Operating Power consumption                                          | VOUT5>5.1V,VOUT3>3.34V<br>V5SW to 5V<br>LDO5, LDO3 no load |      |      | 4    | mW   |

| Ish                 | V <sub>IN</sub> Shutdown Current                                     | SHDN connected to GND,                                     |      | 14   | 18   | μΑ   |

| Isb                 | V <sub>IN</sub> Standby Current                                      | ENx to GND, V5SW to GND                                    |      | 150  | 250  | μΑ   |

Table 5. Shutdown section

| Simbol | Parameter            | Test Condition | Min. | Тур. | Max. | Unit |

|--------|----------------------|----------------|------|------|------|------|

| V      | Device ON threshold  |                | 0.95 | 1.35 | 1.6  | V    |

| VSHDN  | Device OFF threshold |                | 0.8  | 0.85 | 0.9  | V    |

Table 6. Electrical characteristics (continued)

| Simbol              | Parameter                              | Test Co                                                                      | ondition                                                                                             | Min.  | Тур.  | Max.  | Unit |

|---------------------|----------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

|                     | Soft Start Ramp time                   |                                                                              |                                                                                                      | 2     |       | 6     | ms   |

| I <sub>CSENSE</sub> | Input bias current limit               |                                                                              |                                                                                                      | 90    | 100   | 110   | μΑ   |

|                     | Comparator offset                      | V <sub>CSENSE</sub> - V <sub>PGND</sub>                                      |                                                                                                      | -5    |       | 5     | mV   |

|                     | Zero Crossing Comparatot Offset        | V <sub>PGND</sub> - V <sub>PHASE</sub>                                       | :                                                                                                    | -5    |       | 5     | mV   |

|                     | Fixed Negative current limit Threshold | V <sub>PGND</sub> - V <sub>PHASE</sub>                                       |                                                                                                      |       | -120  |       | mV   |

|                     |                                        | FSEL to GND                                                                  | OUT5=5V                                                                                              |       | 2083  |       |      |

|                     |                                        | T SEE 10 GND                                                                 | OUT3=3.3V                                                                                            |       | 917   |       |      |

| T <sub>ON</sub>     | ON-Time duration                       | FSEL to VREF                                                                 | OUT5=5V                                                                                              |       | 1390  |       | ns   |

| ON                  | ON-TIME duration                       | T GEE to VICEI                                                               | OUT3=3.3V                                                                                            |       | 688   |       | 113  |

|                     |                                        | FSEL to LDO5                                                                 | OUT5=5V                                                                                              |       | 1040  |       |      |

|                     |                                        | FSEL 10 LDOS                                                                 | OUT3=3.3V                                                                                            |       | 550   |       |      |

| T <sub>OFFMIN</sub> | Minimum OFF-Time                       |                                                                              |                                                                                                      |       | 300   | 350   | ns   |

|                     | Voltage Accuracy                       | 4.2V < V <sub>LDO5</sub> <                                                   | 5.5V                                                                                                 | 1.224 | 1.237 | 1.249 | V    |

| $V_{REF}$           | Load regulation                        | -100μA < I <sub>REF</sub> <                                                  | 100μΑ                                                                                                | -4    |       | 4     | mV   |

|                     | Undervoltage Lockout fault threshold   | Falling edge of                                                              | Falling edge of REF                                                                                  |       |       | 0.95  | ٧    |

| COMP                | Over voltage clamp                     |                                                                              |                                                                                                      |       | 250   |       | mV   |

| COMP                | Under voltage clamp                    |                                                                              |                                                                                                      |       | -150  |       | IIIV |

|                     | Line regulation                        | Both SMPS, 6V-                                                               | < V <sub>IN</sub> <28V                                                                               |       |       | 0.004 | %/V  |

| $V_{LDO5}$          | LDO5 linear Output Voltage             | 6V < V <sub>IN</sub> < 28V,<br>0 < I <sub>LDO5</sub> < 50mA                  |                                                                                                      | 4.9   | 5.0   | 5.1   | V    |

| * LDO5              | LDO5 line regulation                   | 6V < V <sub>IN</sub> < 28V, I <sub>LDO5</sub> = 50mA<br>LDO3_SEL tied to GND |                                                                                                      |       |       | 0.004 | %/V  |

| I <sub>LDO5</sub>   | LDO5 Current limit                     |                                                                              | V <sub>LDO5</sub> > UVLO, I <sub>LDO3</sub> = 0A V <sub>OUT5</sub> > 5.1V, V <sub>OUT3</sub> > 3.34V |       | 350   | 400   | mA   |

| UVLO                | Under Voltage Lockout of LDO5          |                                                                              |                                                                                                      | 3.94  | 4     | 4.13  | V    |

| $V_{LDO3}$          | LDO3 linear Ouput Voltage              | 0 < I <sub>LDO3</sub> < 50mA                                                 |                                                                                                      | 3.23  | 3.3   | 3.37  | V    |

| I <sub>LDO3</sub>   | LDO3 Current limit                     | V <sub>LDO5</sub> > UVLO                                                     |                                                                                                      | 130   |       | 200   | mA   |

|                     | LICATE driver on registeres            | HGATEx high state(pullup)                                                    |                                                                                                      |       | 2.0   | 3     | Ω    |

|                     | HGATE driver on-resistance             | HGATEx low state (pulldown)                                                  |                                                                                                      |       | 1.8   | 2.7   | Ω    |

|                     | LGATE driver on-resistance             | LGATEx high state(pullup)                                                    |                                                                                                      |       | 1.4   | 2.1   | Ω    |

|                     | FOULE MINEL OIL-162/2/MINE             | LGATEx low state (pulldown)                                                  |                                                                                                      |       | 0.6   | 0.9   | Ω    |

**5**//

4 Electrical characteristics PM6685

Table 6. Electrical characteristics (continued)

| Simbol                | Parameter Test Condition        |                                        | Min.                      | Тур. | Max.                      | Unit |

|-----------------------|---------------------------------|----------------------------------------|---------------------------|------|---------------------------|------|

|                       | High side rise time             | HGATEx-PHASE from 1V to 4V             |                           |      | 20                        |      |

|                       | High side fall time             | CLOAD = 3.3nF                          |                           |      | 20                        | ns   |

|                       | Low side rise time              | LGATEx-PGND from 1V to 4V              |                           |      | 40                        | 20   |

|                       |                                 | CLOAD = 8.2nF                          |                           |      | 40                        | ns   |

| OVP                   | Over voltage threshold          | Both SMPS sections with respect        | 113                       | 116  | 120                       | %    |

| UVP                   | Under voltage threshold         | to VREF.                               | 66                        | 70   | 72                        | %    |

| PGOOD3,5              | Upper threshold (VFB-VREF)      |                                        | 107                       | 110  | 113                       | %    |

| PGOOD3,5              | Lower threshold (VFB-VREF)      |                                        | 90                        | 92   | 94                        | %    |

| I <sub>PGOOD3,5</sub> | PGOOD leakeage current          | VPGOOD3,5 forced to 5.5V               |                           |      | 1                         | μΑ   |

| V <sub>PGOOD3,5</sub> | Ouput Low Voltage               | ISink = 4mA                            |                           | 150  | 250                       | mV   |

|                       | Rising voltage threshold        |                                        |                           | 2.58 |                           | V    |

| PGOOD<br>LDO3         | Falling voltage threshold       |                                        |                           | 2.55 |                           | V    |

| LDOS                  | Hytseresis                      |                                        |                           | 25   |                           | mV   |

| I <sub>PGOOD_LD</sub> | PGOOD leakeage current          | V <sub>PGOOD LDO3</sub> forced to 5.5V |                           |      | 1                         | μΑ   |

| V <sub>PGOOD_LD</sub> | Ouput Low Voltage               | ISink = 4mA                            |                           | 150  | 250                       | mV   |

| T <sub>SDN</sub>      | Shutdown Temperature            |                                        |                           |      | 150                       | °C   |

| ENO E                 | SMPS disabled level             |                                        |                           |      | 0.8                       | .,   |

| EN3,5                 | SMPS enabled level              |                                        | 2.4                       |      |                           | V    |

|                       |                                 | Low level                              |                           |      | 0.5                       |      |

| FSEL                  | Frequency selection range       | Middle level                           | 1.0                       |      | V <sub>LDO5</sub><br>-1.5 | V    |

|                       |                                 | High level                             | V <sub>LDO5</sub><br>-0.8 |      |                           |      |

|                       |                                 | Always-off level                       |                           |      | 0.5                       |      |

| LDO3 SEL              | 3.3V Linear Regulator Selection | Boostrap level                         | 1.0                       |      | V <sub>LDO5</sub><br>-1.5 | V    |

|                       | 1 ""                            | Always-on level                        | V <sub>LDO5</sub><br>-0.8 |      |                           |      |

|                       | Pulse Skip Mode                 |                                        |                           |      | 0.5                       |      |

| SKIP                  | PWM Mode                        |                                        | 1.0                       |      | V <sub>LDO5</sub><br>-1.5 | V    |

|                       | Ultrasonic Mode                 |                                        | V <sub>LDO5</sub><br>-0.8 |      |                           |      |

PM6685 4 Electrical characteristics

Table 6. Electrical characteristics (continued)

| Simbol            | Parameter             | Test Condition                  | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------|---------------------------------|------|------|------|------|

|                   | Input leakage current | V <sub>EN3,4</sub> = 0 to 5V    |      |      | TBV  |      |

|                   |                       | V <sub>SKIP</sub> = 0 to 5V     |      |      | TBV  |      |

| I <sub>LEAK</sub> |                       | V <sub>SHDN</sub> = 0 to 5V     |      |      | TBV  | μΑ   |

|                   |                       | V <sub>FSEL</sub> = 0 to 5V     |      |      | TBV  |      |

|                   |                       | V <sub>LDO3_SEL</sub> = 0 to 5V |      |      | TBV  |      |

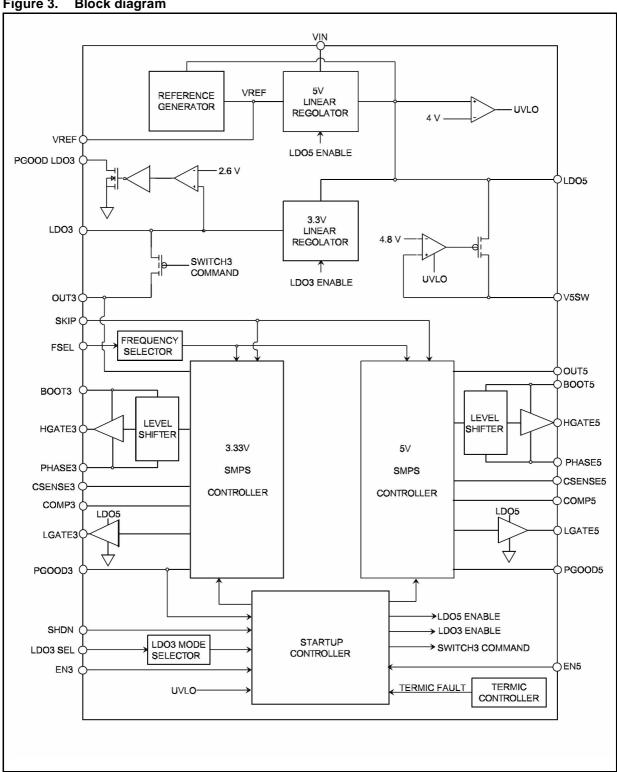

#### Functional & block diagram 5

Figure 3. **Block diagram**

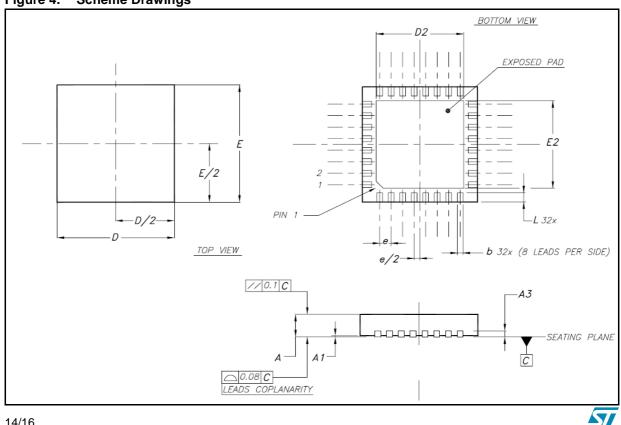

### 6 Package Mechanical Data

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect . The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

5//

Table 7. VFQFPN 5x5x1.0 32L Pitch 0.50

| Tubio II VI       | Databook (mm.) Drawing (m |      |        | Drawing (mm.) |      |       |

|-------------------|---------------------------|------|--------|---------------|------|-------|

| Dim.              |                           |      | '<br>Г |               |      |       |

|                   | Min.                      | Тур. | Max    | Min.          | Тур. | Max   |

| А                 | 0.80                      | 0.90 | 1.00   | 0.80          |      | 1.00  |

| A1                | 0                         | 0.02 | 0.05   | 0             |      | 0.05  |

| А3                |                           | 0.20 |        |               | 0.25 |       |

| b                 | 0.18                      | 0.25 | 0.30   | 0.225         |      | 0.275 |

| D(3)              | 4.85                      | 5.00 | 5.15   | 4.90          | 5.00 | 5.10  |

| D2 <sup>(5)</sup> | 3.65                      |      | 3.95   | 3.65          |      | 3.95  |

| E <sup>(3)</sup>  | 4.85                      | 5.00 | 5.15   | 4.90          | 5.00 | 5.10  |

| E2 <sup>(5)</sup> | 3.65                      |      | 3.95   | 3.65          |      | 3.95  |

| е                 |                           | 0.50 |        |               | 0.50 |       |

| L                 | 0.30                      | 0.40 | 0.50   | 0.35          |      | 0.45  |

- 1. VFQFPN stands for Thermally Enhanced Very thin Fine pitch Quad Flat Package No lead. Very thin: A = 1.00mm Max.

- 2. The leads size have been increased by Pb/Sn thickness in tin plating electrolytic process.

- 3. Dimensions D & E do not include mold protusion, not to exceed 0,15mm.

- 4. Package outline exclusive of metal burr dimensions.

- 5. Dimensions D2 & E2 are not in accordance with JEDEC.

Figure 4. **Scheme Drawings**

14/16

PM6685 7 Revision history

# 7 Revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 23-Sep-2005 | 1        | Initial release. |

**577**

7 Revision history PM6685

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2005 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com