BLUETOOTH<sup>™</sup> TRANSCEIVER

**RF2968**

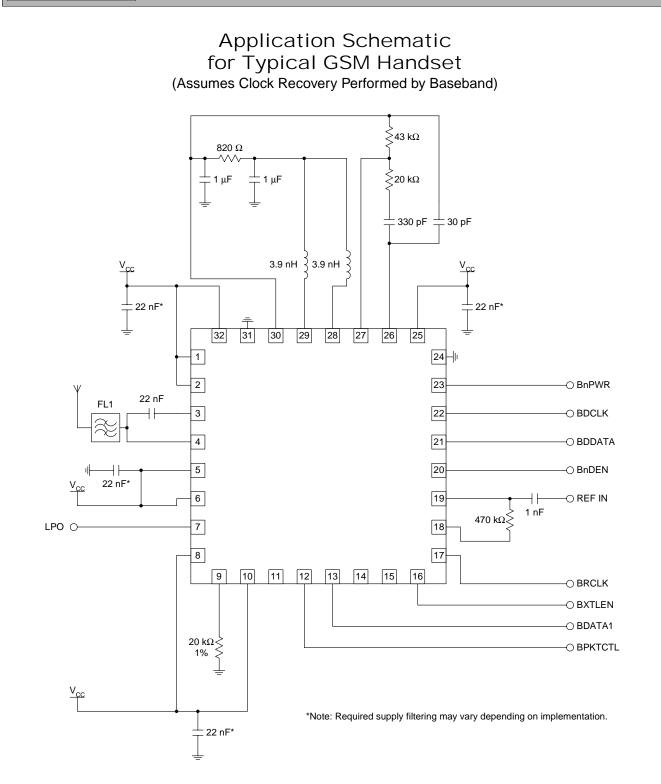

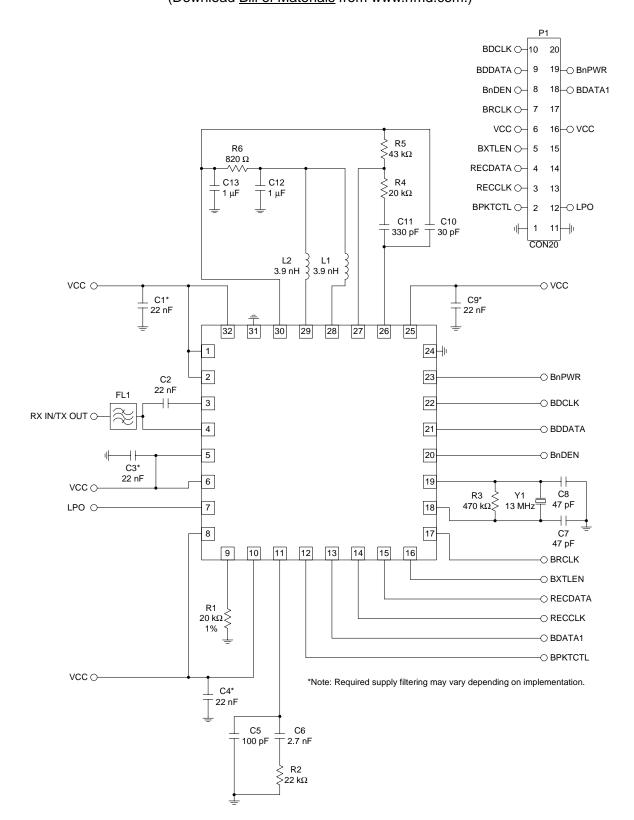

Typical Applications

- Bluetooth GSM/GPRS/EDGE Cellular

Phones

- Bluetooth Wireless LAN

- Cordless Phones

- Battery-Powered Portable Devices

### **Product Description**

The RF2968 is a monolithic integrated circuit intended for use as a low-cost FSK transceiver in *Bluetooth* applications. The device is provided in 32-lead plastic LPCC packaging and is designed to provide a fully-functional FSK transceiver. The chip is intended for *Bluetooth* applications in the 2.4GHz to 2.5GHz ISM band. The IF and demodulation sections of the chip require no external filters or discriminators. The chip also features an image reject front end and a fully programmable synthesizer with integrated oscillator circuitry. Self-calibrating RX and TX IF circuitry optimizes link performance and eliminates manufacturing variations.

$\it BLUETOOTH$  is a trademark owned by the Bluetooth SIG, Inc., and licensed to RF Micro Devices, Inc.

#### Optimum Technology Matching® Applied

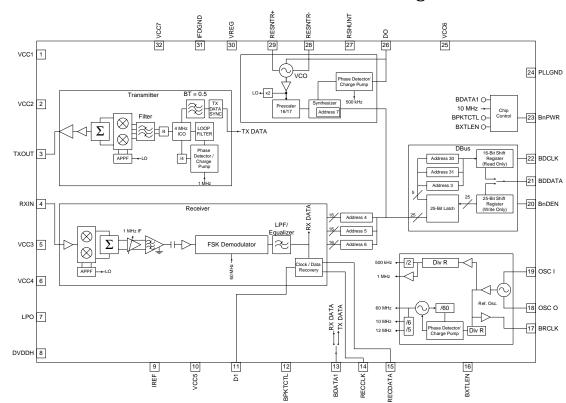

Functional Block Diagram

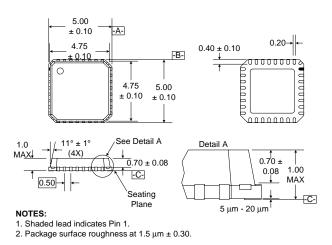

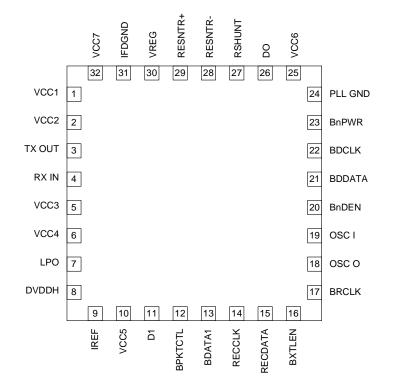

#### Package Style: LCC, 32-Pin, 5x5

#### Features

- Fully Monolithic Integrated Transceiver

- Self-Calibrating Transceiver

- Image Reject Receiver

- Bluetooth and BlueRF compatible

- Supports Reference Clocks to 40MHz

- Smallest Footprint *Bluetooth* Transceiver

Ordering Information

TBD

RF Micro Devices, Inc. 7628 Thorndike Road Greensboro, NC 27409, USA Tel (336) 664 1233 Fax (336) 664 0454 http://www.rfmd.com

#### **Absolute Maximum Ratings**

| Parameter                     | Ratings                 | Unit            |

|-------------------------------|-------------------------|-----------------|

| Supply Voltage                | -0.5 to +3.6            | V <sub>DC</sub> |

| Control Voltages              | -0.5 to V <sub>CC</sub> | V <sub>DC</sub> |

| Input RF Level                | +10                     | dBm             |

| Operating Ambient Temperature | -40 to +85              | °C              |

| Storage Temperature           | -55 to +125             | °C              |

RF Micro Devices believes the furnished information is correct and accurate at the time of this printing. However, RF Micro Devices reserves the right to make changes to its products without notice. RF Micro Devices does not assume responsibility for the use of the described product(s).

| Parameter                | Specification |              |     | Unit   | Condition                                      |  |

|--------------------------|---------------|--------------|-----|--------|------------------------------------------------|--|

| Farameter                | Min.          | Min. Typ.    |     | Unit   | Condition                                      |  |

| Overall                  |               |              |     |        | T=25 °C, V <sub>CC</sub> =3.0 V                |  |

| RF Frequency Range       |               | 2400 to 2500 |     | MHz    |                                                |  |

| VCO and PLL Section      |               |              |     |        |                                                |  |

| VCO Frequency Range      |               | 1100 to 1350 |     | MHz    |                                                |  |

| Frequency Tolerance      | -50           |              | 50  | kHz    | 20ppm crystal; -40°C to +85°C                  |  |

| RF Channels              |               | 79           |     |        |                                                |  |

| Step Size                |               | 1            |     | MHz    | Freq=2.4GHz                                    |  |

| SSB Phase Noise          |               | -90          |     | dBc/Hz | Freq=2.4GHz, 500kHz Offset                     |  |

|                          |               | -110         |     | dBc/Hz | Freq=2.4GHz, 2MHz Offset                       |  |

|                          |               | -124         |     | dBc/Hz | Freq=2.4GHz, 3MHz Offset                       |  |

| Reference Frequency      | 10            | 13           | 20  | MHz    | 10, 11, 12, 13, 20MHz                          |  |

|                          | 20            | 26           | 40  | MHz    | Div2ENB=0; 20, 22, 24, 26, 40MHz.              |  |

| Hop Time                 |               | 130          | 175 | μs     | Dual BW=75kHz and 25kHz; BW switch delay=100μs |  |

| K <sub>VCO</sub>         |               | 85           |     | MHz/V  | VCO Freq=1.2GHz                                |  |

| Transmit Section         |               |              |     |        |                                                |  |

| Data Rate                |               | 1            |     | Mbps   |                                                |  |

| Output Power             |               | 0            | 4   | dBm    |                                                |  |

| Power Control Range      |               | 28           |     | dB     |                                                |  |

| Power Control Step Size  |               | 4            |     | dB     |                                                |  |

| Gain Step Switching Time |               | 4            |     | μs     | From -28dB to 0dB                              |  |

| Output Impedance         | 25            | 50           | 100 | Ω      | VSWR<2:1                                       |  |

| Deviation                | 140           | 160          | 175 | kHz    | Peak, Data Sequence 00001111                   |  |

|                          | 115           |              |     | kHz    | Peak, Data Sequence 01010101                   |  |

| Transmit ISI             |               |              |     |        | Data Sequence 1010                             |  |

| Min Freq Dev, % EYE Open | 80            |              | 100 | %      | Reference Data Sequence 00001111               |  |

| Zero Crossing Error      | -125          |              | 125 | ns     | <u>+</u> 1/8 Symbol                            |  |

| In-Band Spurious         |               |              |     |        | Measurement BW=100kHz                          |  |

| Adjacent Channel Power   |               |              | -20 | dBc    |                                                |  |

| Second Channel Power     |               |              | -20 | dBm    |                                                |  |

| >Third Channel Power     |               |              | -40 | dBm    |                                                |  |

| Out-of-Band Spurious     |               |              |     |        | Measurement BW=100kHz                          |  |

| Operation                |               |              | -36 | dBm    | 30MHz to 1GHz                                  |  |

|                          |               |              | -30 | dBm    | 1 GHz to 12.75 GHz                             |  |

|                          |               |              | -47 | dBm    | 1.8GHz to 1.9GHz                               |  |

|                          |               |              | -47 | dBm    | 5.15GHz to 5.3GHz                              |  |

| Idle                     |               |              | -57 | dBm    | 30MHz to 1 GHz                                 |  |

|                          |               |              | -47 | dBm    | 1 GHz to 12.75 GHz                             |  |

|                          |               |              | -47 | dBm    | 1.8GHz to 1.9GHz                               |  |

|                          |               |              | -47 | dBm    | 5.15GHz to 5.3GHz                              |  |

| Demonster                                                                       | :           | Specificatio | n    | 11 14     | Condition                                                                   |

|---------------------------------------------------------------------------------|-------------|--------------|------|-----------|-----------------------------------------------------------------------------|

| Parameter                                                                       | Min. Typ. M |              | Max. | Unit      | Condition                                                                   |

| Overall Receive Section                                                         |             |              |      |           |                                                                             |

| Cascaded Voltage Gain                                                           | 18          |              | 64   | dB        |                                                                             |

| Cascaded Noise Figure                                                           |             | 8            |      | dB        |                                                                             |

| Cascaded Input IP <sub>3</sub>                                                  |             | -14          |      | dBm       |                                                                             |

| RX Sensitivity                                                                  |             | -85          |      | dBm       | IF BW=1MHz, BER=10 <sup>-3</sup>                                            |

| Image Rejection                                                                 |             | 30           |      | dB        | , -                                                                         |

| RX Input Impedance                                                              | 25          | 50           | 100  | Ω         | 2:1 VSWR max.                                                               |

| Interference Performance                                                        |             |              |      |           | BER<10 <sup>-3</sup> (C=Desired Signal/I=Interferer)                        |

| Co-Channel Interference,<br>C/I <sub>CO-Channel</sub>                           |             |              | 14   | dB        | C=-60dBm                                                                    |

| Adjacent (1MHz) Interference,<br>C/I <sub>1MHz</sub>                            |             |              | +4   | dB        | C=-60dBm                                                                    |

| Adjacent (2MHz) Interference,<br>C/I <sub>2MHz</sub>                            |             |              | -30  | dB        | C=-60dBm                                                                    |

| Adjacent (≥3MHz) Interfer-<br>ence, C/I <sub>≥3MHz</sub>                        |             |              | -40  | dB        | C=-67dBm                                                                    |

| Image Frequency Interfer-                                                       |             |              | -9   | dB        | C=-67dBm                                                                    |

| ence, C/l <sub>image</sub><br>Adjacent (1MHz) Interference<br>to In-Band Image, |             |              | -20  | dB        | C=-67dBm                                                                    |

| C/I <sub>image±1MHz</sub>                                                       |             |              |      |           |                                                                             |

| Out-of-Band Blocking                                                            |             |              |      |           | BER<10 <sup>-3</sup> , C=-67dBm, tested per evalua-<br>tion board schematic |

| Interfering Signal Frequency                                                    |             |              |      |           |                                                                             |

| 30MHz to 2000MHz                                                                | -10         |              |      | dBm       |                                                                             |

| 2000MHz to 2400MHz                                                              | -27         |              |      | dBm       |                                                                             |

| 2500MHz to 3000MHz                                                              | -27         |              |      | dBm       |                                                                             |

| 3000MHz to 12.75GHz                                                             | -10         |              |      | dBm       |                                                                             |

| Intermodulation Characteristic                                                  |             |              |      |           | BER<10 <sup>-3</sup> (BT= <i>Bluetooth</i> Modulated Signal)                |

| f1, f2                                                                          | -39         |              |      | dBm       | f0=-64dBm BT signal                                                         |

|                                                                                 |             |              |      |           | f1=sine                                                                     |

|                                                                                 |             |              |      |           | f2=BT signal                                                                |

|                                                                                 |             |              |      |           | f2-f1 =3MHz, 4MHz or 5MHz                                                   |

|                                                                                 |             |              |      |           | f0=2f1-f2                                                                   |

| Maximum Usable Level                                                            | -20         |              |      | dBm       | BER<10 <sup>-3</sup>                                                        |

| Spurious Emissions                                                              |             |              |      |           | Measurement BW=100kHz                                                       |

| 30MHz to 1GHz                                                                   |             |              | -57  | dBm       |                                                                             |

| 1GHz to 12.75GHz                                                                |             |              | -47  | dBm       |                                                                             |

| RSSI Operating Range                                                            | -80         |              | -20  | dBm       | Power level at RX IN pin                                                    |

| RSSI Resolution                                                                 |             | 1            |      | dB        |                                                                             |

| RSSI Absolute Accuracy                                                          | -4          |              | 4    | dB        | -60dBm input power                                                          |

| Front End                                                                       | 0F F        | 07 5         | 00.5 |           |                                                                             |

| Voltage Gain                                                                    | 25.5        | 27.5         | 29.5 | dB        |                                                                             |

| Power Gain                                                                      |             | 20           | 0.5  | dB        |                                                                             |

| Noise Figure<br>IIP3                                                            |             | 6<br>-14     | 8.5  | dB<br>dBm |                                                                             |

| IF Section                                                                      |             | -14          |      | UDIII     |                                                                             |

| IF Frequency                                                                    |             | 1            |      | MHz       |                                                                             |

| Voltage Gain                                                                    | -9.5        |              | 37   | dB        | Followed by 1 bit A/D                                                       |

| Noise Figure                                                                    | 0.0         | 25           | 57   | dB        |                                                                             |

| Parameter              | S                    | Specification |      |      | Condition                                    |

|------------------------|----------------------|---------------|------|------|----------------------------------------------|

| Faialletei             | Min.                 | Тур.          | Max. | Unit | Condition                                    |

| Data Voltages          |                      |               |      |      | $Z_{LOAD}$ >10k $\Omega$                     |

| Logic Low              |                      |               | 0.3  | V    |                                              |

| Logic High             | V <sub>CC</sub> -0.3 |               |      | V    |                                              |

| Power Supply           |                      |               |      |      |                                              |

| Voltage                | 2.5                  | 3.3           | 3.6  | V    |                                              |

| TX Current Consumption |                      | 49            |      | mA   | Transmit mode, +4dBm output power            |

| RX Current Consumption |                      | 49            |      | mA   | Receive mode                                 |

| Sleep Modes            |                      | 1             |      | μA   | Sleep mode, no low power clock               |

|                        |                      | 250           |      | μA   | Sleep mode, low power clock, 12MHz reference |

|                        |                      | 750           |      | μΑ   | Sleep mode, low power clock, other reference |

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Interface Schematic |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1   | VCC1     | Supply voltage for the VCO doubler and LO amplifier circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |

| 2   | VCC2     | Supply voltage for the RX mixers, TX PA, and LNA bias circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     |

| 3   | TX OUT   | Transmitter output. TX OUT output impedance is $50\Omega$ (nominal) when<br>the transmitter is enabled. TX OUT is a high impedance when the<br>transmitter is disabled. Because this pin is DC-biased, an external cou-<br>pling capacitor is required.                                                                                                                                                                                                                                                                                                                      |                     |

| 4   | RX IN    | Receiver input. RX IN input impedance is a low impedance when the receiver is enabled. RX IN is a high impedance when the receiver is disabled. An internal series inductor is used to tune the input impedance.                                                                                                                                                                                                                                                                                                                                                             |                     |

| 5   | VCC3     | Supply voltage for the RX input stage (LNA).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |

| 6   | VCC4     | Supply voltage for the TX mixers and bias circuits of the LO amplifier, LNA, and RX mixers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                     |

| 7   | LPO      | Low frequency clock output for low power mode. In sleep mode, this pin may provide either a 3.2kHz or 32kHz clock having a 50% duty cycle to the baseband. In other modes, the output is disabled.                                                                                                                                                                                                                                                                                                                                                                           |                     |

| 8   | DVDDH    | Supply voltage for the RX IF VGA circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |

| 9   | IREF     | Connects an external precision resistor (1% tolerance) for generation of a constant current reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |

| 10  | VCC5     | Supply voltage for the analog IF circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |

| 11  | D1       | This is the output of the charge pump for clock recovery circuit. A RC network from this pin to ground is used to establish the PLL bandwidth.                                                                                                                                                                                                                                                                                                                                                                                                                               | See pin 26.         |

| 12  | BPKTCTL  | In transmit mode, this pin is used as a strobe to enable the PA stage. In receive mode, the baseband has the option to use this pin to signal the detection of the sync word. The baseband drives this pin high at the end of the sync word, at which time a second DC estimation is performed by sampling the trailer bits. If baseband control is not desired to signal the second DC estimation, then an internal timer is used to mark the end of the sync word. The BBC bit is used to select the baseband control option; the default setting uses the internal timer. | See pin 23.         |

| 13  | BDATA1   | Input data to transmitter/output data from receiver. The input data is<br>unfiltered data at 1MHz data rate. The pin is bidirectional, switching<br>between data in and data out modes during Transmit and Receive<br>modes respectively.                                                                                                                                                                                                                                                                                                                                    | RXDATA              |

| 14  | RECCLK   | Recovered clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | See pin 17.         |

| 15  | RECDATA  | Recovered data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | See pin 17.         |

| 16  | BXTLEN   | This pin is part of the chip power control circuit. It is used to enable/dis-<br>able "sleep" mode of chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                     |

11

TRANSCEIVERS

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Interface Schematic                                          |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 17  | BRCLK    | Reference clock output. This is a crystal controlled reference clock in the 10-40MHz range, typically 13MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                              |

| 18  | OSC O    | Same as pin 19.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | See pin 19.                                                  |

| 19  | OSC I    | The OSC pins are used to produce the reference frequency by means of negative feedback. A crystal and resistor are placed in parallel from OSC I to OSC O to provide the feedback path and establish the resonant frequency. A shunt capacitor is placed on each OSC pin to provide the proper loading of the crystal. If an external reference is used, it is connected to OSC I through a DC-blocking capacitor, and OSC O is connected to OSC I through a 470k $\Omega$ resistor.                                                                         | osc 1 0                                                      |

| 20  | BnDEN    | Latches data entered into the serial port. Data is clocked into the latch<br>on the rising edge of BnDEN.                                                                                                                                                                                                                                                                                                                                                                                                                                                    | See pin 23.                                                  |

| 21  | BDDATA   | Serial data port. Read/write data is sent through this pin into / out of the on chip shift register. Read data is transferred on the rising edge of BDCLK. Write data is transferred on the falling edge of BDCLK.                                                                                                                                                                                                                                                                                                                                           | READ DATA                                                    |

| 22  | BDCLK    | Serial port input clock. This pin is used to clock data into the serial port.<br>To minimize the hop frequency programming time, a BDCLK frequency<br>of 10-20MHz is recommended.                                                                                                                                                                                                                                                                                                                                                                            | See pin 23.                                                  |

| 23  | BnPWR    | This pin is part of the chip power control circuit. It is used to power up<br>the chip from the "off" state.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                              |

| 24  | PLL GND  | Ground connection for the RF synthesizer, crystal oscillator, and serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                              |

| 25  | VCC6     | Supply voltage for the RF synthesizer, crystal oscillator, and serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                              |

| 26  | D0       | This is the output of the charge pump for the RF PLL. An RC network<br>from this pin to ground is used to establish the PLL bandwidth. To mini-<br>mize synthesizer settling time and phase noise, a dual loop bandwidth<br>scheme is implemented. During the initial period of frequency acquisi-<br>tion, a wide loop bandwidth is used. RSHUNT is used to switch to a<br>narrow loop bandwidth near the end of the frequency acquisition, pro-<br>viding improved VCO phase noise. The time at which the bandwidth<br>switches is set by the PLLDel bits. |                                                              |

| 27  | RSHUNT   | Switches the loop filter from wide to narrow bandwidth by shunting the midpoint of two external series resistors to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                              |

| 28  | RESNTR-  | The RESNTR pins are used to supply DC voltage to the VCO as well<br>as to tune the center frequency of the VCO. Two inductors are required<br>between RESNTR- and RESNTR+ to resonate with the internal capac-<br>itance. Inductance of traces from the RESNTR pins to the inductor<br>should be taken into account in the board layout.                                                                                                                                                                                                                     | RESNTR+ RESNTR-<br>D0 0 4 kQ 4 |

| Pin         | Function | Description                                                                                                                                                                            | Interface Schematic |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 29          | RESNTR+  | See pin 28.                                                                                                                                                                            |                     |

| 30          | VREG     | Voltage Regulator Output (2.2V). A bypass capacitor from this pin to ground is required. This voltage is used to bias the VCO through the tank circuit tied to pins 28 and 29.         |                     |

| 31          | IFDGND   | Ground connection for the digital IF circuits.                                                                                                                                         |                     |

| 32          | VCC7     | Supply voltage for the digital IF circuits.                                                                                                                                            |                     |

|             | ESD      | This diode structure is used to provide electrostatic discharge protec-<br>tion to 3kV using the Human body model. The following pins are pro-<br>tected: 6-7, 9-17, 20-27, 30-32.     |                     |

| Die<br>Flag | GND      | Ground connection for all circuits other than those grounded through dedicated pins. The die flag must be connected to the ground plane with very low inductance for best performance. |                     |

### Theory of Operation

The RF2968 is the first in a family of 2.4GHz transceivers developed specifically for *Bluetooth* applications. It operates as a Power Class 2 (+4dBm) or Class 3 (0dBm) *Bluetooth* device and is fully compliant to Version 1.0b of the *Bluetooth* Radio Specification. For Power Class 1 (+20dBm) applications, the RF2968 may be used with a power amplifier such as the RF2172. Processed in 0.35 um silicon Bi-CMOS and packaged in a 5mm-square, industry-standard 32-pin leadless plastic package, the RF2968 provides high performance at a very low cost. With integrated IF filtering, the RF2968 requires minimal external components and eliminates the need for costly components such as IF SAW filters and baluns. The high impedance 'off' states of the receiver input and transmitter output also eliminate the need for an external transmit/receive (T/R) switch. A complete *Bluetooth* solution may be implemented with the RF2968 in conjunction with an antenna, RF bandpass filter, and baseband controller. In addition to the RF signal processing, the RF2968 also performs the baseband functions of data demodulation, DC compensation, and data and clock recovery while access code correlation takes place in the baseband device.

The RF2968 transmitter output is internally matched to  $50\Omega$ , and requires an AC-coupling capacitor. The receiver's low noise amplifier (LNA) input (**RXIN** pin) is internally matched to present a  $50\Omega$  impedance to the front end filter. A single front end filter may be shared by the transmitter and receiver by simply connecting the **TXOUT** coupling capacitor to **RXIN**. Alternatively, the transmit path may be externally amplified to +20dBm, which, in conjunction with the RF2968's transmit gain control and received signal strength indicator (RSSI), allows *Bluetooth*-compliant operation for Power Class 1. The RSSI data is accessed via the serial port and provides a 1dB resolution over the RX input power range of -20to-80dBm. Transmit gain control is adjustable in 4dB steps and is also set via the serial port.

Baseband data is sent to the transmitter via the **BDATA1** pin, which is a bidirectional pin, acting as an input in transmit mode and an output in receive mode. The RF2968 performs the Gaussian filtering of the baseband data, FSK-modulates the IF current controlled oscillator (ICO), and upconverts the IF to the RF channel frequency.

The on-chip voltage controlled oscillator (VCO) is frequency synthesized to one half of the required local oscillator (LO) frequency and then doubled to produce the correct LO frequency. Two external tank inductors between **RESNTR+** and **RESNTR-** set the tuning range of the VCO. Voltage is supplied to the VCO from an on-chip regulator that is connected to the midpoint of the two tank inductors through a filtering network. Due to the fast frequency hopping requirements of *Bluetooth*, the loop filter components (connected to pins **D0** and **RSHUNT**) are especially critical as they largely determine the hopping and settling time of the VCO. Use of the component values as given in the Application Schematic is strongly recommended.

The RF2968 may use either a 10MHz, 11MHz, 12MHz, 13MHz, or 20MHz reference clock frequency and can also support a reference clock at double these frequencies to provide a migration path toward smaller end-product designs. This clock may be supplied by an external reference applied directly to **OSC I** through a DC-blocking capacitor. If an external reference is not available, then a crystal and two capacitors may be used to complete the reference oscillator circuitry contained on-chip. For either an externally or internally generated reference d frequency, a resistor between **OSC I** and **OSC O** is required for proper biasing. The frequency tolerance of the reference clock must be 20ppm or better to assure that the maximum allowed system frequency error remains within the demodulation bandwidth of the RF2968. A selectable 3.2kHz or 32kHz low power mode clock is available at the **LPO** pin to supply the baseband device with a low frequency clock in sleep mode. Where minimal sleep mode power consumption is a concern and reference clock frequency selection is flexible, a 12MHz reference clock should be chosen.

The receiver uses a low-IF architecture to minimize external component count. The RF signal is downconverted to 1MHz, allowing IF filtering to be incorporated on chip. Demodulated data is output at the **BDATA1** pin. Further data processing is performed by the data and clock recovery circuitry, which utilizes a baseband PLL. Pin **D1** is the loop filter connection for the baseband PLL. The synchronized data and clock are output at pins **RECDATA** and **RECCLK**. If the baseband device used with the RF2968 performs the clock recovery, then the **D1** loop filter components may be omitted.

The interface between the RF2968 and baseband device is described in the 'Application Information' section of the fulllength datasheet available from the RFMD web site (www.rfmd.com).

11

**TRANSCEIVERS**

Detailed Functional Block Diagram

Pin Out

TRANSCEIVERS

### Application Information

#### **Baseband Interface**

The RF2968 RF transceiver serves as the physical layer (PHY) in a *Bluetooth* system and supports the BlueRF interface between PHY and baseband devices. The RF2968 contains the data demodulation, DC compensation, and data and clock extraction circuitry while the access code correlator function takes place in the baseband.

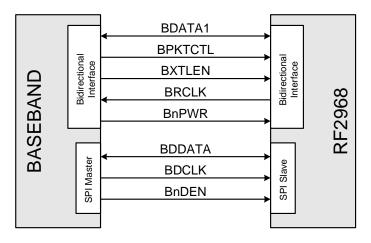

There are two interfaces between the RF2968 and the baseband. The serial interface provides the path for control data exchange, and the bidirectional interface provides the path for modem, timing, and chip power control signals. Figure 1 shows bidirectional signals with arrowheads on both ends of the line.

#### Figure1. Baseband/RF2968 Interface

#### Serial Interface

11

**TRANSCEIVERS**

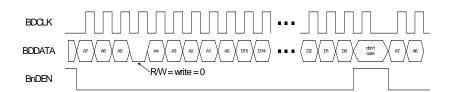

Control data is exchanged between the RF2968 and the baseband by means of the DBus serial interface protocol. **BDCLK**, **BDDATA**, and **BnDEN** are the signals comprising the serial interface. The baseband is the master device, initiating all accesses to the RF2968 registers. The data registers of the RF2968 are programmed or recalled according to the specified command format and address assignments. Data packets are transmitted MSB first.

#### Serial Data Packet Format

| Field            | Number of Bits | Comments                                                                               |

|------------------|----------------|----------------------------------------------------------------------------------------|

| Device Address   | 3 [A7:A5]      | "101" for PHY                                                                          |

| Read/Write       | 1 [R/W]        | "1"=Read, "0"=Write                                                                    |

| Register Address | 5 [A4:A0]      | Maximum of 32 registers                                                                |

| Data             | 16 [D15:D0]    | The RF2968 is programmed in Write mode and returns its register contents in Read mode. |

During a write, the baseband drives out each bit of the packet on the falling edge of **BDCLK**. The RF2968's data register is updated with the shift register contents on the first falling edge of **BDCLK** after **BnDEN** is driven high. See Figure 2.

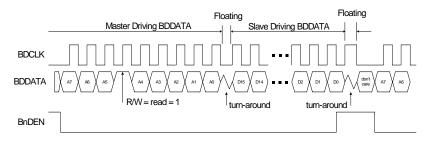

In a read operation, the baseband sends the device address, READ bit (R/W = 1), and register address to the RF2968 followed by a "turn-around" bit which lasts half a clock cycle. This turn-around allows the RF2968 to drive its requested data, via **BDDATA**, on the rising edges of **BDCLK**. Following the transfer of the last data bit (D[0]), the baseband drives **BnDEN** high and resumes control of **BDDATA** on the falling edge of the first **BDCLK** pulse after **BnDEN** is driven high. See Figure 3.

Figure 3. DBus Read Programming Diagram

#### Register Definition

The register address field allows up to 32 registers for various functions. The RF2968 implements only register addresses 3-7 and 30-31.

| Register | <sup>.</sup> 3 - IF | Register 1 | (Read-Only) |

|----------|---------------------|------------|-------------|

|----------|---------------------|------------|-------------|

| Bit Number | Bit Name  | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 - 15     | N/A       | Not Assigned                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0 -6       | RSSI[6:0] | The RSSI value indicates the average power measured during the first $10\mu$ s after a packet has been detected. The baseband reads this register to obtain the current received signal strength indicator measurement. The RSSI value may range from 0dBm to -127dBm in 1dB increments. (All 0's indicates 0dBm; all 1's indicates -127dBm.) The RSSI circuitry is designed to operate from -20dBm to -80dBm with an accuracy of 4dB at -60dBm. Example: RSSI[6:0]=[110101] indicates -53dBm. |

| Register  | 4 - | IF | Register | 2 | (Write-Only) |

|-----------|-----|----|----------|---|--------------|

| riogiotoi | -   | •• | regiotor | _ | (            |

| Bit Number | Bit Name   | Comments                                                                                                                                                                                                                                                                                                                                                                           |

|------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-15      | N/A        | Not Assigned                                                                                                                                                                                                                                                                                                                                                                       |

| 11         | ChopENB    | <ul><li>Enables circuitry that significantly reduces the levels of RF PLL comparison frequency spurious responses.</li><li>1: Spur cancellation disabled.</li><li>0: Normal mode. Spur cancellation enabled.</li></ul>                                                                                                                                                             |

| 10         | Div2ENB    | Enables an additional divide-by-two operation in the reference divider cir-<br>cuitry to accommodate the use of a 20MHz-40MHz crystal or clock. This<br>allows a migration path to higher reference frequencies.<br>1: Normal mode. 10, 11, 12, 13, or 20MHz reference clock.<br>0: Expanded mode. Reference clock is double that allowed in normal mode.                          |

| 8-9        | LPO[1:0]   | Determines the function of the low power mode clock (output at pin 7) when<br>the device is in Sleep mode according to the table below. In non-Sleep<br>modes, the output is disabled.                                                                                                                                                                                             |

| 5-7        | Gain[2:0]  | Sets the gain of the transmitter path. The gain is normally programmed immediately after the register write to enter the WAIT DATA SYNC state in Power Class 1 applications. Gain is adjustable from 0dBto-28dB in 4dB steps. [All 0's indicates high gain (0dB attenuation); all 1's indicates low gain (28dB attenuation).] Example: Gain[2:0]=[011] indicates 12dB attenuation. |

| 4          | ENSIowAGCB | 1: Slow AGC disabled.<br>0: Normal mode. Slow AGC enabled.                                                                                                                                                                                                                                                                                                                         |

| 3          | N/A        | Not Assigned                                                                                                                                                                                                                                                                                                                                                                       |

| 2          | TPL_AC     | <ul> <li>Selects a path in the RX data DC estimation circuit.</li> <li>1: Selects the DC estimation path that is AC coupled and which is normally used for the payload part of packet.</li> <li>0: Selects the fast DC estimation RX data path normally used for the access code of packet.</li> </ul>                                                                             |

| 0-1        | TDet[1:0]  | Sets the receiver gain according to the table below.                                                                                                                                                                                                                                                                                                                               |

### LPO [1:0]:

| LPO[1:0] | Output at LPO (Pin 7) |

|----------|-----------------------|

| 0 X      | 32kHz clock           |

| 10       | 3.2 kHz clock         |

| 1 1      | Clock disabled        |

|          |                       |

### TDet [1:0]:

| TDet[1:0] | VGA Gain (dB) | Filter Gain (dB) | Total Gain (dB) | Step Size (dB) |

|-----------|---------------|------------------|-----------------|----------------|

| 11        | -11           | 1.5              | -9.5            |                |

| 10        | 4.5           | 1.5              | 6.0             | 15.5           |

| 01        | 4.5           | 17               | 21.5            | 15.5           |

| 00        | 20            | 17               | 37.0            | 15.5           |

| Register | 5 - | IF | Register | 3 | (Write-Only) |

|----------|-----|----|----------|---|--------------|

|----------|-----|----|----------|---|--------------|

| Bit Number | Bit Name       | Comments                                                                                                                                                                                                                                                                                                            |

|------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15         | BypassSM       | <ul> <li>Selects or bypasses the state machine.</li> <li>1: Bypass mode. Internal power-up signals can be directly controlled by programming of the respective bits in this register [0:3, 6:7].</li> <li>0: Normal mode. All internally controlled power-up signals are derived from the state machine.</li> </ul> |

| 14         | BBC            | Selects baseband control or internal timer control for determining the time at which to perform DC estimation on the trailer bits.<br>1: Baseband control. The baseband drives BPKTCTL high at the end of the sync word.<br>0: Internal timer control.                                                              |

| 13         | N/A            | Not assigned.                                                                                                                                                                                                                                                                                                       |

| 12         | Test           | IF test mode enable. Used only in IC verification; not for use in end product.<br>1: IF test mode<br>0: Normal mode                                                                                                                                                                                                 |

| 11         | CalRxVGA       | Calibration which compensates for the gain of the LNA, mixer, and VGA. See "Special Modes: Cal-<br>ibration".                                                                                                                                                                                                       |

| 10         | Cal_Tx_PLL     | Calibrates the $K_0$ (gain of the current controlled oscillator) of the TX PLL and, by nature of the design, calibrates the $K_0$ of the RX PLL. See "Special Modes: Calibration".                                                                                                                                  |

| 9          | Cal_Gauss_Cell | Calibration which compensates for the offset and the amplitude of the Gaussian TX data that mod-<br>ulates the TX PLL ICO. See "Special Modes: Calibration".                                                                                                                                                        |

| 8          | Loopback       | 1: Loopback mode. The TX IF output is looped back to the RX IF input.<br>0: Normal mode                                                                                                                                                                                                                             |

| 7          | PU_XTAL        | Powers up the crystal oscillator circuitry. See "BypassSM" bit.<br>1: Power on<br>0: Power off                                                                                                                                                                                                                      |

| 6          | PU_MULT        | Powers up the frequency multiplier for the FM demodulator clock. See "Bypass SM" bit.<br>1: Power on<br>0: Power off                                                                                                                                                                                                |

| 5          | CalRxFil       | Calibrates the channel filter, demodulator low pass filter, and AC coupling filter in the DC estima-<br>tion circuit in the receiver, as well as the Gaussian filter and GFSK harmonic filter in the transmit-<br>ter. See "Special Modes: Calibration".                                                            |

| 4          | CalRXPLL_Int   | Calibration which compensates for the offset of the RX data path in the RX PLL interface circuit. See "Special Modes: Calibration".                                                                                                                                                                                 |

| 3          | PU_PA          | Powers up the transmit output amplifier. See "BypassSM" bit.<br>1: Power on<br>0: Power off                                                                                                                                                                                                                         |

| 2          | PU_RX          | Powers up all receiver and synthesizer circuits. See "BypassSM" bit.<br>1: Power on<br>0: Power off                                                                                                                                                                                                                 |

| 1          | PLL_BW         | Selects the loop bandwidth of the RF PLL by controlling the state of the RSHUNT pin. Under state machine control, this switch is executed according to the setting of the PLLDel[1:0] bits.<br>1: Narrow bandwidth. RSHUNT is short-circuited to ground.<br>0: Wide bandwidth. RSHUNT is a high impedance.          |

| 0          | PU_TX          | Powers up all transmitter and synthesizer circuits except for the output amplifier. See "BypassSM" bit.<br>1: Power on<br>0: Power off                                                                                                                                                                              |

#### Register 6 - IF Register 4 (Write-Only)

| Bit Number | Bit Name | Comments     |

|------------|----------|--------------|

| 0-15       | N/A      | Not Assigned |

#### Register 7 - PLL Control (Write-Only)

| Bit Number | Bit Name          | Comments                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15         | Set_Tx_PLL_LF_Ext | <ul> <li>Configures the LPO pin as a test pin when bits LPO[1:0] are set high.</li> <li>1: Test mode. LPO is connected to the IF PLL loop filter of the transmitter.<br/>(See "Special Modes: Transmitter Test Mode".)</li> <li>0: Normal mode. LPO is not connected to the IF PLL loop filter of the transmitter.<br/>mitter.</li> </ul>                                                 |

| 13 - 14    | PLLDel [1:0]      | Determines the time in which the PLL remains in high bandwidth mode<br>before switching to low bandwidth mode. In high bandwidth mode, the PLL<br>loop bandwidth is optimized for fast frequency locking. In low bandwidth<br>mode, the loop bandwidth is optimized for low phase noise. See below. See<br>also pin descriptions of D0 and RSHUNT, and bit PLL_BW (Register 5, Bit<br>1). |

| 12         | RSSI_Test         | Configures the RSSI circuitry to operate continuously for test purposes.<br>1: Test mode. Continuous operation.<br>0: Normal mode. Packet-based operation.                                                                                                                                                                                                                                |

| 9 - 11     | DivR [2:0]        | Selects the external crystal frequency. See below.                                                                                                                                                                                                                                                                                                                                        |

| 8          | TX_EN             | Powers up the TX voltage and current bias circuits and the TX PLL's ICO voltage threshold set circuit.                                                                                                                                                                                                                                                                                    |

| 7          | RX_EN             | Powers up the RX voltage and current bias circuits.                                                                                                                                                                                                                                                                                                                                       |

| 0 - 6      | PLL [6:0]         | Sets the RF PLL frequency. See below.                                                                                                                                                                                                                                                                                                                                                     |

#### PLLDel [1:0]:

| PLLDel [1:0] | Delay (us) |

|--------------|------------|

| 00           | 0          |

| 01           | 50         |

| 10           | 100        |

| 11           | 150        |

|              |            |

### DivR [2:0]:

| DivR [2:0] | Crystal Freq (MHz) |

|------------|--------------------|

| 011        | 12                 |

| 100        | 10                 |

| 101        | 11                 |

| 110        | 13                 |

| 111        | 20                 |

#### PLL[6:0]:

These bits determine the local oscillator (LO) frequency (i.e., the frequency at the doubler output) for both RX and TX modes. The LO frequency is set 1MHz above the channel center frequency. The PLL [6:0] data bits represent the frequency offset ( $F_{OFFSET}$ ) in MHz from a base frequency of 2400MHz. For the normal *Bluetooth* frequency range of 2402MHz to 2480MHz,  $F_{OFFSET}$  will range from 3 to 81; for the optional extended *Bluetooth* range (up to 2497MHz),  $F_{OFFSET}$  will range from 3 to 98 (high-side injection assumed in both cases).

#### Example:

Assume a channel frequency of 2448 MHz. The LO frequency is then: 2448+1=2449 MHz, and F<sub>OFFSET</sub> is: 2449-2400=49. PLL [6:0] is then: 0110001

#### Register 30 - Manufacturer's ID Code LSB's (Read-Only)

| Bit Number | Bit Name       | Comments                                                                                           |

|------------|----------------|----------------------------------------------------------------------------------------------------|

| 0 - 15     | ID_Code [15:0] | Lower 16 bits of manufacturer's code. The fixed "1" LSB of the manufacturer code is read at bit 0. |

#### Register 31 - Manufacturer's ID Code MSB's (Read-Only)

Figure 4. General Bidirectional Timing (RF2968 writing to baseband)

| Bit Number | Bit Name | Comments                                                                                                               |

|------------|----------|------------------------------------------------------------------------------------------------------------------------|

| 0 - 15     |          | Upper 16 bits of manufacturer's code. The MSB of the version number is read at bit 15. The RF2968 code is hex10B9825D. |

#### **Bidirectional Interface**

#### Data Exchange and Timing

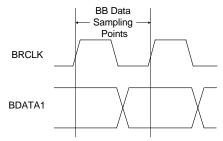

All bidirectional timing may be derived from **BRCLK**, which is generated by the RF2968. The RF2968 uses the falling edges of **BRCLK**, and the baseband uses the rising edges. Figure 4 shows the general timing for the case of data being transferred from the RF2968 to the baseband.

#### State Machine Control

The chip control circuitry of the RF2968 places the device into the required transmit, receive or power saving mode by controlling the power down and reset states of all other circuits in the device. The chip control inputs come from the baseband device (**BnPWR**, **BXTLEN**, **BPKTCTL**, **BDATA1**) via the bidirectional interface and from the registers at the output of the DBus block (**RXEN**, **TXEN**). State machines in the baseband and the RF2968 maintain the state which controls the direction of the bidirectional lines. The baseband controls the state machine in the RF2968 and ensures that data contentions do not occur during reset and normal operation. The control of individual sections of the RF2968 in each state is as follows.

| State          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OFF            | All circuits are powered down and reset; configuration data is lost. (CLRB=0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PWRON WAIT XTL | Reset is released (CLRB=1) and the oscillator is turned on (PDXTAL=1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HOLD XTL       | This mode is entered when the oscillator has settled. Configuration data can be read through the DBus inter-<br>face.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IDLE           | This is a standby mode. Data can be read into the control registers (through the DBus) and the oscillator remains on. All other circuits are powered down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SLEEP          | The device normally enters this mode from IDLE, in which case every circuit is powered down but not reset, so that configuration data is retained. The device may also enter this mode from any other except PWRON WAIT XTL or HOLD XTL, but the TXEN and RXEN functions are not overridden, so that TX and RX circuits may remain on.                                                                                                                                                                                                                                                                                                            |

| WAIT XTL       | The oscillator is turned on (PDXTAL=1) and allowed to settle before returning to IDLE mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| WAIT DATA SYNC | This is the start of the transmit sequence. This mode is entered by the baseband writing to the control registers (through the DBus). When this happens, TXEN goes high, turning on the synthesizer and initializing a fixed delay, after which all the transmit circuits (except for the PA) are turned on (PD_TX=1). The baseband waits $175\mu$ s before it starts sending transmit data to the RF2968 (to allow the synthesizer to settle). The device cannot be in both transmit and receive modes at the same time, so RXEN must be low to enter this mode.                                                                                 |

| DATA SYNC      | A transition on BDATA1 (0 to 1) starts the synchronization of data between the RF2968 and the baseband device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ENABLE PA      | The PA is powered up (PDPA=1) and ready to begin transmitting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TX DATA        | Data is transmitted in this mode. (The synthesizer has settled and the data path synchronized.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DISABLE PA     | The PA is powered down (PDPA=0). 1µs later, the synthesizer and the rest of the transmit circuits are powered down (PD_TX=0). This delay prevents any "unwanted transmission" during power down. The device then returns to IDLE mode when the baseband writes to the control registers and drives TXEN low.                                                                                                                                                                                                                                                                                                                                      |