### INTRODUCTION

The KT8555 is a per channel Time Slot Assignment Circuit (TSAC) that produces 8-bit receive and transmit time slots for four 1 CHIP CODEC.

Each frame synchronization pulse may be independently assigned to a time slot in a frame of up to 84 time slots.

#### FEATURES

- I Single, 5V operation

- Low power consumption: 5mW I

- Controls four 1 CHIP CODEC I

- Independent transmit and receive frame syncs Т

- enables

- channel unidirectional mode Т

- Up to 64 time slots per frame Compatible with KT8554/7 CODECs TTL and CMOS compatible Т

- Т

- 1

### **ORDERING INFORMATION**

| Device  | vice Package Operating Tempe |                  |  |  |

|---------|------------------------------|------------------|--|--|

| KT8555J | 20-CERDIP                    | - 20°C ~ + 125°C |  |  |

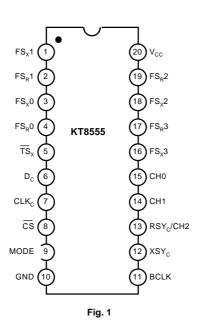

### **PIN CONFIGURATION**

# TIME SLOT ASSIGNMENT CIRCUIT

### **PIN DESCRIPTION**

| Pin No Symbol                           |                                                                              | Description                                                                                                                                             |  |

|-----------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3 FS <sub>x</sub> 0                     |                                                                              | A frame sync output which is normally low, and goes active-high for 8 cycles of                                                                         |  |

| 1 FS <sub>x</sub> 1                     |                                                                              | BCLK when a valid transmit time slot assignment is made.                                                                                                |  |

| 18                                      | FS <sub>x</sub> 2                                                            |                                                                                                                                                         |  |

| 16                                      | FS <sub>X</sub> 3                                                            |                                                                                                                                                         |  |

| 4                                       | FS <sub>R</sub> 0                                                            | A frame sync output which is normally low, and goes active-high for 8 cycles of                                                                         |  |

| 2                                       | FS <sub>R</sub> 1                                                            | BCLK when a valid receive time slot assignment is made.                                                                                                 |  |

| 19                                      | FS <sub>R</sub> 2                                                            |                                                                                                                                                         |  |

| 17                                      | FS <sub>R</sub> 3                                                            |                                                                                                                                                         |  |

| 5                                       | TS <sub>x</sub>                                                              | This pin pulls low during any active transmit time slot. (N-channel open drain)                                                                         |  |

| 6                                       | D <sub>c</sub>                                                               | The input for an 8 bit serial control word. $\overline{X}$ is the first bit clocked in.                                                                 |  |

| 7                                       | CLKc                                                                         | The clock input for the control interface.                                                                                                              |  |

| 8                                       | CS                                                                           | The active-low chip select for the control interface.                                                                                                   |  |

| 9                                       | MODE Mode 1 = Open or V <sub>CC</sub><br>Mode 2 = Gnd                        |                                                                                                                                                         |  |

| 10 GND Ground                           |                                                                              | Ground                                                                                                                                                  |  |

| 11 BCLK The bit clock input (2.048 MHz) |                                                                              | The bit clock input (2.048 MHz)                                                                                                                         |  |

| 12                                      | XSYc                                                                         | The transmit TSO sync pulse input. Must be synchronous with BCLK.                                                                                       |  |

|                                         |                                                                              | The transmit time slot 0 sync pulse input. Must be synchronous with BCLK.                                                                               |  |

| 13                                      | RSY <sub>c</sub> /CH2                                                        | In mode 1 this input is the receive time slot 0 sync pulse, $RSY_C$ , which must be                                                                     |  |

| 15                                      | RSY <sub>C</sub> /CH2                                                        | synchronous with BCLK. In mode 2 this is the CH2 input for the MSB of the                                                                               |  |

|                                         |                                                                              | channel select word.                                                                                                                                    |  |

| 14                                      | CH1 The input for the NSB (next significant bit) of the channel select word. |                                                                                                                                                         |  |

| 15                                      | CH0                                                                          | The input for the LSB (last significant bit) of the channel select word,<br>which defines the frame sync output affected by the following control word. |  |

| 20                                      | V <sub>cc</sub>                                                              | Power supply pin. 5V ±5%                                                                                                                                |  |

### ABSOLUTE MAXIMUM RATINGS (Ta = 25°C)

| Characteristic                        | Symbol            | Value                         | Unit |

|---------------------------------------|-------------------|-------------------------------|------|

| Positive Supply Voltage               | Vcc               | 7.0                           | V    |

| Input Voltage                         | VI                | V <sub>CC</sub> + 0.3 ~ - 0.3 | V    |

| Output Voltage                        | Vo                | V <sub>CC</sub> + 0.3 ~ - 0.3 | V    |

| Operating Temperature Range           | T <sub>OPR</sub>  | - 25 ~ 125                    | °C   |

| Storage Temperature Range             | T <sub>STG</sub>  | - 65 ~ 150                    | °C   |

| Lead Temperature (Soldering, 10 secs) | T <sub>LEAD</sub> | 300                           | °C   |

# TIME SLOT ASSIGNMENT CIRCUIT

### **ELECTRICAL CHARACTERISTICS** (Unless otherwise noted; $V_{CC} = 5.0V \pm 5\%$ , Ta = 0°C ~70°C)

| Characteristic                                         | Symbol                                    | Test Conditions                                        | Min  | Тур | Max | Unit |

|--------------------------------------------------------|-------------------------------------------|--------------------------------------------------------|------|-----|-----|------|

| Operating Current                                      | I <sub>CC</sub>                           | BCLK = 2.048MHz, all outputs open                      |      | 1   | 1.5 | mA   |

| Input Voltage High                                     | VIH                                       |                                                        | 2.0  |     |     | V    |

| Input Voltage Low                                      | VIL                                       |                                                        |      |     | 0.7 | V    |

| Input Current 1                                        | I <sub>I1</sub>                           | All Inputs Except Mode, $V_{IL}$ < $V_{IN}$ < $V_{IH}$ | -1   |     | 1   | μΑ   |

| Input Current 2                                        | I <sub>12</sub>                           | Mode, $V_{IN} = 0V$                                    | -100 |     |     | μΑ   |

| Output Voltage High                                    | V <sub>OH</sub>                           | $FS_X$ and $FS_R$ Outputs, $I_{OH} = 3mA$              | 2.4  |     |     | V    |

| Output Voltage Low                                     | Vol                                       | $FS_X$ and $FS_R$ Outputs, $I_{OL} = 3mA$              |      |     | 0.4 | V    |

|                                                        |                                           | $TS_X$ output, $I_{OL} = 3mA$                          |      |     | 0.4 | V    |

| Rise and Fall Time of Clock                            | t <sub>R (СК)</sub><br>t <sub>F(СК)</sub> | BCLK, CLK <sub>C</sub>                                 |      |     | 50  | nS   |

| Delay to TS <sub>x</sub> Low                           | t <sub>D (TSX L)</sub>                    | $C_L = 50 pF$                                          |      |     | 140 | nS   |

| Delay to $\overline{TS_X}$ High                        | t <sub>D (TSX H)</sub>                    | $R_L = 1K\Omega$ to $V_{CC}$                           | 30   |     | 100 | nS   |

| Hold Time from BCLK to Frame Sync                      | t <sub>H (BFS)</sub>                      |                                                        | 50   |     |     | nS   |

| Set-Up Time from Frame Sync to BLCK                    | t <sub>H (FSB)</sub>                      |                                                        | 30   |     |     | nS   |

| Delay Time from BLCK Low to $FX_{X/R}$ 0-3 High or Low | t <sub>D</sub>                            | C <sub>L</sub> = 50pF                                  |      |     | 50  | nS   |

| Hold Time from Channel Select to CLKC                  | t <sub>H (CSC)</sub>                      |                                                        | 50   |     |     | nS   |

| Set-Up Time from Channel Select to CLKC                | t <sub>SU (CSC)</sub>                     |                                                        | 30   |     |     | nS   |

| Period of Clock                                        | t <sub>CK</sub>                           | BCLK, CLK <sub>C</sub>                                 | 240  |     |     | nS   |

| Width of Clock High                                    | t <sub>w (CKH)</sub>                      | BCLK, CLK <sub>C</sub>                                 | 50   |     |     | nS   |

| Width of Clock Low                                     | t <sub>W (CLK)</sub>                      | BCLK, CLK <sub>C</sub>                                 | 50   |     |     | nS   |

| Set-Up Time from D <sub>C</sub> to CLKC                | t <sub>SU (Dc C)</sub>                    |                                                        | 30   |     |     | nS   |

| Hold Time from CLKC to D <sub>C</sub>                  | t <sub>H (CDc)</sub>                      |                                                        | 50   |     |     | nS   |

| Set-Up Time from CS to CLKC                            | t <sub>SU (CC)</sub>                      |                                                        | 30   |     |     | nS   |

| Hold Time from CLKC to CS                              | t <sub>H (CC)</sub>                       |                                                        | 100  |     |     | nS   |

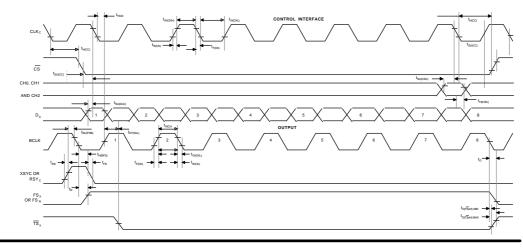

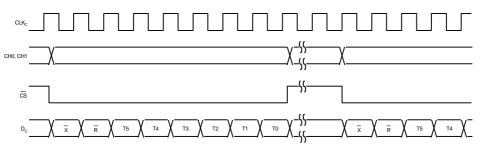

## TIMING DIAGRAM

### APPLICATION INFORMATION OPERATING CONTROL MODE 1

The KT8555 is a control interface which requires an 8 bit serial control word. Either one of the frame sync output group,  $FS_x0$  to  $FS_x0$  to  $FS_x0$  to  $FS_x0$  to  $FS_x3$ , affected by the control word is defined by the two bits,  $\overline{X}$  and  $\overline{R}$ . Time slot selected from 0 to 63 is specified. A frame sync output is highly active for one time slot which is equivalent to 8 cycles of BCLK. Up to 64 time slots are allowed to form a frame. There are two operational mode. In mode 1, each channel of transmit and receive direction has different time slot assigned. This mode can be selected by either leaving pin 9 (MODE) opened or connecting it with V<sub>CC</sub>. In such a case, pin 13 is RSYC input defining the start of each receive frame while four output,  $FS_x0$  to  $FS_x3$  are assigned with respect to RSYC. On the other hand, start of each transmit frame is defined by XSYC input by which output  $FS_x0$  to  $FS_x3$ , are assigned. XSYC and RSYC can be phase related. Channels from 0-3 are selected by the input CH0 and CH1 (refer to the table 1).

| X R T | 5 T4 T | <sup>-</sup> 3 T2 T1 T( |

|-------|--------|-------------------------|

|-------|--------|-------------------------|

$\overline{X}$  is the first bit clocked into  $D_C$  input

| CH1 CH0 |   | Channel Selected                                     |

|---------|---|------------------------------------------------------|

| 0 0     |   | Assign to FS <sub>x</sub> 0 and/or FS <sub>R</sub> 0 |

| 0       | 1 | Assign to FS <sub>x</sub> 1 and/or FS <sub>R</sub> 1 |

| 1       | 0 | Assign to FS <sub>x</sub> 2 and/or FS <sub>R</sub> 2 |

| 1       | 1 | Assign to FS <sub>x</sub> 3 and/or FS <sub>R</sub> 3 |

#### CONTROL DATA FORMAT

| T5 | T4 | Т3 | T2 | T1 | T1 | Time Slot |

|----|----|----|----|----|----|-----------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0         |

| 0  | 0  | 0  | 0  | 0  | 1  | 1         |

| 0  | 0  | 0  | 0  | 1  | 0  | 2         |

|    |    |    |    |    |    |           |

|    |    |    |    |    |    |           |

|    |    |    |    |    |    |           |

| 0  | 1  | 1  | 1  | 1  | 0  | 30        |

| 0  | 1  | 1  | 1  | 1  | 1  | 31        |

| 1  | 0  | 0  | 0  | 0  | 0  | 32        |

| 1  | 0  | 0  | 0  | 0  | 1  | 33        |

|    |    |    |    |    |    |           |

|    |    |    |    |    |    |           |

|    |    |    |    |    |    |           |

| 1  | 1  | 1  | 1  | 1  | 1  | 63        |

| X | R | Action                                              |  |  |  |

|---|---|-----------------------------------------------------|--|--|--|

| 0 | 0 | Assign time slot to both selected $FS_X$ and $FS_R$ |  |  |  |

| 0 | 1 | Assign time slot to selected $FS_X$ only            |  |  |  |

| 1 | 0 | Assign time slot to selected $FS_R$ only            |  |  |  |

| 1 | 1 | Disable both selected $FS_X$ and $FS_R$             |  |  |  |

#### TABLE 1. OPERATING CONTROL MODE 1

#### **OPERATING CONTROL MODE 2**

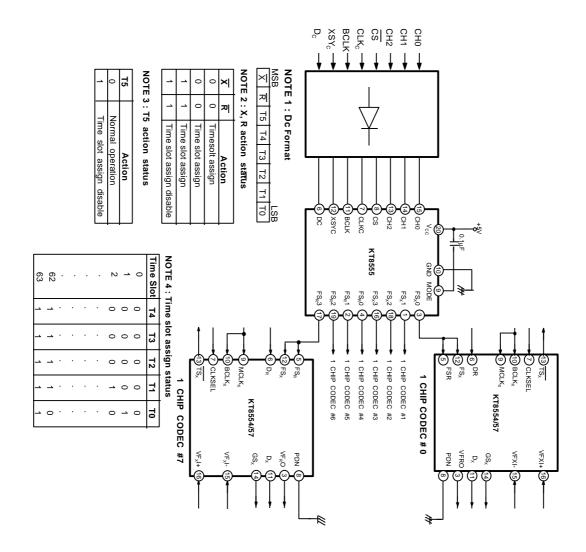

In mode 2, all 8 frame sync outputs can be assigned with respect to XSYC input. The mode 2, selected by connecting pin 9 (MODE) to GND, enables the KT8555 TSAC suitable for an 8-channel unidirectional controller and for a system where both transmit and receive direction of each channel have same time slot assigned. For instance,  $FS_X$  and  $FS_R$  input of 1 CHIP CODEC are hard wired together. The channel assigned has its channel selected by CH0, CH1 and CH2 (refer to table 2).

| CH2 | CH2 CH1 CH0 |   | Channel Selected            |

|-----|-------------|---|-----------------------------|

| 0   | 0           | 0 | Assign to FS <sub>x</sub> 0 |

| 0   | 0           | 1 | Assign to FS <sub>x</sub> 1 |

| 0   | 1           | 0 | Assign to FS <sub>x</sub> 2 |

| 0   | 1           | 1 | Assign to FS <sub>x</sub> 3 |

| 1   | 0           | 0 | Assign to FS <sub>R</sub> 0 |

| 1   | 0           | 1 | Assign to FS <sub>R</sub> 1 |

| 1   | 1           | 0 | Assign to FS <sub>R</sub> 2 |

| 1   | 1           | 1 | Assign to FS <sub>R</sub> 3 |

| X | R | Action                              |  |  |  |

|---|---|-------------------------------------|--|--|--|

| 0 | 0 | Assign time slot to selected output |  |  |  |

| 0 | 1 | Assign time slot to selected output |  |  |  |

| 1 | 0 | Assign time slot to selected output |  |  |  |

| 1 | 1 | Disable both selected output        |  |  |  |

TABLE 2. OPERATING CONTROL MODE 2

### **APPLICATION CIRCUIT**

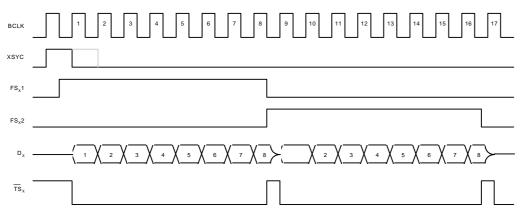

The KT8555 TSAC combined with any kind of 1 CHIP CODEC from KT8554/7 series can obtain data timing as illustrated in Fig. 3. Even though  $FS_X$  output goes high before BCLK gets high, the  $D_X$  output of the 1 CHIP CODEC remains in the TRI-STATE mode until both outputs are high. The eight bit period is shortened to avoid PCM data clash at PCM prehighway.

Alternatively, full 8 bits can be obtained by inverting the BCLK to the 1 CHIP CODEC devices, thereby rising edges of BCLK and  $FS_{X/R}$  are aligned.

Fig. 4 is typical timing of the control data interface.

Fig. 5 is the typical application circuit at operating control mode 2.

Fig. 3 Transmit Data Timing

#### Fig. 4 Control Data Timing

## TIME SLOT ASSIGNMENT CIRCUIT

NOTE 5 : Different time slot assign for RX and TX respectively also available.

Fig. 5 Digital interface on a typical subscriber linecard