# Dual 12-Bit, 1.0 GSPS **D/A Converter**

# **Preliminary Technical Data**

AD9776

## **FEATURES**

- 1.8/3.3 V Single Supply Operation

- Low power: 560 mW ( $I_{OUTFS} = 20$  mA;  $f_{DAC} = 1$  GSPS,  $4 \times$ Interpolation

- DNL = TBD LSB, INL = TBD LSB

- SFDR = TBD dBc to  $f_{OUT} = 100 \text{ MHz}$

- ACLR = 78 dBc @ 80 MHz IF

- CMOS data interface with Autotracking Input Timing

- Analog Output: Adjustable 10-30mA (RL=25  $\Omega$  to 50  $\Omega$ )

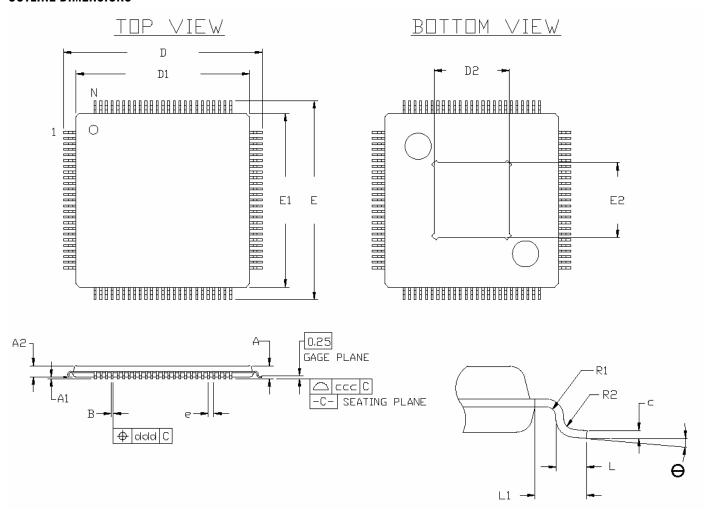

- 100-lead Exposed Paddle TQFP Package

- Multiple Chip Synchronization Interface

- 84dB Digital Interpolation Filter Stopband Attenuation

- Digital Inverse Sinc Filter

#### **APPLICATIONS**

- Wireless Infrastructure **Direct Conversion Transmit Diversity**

- Wideband Communications Systems: Point-to-Point Wireless, LMDS

#### PRODUCT DESCRIPTION

The AD9776 is a dual 12-bit high performance, high frequency

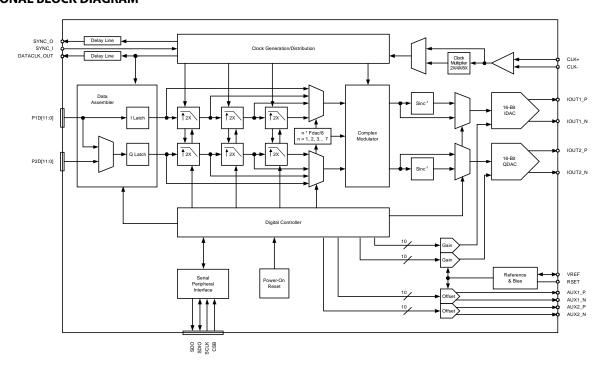

## **FUNCTIONAL BLOCK DIAGRAM**

DAC that provides a sample rate of 1 GSPS, permitting multi carrier generation up to its Nyquist frequency. It includes features optimized for direct conversion transmit applications, including complex digital modulation and gain and offset compensation. The DAC outputs are optimized to interface seamlessly with analog quadrature modulators such as the AD8349. A serial peripheral interface (SPI) provides for programming many internal parameters and also enables read-back of status registers. The output current can be programmed over a range of 10mA to 30mA. The AD9776 is manufactured on an advanced 0.18µm CMOS process and operates from 1.8V and 3.3V supplies for a total power consumption of 325mW. It is supplied in a 100-lead QFP package.

#### **PRODUCT HIGHLIGHTS**

Ultra-low Noise and Intermodulation Distortion (IMD) enable high quality synthesis of wideband signals from baseband to high intermediate frequencies.

Single-ended CMOS interface supports a maximum input rate of 300 MSPS with 1x interpolation.

Manufactured on a CMOS process, the AD9776 uses a proprietary switching technique that enhances dynamic performance.

The current outputs of the AD9776 can be easily configured for various single-ended or differential circuit topologies.

Figure 1 Functional Block Diagram

#### Rev. PrA

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## **TABLE OF CONTENTS**

| Specifications                              | Instruction Byte                                     |

|---------------------------------------------|------------------------------------------------------|

| DC SPECIFICATIONS                           | Serial Interface Port Pin Descriptions12             |

| DIGITAL SPECIFICATIONS4                     | MSB/LSB Transfers13                                  |

| AC SPECIFICATIONS4                          | Notes on Serial Port Operation13                     |

| Pin Function Descriptions5                  | SPI Register Map14                                   |

| Pin Configuration6                          | Internal Reference/Full Scale Current Generation22   |

| Interpolation Filter Coefficients7          | Auxiliary DACs22                                     |

| INTERPOLATION Filter RESPONSE CURVES8       | Power Down and Sleep Modes22                         |

| CHARACTERIZATION DATA9                      | Internal PLL Clock Multiplier / Clock Distribution23 |

| General Description                         | Timing Information                                   |

| Serial Peripheral Interface                 | Interpolation Filter Architecture25                  |

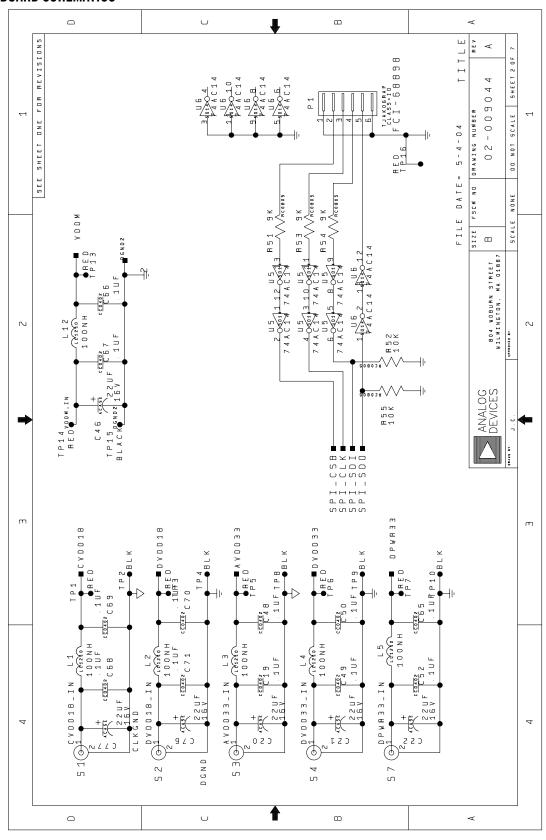

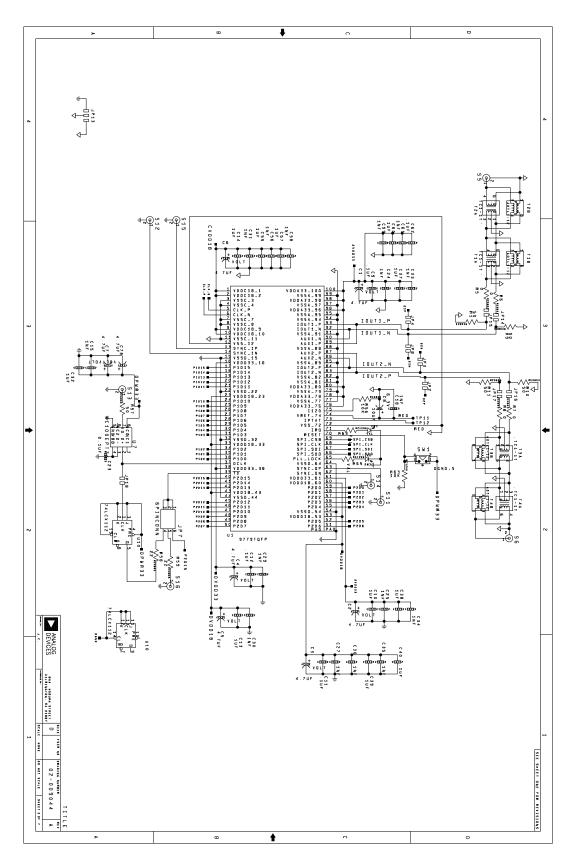

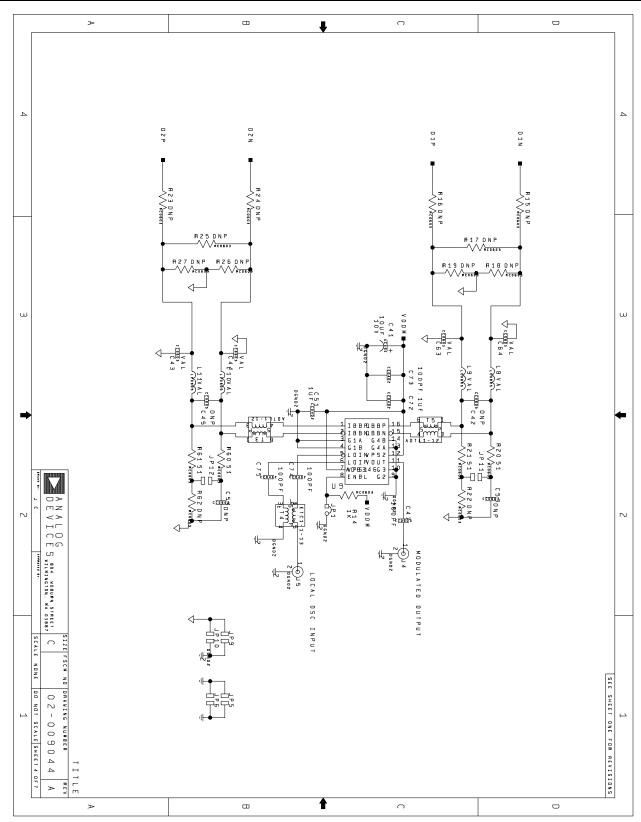

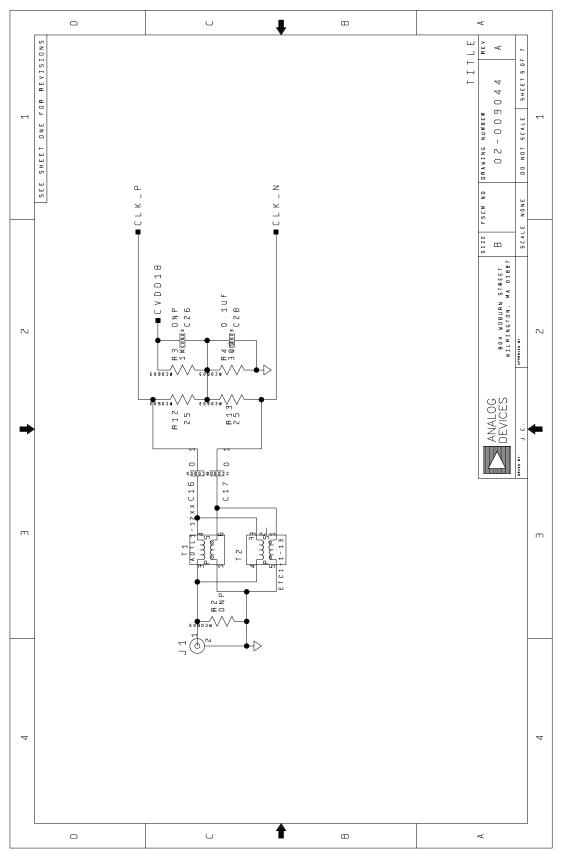

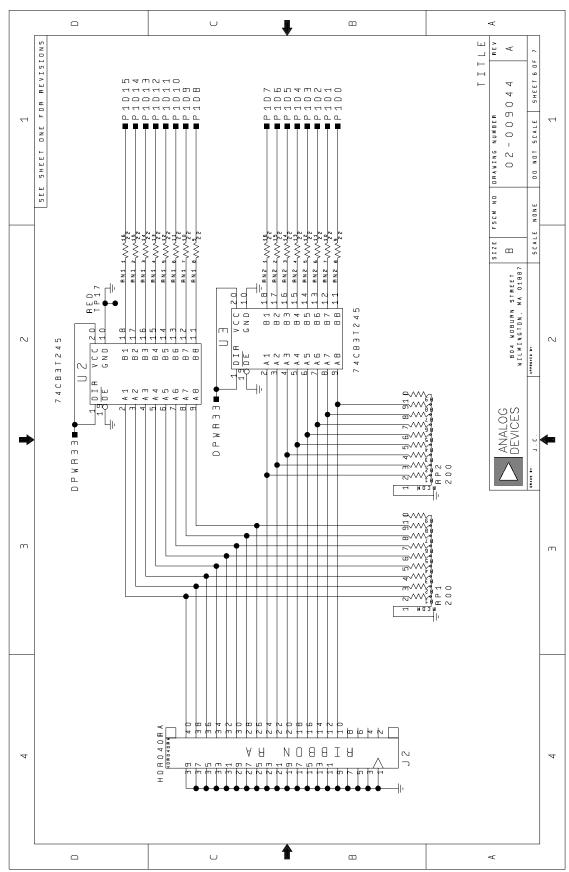

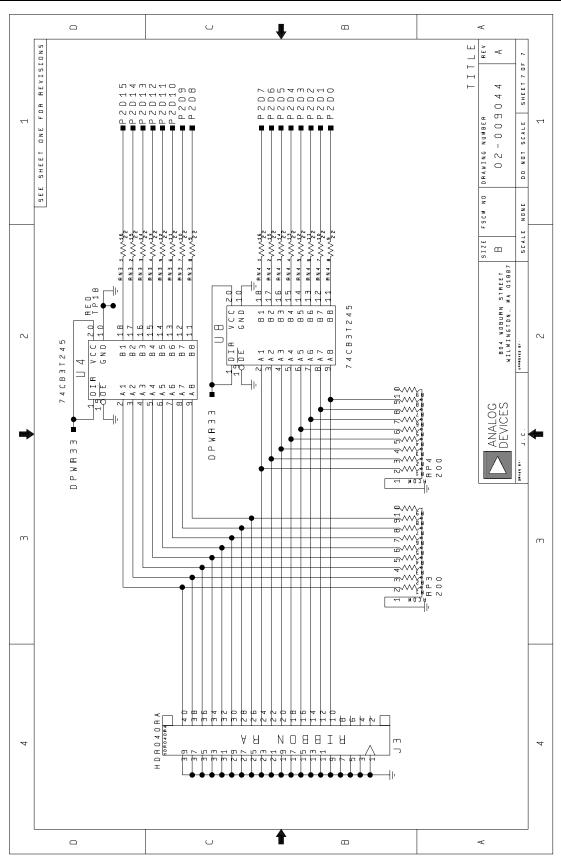

| General Operation of the Serial Interface12 | EvaLuation Board Schematics27                        |

#### **REVISION HISTORY**

Revision PrA: Initial Version

## SPECIFICATIONS1

## DC SPECIFICATIONS

## (VDD33 = 3.3 V, VDD18 = 1.8 V, MAXIMUM SAMPLE RATE, UNLESS OTHERWISE NOTED)

| Parameter                  |                                         | Temp | Test Level | Min  | Тур   | Max  | Unit   |

|----------------------------|-----------------------------------------|------|------------|------|-------|------|--------|

| RESOLUTION                 | ESOLUTION                               |      |            |      | 12    |      | Bits   |

| ACCLIDACY                  | Integral Nonlinearity (DNL)             |      |            |      | TBD   |      | LSB    |

| ACCURACY                   | Differential Nonlinearity (INL)         |      |            |      | TBD   |      | LSB    |

|                            | Offset Error                            |      |            |      | ± TBD |      | % FSR  |

|                            | Gain Error (With Internal Reference)    |      |            |      | ± TBD |      | % FSR  |

|                            | Gain Error (Without Internal Reference) |      |            |      | ± TBD |      | % FSR  |

| ANALOG OUTPUTS             | Full Scale Output Current               |      |            | 10   | 20    | 30   | mA     |

|                            | Output Compliance Range                 |      |            | 1.0  |       |      | V      |

|                            | Output Resistance                       |      |            |      | TBD   |      | kΩ     |

|                            | Output Capacitance                      |      |            |      | TBD   |      | pF     |

|                            | Offset                                  |      |            |      | TBD   |      | ppm/°C |

| TEMPERATURE DRIFT          | Gain                                    |      |            |      | TBD   |      | ppm/°C |

|                            | Reference Voltage                       |      |            |      | TBD   |      | ppm/°C |

| REFERENCE                  | Internal Reference Voltage              |      |            |      | 1.2   |      | V      |

| REFERENCE                  | Output Current                          |      |            |      | 100   |      | nA     |

| ANALOG SUPPLY              | VDDA33                                  |      |            | 3.13 | 3.3   | 3.47 | V      |

| VOLTAGES                   | VDDA18                                  |      |            | 1.70 | 1.8   | 1.90 | V      |

| DICITAL CLIDDLY            | VDDD33                                  |      |            | 3.13 | 3.3   | 3.47 | V      |

| DIGITAL SUPPLY<br>VOLTAGES | VDDD18                                  |      |            | 1.70 | 1.8   | 1.90 | V      |

| VOLIAGES                   | VDDCLK                                  |      |            | 1.70 | 1.8   | 1.90 | V      |

| POWER CONSUMPTION          | 600 MSPS                                |      |            |      | TBD   |      | mW     |

|                            | Standby Power                           |      |            |      | TBD   |      | mW     |

Table 1: DC Specifications

Rev. PrA | Page 3 of 34

<sup>&</sup>lt;sup>1</sup> Specifications subject to change without notice

## **DIGITAL SPECIFICATIONS**

## (VDD33 = 3.3 V, VDD18 = 1.8 V, MAXIMUM SAMPLE RATE, UNLESS OTHERWISE NOTED)

| Parameter                       |                                   | Temp | Test Level | Min | Тур | Max | Unit |

|---------------------------------|-----------------------------------|------|------------|-----|-----|-----|------|

| DAC CLOCK INPUT<br>(CLK+, CLK-) | Differential peak-to-peak Voltage |      |            |     | 800 |     | mV   |

|                                 | Common Mode Voltage               |      |            |     | 400 |     | mV   |

|                                 | Maximum Clock Rate                |      |            |     | 1   |     | GSPS |

| SERIAL PERIPHERAL               | Maximum Clock Rate (SCLK)         |      |            |     |     | 40  | MHz  |

|                                 | Maximum Pulse width high          |      |            |     |     | TBD | ns   |

| IIVIEIII /ICE                   | Maximum pulse width low           |      |            |     |     | TBD | ns   |

Table 2: Digital Specifications

#### **AC SPECIFICATIONS**

## (VDD33 = 3.3 V, VDD18 = 1.8 V, MAXIMUM SAMPLE RATE, UNLESS OTHERWISE NOTED)

|                                            | Parameter                                                  |  |  | Min | Тур  | Max | Unit    |

|--------------------------------------------|------------------------------------------------------------|--|--|-----|------|-----|---------|

| -                                          | Output Settling Time (tst) (to 0.025%)                     |  |  |     | TBD  |     | ns      |

| DYNAMIC                                    | Output Rise Time (10% to 90%)                              |  |  |     | TBD  |     | ns      |

| PERFORMANCE                                | Output Fall Time (90% to 10%)                              |  |  |     | TBD  |     | ns      |

|                                            | Output Noise (IoutFS=20mA)                                 |  |  |     | TBD  |     | pA/rtHz |

|                                            | $f_{DAC} = 100 \text{ MSPS}, f_{OUT} = 20 \text{ MHz}$     |  |  |     | 73   |     | dBc     |

| SPURIOUS FREE<br>DYNAMIC RANGE             | $f_{DAC} = 200 \text{ MSPS}, f_{OUT} = 50 \text{ MHz}$     |  |  |     | 73   |     | dBc     |

| (SFDR)                                     | $f_{DAC} = 400 \text{ MSPS}, f_{OUT} = 70 \text{ MHz}$     |  |  |     | 75   |     | dBc     |

| (3. 2)                                     | $f_{DAC} = 800 \text{ MSPS}, f_{OUT} = 70 \text{ MHz}$     |  |  |     | 78   |     | dBc     |

|                                            | $f_{DAC} = 200 \text{ MSPS}, f_{OUT} = 50 \text{ MHz}$     |  |  |     | 82   |     | dBc     |

| TWO-TONE INTERMODULATION                   | $f_{DAC} = 400 \text{ MSPS}, f_{OUT} = 60 \text{ MHz}$     |  |  |     | 79   |     | dBc     |

| DISTORTION (IMD)                           | $f_{DAC} = 400 \text{ MSPS}, f_{OUT} = 80 \text{ MHz}$     |  |  |     | 72   |     | dBc     |

| 2.2. CC. (2)                               | f <sub>DAC</sub> = 800 MSPS, f <sub>OUT</sub> = 100 MHz    |  |  |     | 79   |     | dBc     |

|                                            | f <sub>DAC</sub> = 156 MSPS, f <sub>OUT</sub> = 60 MHz     |  |  |     | -149 |     | dBm/Hz  |

| NOISE SPECTRAL                             | $f_{DAC} = 200 \text{ MSPS}, f_{OUT} = 80 \text{ MHz}$     |  |  |     | -148 |     | dBm/Hz  |

| DENSITY (NSD)                              | f <sub>DAC</sub> = 312 MSPS, f <sub>OUT</sub> = 100 MHz    |  |  |     | -150 |     | dBm/Hz  |

|                                            | $f_{DAC} = 400 \text{ MSPS}, f_{OUT} = 100 \text{ MHz}$    |  |  |     | -150 |     | dBm/Hz  |

| WCDMA ADJACENT                             | $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 20 \text{ MHz}$  |  |  |     | 71   |     | dBc     |

| CHANNEL LEAKAGE                            | $f_{DAC} = 491.52 \text{ MSPS}, f_{OUT} = 100 \text{ MHz}$ |  |  |     | 70   |     | dBc     |

| RATIO (ACLR), SINGLE<br>CARRIER            | f <sub>DAC</sub> = 491.52 MSPS, f <sub>OUT</sub> = 200 MHz |  |  |     | 65   |     | dBc     |

| WCDMA SECOND                               | $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 60 \text{ MHz}$  |  |  |     | 69   |     | dBc     |

| ADJACENT CHANNEL                           | f <sub>DAC</sub> = 491.52 MSPS, f <sub>OUT</sub> = 100 MHz |  |  |     | 71   |     | dBc     |

| LEAKAGE RATIO<br>(ACLR), SINGLE<br>CARRIER | f <sub>DAC</sub> = 491.52 MSPS, f <sub>OUT</sub> = 200 MHz |  |  |     | 67   |     | dBc     |

Table 3: AC Specifications

## PIN FUNCTION DESCRIPTIONS

| Pin<br>No. | Name        | Description                        | Pin<br>No. | Name     | Description                                |

|------------|-------------|------------------------------------|------------|----------|--------------------------------------------|

| 1          | VDDC18      | 1.8 V Clock Supply                 | 51         | P2D<6>   | Port 2 Data Input D6                       |

| 2          | VDDC18      | 1.8 V Clock Supply                 | 52         | P2D<5>   | Port 2 Data Input D5                       |

| 3          | VSSC        | Clock Common                       | 53         | VDDD18   | 1.8 V Digital Supply                       |

| 4          | VSSC        | Clock Common                       | 54         | VSSD     | Digital Common                             |

| 5          | CLK+        | Differential Clock Input           | 55         | P1D<4>   | Port 2 Data Input D4                       |

| 6          | CLK-        | Differential Clock Input           | 56         | P1D<3>   | Port 2 Data Input D3                       |

| 7          | VSSC        | Clock Common                       | 57         | P1D<2>   | Port 2 Data Input D2                       |

| 8          | VSSC        | Clock Common                       | 58         | P1D<1>   | Port 2 Data Input D1                       |

| 9          | VDDC18      | 1.8 V Clock Supply                 | 59         | P1D<0>   | Port 2 Data Input D0 (LSB)                 |

| 10         | VDDC18      | 1.8 V Clock Supply                 | 60         | VDDD18   | 1.8 V Digital Supply                       |

| 11         | VSSC        | Clock Common                       | 61         | VDDD33   | 3.3 V Digital Supply                       |

| 12         | VSSC        | Clock Common                       | 62         | SYNC_O-  | Differential Synchronization Output        |

| 13         | SYNC_I+     | Differential Synchronization Input | 63         | SYNC_O+  | Differential Synchronization Output        |

| 14         | SYNC_I-     | Differential Synchronization Input | 64         | VSSD     | Digital Common                             |

| 15         | VSSD        | Digital Common                     | 65         | PLL_LOCK | PLL Lock Indicator                         |

| 16         | VDDD33      | 3.3 V Digital Supply               | 66         | SPI_SDO  | SPI Port Data Output                       |

| 17         | P1D<15>     | Port 1 Data Input D15 (MSB)        | 67         | SPI_SDIO | SPI Port Data Input/Output                 |

| 18         | P1D<14>     | Port 1 Data Input D14              | 68         | SPI_CLK  | SPI Port Clock                             |

| 19         | P1D<13>     | Port 1 Data Input D13              | 69         | SPI_CSB  | SPI Port Chip Select Bar                   |

| 20         | P1D<12>     | Port 1 Data Input D12              | 70         | RESET    | Reset                                      |

| 21         | P1D<11>     | Port 1 Data Input D11              | 71         | IRQ      | Interrupt Request                          |

| 22         | VSSD        | Digital Common                     | 72         | VSS      | Analog Common                              |

| 23         | VDDD18      | 1.8 V Digital Supply               | 73         | IPTAT    | Reference Current                          |

| 24         | P1D<10>     | Port 1 Data Input D10              | 74         | VREF     | Voltage Reference Output                   |

| 25         | P1D<9>      | Port 1 Data Input D9               | 75         | l120     | 120 μA Reference Current                   |

| 26         | P1D<8>      | Port 1 Data Input D8               | 76         | VDDA33   | 3.3 V Analog Supply                        |

| 27         | P1D<7>      | Port 1 Data Input D7               | 77         | VSSA     | Analog Common                              |

| 28         | P1D<6>      | Port 1 Data Input D6               | 78         | VDDA33   | 3.3 V Analog Supply                        |

| 29         | P1D<5>      | Port 1 Data Input D5               | 79         | VSSA     | Analog Common                              |

| 30         | P1D<4>      | Port 1 Data Input D4               | 80         | VDDA33   | 3.3 V Analog Supply                        |

| 31         | P1D<3>      | Port 1 Data Input D3               | 81         | VSSA     | Analog Common                              |

| 32         | VSSD        | Digital Common                     | 82         | VSSA     | Analog Common                              |

| 33         | VDDD18      | 1.8 V Digital Supply               | 83         | IOUT2_P  | Differential DAC Current Output, Channel 2 |

| 34         | P1D<2>      | Port 1 Data Input D2               | 84         | IOUT2_N  | Differential DAC Current Output, Channel 2 |

| 35         | P1D<1>      | Port 1 Data Input D1               | 85         | VSSA     | Analog Common                              |

| 36         | P1D<0>      | Port 1 Data Input D0 (LSB)         | 86         | AUX2_P   | Auxiliary DAC Voltage Output, Channel 2    |

| 37         | DATACLK_OUT | Data Clock Output                  | 87         | AUX2_N   | Auxiliary DAC Voltage Output, Channel 2    |

| 38         | VDDD33      | 3.3 V Digital Supply               | 88         | VSSA     | Analog Common                              |

| 39         | TXENABLE    | Transmit Enable                    | 89         | AUX1_N   | Auxiliary DAC Voltage Output, Channel 1    |

| 40         | P2D<15>     | Port 2 Data Input D15 (MSB)        | 90         | AUX1_N   | Auxiliary DAC Voltage Output, Channel 1    |

| 41         | P2D<14>     | Port 2 Data Input D14              | 91         | VSSA     | Analog Common                              |

| 42         | P2D<13>     | Port 2 Data Input D13              | 92         | IOUT1_N  | Differential DAC Current Output, Channel 1 |

| 43         | VDDD18      | 1.8 V Digital Supply               | 93         | IOUT1_N  | Differential DAC Current Output, Channel 1 |

| 44         | VSSD        | Digital Common                     | 94         | VSSA     | Analog Common                              |

| 45         | P2D<12>     | Port 2 Data Input D12              | 95         | VSSA     | Analog Common                              |

| 46         | P2D<12>     | Port 2 Data Input D11              | 96         | VDDA33   | 3.3 V Analog Supply                        |

| 47         | P2D<10>     | Port 2 Data Input D10              | 97         | VSSA     | Analog Common                              |

| 48         | P2D<10>     | Port 2 Data Input D19              | 98         | VDDA33   | 3.3 V Analog Supply                        |

| 70         | 1 ムロヘヨン     | 1 OIL 2 Data IIIPUL D3             |            |          |                                            |

| 49         | P2D<8>      | Port 2 Data Input D8               | 99         | VSSA     | Analog Common                              |

Table 4: Pin Function Descriptions

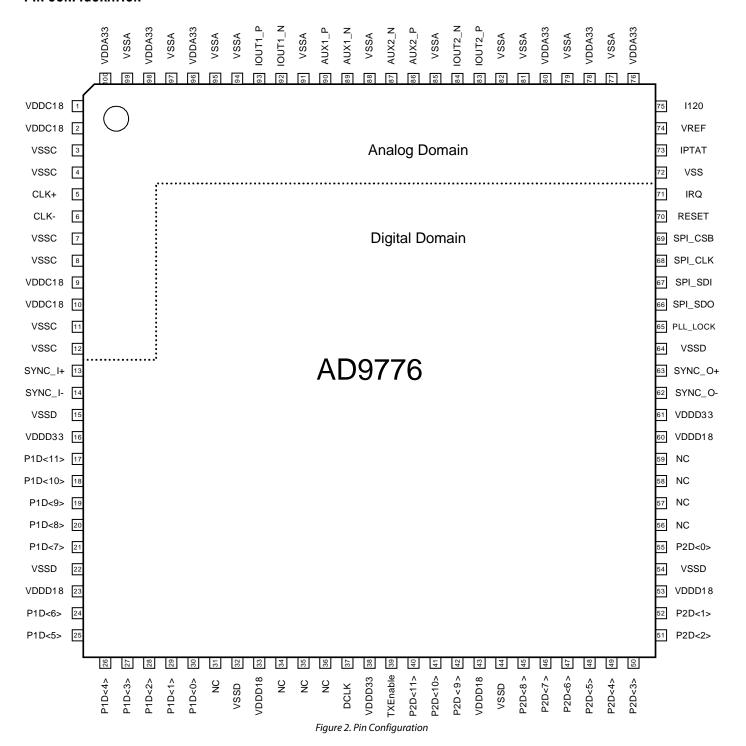

## **PIN CONFIGURATION**

## INTERPOLATION FILTER COEFFICIENTS

Table 5: Halfband Filter 1

| Lower       | Upper       | Integer |

|-------------|-------------|---------|

| Coefficient | Coefficient | Value   |

|             |             |         |

| H(1)        | H(55)       | -4      |

| H(2)        | H(54)       | 0       |

| H(3)        | H(53)       | 13      |

| H(4)        | H(52)       | 0       |

| H(5)        | H(51)       | -34     |

| H(6)        | H(50)       | 0       |

| H(7)        | H(49)       | 72      |

| H(8)        | H(48)       | 0       |

| H(9)        | H(47)       | -138    |

| H(10)       | H(46)       | 0       |

| H(11)       | H(45)       | 245     |

| H(12)       | H(44)       | 0       |

| H(13)       | H(43)       | -408    |

| H(14)       | H(42)       | 0       |

| H(15)       | H(41)       | 650     |

| H(16)       | H(40)       | 0       |

| H(17)       | H(39)       | -1003   |

| H(18)       | H(38)       | 0       |

| H(19)       | H(37)       | 1521    |

| H(20)       | H(36)       | 0       |

| H(21)       | H(35)       | -2315   |

| H(22)       | H(34)       | 0       |

| H(23)       | H(33)       | 3671    |

| H(24)       | H(32)       | 0       |

| H(25)       | H(31)       | -6642   |

| H(26)       | H(30)       | 0       |

| H(27)       | H(29)       | 20755   |

| H(28)       |             | 32768   |

## Table 6: Halfband Filter 2

| Lower       | Upper       | Integer |

|-------------|-------------|---------|

| Coefficient | Coefficient | Value   |

| H(1)        | H(23)       | -2      |

| H(2)        | H(22)       | 0       |

| H(3)        | H(21)       | 17      |

| H(4)        | H(20)       | 0       |

| H(5)        | H(19)       | -75     |

| H(6)        | H(18)       | 0       |

| H(7)        | H(17)       | 238     |

| H(8)        | H(16)       | 0       |

| H(9)        | H(15)       | -660    |

| H(10)       | H(14)       | 0       |

| H(11)       | H(13)       | 2530    |

| H(12)       |             | 4096    |

Table 7: Halfband Filter 3

| Lower       | Upper       | Integer |

|-------------|-------------|---------|

| Coefficient | Coefficient | Value   |

| H(1)        | H(15)       | -39     |

| H(2)        | H(14)       | 0       |

| H(3)        | H(13)       | 273     |

| H(4)        | H(12)       | 0       |

| H(5)        | H(11)       | -1102   |

| H(6)        | H(10)       | 0       |

| H(7)        | H(9)        | 4964    |

| H(8)        |             | 8192    |

## Table 8: Inverse Sinc Filter

| Lower       | Upper       | Integer |

|-------------|-------------|---------|

| Coefficient | Coefficient | Value   |

| H(1)        | H(9)        | 2       |

| H(2)        | H(8)        | -4      |

| H(3)        | H(7)        | 10      |

| H(4)        | H(6)        | -35     |

| H(5)        |             | 401     |

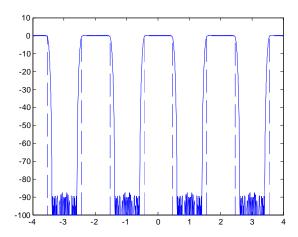

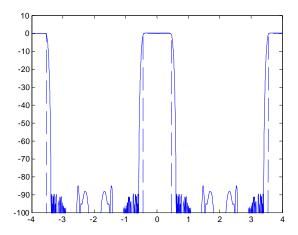

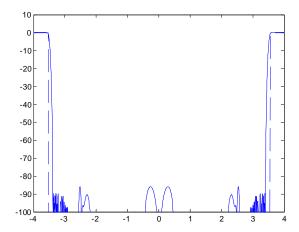

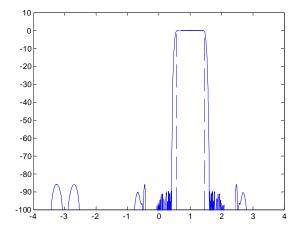

## INTERPOLATION FILTER RESPONSE CURVES

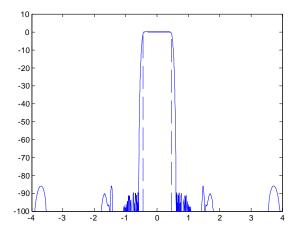

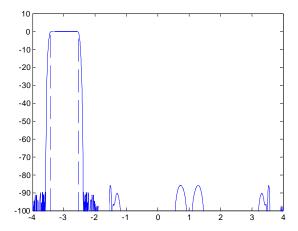

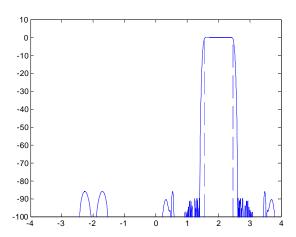

Figure 3. AD9776 2x Interpolation, Low Pass Response to  $\pm 4x$  Input Data Rate (Dotted Lines Indicate 1dBRoll-Off)

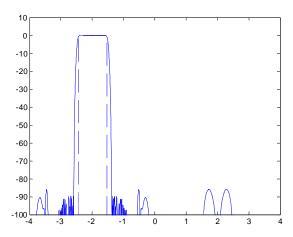

Figure 4. AD9776 4x Interpolation, Low Pass Response to  $\pm 4x$  Input Data Rate (Dotted Lines Indicate 1dBRoll-Off)

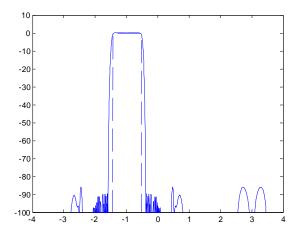

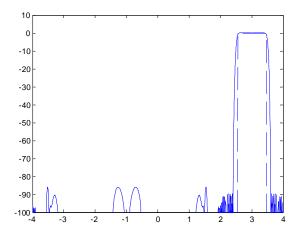

Figure 5.AD9776 8x Interpolation, Low Pass Response to  $\pm 4x$  Input Data Rate (Dotted Lines Indicate 1dBRoll-Off)

## **CHARACTERIZATION DATA**

Figure 6. AD9776 Typical INL

Figure 7. AD9776 Typical DNL

Figure 8. SFDR vs.  $F_{OUT}$ , 1x Interpolation

Figure 9. SFDR vs. Fout, 2x Interpolation

Figure 10. SFDR vs.  $F_{OUT}$ , 4x Interpolation

Figure 11. SFDR vs. Fout, 8x Interpolation

Figure 12. Third Order IMD vs.  $F_{OUT}$ , 1x Interpolation

Figure 13. Third Order IMD vs. Fout, 2x Interpolation

Figure 14. Third Order IMD vs.  $F_{OUT}$ , 4x Interpolation

Figure 15. Third Order IMD vs. F<sub>OUT</sub>, 8x Interpolation

Figure 16. Noise Spectral Density vs. F<sub>OUT</sub>, 1x Interpolation

Figure 17. Noise Spectral Density vs.  $F_{OUT}$ , 2x Interpolation

Figure 18. ACLR for 1<sup>st</sup> Adjacent Band WCDMA, 4x Interpolation. On-Chip Modulation is used to translate baseband signal to IF.

Figure 19. ACLR for 2nd Adjacent Band WCDMA, 4x Interpolation. On-Chip Modulation is used to translate baseband signal to IF.

Figure 20. ACLR for 3rd Adjacent Band WCDMA, 4x Interpolation. On-Chip Modulation is used to translate baseband signal to IF.

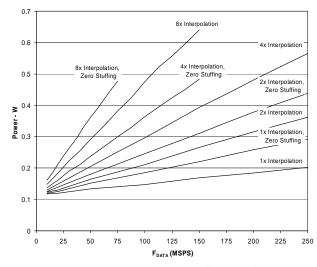

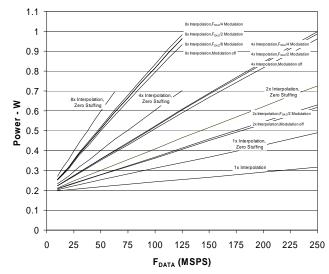

Figure 21. Power Dissipation, Single DAC Mode

Figure 22. Power Dissipation, Dual DAC Mode

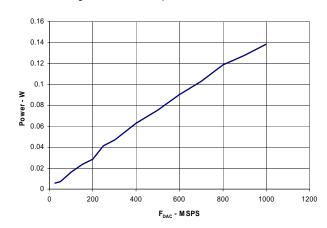

Figure 23. Power Dissipation of Inverse Sinc Filter

#### **GENERAL DESCRIPTION**

The AD9776 combines many features which make it a very attractive DAC for wired and wireless communications systems. The dual digital signal path and dual DAC structure allow an easy interface with common quadrature modulators when designing single sideband transmitters. The speed and performance of the AD9776 allow wider bandwidths/more carriers to be synthesized than with previously available DACs. The digital engine in the AD9776 uses a breakthrough filter architecture that combines the interpolation with a digital quadrature modulator. This allows the AD9776 to do digital quadrature frequency up conversion. The AD9776 also has features which allow simplified synchronization with incoming data, and also allows multiple AD9776s to be synchronized.

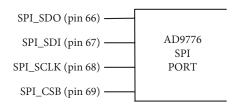

#### Serial Peripheral Interface

Figure 24. AD9776 SPI Port

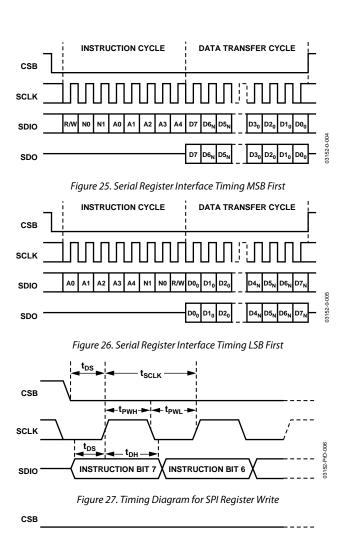

The AD9776 serial port is a flexible, synchronous serial communications port allowing easy interface to many industry-standard microcontrollers and microprocessors. The serial I/O is compatible with most synchronous transfer formats, including both the Motorola SPI\* and Intel\* SSR protocols. The interface allows read/write access to all registers that configure the AD9776. Single or multiple byte transfers are supported, as well as MSB first or LSB first transfer formats. The AD9776's serial interface port can be configured as a single pin I/O (SDIO) or two unidirectional pins for in/out (SDIO/SDO).

#### **General Operation of the Serial Interface**

There are two phases to a communication cycle with the AD9776. Phase 1 is the instruction cycle, which is the writing of an instruction byte into the AD9776, coincident with the first eight SCLK rising edges. The instruction byte provides the AD9776 serial port controller with information regarding the data transfer cycle, which is Phase 2 of the communication cycle. The Phase 1 instruction byte defines whether the upcoming data transfer is read or write, the number of bytes in the data transfer, and the starting register address for the first byte of the data transfer. The first eight SCLK rising edges of each communication cycle are used to write the instruction byte into the AD9776.

A logic high on the CS pin, followed by a logic low, will reset the SPI port timing to the initial state of the instruction cycle. This is true regardless of the present state of the internal registers or the other signal levels present at the inputs to the SPI port. If the SPI port is in the midst of an instruction cycle or a data transfer cycle,none of the present data will be written.

The remaining SCLK edges are for Phase 2 of the communication cycle. Phase 2 is the actual data transfer between the AD9776 and the system controller. Phase 2 of the communication cycle is a transfer of 1, 2, 3, or 4 data bytes as determined by the instruction byte. Using one multibyte transfer is the preferred method. Single byte data transfers are useful to reduce CPU overhead when register access requires one byte only. Registers change immediately upon writing to the last bit of each transfer byte.

#### **Instruction Byte**

The instruction byte contains the information shown in **Error!** Reference source not found..

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| 17  | 16 | 15 | 14 | 13 | 12 | I1 | 10  |

| R/W | N1 | N0 | A4 | А3 | A2 | A1 | A0  |

Table 9. SPI Instruction Byte

**R/W**, Bit 7 of the instruction byte, determines whether a read or a write data transfer will occur after the instruction byte write. Logic high indicates read operation. Logic 0 indicates a write operation. **N1**, **N0**, Bits 6 and 5 of the instruction byte, determine the number of bytes to be transferred during the data transfer cycle. The bit decodes are shown in Table 10.

A4, A3, A2, A1, A0, Bits 4, 3, 2, 1, 0 of the instruction byte, determine which register is accessed during the data transfer portion of the communications cycle. For multibyte transfers, this address is the starting byte address. The remaining register addresses are generated by the AD9776 based on the LSBFIRST bit (REG00, bit 6).

| N1 | N2 | Description      |

|----|----|------------------|

| 0  | 0  | Transfer 1 Byte  |

| 0  | 1  | Transfer 2 Bytes |

| 1  | 0  | Transfer 3 Bytes |

| 1  | 1  | Transfer 4 Bytes |

Table 10. Byte Transfer Count

#### **Serial Interface Port Pin Descriptions**

SCLK—Serial Clock. The serial clock pin is used to synchronize data to and from the AD9776 and to run the internal state machines. SCLK's maximum frequency is 20 MHz. All data input to the AD9776 is registered on the rising edge of SCLK. All data is driven out of the AD9776 on the falling edge of SCLK.

CSB—Chip Select. Active low input starts and gates a communication cycle. It allows more than one device to be used on the same serial communications lines. The SDO and SDIO pins will go to a high impedance state when this input is high. Chip select should stay low during the entire communication cycle.

# **Preliminary Technical Data**

**SDIO**—**Serial Data I/O.** Data is always written into the AD9776 on this pin. However, this pin can be used as a bidirectional data line. The configuration of this pin is controlled by Bit 7 of register address 00h. The default is Logic 0, which configures the SDIO pin as unidirectional.

**SDO**—**Serial Data Out**. Data is read from this pin for protocols that use separate lines for transmitting and receiving data. In the case where the AD9776 operates in a single bidirectional I/O mode, this pin does not output data and is set to a high impedance state.

#### MSB/LSB Transfers

The AD9776 serial port can support both most significant bit (MSB) first or least significant bit (LSB) first data formats. This functionality is controlled by register bit LSBFIRST (REG00, bit 6). The default is MSB first (LSBFIRST = 0).

When LSBFIRST = 0 (MSB first) the instruction and data bytes must be written from most significant bit to least significant bit. Multibyte data transfers in MSB first format start with an instruction byte that includes the register address of the most significant data byte. Subsequent data bytes should follow in order from high address to low address. In MSB first mode, the serial port internal byte address generator decrements for each data byte of the multibyte communication cycle.

When LSBFIRST = 1 (LSB first) the instruction and data bytes must be written from least significant bit to most significant bit. Multibyte data transfers in LSB first format start with an instruction byte that includes the register address of the least significant data byte followed by multiple data bytes. The serial port internal byte address generator increments for each byte of the multibyte communication cycle.

The AD9776 serial port controller data address will decrement from the data address written toward 0x00 for multibyte I/O operations if the MSB first mode is active. The serial port controller address will increment from the data address written toward 0x1F for multibyte I/O operations if the LSB first mode is active.

#### **Notes on Serial Port Operation**

The AD9776 serial port configuration is controlled by REG00, bits 6 and 7 . It is important to note that the configuration changes immediately upon writing to the last bit of the register. For multibyte transfers, writing to this register may occur during the middle of communication cycle. Care must be taken to compensate for this new configuration for the remaining bytes of the current communication cycle.

The same considerations apply to setting the software reset, RESET (REG00, bit 5). All registers are set to their default values EXCEPT REG00 and REG04 which remain unchanged.

Use of only single byte transfers when changing serial port

configurations or initiating a software reset is recommended to prevent unexpected device behavior.

Figure 28. Timing Diagram for SPI Register Read

DATA BIT n-1

DATA BIT n

SDIO

## SPI Register Map

| Register<br>Name                 | Addı | ress | Bit 7                  | Bit 6                                     | Bit 5                               | Bit 4                                                 | Bit 3                           | Bit 2                           | Bit 1                          | Bit 0      | Default |

|----------------------------------|------|------|------------------------|-------------------------------------------|-------------------------------------|-------------------------------------------------------|---------------------------------|---------------------------------|--------------------------------|------------|---------|

| Comm<br>Register                 | 00h  | 00   | SDIO<br>Bidirectional  | LSB,MSB First                             | Software<br>Reset                   | Power<br>Down<br>Mode                                 | Auto<br>Power<br>Down<br>Enable |                                 | PLL Lock<br>Indicator          |            | 00h     |

| Digital<br>Control<br>Register   | 01h  | 01   | Filter Interpolat      | tion Factor                               | Filter Interpola                    | Filter Interpolation Mode <4:0>  Zero Stuffing Enable |                                 |                                 |                                |            | 00h     |

|                                  | 02h  | 02   | Data Format            | One Port<br>Mode                          | Real Mode                           |                                                       | Inverse<br>Sinc<br>Enable       | DATACLK<br>Invert               | IQ Select<br>Invert            | Q First    | 00h     |

| Sync<br>Control                  | 03h  | 03   | Data Delay Mod         | de <1:0>                                  | Data Clock De                       | elay <2:0>                                            |                                 | Data Window                     | v Delay <2:0>                  |            | 00h     |

| Control                          | 04h  | 04   | Sync Out Delay         | <3:0>                                     |                                     |                                                       | Sync Window                     | v Delay <3:0>                   |                                |            | 00h     |

|                                  | 05h  | 05   | Sync Enable            | Sync Driver<br>Enable                     | Dac Clock Offs                      | set <2:0>                                             |                                 |                                 |                                |            | 00h     |

| Interrupt<br>Register            | 06h  | 06   | Data Delay<br>IRQ      | Sync Delay<br>IRQ                         | Cross<br>Control IRQ                |                                                       | Data Delay<br>IRQ Enable        | Sync Delay<br>IRQ Enable        | Cross<br>Control IRQ<br>Enable |            | 00h     |

| PLL Control                      | 07h  | 07   | PLL Band Selec         | t <4:0>                                   |                                     |                                                       |                                 | PLL Loop Cap                    | o Select <2:0>                 |            | CFh     |

|                                  | 08h  | 08   | PLL Enable             | PLL Output Fre<br><1:0>                   | q Divide PLL Loop Freq Divide <1:0> |                                                       |                                 | PLL Loop Filter Pole/Zero <2:0> |                                |            | 37h     |

| Misc.<br>Control<br>Register     | 09h  | 24   | PLL Error<br>Source    | PLL Ref<br>Bypass                         | PLL Gain <2:0                       | >                                                     |                                 | PLL Bias <2:0                   | >                              |            | 38h     |

| I DAC<br>Control                 | 0Ah  | 09   | IDAC Gain Adju         | stment <7:0>                              |                                     |                                                       |                                 |                                 |                                |            | F9h     |

| Register                         | 0Bh  | 10   | IDAC SLEEP             | IDAC Power<br>Down                        |                                     |                                                       |                                 |                                 | IDAC Gain Ad                   | djustment  | 01h     |

| Aux 1 DAC<br>Control<br>Register | 0Ch  | 11   | Auxiliary DAC1         | Data <7:0>                                |                                     |                                                       |                                 |                                 |                                |            | 00h     |

|                                  | 0Dh  | 12   | Auxiliary<br>DAC1 Sign | Auxiliary<br>DAC1<br>Current<br>Direction | Auxiliary DAC1 Data <9:8>           |                                                       |                                 |                                 |                                | C1 Data    | 00h     |

| Q DAC<br>Control<br>Register     | 0Eh  | 13   | QDAC Gain Adj          | ustment <7;0>                             |                                     |                                                       |                                 |                                 |                                |            | F9h     |

|                                  | 0Fh  | 14   | QDAC SLEEP             | QDAC Sleep                                |                                     |                                                       |                                 |                                 | QDAC Gain A                    | Adjustment | 01h     |

| Aux 2 DAC<br>Control<br>Register | 10h | 15 | Auxiliary DAC2         | Data <7:0>                                 |                                 |                                     |                            |               |                              | 00h |

|----------------------------------|-----|----|------------------------|--------------------------------------------|---------------------------------|-------------------------------------|----------------------------|---------------|------------------------------|-----|

|                                  | 11h | 16 | Auxiliary<br>DAC2 Sign | Auxiliary<br>DAC2<br>Current<br>Direction  | Auxiliary<br>DAC2 Power<br>Down |                                     |                            |               | Auxiliary DAC2 Data<br><9:8> | 00h |

|                                  | 12h | 17 | Cross Updel <7         | ross Updel <7:0>                           |                                 |                                     |                            |               |                              | 00h |

| Cross<br>Register                | 13h | 18 | Cross Dndel <7         | 0>                                         |                                 |                                     |                            |               |                              | 00h |

| Register                         | 14h | 19 | Cross Clock Div        | ide <3:0>                                  |                                 |                                     | Cross Wiggl                | e Delay <3:0> |                              | 00h |

|                                  | 15h | 20 | Cross Run              | Cross Status                               | Cross Done                      | Cross Wiggle <2:0> Cross Step <1:0> |                            |               |                              | 00h |

| Analog<br>Write                  | 16h | 23 | Analog Write <         | nalog Write <7:0>                          |                                 |                                     |                            |               | 00h                          |     |

| Analog<br>Control                | 17h | 21 | Mirror Roll Off <      | Mirror Roll Off <1:0>  Band Gap Trim <2:0> |                                 |                                     |                            |               | m <2:0>                      | 00h |

| Register                         | 18h | 22 | Stack Headroor         | n Control<7:0>                             |                                 |                                     |                            |               |                              | CAh |

| Analog<br>Status<br>Register     | 19h | 25 | Analog Status <        | Analog Status <7:0>                        |                                 |                                     |                            |               | h                            |     |

| Test 1<br>Register               | 1Ah | 26 | MISR Enable            | MISR IQ<br>Select                          | MISR<br>Samples                 |                                     | Internal<br>Data<br>Enable | Test Mode <2  | 2:0>                         | 00h |

| Test 2<br>Register               | 1Bh | 27 | BIST<31:24>            |                                            |                                 |                                     |                            |               |                              | h   |

| negistei                         | 1Ch | 28 | BIST<23:16>            | BIST<23:16>                                |                                 |                                     |                            |               |                              | h   |

|                                  | 1Dh | 29 | BIST<15:8>             |                                            |                                 |                                     |                            |               |                              | h   |

|                                  | 1Eh | 30 | BIST<7:0>              |                                            |                                 |                                     |                            |               |                              | h   |

Table 11: SPI Register Map

| Register (hex)           | Bits | Name                      | Function                                                             | Default |

|--------------------------|------|---------------------------|----------------------------------------------------------------------|---------|

| 00                       | 7    | SDIO Bidirectional        | 0: Use SDIO pin as input data only                                   | 0       |

| Comm Register            |      |                           | 1: Use SDIO as both input and output data                            |         |

|                          | 6    | LSB/MSB First             | 0: First bit of serial data is MSB of data byte                      | 0       |

|                          |      |                           | 1: First bit of serial data is LSB of data byte                      |         |

|                          | 5    | Software RESET            | Bit must be written with a 1, then 0 to soft reset SPI register map  | 0       |

|                          | 4    | Power Down                | 0: All circuitry is active                                           | 0       |

|                          |      | Mode                      | 1: Disable all digital and analog circuitry, only SPI port is active |         |

|                          | 3    | Auto Power Down<br>Enable |                                                                      | 0       |

|                          | 1    | PLL LOCK (read only)      | 0: PLL is not locked 1: PLL is locked                                | 0       |

| 01                       | 7:6  | Filter Interpolation      | 00: 1x interpolation                                                 | 00      |

| Digital Path Filter      | 7.0  | Rate                      | 01: 2x interpolation                                                 |         |

| Control                  |      |                           | 10: 4x interpolation                                                 |         |

|                          |      |                           | 11: 8x interpolation                                                 |         |

|                          | 5:2  | Control Halfband          | See Table 13 for filter modes                                        | 0000    |

|                          | 3.2  | Filters 1,2,3             | See Table 13 for filter friodes                                      | 0000    |

|                          | 0    | Zero Stuffing             | 0: Zero stuffing off                                                 | 0       |

|                          |      |                           | 1: Zero stuffing on                                                  |         |

|                          |      | 0: Signed binary          | 0                                                                    |         |

| General Mode             |      |                           | 1: Unsigned binary                                                   |         |

| Control                  | 6    | One Port Mode             | 0: Both input data ports receive data                                | 0       |

|                          |      |                           | 1: Data port 1 only receives data                                    |         |

|                          | 5    | Real Mode                 | 0: Enable Q path for signal processing                               | 0       |

|                          |      | aac                       | 1: Disable Q path data (clocks disabled)                             |         |

|                          | 3    | Inverse Sinc              | 0: Inverse sinc disabled                                             | 0       |

|                          | '    | Enable                    | 1: Inverse sinc disabled                                             | · ·     |

|                          | 2    | DATACLK Invert            | 0: Output DATACLK same phase as internal capture clock               | 0       |

|                          | 2    | DATACLINITIVEIT           | 1: Output DATACEK same phase as internal capture clock               | O       |

|                          | 1    | IQ Select Invert          | 0: TxEnable (pin 39) = 1, routes input data to I channel             | 0       |

|                          | '    | iQ select invert          | ·                                                                    | 0       |

|                          |      |                           | TxEnable (pin 39) =0, routes input data to Q channel                 |         |

|                          |      |                           | 1: TxEnable (pin 39) = 1, routes input data to Q channel             |         |

|                          |      | 0.51                      | TxEnable (pin 39) =0, routes input data to I channel                 |         |

|                          | 0    | Q First                   | 0: First byte of data is always I data at beginning of transmit      |         |

|                          |      |                           | 1: First byte of data is always Q data at beginning of transmit      |         |

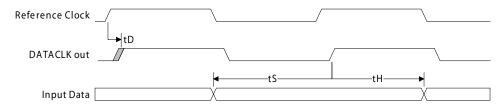

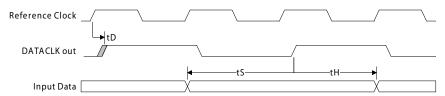

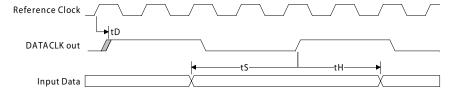

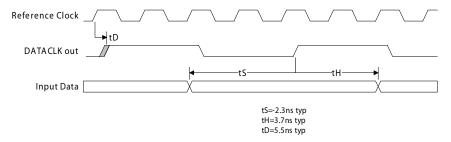

| 03                       | 7:6  | Data Delay Mode           | 00: Manual, no error correction                                      | 00      |

| Data Clock Delay         |      |                           | 01: Manual, continuous error correction                              |         |

|                          |      |                           | 10: automatic, one pass check                                        |         |

|                          |      |                           | 11: automatic, continuous pass check                                 |         |

|                          | 5:3  | Data Clock Delay          | Data Clock delay control                                             | 000     |

|                          | 2:0  | Data Window<br>Delay      | Window delay control                                                 | 000     |

| )4                       | 7:4  | Sync Output Delay         |                                                                      | 0000    |

| Synchronization<br>Delay | 3:0  | Sync Window<br>Delay      |                                                                      | 0000    |

| 05                       | 7    | Sync Enable               | 0: LVDS and synchronization rceiver logic off                        | 0       |

| Chip Sync and Data       |      |                           | 1: LVDS and synchronization rceiver logic on                         |         |

| Delay Control            | 6    | Sync Driver Enable        | 0: LVDS driver off                                                   | 0       |

|                          |      |                           | 1: LVDS driver on                                                    |         |

|                          | 5:3  | DAC Clock Offset          |                                                                      | 0       |

| 06<br>IRQ Status                    | 7   | Data Delay Error<br>(read only)                                                                 |                                                                                                                                                      | 0        |

|-------------------------------------|-----|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                     | 6   | Chip<br>Synchronization<br>Delay Error (read                                                    |                                                                                                                                                      | 0        |

|                                     | 5   | only)  Cross Control                                                                            |                                                                                                                                                      | 0        |

|                                     | 3   | Error (read only)  Data Delay Error                                                             |                                                                                                                                                      | 0        |

|                                     |     | Enable                                                                                          |                                                                                                                                                      | -        |

|                                     | 2   | Chip<br>Synchronization<br>Error Enable                                                         |                                                                                                                                                      | 0        |

|                                     | 1   | Cross Control<br>Error Enable                                                                   |                                                                                                                                                      | 0        |

| 07<br>PLL Band and Divide           | 7:3 | PLL Band Select<br>See Table 14 for<br>values.                                                  |                                                                                                                                                      | 11001    |

|                                     | 2:0 | PLL Ripple Cap<br>Adjust                                                                        |                                                                                                                                                      | 111      |

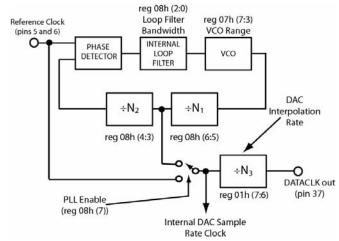

| 08<br>PLL Enable and<br>Charge Pump | 7   | PLL Enable                                                                                      | 0: PLL off, DAC rate clock supplied by outside source 1: PLL on, DAC rate clock synthesized internally from data rate clock via PLL clock multiplier | 0        |

| Control                             | 6:5 | PLL Output Divide<br>Ratio                                                                      | 00: Divide by 1 01: Divide by 2 10: Divide by 4 11: Divide by 8                                                                                      | 01       |

|                                     | 4:3 | PLL Loop<br>Feedback Divide<br>Ratio                                                            | 00: Divide by 1 01: Divide by 2 10: Divide by 4 11: Divide by 8                                                                                      | 10       |

|                                     | 2:0 | PLL Loop Filter Bandwidth Tuning Recommended Settings. See Table 14 for PLL Band Select values. | 000: PLL band select 00000-00111 100: PLL band select 01000-01111 110: PLL band select 10000-10111 111: PLL band select 11000-11111                  | 111      |

| 09<br>Misc. Control                 | 7   | PLL Error Bit<br>Source                                                                         | 0: Phase error detect 1: Range limit                                                                                                                 | 0        |

|                                     | 6   | PLL Reference<br>Bypass                                                                         | 0: Use PLL reference 1: Use DAC reference                                                                                                            | 0        |

|                                     | 5:3 | VCO AGC Gain<br>Control. See Table<br>14 for PLL Band<br>Select values.                         | 000: PLL band select 00000-00111 100: PLL band select 01000-01111 110: PLL band select 10000-10111 111: PLL band select 11000-11111                  | 111      |

|                                     | 2:0 | PLL Bias Current<br>Level/Trim                                                                  |                                                                                                                                                      | 000      |

| 0A<br>IDAC Gain                     | 7:0 | IDAC Gain<br>Adjustment                                                                         | (7:0) LSB slice of 10 bit gain setting word for IDAC                                                                                                 | 11111001 |

| 0B<br>IDAC Gain and                 | 7   | IDAC Sleep                                                                                      | 0: IDAC on<br>1: IDAC off                                                                                                                            | 0        |

| Control                             | 6   | IDAC Power Down                                                                                 | 0: IDAC on<br>1: IDAC off                                                                                                                            | 0        |

|                                     | 1:0 | IDAC Gain<br>Adjustment                                                                         | (9:8) MSB slice of 10 bit gain setting word for IDAC                                                                                                 | 01       |

| 0C                                  | 7:0 | Aux DAC1 Gain                                                                                   | (7:0) LSB slice of 10 bit gain setting word for Aux DAC1                                                                                             | 00000000 |

| 0D                               | 7        | Aux DAC1 Sign                                  | 0: Positive                                                                                          | 0        |

|----------------------------------|----------|------------------------------------------------|------------------------------------------------------------------------------------------------------|----------|

| Auxiliary DAC1 Control and Data  |          |                                                | 1: Negative                                                                                          |          |

| Control and Data                 | 6        | Aux DAC1<br>Direction                          | 0: Source<br>1: Sink                                                                                 | 0        |

|                                  | 5        | Aux DAC1 Sleep                                 | 0: Aux DAC1 on<br>1: Aux DAC 1 off                                                                   | 0        |

|                                  | 1:0      | Aux DAC1 Gain<br>Adjustment                    | (9:8) MSB slice of 10 bit gain setting word for Aux DAC1                                             | 00       |

| 0E<br>QDAC Gain                  | 7:0      | QDAC Gain<br>Adjustment                        | (7:0) LSB slice of 10 bit gain setting word for QDAC                                                 | 11111001 |

| 0F<br>QDAC Gain and              | 7        | QDAC Sleep                                     | 0: QDAC on<br>1: ODAC off                                                                            | 0        |

| Control                          | 6        | QDAC Power<br>Down                             | 0: QDAC on<br>1: QDAC off                                                                            | 0        |

|                                  | 1:0      | QDAC Gain<br>Adjustment                        | (9:8) MSB slice of 10 bit gain setting word for QDAC                                                 | 01       |

| 10<br>Auxiliary DAC2 Gain        | 7:0      | Aux DAC2 Gain<br>Adjustment                    | (7:0) LSB slice of 10 bit gain setting word for Aux DAC2                                             | 00000000 |

| 11 Auxiliary DAC2                | 7        | Aux DAC2 Sign                                  | 0: Positive<br>1: Negative                                                                           | 0        |

| Control and Data                 | 6        | Aux DAC2<br>Direction                          | 0: Source<br>1: Sink                                                                                 | 0        |

|                                  | 5        | Aux DAC2 Sleep                                 | 0: Aux DAC1 on<br>1: Aux DAC 1 off                                                                   | 0        |

|                                  | 1:0      | Aux DAC2 Gain<br>Adjustment                    | (9:8) MSB slice of 10 bit gain setting word for Aux DAC2                                             | 00       |

| 12<br>Cross Point Upper<br>Delay | 7:0      | Updelay                                        | Value above zero for upper cross delay (bits 7,6, unused)                                            | 00000000 |

| 13<br>Cross Point Upper<br>Delay | 7:0      | Dndelay                                        | Value below zero for lower cross delay (bits 7,6, unused)                                            | 00000000 |

| 14<br>Wiggle Delay for           | 7:3      | Cross Control<br>Clock Delay                   | Divide rate of CNTCLK by 2^(3:0), CNTCLK = 1/16 DAC clock rate                                       | 00000    |

| Cross Point Control              | 2:0      | Wiggle Delay                                   | Time step in 2^(Wiggle Delay) CNTCLK cycles                                                          | 000      |

| 15<br>Cross Point Control        | 7        | Cross Run                                      | 0: Disables Cross Control loop 1: Enables Cross Control loop                                         | 0        |

|                                  | 6        | Cross Status (read only)                       | 0: Control loop is lowering cross point 1: Control loop is raising cross point                       | 0        |

|                                  | 5        | Cross Done (read only)                         | 0: Control loop is chnaging cross point value 1: Control loop is holding cross point value           | 0        |

|                                  | 4:2      | Cross Wiggle                                   | (2:0) Number of iterations allowed in control loop                                                   | 000      |

|                                  | 1:0      | Cross Step                                     | (1:0) Value to change cross point value per iteration (wiggle)                                       | 00       |

| 16<br>Analog Write               | 7:0      | Analog Write                                   | Provides extra writeable control registers for analog circuit                                        | 00000000 |

| 17<br>Mirror Roll off and        | 7:6      | Mirror Roll off<br>Frequency                   |                                                                                                      | 00       |

| band gap Trim                    | 2:0      | Band Gap Trim<br>Temperature<br>Characteristic |                                                                                                      | 000      |

| 18                               |          |                                                | Output stack headroom control                                                                        |          |

| Output Stack<br>headroom Control |          |                                                | Overdrive (current density) trim (temperature packing)  Reference offset from VDD3V (vcas centering) |          |

| 19                               | 7:0      | Analog Status                                  | Provides extra status register for analog circuitry (unused, read only)                              |          |

| Analog Status                    | <u> </u> |                                                |                                                                                                      |          |

| 1A                           | 7   | MISR Enable    | 0: MISR disabled                       | 0   |

|------------------------------|-----|----------------|----------------------------------------|-----|

| MISR Control                 |     |                | 1: MISR Enabled                        |     |

|                              | 6   | MISR IQ Select | 0: Read back I path signature          | 0   |

|                              |     |                | 1: Read back Q path signature          |     |

|                              | 5   | MISR Samples   | 0: MISR uses short sample period       | 0   |

|                              |     |                | 1: MISR uses long sample period        |     |

|                              | 3   | Internal Data  | 0: Internal data generator off         | 0   |

|                              |     | Enable         | 1: Internal data generator on          |     |

|                              | 2:0 | Test Mode      | 000: Normal data port operation        | 000 |

|                              |     |                | 001-111: To be defined test modes      |     |

| 1B                           | 7:0 | MISR Signature | (31:24) Slice of 32 bit MISR signature |     |

| MISR Signature<br>Register 1 |     |                |                                        |     |

| 1C                           | 7:0 | MISR Signature | (23:16) Slice of 32 bit MISR signature |     |

| MISR Signature<br>Register 2 |     |                |                                        |     |

| 1D                           | 7:0 | MISR Signature | (15:8) Slice of 32 bit MISR signature  |     |

| MISR Signature<br>Register 3 |     |                |                                        |     |

| 1E                           | 7:0 | MISR Signature | (7:0) Slice of 32 bit MISR signature   |     |

| MISR Signature<br>Register 4 |     |                |                                        |     |

Table 12: SPI RegisterDescription

# AD9776

# **Preliminary Technical Data**

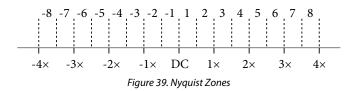

| Interp.<br>Factor | Filter<br>Mode | Filter1 mode<br>(Mode_F1) | Filter2 mode<br>(Mode_F2) | Filter3 mode<br>(Mode_F3) | Modulation | Nyquist<br>Zone | F_low     | Center        | F_High |                                        |

|-------------------|----------------|---------------------------|---------------------------|---------------------------|------------|-----------------|-----------|---------------|--------|----------------------------------------|

| <7:6>             | <5:2>          |                           |                           |                           |            | Passband        | (Freq. No | rmalized to F | DAC)   |                                        |

| 8                 | 00h            | 0                         | 0                         | 0                         | DC_odd     | 1               | -0.05     | 0             | 0.05   | In 8x<br>interpolation,                |

| 8                 | 01h            | 1                         | 1                         | 0                         | DC_even    | 2               | 0.0125    | 0.0625        | 0.1125 | BW=0.0375-<br>(0.1* F <sub>DAC</sub> ) |

| 8                 | 02h            | 2                         | 2                         | 1                         | F/8_odd    | 3               | 0.075     | 0.125         | 0.175  | Worst case:                            |

| 8                 | 03h            | 3                         | 3                         | 2                         | F/8_even   | 4               | 0.1375    | 0.1875        | 0.2375 | F/32                                   |

| 8                 | 04h            | 0                         | 4                         | 2                         | 2F/8_odd   | 5               | 0.2       | 0.25          | 0.3    |                                        |

| 8                 | 05h            | 1                         | 5                         | 2                         | 2F/8_even  | 6               | 0.2625    | 0.3125        | 0.3625 |                                        |

| 8                 | 06h            | 2                         | 6                         | 3                         | 3F/8_odd   | 7               | 0.325     | 0.375         | 0.425  |                                        |

| 8                 | 07h            | 3                         | 7                         | 4                         | 3F/8_even  | 8               | 0.3875    | 0.4375        | 0.4875 |                                        |

| 8                 | 08h            | 0                         | 0                         | 4                         | -4F/8_even | -8              | 0.45      | 0.5           | 0.55   |                                        |

| 8                 | 09h            | 1                         | 1                         | 4                         | -4F/8_odd  | -7              | 0.5125    | 0.5625        | 0.6125 |                                        |

| 8                 | 0Ah            | 2                         | 2                         | 5                         | -3F/8_even | -6              | 0.575     | 0.625         | 0.675  |                                        |

| 8                 | 0Bh            | 3                         | 3                         | 6                         | -3F/8_odd  | -5              | 0.6375    | 0.6875        | 0.7375 |                                        |

| 8                 | 0Ch            | 0                         | 4                         | 6                         | -2F/8_even | -4              | 0.7       | 0.75          | 0.8    |                                        |

| 8                 | 0Dh            | 1                         | 5                         | 6                         | -2F/8_odd  | -3              | 0.7625    | 0.8125        | 0.8625 |                                        |

| 8                 | 0Eh            | 2                         | 6                         | 7                         | -F/8_even  | -2              | 0.825     | 0.875         | 0.925  |                                        |

| 8                 | 0Fh            | 3                         | 7                         | 0                         | -F/8_odd   | -1              | 0.8875    | 0.9375        | 0.9875 |                                        |

| 4                 | 00h            | 0                         | 0                         | OFF                       | DC_odd     | 1               | -0.1      | 0             | 0.1    | In 8x<br>interpolation,                |

| 4                 | 01h            | 1                         | 1                         | OFF                       | DC_even    | 2               | 0.025     | 0.125         | 0.225  | BW=0.075-(0.2*<br>F <sub>DAC</sub> )   |

| 4                 | 02h            | 2                         | 2                         | OFF                       | F/4_odd    | 3               | 0.15      | 0.25          | 0.35   | Worst case:                            |

| 4                 | 03h            | 3                         | 3                         | OFF                       | F/4_even   | 4               | 0.275     | 0.375         | 0.475  | F/16                                   |

| 4                 | 04h            | 0                         | 4                         | OFF                       | -F/2_even  | -4              | 0.4       | 0.5           | 0.6    |                                        |

| 4                 | 05h            | 1                         | 5                         | OFF                       | -F/2_odd   | -3              | 0.525     | 0.625         | 0.725  |                                        |

| 4                 | 06h            | 2                         | 6                         | OFF                       | -F/4_even  | -2              | 0.65      | 0.75          | 0.85   |                                        |

| 4                 | 07h            | 3                         | 7                         | OFF                       | -F/4_odd   | -1              | 0.775     | 0.875         | 0.975  |                                        |

| 2                 | 00h            | 0                         | OFF                       | OFF                       | DC_odd     | 1               | -0.2      | 0             | 0.2    | In 2x<br>Interpolation                 |

| 2                 | 01h            | 1                         | OFF                       | OFF                       | DC_even    | 2               | 0.05      | 0.25          | 0.45   | BW=0.15-0.4                            |

| 2                 | 02h            | 2                         | OFF                       | OFF                       | -F/2_even  | -1              | 0.3       | 0.5           | 0.7    | F <sub>DAC</sub>                       |

| 2                 | 03h            | 3                         | OFF                       | OFF                       | -F/2_odd   | -2              | 0.55      | 0.75          | 0.95   | Worst case: F/8                        |

|                   |                |                           |                           |                           |            |                 |           |               |        |                                        |

Table 13: Interpolation Filter Modes, see Reg 01, bits 5:2

# **Preliminary Technical Data**

| PLL Frequency Band Select |                  |

|---------------------------|------------------|

| PLL Band Select Value     | Frequency in MHz |

| 11111 (31)                | 804 – 850        |

| 11110 (30)                | 827 – 875        |

| 11101 (29)                | 850 – 899        |

| 11100 (28)                | 875 – 925        |

| 11011 (27)                | 899 – 951        |

| 11010 (26)                | 925 – 977        |

| 11001 (25)                | 951 – 1005       |

| 11000 (24)                | 977 – 1032       |

| 10111 (23)                | 1004 – 1061      |

| 10110 (22)                | 1032 – 1089      |

| 10101 (21)                | 1060 – 1119      |

| 10100 (20)                | 1089 – 1149      |

| 10011 (19)                | 1118 – 1179      |

| 10010 (18)                | 1148 – 1210      |

| 10001 (17)                | 1176 – 1239      |

| 10000 (16)                | 1206 – 1270      |

| 01111 (15)                | 1237 – 1302      |

| 01110 (14)                | 1268 – 1334      |

| 01101 (13)                | 1299 – 1366      |

| 01100 (12)                | 1331 – 1399      |

| 01011 (11)                | 1363 – 1432      |

| 01010 (10)                | 1396 – 1466      |

| 01001 (9)                 | 1425 – 1495      |

| 01000 (8)                 | 1458 – 1529      |

| 00111 (7)                 | 1492 – 1563      |

| 00110 (6) | 1525 – 1597 |

|-----------|-------------|

| 00101 (5) | 1560 – 1632 |

| 00100 (4) | 1594 – 1667 |

| 00011 (3) | 1629 – 1702 |

| 00010 (2) | 1665 – 1737 |

| 00001 (1) | 1700 – 1773 |

| 00000 (0) | 1735 – 1810 |

Table 14. VCO Frequency Range vs. PLL Band Select Value

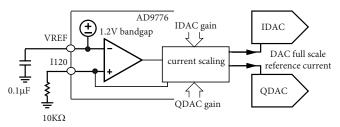

#### Internal Reference/Full Scale Current Generation

Full scale current on the AD9776 IDAC and QDAC can be set from 10 to 30ma. Initially, the 1.2V bandgap reference is used to set up a current in an external resistor connected to I120 (pin 75). A simplified block diagram of the AD9776 reference circuitry is given below in *Figure 29*. The recommended value for the external resistor is 10K  $\Omega$ , which sets up an I REFERENCE in the resistor of 120 $\mu$ a. Internal current mirrors provide a current gain scaling, where IDAC or QDAC gain is a 10 bit word in the SPI port register (registers 0A, 0B, 0E, and 0F). The default value for the DAC gain registers gives an IFS of 20ma.

Figure 29. Reference Circuitry

where IFS is equal to;

30

25

$$\frac{1.2V}{R} \times \left(\frac{27}{12} + \left(\frac{6}{1024} \times DAC \text{ gain}\right)\right) \times 32$$

Figure 30. I<sub>FS</sub> vs. DAC Gain Code

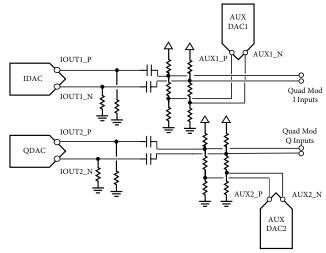

#### **Auxiliary DACs**

Two auxiliary DACs are provided on the AD9776. The full scale output current on these DACs is derived from the 1.2V bandgap reference and external resistor. The gain scale from the reference amplifier to the DAC reference current for each aux DAC is 16.67. with the Aux DAC gain set to full scale (10 bit values, SPI reg 0C, 0D, 10, 11), this gives a full scale current of 2ma for Aux DAC1 and for Aux DAC2. Through these same SPI port registers, the Aux DACs can be turned off, their signs can be inverted (scale is reversed, 0-1024 gives  $I_{\rm FS}$  to 0), and they can be programmed for sourcing or sinking current. When sourcing current, the output compliance voltage is 0-1.5V, and when sinking current the output compliance voltage is 0.8-1.5V.

The Aux DACs can be used for LO cancellation when the DAC output is followed by a quadrature. A typical DAC to Quadrature Modulator interface is given in Figure 31. Often, the input common mode voltage for the modulator is much higher than the output compliance range of the DAC, so that ac coupling is necessary. The input referred offset voltage of thee quadrature modulator can result in LO feed through on the modulator output, degrading system, performance. If the configuration of *Figure 29* is used, the Aux DACs can be used to compensate for the input DC offset of the quad mod, thus reducing LO feedthrough.

Figure 31. Typical Use of Auxiliary DACs

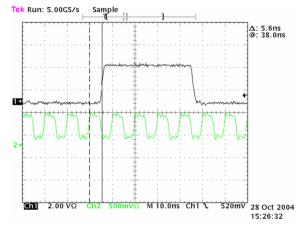

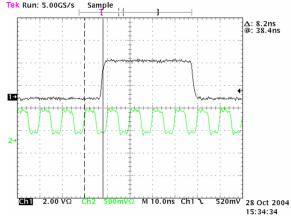

#### Power Down and Sleep Modes