## MC68181

## Advance Information ROAMING FLEX™ chip SIGNAL PROCESSOR

The FLEX™ protocol is a multi-speed, high-performance protocol adopted by leading service providers worldwide as a de facto paging standard. The FLEX protocol gives service providers the increased capacity, added reliability, and enhanced pager battery performance they need today. It also provides an upward migration path to the service provider that is completely transparent to the end user.

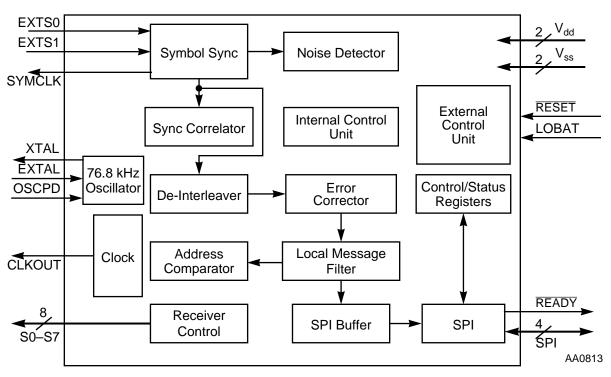

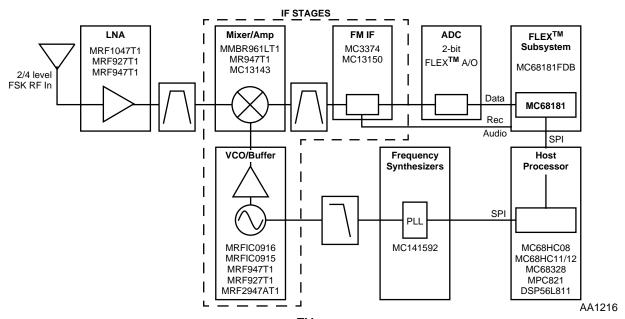

The MC68181 Roaming FLEX™ chip IC is part of a total solution available from Motorola for providing FLEX capabilities in a low-power, low-cost system. The FLEX™ chip simplifies implementation of a FLEX paging device by interfacing with any of several off-the-shelf paging receivers, and any of several off-the-shelf host microcontroller/microprocessors. The primary function of the FLEX™ chip is to process information received and demodulated from a FLEX-radio paging channel, select messages addressed to the paging device, and communicate the message information to the host. The host controls receiver channel selection, and interprets the message information in an appropriate manner (numeric, alphanumeric, binary, etc.) and handles all the I/O activity. The FLEX™ chip IC also operates the paging receiver in an efficient power consumption mode and enables the host to operate in a low power mode when monitoring a single channel for message information. **Figure 1** shows the MC68181 functional block diagram.

Figure 1 MC68181 Functional Block Diagram

This document contains information on a new product. Specifications and information herein are subject to change without notice.

## **TABLE OF CONTENTS**

| SECTION 1  | SIGNAL/CONNECTION DESCRIPTIONS      | . 1-1 |

|------------|-------------------------------------|-------|

| SECTION 2  | SPECIFICATIONS                      | . 2-1 |

| SECTION 3  | PACKAGING                           | . 3-1 |

| SECTION 4  | DESIGN CONSIDERATIONS               | . 4-1 |

| SECTION 5  | ORDERING INFORMATION                | . 5-1 |

| APPENDIX A | FLEX SIGNAL OVERVIEW                | . A-1 |

| APPENDIX B | SPI PACKET DESCRIPTION AND HANDLING | . B-1 |

| APPENDIX C | FLEX™ CHIP IC APPLICATION NOTES     | .C-1  |

## FOR TECHNICAL ASSISTANCE:

**Telephone:** 1-800-521-6274

Internet: <a href="http://www.mot.com/sps/dsp/helpline/messaging">http://www.mot.com/sps/dsp/helpline/messaging</a>

## **Data Sheet Conventions**

This data sheet uses the following conventions:

| OVERBAR      | Used to indicate a signal that is active when pulled low (For example, the $\overline{\text{RESET}}$ pin is active when low.) |                        |                         |                   |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------|-------------------|--|--|--|

| "asserted"   | Means that a high true (active high) signal is high or that a low true (active low) signal is low                             |                        |                         |                   |  |  |  |

| "deasserted" | Means that a high tru<br>signal is high                                                                                       | ue (active high) signa | al is low or that a low | true (active low) |  |  |  |

| Examples:    | Signal/Symbol                                                                                                                 | <b>Logic State</b>     | Signal State            | Voltage           |  |  |  |

|              | PIN                                                                                                                           | True                   | Asserted                | $V_{IL}/V_{OL}$   |  |  |  |

|              | PIN                                                                                                                           | False                  | Deasserted              | $V_{IH}/V_{OH}$   |  |  |  |

|              | PIN                                                                                                                           | True                   | Asserted                | $V_{IH}/V_{OH}$   |  |  |  |

|              | PIN                                                                                                                           | False                  | Deasserted              | $V_{II}/V_{OI}$   |  |  |  |

Note: Values for  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$  are defined by individual product specifications.

Features

## **FEATURES**

- FLEX paging protocol signal processor

- Sixteen programmable user address words

- Sixteen temporary addresses

- Sixteen operator messaging addresses

- 1600, 3200, and 6400 bits-per-second decoding

- Any-phase or single-phase decoding

- Uses standard Serial Peripheral Interface (SPI) in Slave mode

- Allows low current Stop mode operation of host processor

- Highly programmable receiver control

- Real-time clock time base

- FLEX software fragmentation and group messaging support

- Real time clock over-the-air update support

- Compatible with synthesized receivers

- SSID and NID Roaming support

- Low Battery Indication (requires external detector)

- 1.8 to 3.3 V low power operation

- 32-pin Thin Quad Flat Pack (TQFP) package

- Backward compatible with MC68175

## ADDITIONAL SUPPORT

FLEX System Software from Motorola is a family of software components for building world-class products incorporating messaging capabilities. FLEXstack $^{\text{TM}}$  Roaming Software is specifically designed to support the Roaming FLEX $^{\text{TM}}$  chip IC. FLEXstack Roaming Software runs on a product's host processor and takes care of communicating with the FLEX $^{\text{TM}}$  chip IC, acquiring the proper FLEX channel, and fully interpreting the codewords that are passed to the host from the FLEX $^{\text{TM}}$  chip IC.

Documentation

## **DOCUMENTATION**

This document is the primary document supporting the MC68181 FLEX™ chip IC. Documentation is available from:

- A local Motorola distributor

- A Motorola semiconductor sales office

- A Motorola Literature Distribution Center

- Through the Motorola Wireless Semiconductor home page on the Internet

See the back cover for detailed information. The Motorola Wireless Semiconductors home page on the Internet is the source for the latest information.

## Freescale Semiconductor, Inc.

## SECTION 1 SIGNAL/CONNECTION DESCRIPTIONS

## SIGNAL GROUPINGS

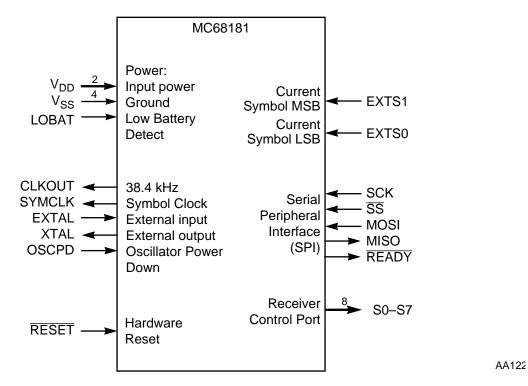

The input and output signals of the MC68181 are organized into six functional groups, as shown in Table 1-1 and as illustrated in Figure 1-1.

**Table 1-1** MC68181 Functional Signal Groupings

| Functional Group                  | Number of<br>Signals | Detailed<br>Description |

|-----------------------------------|----------------------|-------------------------|

| Power Input and Monitoring        | 7                    | Table 1-2               |

| Processor Clocks                  | 1                    | Table 1-3               |

| Reset                             | 1                    | Table 1-4               |

| Current Symbol Inputs             | 2                    | Table 1-5               |

| Serial Peripheral Interface (SPI) | 5                    | Table 1-6               |

| Receiver Control Port             | 8                    | Table 1-7               |

**Figure 1-1** is a diagram of MC68181 signals by functional group.

Power Input and Monitoring

Figure 1-1 Signals Identified by Functional Group

## POWER INPUT AND MONITORING

**Table 1-2** Power Input, Monitoring, and Control Signals

| Power Name        | Description                                                                                                                                                          |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{\mathrm{DD}}$ | <b>Power</b> —V <sub>DD</sub> is the input power for the IC.                                                                                                         |

| $V_{SS}$          | <b>Ground</b> —V <sub>SS</sub> is ground connection for the IC.                                                                                                      |

| LOBAT             | <b>Low Battery</b> —LOBAT provides an input signal to indicate to the IC when external battery power is going low. (An external voltage sensing circuit is required) |

Processor Clock

## PROCESSOR CLOCK

Table 1-3

Processor Clock Signals

| Signal<br>Name | Type   | State During<br>Reset | Signal Description                                                                                                                                                                                                               |

|----------------|--------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKOUT         | Output | Indeterminate         | <b>Clock Output</b> —This is typically a 38.4 kHz clock output (derived from 76.8 kHz oscillator).                                                                                                                               |

| SYMCLK         | Output | Indeterminate         | <b>Recovered Symbol Clock</b> —Data is synchronized to the internal clock and this recovered clock output enhances lockon capability by reducing jitter from cable-induced noise.                                                |

| EXTAL          | Input  | Input                 | <b>External Clock/Crystal Input</b> —EXTAL interfaces the internal crystal oscillator input to a 76.8 kHz crystal input or other external input clock.                                                                           |

| XTAL           | Output | Indeterminate         | External Clock/Crystal Output—This is typically a 76.8 kHz clock output.                                                                                                                                                         |

| OSCPD          | Input  | Input                 | Oscillator Power Down—This input determines whether the internal oscillator is used. Connect this pin to $V_{SS}$ when using the 76.8 kHz crystal input. Connect this pin to $V_{DD}$ when using an external input clock signal. |

## **RESET**

Table 1-4 Test and Reset Signals

| Signal Name | Туре  | State During<br>Reset | Signal Description                                                                                                                                                                              |

|-------------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET       | Input | Input                 | <b>Reset</b> —This input is a direct hardware reset on the FLEX <sup>TM</sup> chip IC. When RESET is asserted low, the FLEX <sup>TM</sup> chip IC is initialized and placed in the Reset state. |

## **CURRENT SYMBOL INPUTS**

Table 1-5

Interrupt and Mode Control

| Signal Name | Туре  | State During<br>Reset | Signal Description                                                                           |

|-------------|-------|-----------------------|----------------------------------------------------------------------------------------------|

| EXTS1       | Input | Input                 | <b>External Symbol 1</b> —This is the Most Significant Bit (MSB) of the symbol being tested. |

| EXTS0       | Input | Input                 | <b>External Symbol</b> 0—This is the Least Significant Bit (LSB) of the symbol being tested. |

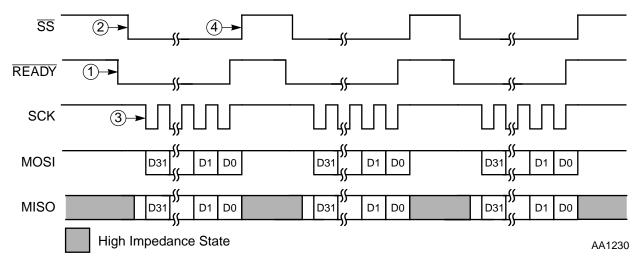

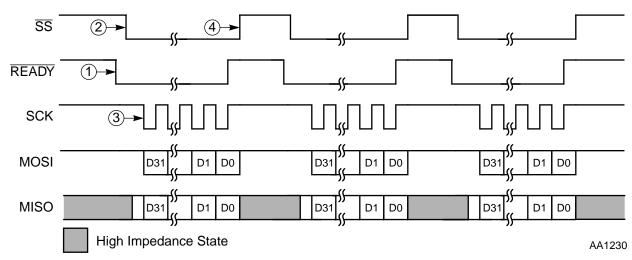

Serial Peripheral Interface (SPI)

## SERIAL PERIPHERAL INTERFACE (SPI)

Table 1-6

Serial Peripheral Interface (SPI) Signals

| Signal<br>Name | Signal<br>Type | State during<br>Reset | Signal Description                                                                                                                                                                                                                    |

|----------------|----------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK            | Input          | Input                 | <b>SPI Serial Clock</b> —The SCK signal is an input, and the clock signal from the external master synchronizes the data transfer. The SCK signal is ignored by the SPI if the Slave Select $(\overline{SS})$ signal is not asserted. |

| SS             | Input          | Input                 | SPI Slave Select—This signal is used to enable the SPI slave for transfer.                                                                                                                                                            |

| MOSI           | Input          | Input                 | SPI Master-Out-Slave-In—Since the MC68181 is always a slave device, this is the data input for SPI communications. The MOSI signal is used in conjunction with the MISO signal for transmitting and receiving serial data.            |

| MISO           | Output         | Tri-stated            | SPI Master-In-Slave-Out—Since the MC68181 is always a slave device, this is the data output for SPI communications. The MISO signal is used in conjunction with the MOSI signal for transmitting and receiving serial data.           |

| READY          | Output         | Output, driven high   | <b>SPI Ready</b> —This signal is driven low when the FLEX <sup>TM</sup> chip IC is ready for an SPI packet.                                                                                                                           |

## **RECEIVER CONTROL LINES**

Table 1-7

Receiver Control Lines

| Signal<br>Name | Signal Type | State during<br>Reset | Signal Description                                                                        |

|----------------|-------------|-----------------------|-------------------------------------------------------------------------------------------|

| S0–S7          | Output      | Tri-stated            | <b>Control Line 0–Control Line 7</b> —These signals are the eight receiver control lines. |

## SECTION 2 SPECIFICATIONS

## INTRODUCTION

The MC68181 is fabricated in high density CMOS with Transistor-Transistor Logic (TTL) compatible inputs and outputs.

## MAXIMUM RATINGS

## **CAUTION**

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either GND or V<sub>DD</sub>).

Note: In the calculation of timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification will never occur in the same device that has a "minimum" value for another specification; adding a maximum to a minimum represents a condition that can never exist.

## Thermal characteristics

Table 2-1 Maximum Ratings

| Rating                                                | Symbol            | Min  | Max  | Unit |

|-------------------------------------------------------|-------------------|------|------|------|

| Supply Voltage                                        | $V_{\mathrm{DD}}$ | -0.5 | 6    | V    |

| All input voltages                                    | V <sub>IN</sub>   | -0.5 | 6.5  | V    |

| Current drain per pin excluding $V_{DD}$ and $V_{SS}$ | I                 | _    | 10   | mA   |

| Operating temperature range                           | T <sub>A</sub>    | -30  | +85  | °C   |

| Storage temperature                                   | T <sub>STG</sub>  | -65  | +150 | °C   |

## THERMAL CHARACTERISTICS

Table 2-2 Thermal Characteristics

| Characteristic                                      | Symbol                           | TQFP Value | Unit |

|-----------------------------------------------------|----------------------------------|------------|------|

| Junction-to-ambient thermal resistance <sup>1</sup> | $R_{\theta JA}$ or $\theta_{JA}$ | 95         | °C/W |

| Thermal characterization parameter                  | $\Psi_{ m JT}$                   | 21         | °C/W |

Note: 1. Junction-to-ambient thermal resistance is based on measurements on a horizontal, single-sided Printed Circuit Board per SEMI G38-87 in natural convection. (SEMI is Semiconductor Equipment and Materials International, 805 East Middlefield Rd., Mountain View, CA 94043, (415) 964-5111) Values were measured with the parts mounted on thermal test boards meeting the specification EIA/ JESD51-3.

**DC Electrical Characteristics**

## DC ELECTRICAL CHARACTERISTICS

**Table 2-3** DC Electrical Characteristics

| Characteristics                                                | Symbol           | Min                                        | Тур          | Max                | Unit   |

|----------------------------------------------------------------|------------------|--------------------------------------------|--------------|--------------------|--------|

| Supply voltage                                                 | V <sub>DD</sub>  | 1.8                                        | 3.3          | 3.6                | V      |

| Input voltage                                                  | V <sub>I</sub>   | 0                                          | _            | V <sub>DD</sub>    | V      |

| Output voltage <sup>1</sup>                                    | V <sub>O</sub>   | 0                                          | _            | V <sub>DD</sub>    | V      |

| Input high voltage RESET, SS, SCK, MOSI All other inputs       | V <sub>IH</sub>  | 0.75V <sub>DD</sub><br>0.7 V <sub>DD</sub> | <u> </u>     |                    | V<br>V |

| Input low voltage                                              | V <sub>IL</sub>  | _                                          | <del>-</del> | $0.2 V_{ m DD}$    | V      |

| Input transition (rise and fall) time                          | t <sub>t</sub>   | 0                                          | _            | 25                 | ns     |

| Input leakage current                                          | I <sub>IN</sub>  | -0.25                                      | _            | 0.25               | μΑ     |

| High impedance (off-state) input current (@ 1.44 V /0.3 V)     | I <sub>TSI</sub> | -10                                        | _            | +10                | μΑ     |

| Output high voltage ( $I_{OH} = -1.0 \text{ mA}$ )             | V <sub>OH</sub>  | 0.8 V <sub>DD</sub>                        | _            | _                  | V      |

| Output low voltage (I <sub>OL</sub> = 2.8 mA)                  | V <sub>OL</sub>  | _                                          | _            | 0.3                | V      |

| Internal Supply Current <sup>2</sup>                           | I <sub>DD</sub>  | _                                          | 100          | _                  | μΑ     |

| Input capacitance                                              | C <sub>IN</sub>  | _                                          | 10           | _                  | pF     |

| Virtual junction temperature                                   | T <sub>j</sub>   | -30                                        | 25           | 150                | °C     |

| Positive-going threshold voltage <sup>3,4</sup>                | V <sub>iT+</sub> | _                                          | _            | 0.7V <sub>DD</sub> | V      |

| Negative-going threshold voltage <sup>3,4</sup>                | V <sub>iT-</sub> | $0.2 V_{ m DD}$                            | _            | _                  | V      |

| Hysteresis (V <sub>iT+</sub> - V <sub>iT-</sub> ) <sup>3</sup> | V <sub>hys</sub> | $0.1V_{ m DD}$                             | _            | $0.3V_{ m DD}$     | V      |

| 3-state-output Hi-Z current <sup>5</sup>                       | $I_{OZ}$         | _                                          | _            | +/- 10             | μА     |

| Lower-level input current <sup>6</sup>                         | I <sub>IL</sub>  | _                                          | _            | -1                 | μА     |

| High-level input current <sup>7</sup>                          | I <sub>IH</sub>  | _                                          | _            | 1                  | μΑ     |

Note:

- 1. Applies to output buffers

- 2. This value is for static I<sub>DD</sub>.

- 3. Applies to input and bi-directional buffers with hystersis

- 4. Test condition = CMOS compatible

- 5. 3-state or open-drain output must be in the high-impedance mode.

- 6. Specifications only apply with pullup terminator turned off.

- 7. Specifications only apply with pulldown terminator turned off

**AC Electrical Characteristics**

## **AC ELECTRICAL CHARACTERISTICS**

The timing waveforms in the AC Electrical Characteristics are tested with a  $V_{IL}$  maximum of  $0.2 \times V_{DD}$  in V and a  $V_{IH}$  minimum of  $0.7 \times V_{DD}$  in V for all inputs. AC timing specifications that are referenced to a device input signal are measured in production with respect to the 50% point of the respective input signal's transition. MC68181 output levels are measured with the production test machine  $V_{OL}$  and  $V_{OH}$  reference levels set at  $0.3 \times V_{DD}$  in V and  $0.6 \times V_{DD}$  in V, respectively.

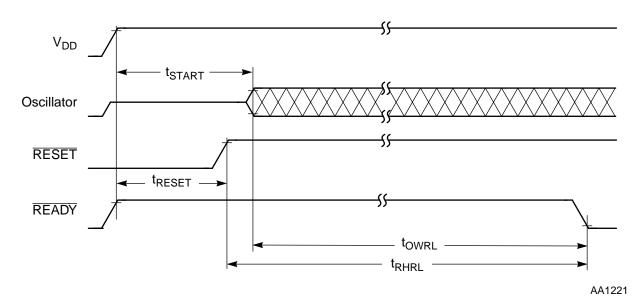

## **INITIALIZATION TIMING**

$(V_{DD} = 1.8 \text{ to } 3.6 \text{ V}, TA = -30 \text{ to } + 85^{\circ}\text{C})$

**Table 2-4** Initialization Timing

| Characteristic                    | Conditions    | Symbol             | Min    | Max    | Unit |

|-----------------------------------|---------------|--------------------|--------|--------|------|

| Oscillator Start-up Time          | _             | t <sub>START</sub> | _      | 5      | sec  |

| RESET Hold Time                   | _             | t <sub>RESET</sub> | 200    | _      | ns   |

| RESET High to READY Low           | _             | t <sub>RHRL</sub>  | 76,800 | 76,800 | T    |

| Oscillator Warmed Up to READY Low | $C_L = 50 pf$ | t <sub>OWRL</sub>  | _      | 1      | sec  |

Note: T is one period of the 76.8 kHz clock source. From power-up, the oscillator start-up time can impact the availability and period of clock strobes. This can affect the actual **RESET** high to **READY** low timing.

**RESET Timing**

Figure 2-1 Startup Timing

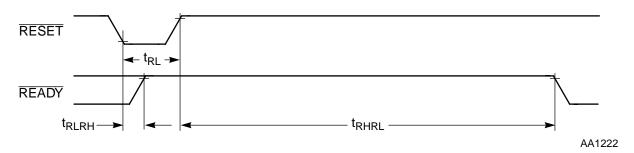

## **RESET TIMING**

$$(V_{DD} = 1.8 \text{ to } 3.6 \text{ V}, \text{TA} = -30 \text{ to } 85^{\circ}\text{C})$$

**Table 2-5** Reset Timing

| Characteristic          | Conditions                               | Symbol            | Min | Max | Unit |

|-------------------------|------------------------------------------|-------------------|-----|-----|------|

| RESET Pulse Width       | _                                        | t <sub>RL</sub>   | 200 | _   | ns   |

| RESET Low to READY High | _                                        | t <sub>RLRH</sub> | _   | 200 | ns   |

| RESET High to READY Low | Requires stable<br>76.8 kHz clock source | t <sub>RHRL</sub> | _   | 1   | sec  |

Figure 2-2 Reset Timing

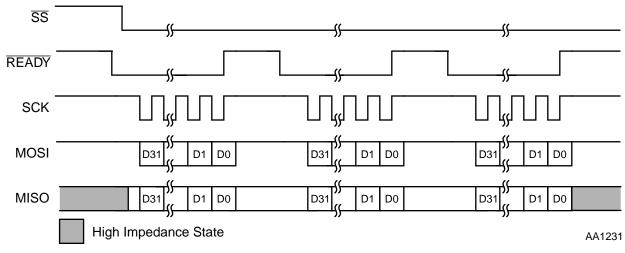

Serial Peripheral Interface (SPI) Timing

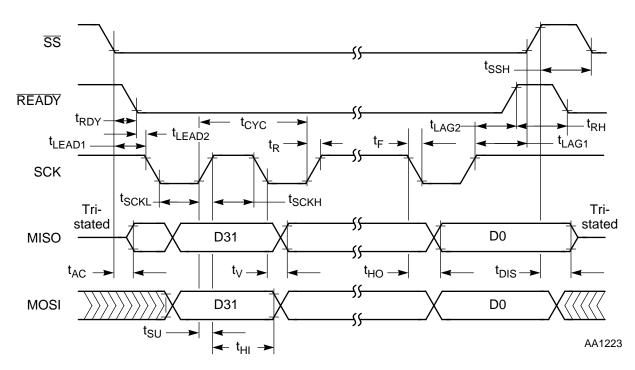

## SERIAL PERIPHERAL INTERFACE (SPI) TIMING

$(V_{DD} = 1.8 \text{ to } 3.6 \text{ V}, T_A = -30 \text{ to } +85^{\circ}\text{C})$

**Table 2-6** SPI Timing

| Characteristic       | Conditions                                                             | Symbol             | Min  | Max | Unit |

|----------------------|------------------------------------------------------------------------|--------------------|------|-----|------|

| Operating Frequency  | _                                                                      | $f_{OP}$           | 0    | 1   | MHz  |

| Cycle Time           | _                                                                      | t <sub>CYC</sub>   | 1000 | _   | ns   |

| Select Lead Time     | _                                                                      | t <sub>LEAD1</sub> | 200  | _   | ns   |

| De-select Lag Time   | _                                                                      | t <sub>LAG1</sub>  | 200  | _   | ns   |

| Select-to-Ready Time | Previous packet did not program an address word; $C_L = 50 \text{ pf}$ | t <sub>RDY</sub>   | _    | 80  | μs   |

| Select-to-Ready Time | Previous packet programmed an address word; $C_L = 50 \text{ pf}$      | t <sub>RDY</sub>   | _    | 420 | μs   |

| Ready High Time      | _                                                                      | t <sub>RH</sub>    | 50   | _   | μs   |

| Ready Lead Time      | _                                                                      | t <sub>LEAD2</sub> | 200  | _   | ns   |

| Not Ready Lag Time   | $C_L = 50 pf$                                                          | t <sub>LAG2</sub>  | _    | 200 | ns   |

| MOSI Data Setup Time | _                                                                      | t <sub>SU</sub>    | 200  | _   | ns   |

| MOSI Data Hold Time  | _                                                                      | t <sub>HI</sub>    | 200  | _   | ns   |

| MISO Access Time     | $C_L = 50 pf$                                                          | t <sub>AC</sub>    | 0    | 200 | ns   |

| MISO Disable Time    | _                                                                      | t <sub>DIS</sub>   | _    | 300 | ns   |

| MISO Data Valid Time | $C_L = 50 pf$                                                          | $t_{ m V}$         | _    | 200 | ns   |

| MISO Data Hold Time  | _                                                                      | t <sub>HO</sub>    | 0    | _   | ns   |

| SS High Time         | _                                                                      | t <sub>SSH</sub>   | 200  | _   | ns   |

| SCK High Time        | _                                                                      | t <sub>SCKH</sub>  | 300  | _   | ns   |

| SCK Low Time         | _                                                                      | t <sub>SCKL</sub>  | 300  | _   | ns   |

| SCK Rise Time        | 20% to 70% V <sub>DD</sub>                                             | t <sub>R</sub>     |      | 1   | μs   |

| SCK Fall Time        | 20% to 70% V <sub>DD</sub>                                             | t <sub>F</sub>     |      | 1   | μs   |

Note: When the host reprograms an address word with a Host-to-FLEX<sup>TM</sup> chip packet ID > 127 (decimal), there may be an added delay before FLEX<sup>TM</sup> chip is ready for another packet.

Serial Peripheral Interface (SPI) Timing

Figure 2-3 SPI Timing

Serial Peripheral Interface (SPI) Timing

## Freescale Semiconductor, Inc.

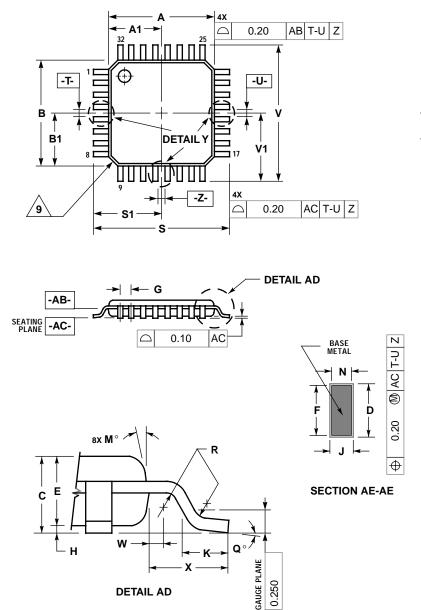

## SECTION 3 PACKAGING

## PIN-OUT AND PACKAGE INFORMATION

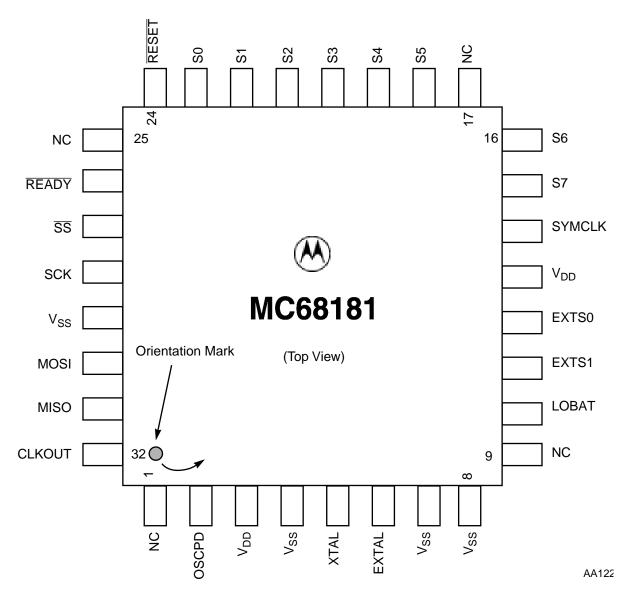

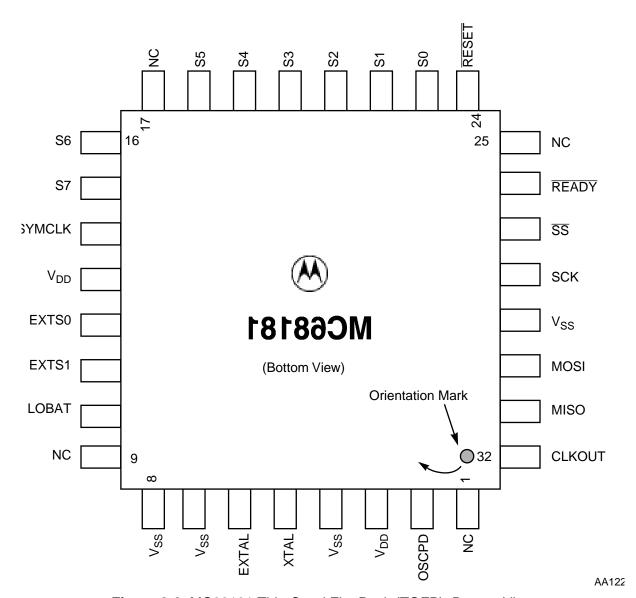

This section provides information about the available packages for this product, including diagrams of the package pinouts and tables describing how the signals described in **Section 1** are allocated. The MC68181 is available in a 32-pin Thin Quad Flat Pack (TQFP) package.

## **TQFP Package Description**

Top and bottom views of the TQFP package are shown in **Figure 3-1** and **Figure 3-2** with their pin-outs.

Figure 3-1 MC68181 Thin Quad Flat Pack (TQFP), Top View

Figure 3-2 MC68181 Thin Quad Flat Pack (TQFP), Bottom View

Table 3-1 Signal by Pin Number

| Pin# | Signal Name                  | Pin# | Signal Name       | Pin# | Signal Name     | Pin# | Signal Name     |

|------|------------------------------|------|-------------------|------|-----------------|------|-----------------|

| 1    | NC <sup>1</sup>              | 9    | NC <sup>1</sup>   | 17   | NC <sup>1</sup> | 25   | NC <sup>1</sup> |

| 2    | OSCPD                        | 10   | LOBAT             | 18   | S5              | 26   | READY           |

| 3    | $V_{\mathrm{DD}}$            | 11   | EXTS1             | 19   | S4              | 27   | SS              |

| 4    | ${ m V_{SS}}^2$              | 12   | EXTS0             | 20   | S3              | 28   | SCK             |

| 5    | XTAL                         | 13   | $V_{\mathrm{DD}}$ | 21   | S2              | 29   | ${ m V_{SS}}^2$ |

| 6    | EXTAL                        | 14   | SYMCLK            | 22   | S1              | 30   | MOSI            |

| 7    | $V_{SS}^2$                   | 15   | S7                | 23   | S0              | 31   | MISO            |

| 8    | V <sub>SS</sub> <sup>2</sup> | 16   | S6                | 24   | RESET           | 32   | CLKOUT          |

Note: 1. NC indicates reserved pins. These pins must not be connected to any external line.

2. To ensure proper chip operation, all  $V_{SS}$  pins must be connected to GND.

**Table 3-2** Signal by Name

| Signal Name | Pin # | Signal Name | Pin # | Signal Name | Pin # | Signal Name     | Pin # |

|-------------|-------|-------------|-------|-------------|-------|-----------------|-------|

| CLKOUT      | 32    | NC          | 9     | S2          | 21    | SYMCLK          | 14    |

| EXTAL       | 6     | NC          | 17    | S3          | 20    | V <sub>DD</sub> | 3     |

| EXTS0       | 12    | NC          | 25    | S4          | 19    | V <sub>DD</sub> | 13    |

| EXTS1       | 11    | OSCPD       | 2     | S5          | 18    | V <sub>SS</sub> | 4     |

| LOBAT       | 10    | READY       | 26    | S6          | 16    | V <sub>SS</sub> | 7     |

| MISO        | 31    | RESET       | 24    | S7          | 15    | V <sub>SS</sub> | 8     |

| MOSI        | 30    | S0          | 23    | SCK         | 28    | V <sub>SS</sub> | 29    |

| NC          | 1     | S1          | 22    | SS          | 27    | XTAL            | 5     |

# P AE DETAIL Y

### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 2. CONTROLLING DIMENSION: MILLIMETER.

- 3. DATUMPLANE-AB-ISLOCATEDATBOTTOMOFLEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOMOF THE PARTING LINE.

- DATUMS -T-, -U-, AND -Z- TO BE DETERMINED AT DATUM PLANE -AB-.

- DIMENSIONS S AND V TO BE DETERMINED AT SEATING PLANE -AC-

- DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0,250 (0.010) PER SIDE. DIMENSIONS A AND B DO INCLUDE MOLDMISMATCHAND ARE DETERMINED AT DATUM PLANE - AB-.

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE D DIMENSION TO EXCEED 0.520.

- 8. MINIMUM SOLDER PLATE THICKNESS SHALL BE 0.0076.

- EXACT SHAPE OF EACH CORNER MAY VARY FROM DEPICTION.

|     | MILLIN      | <b>METERS</b> |  |  |  |  |  |  |  |

|-----|-------------|---------------|--|--|--|--|--|--|--|

| DIM | MIN         | MAX           |  |  |  |  |  |  |  |

| Α   | 7.000       | BSC           |  |  |  |  |  |  |  |

| A1  | 3.500       | BSC           |  |  |  |  |  |  |  |

| В   | 7.000       | BSC           |  |  |  |  |  |  |  |

| B1  | 3.500       | BSC           |  |  |  |  |  |  |  |

| С   | 1.400 1.600 |               |  |  |  |  |  |  |  |

| D   | 0.300       | 0.450         |  |  |  |  |  |  |  |

| Ε   | 1.350       | 1.450         |  |  |  |  |  |  |  |

| F   | 0.300       | 0.400         |  |  |  |  |  |  |  |

| G   | 0.800 BSC   |               |  |  |  |  |  |  |  |

| Н   | 0.050       | 0.150         |  |  |  |  |  |  |  |

| J   | 0.090       | 0.200         |  |  |  |  |  |  |  |

| K   | 0.500       | 0.700         |  |  |  |  |  |  |  |

| М   | 12°         | REF           |  |  |  |  |  |  |  |

| N   | 0.090       | 0.160         |  |  |  |  |  |  |  |

| Р   |             | BSC           |  |  |  |  |  |  |  |

| Q   | 1°          | 5°            |  |  |  |  |  |  |  |

| R   | 0.150       | 0.250         |  |  |  |  |  |  |  |

| S   | 9.000       | BSC           |  |  |  |  |  |  |  |

| S1  | 4.500       | BSC           |  |  |  |  |  |  |  |

| ٧   | 9.000       | BSC           |  |  |  |  |  |  |  |

| V1  | 4.500       | BSC           |  |  |  |  |  |  |  |

| W   | 0.200       | REF           |  |  |  |  |  |  |  |

| Х   | 1.000       | REF           |  |  |  |  |  |  |  |

CASE 873A-02 ISSUE A

**DATE 12/16/93**

Figure 3-3 32-pin Thin Quad Flat Pack (TQFP) Mechanical Information

Ordering Drawings

## **ORDERING DRAWINGS**

Complete mechanical information regarding MC68181 packaging is available by facsimile through Motorola's  $Mfax^{TM}$  system. Call the following number to obtain information by facsimile:

(602) 244-6591

The Mfax automated system requests the following information:

- The receiving facsimile telephone number including area code or country code

- The caller's Personal Identification Number (PIN)

**Note:** For first time callers, the system provides instructions for setting up a PIN, which requires entry of a name and telephone number.

- The type of information requested:

- Instructions for using the system

- A literature order form

- Specific part technical information or data sheets

- Other information described by the system messages

A total of three documents may be ordered per call.

The MC68181 32-pin TQFP package mechanical drawing is referenced as 873A-02.

## SECTION 4 DESIGN CONSIDERATIONS

## THERMAL DESIGN CONSIDERATIONS

An estimation of the chip junction temperature,  $T_J$ , in  $^{\circ}C$  can be obtained from the equation:

**Equation 1:**

$$T_J = T_A + (P_D \times R_{\theta JA})$$

Where:

$T_A$  = ambient temperature  $^{\circ}C$

$R_{\theta JA}$  = package junction-to-ambient thermal resistance °C/W

$P_D$  = power dissipation in package

Historically, thermal resistance has been expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

**Equation 2:**

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

Where:

$R_{\theta JA}$  = package junction-to-ambient thermal resistance °C/W

$R_{\theta IC}$  = package junction-to-case thermal resistance °C/W

$R_{\theta CA}$  = package case-to-ambient thermal resistance °C/W

$R_{\theta JC}$  is device-related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For example, the user can change the air flow around the device, add a heat sink, change the mounting arrangement on the Printed Circuit Board, or otherwise change the thermal dissipation capability of the area surrounding the device on a Printed Circuit Board. This model is most useful for ceramic packages with heat sinks; some 90% of the heat flow is dissipated through the case to the heat sink and out to the ambient environment. For ceramic packages, in situations where the heat flow is split between a path to the case and an alternate path through the Printed Circuit Board, analysis of the device thermal performance may need the additional modeling capability of a system level thermal simulation tool.

The thermal performance of plastic packages is more dependent on the temperature of the Printed Circuit Board to which the package is mounted. Again, if the

## **Thermal Design Considerations**

estimations obtained from  $R_{\theta JA}$  do not satisfactorily answer whether the thermal performance is adequate, a system level model may be appropriate.

A complicating factor is the existence of three common ways for determining the junction-to-case thermal resistance in plastic packages:

- To minimize temperature variation across the surface, the thermal resistance is measured from the junction to the outside surface of the package (case) closest to the chip mounting area when that surface has a proper heat sink.

- To define a value approximately equal to a junction-to-board thermal resistance, the thermal resistance is measured from the junction to where the leads are attached to the case.

- If the temperature of the package case  $(T_T)$  is determined by a thermocouple, the thermal resistance is computed using the value obtained by the equation  $(T_J T_T)/P_D$ .

As noted above, the junction-to-case thermal resistances quoted in this data sheet are determined using the first definition. From a practical standpoint, that value is also suitable for determining the junction temperature from a case thermocouple reading in forced convection environments. In natural convection, using the junction-to-case thermal resistance to estimate junction temperature from a thermocouple reading on the case of the package will estimate a junction temperature slightly hotter than actual temperature. Hence, the new thermal metric, Thermal Characterization Parameter or  $\Psi_{TT}$ , has been defined to be

$(T_J - T_T)/P_D$ . This value gives a better estimate of the junction temperature in natural convection when using the surface temperature of the package. Remember that surface temperature readings of packages are subject to significant errors caused by inadequate attachment of the sensor to the surface and to errors caused by heat loss to the sensor. The recommended technique is to attach a 40-gauge thermocouple wire and bead to the top center of the package with thermally conductive epoxy.

**Application Design Considerations**

## APPLICATION DESIGN CONSIDERATIONS

The FLEX™ chip IC connects to a receiver capable of converting a four-level FSK-encoded audio signal into a 2-bit digital signal. The FLEX™ chip IC has eight receiver control lines used for warming up and shutting down a receiver in stages. The FLEX™ chip IC has dual bandwidth control signals for two post detection filter bandwidths for receiving the two symbol rates of the FLEX signal. The FLEX™ chip IC has the ability to detect a low battery signal during the receiver control sequences. It interfaces to a host MCU through a standard SPI. It has a 38.4 kHz clock output capable of driving other devices. It has a 1 minute timer that offers low power support for time of day function on the host. **Figure 4-1** shows a typical application block diagram.

Figure 4-1 Roaming FLEX<sup>TM</sup> chip System Block Diagram

## **Application Design Considerations**

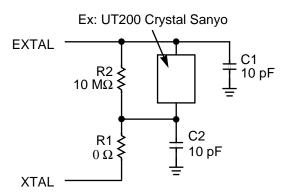

Figure 4-2 shows a recommended circuit for a 76.8 kHz crystal input.

Note: R1 can be increased in size to be used as a current limiter, if needed.

AA1069

Figure 4-2 Input Circuit for 76.8 kHz Crystal

**Appendix A** of this document provides a background of the FLEX signal protocol. **Appendix B** provides a description of the way in which the MC68181 FLEX<sup>™</sup> chip IC handles packets through the SPI, including sections that describe transfer from the host to the decoder from the decoder to the host. **Appendix C** provides a sample application to illustrate how the MC68181 FLEX<sup>™</sup> chip IC might be used in an application.

## SECTION 5 ORDERING INFORMATION

Consult a Motorola Semiconductor sales office or authorized distributor to determine product availability and to place an order.

**Table 5-1** Ordering Information

| Part    | Supply<br>Voltage | Package Type                  | Pin<br>Count | Frequency<br>(kHz) | Order Number |

|---------|-------------------|-------------------------------|--------------|--------------------|--------------|

| MC68181 | 2/3 V             | Thin Quad Flat Pack<br>(TQFP) | 32           | 76.8               | MC68181FA    |

## APPENDIX A FLEX OVERVIEW

This appendix gives an overview of the FLEX protocol as it pertains to the Roaming FLEX chip IC. This is only an overview and in the event that there is contradictory information, the FLEX Protocol Specification prevails. This overview is derived from Issue G1.8 of the FLEX Protocol Specification.

## FLEX SIGNAL STRUCTURE

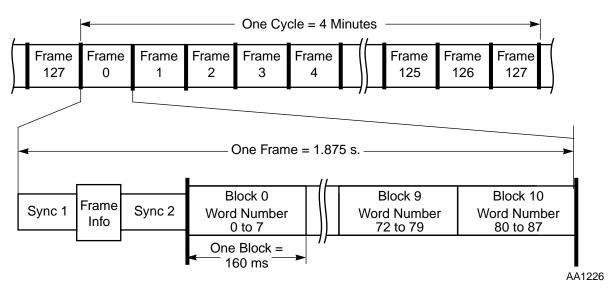

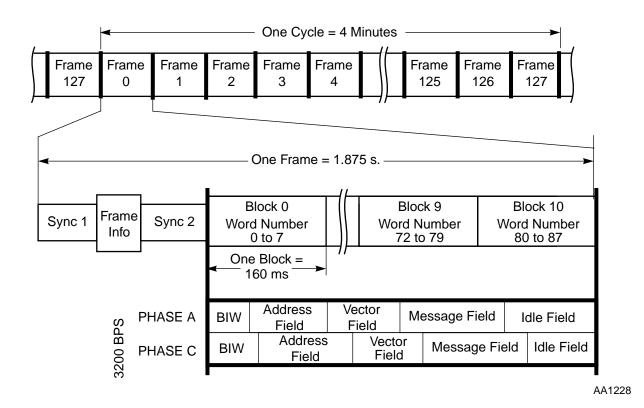

As shown in **Figure A-1**, a FLEX signal is transmitted on a radio channel and consists of a series of four-minute cycles, each cycle having 128 frames at 1.875 seconds per frame. A pager may be assigned to process any number of these frames. Any unassigned frames are not processed, thus reducing power required for signal processing and extending battery life. If required, however, the pager may temporarily process more complex information, because individual FLEX cycles can assign additional frames dynamically using collapse, fragmentation, temporary addressing, or carry-on information within the FLEX signal.

Figure A-1 FLEX™ Signal Structure

## **FLEX FRAME STRUCTURE**

As shown in **Figure A-1** on page A-1, each FLEX frame consists of:

- Synchronization portion

- Data portion—Eleven data blocks lasting 160 milliseconds each

## **Frame Synchronization Portion**

The synchronization portion consists of:

- First synchronization signal at 1600 bps

- Frame Information Word including:

- Frame Number 0–127 (7 bits)

- Cycle Number 0–14 (4 bits)

- Second synchronization signal at the data rate of the interleaved portion.

## FIRST SYNCHRONIZATION SIGNAL

The first synchronization signal is transmitted at 1600 bps and provides a signal to lock onto the specific frame.

## FRAME INFORMATION WORD

The Frame Information Word transmits 11 bits that are divided into a 7-bit frame number and a 4-bit cycle number. This allows the pager to identify the frame and the cycle in which it resides uniquely.

## SECOND SYNCHRONIZATION SIGNAL

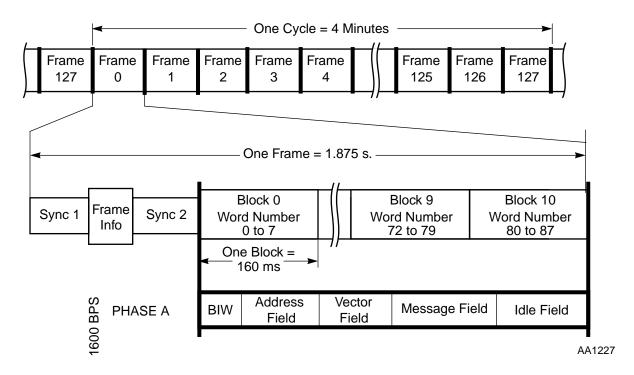

The second synchronization signal indicates the rate at which the data portion is transmitted, 1600, 3200 or 6400 bits per second.

The 1600 bps rate is transmitted as a single phase of information (A), as shown in **Figure A-2** on page A-3, at 1600 symbols per second using 2-level Frequency Shift Keyed (FSK) modulation.

Figure A-2 FLEX™ Signal Structure for 1600 BPS

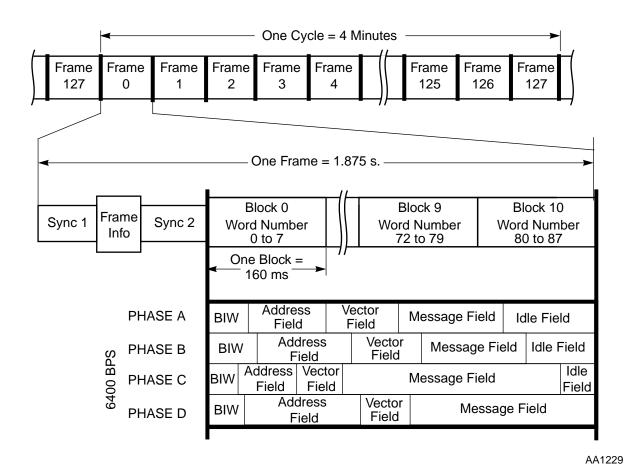

The 3200 bps rate is transmitted as two concurrent phases of information (A and C), as shown in **Figure A-3**, at either:

- 1600 symbols per second using 4-level FSK modulation, or

- 3200 symbols per second using 2-level FSK modulation.

Figure A-3 FLEX™ Signal Structure for 3200 BPS

The 6400 bps rate is transmitted as four concurrent phases of information (A,B, C, and D), as shown in **Figure A-4**, at 3200 symbols per second using 4-level FSK modulation.

Figure A-4 FLEX™ Signal Structure For 6400 BPS

## Frame Data Portion

As noted above, there are eleven data blocks following the frame synchronization portion of each frame. Each block has eight interleaved words per phase, numbered 0–87 contiguously for all eleven blocks, in every frame. Each word has information that allows for bit error correction and detection contained within an error correcting code.

Each of the eighty-eight words in each phase is organized into the following five fields:

- Block information field

- Address field

- Vector field

- Message field

- Idle field

The boundaries between the fields are independent of the block boundaries. Furthermore, at 3200 and 6400 bps, the information in one phase is independent of the information in a concurrent phase, and the boundaries between the fields of one phase are unrelated to the boundaries between the fields in a concurrent phase.

## **BLOCK INFORMATION FIELD**

The block information field may contain information words for determining time and date information and certain paging system information.

## ADDRESS FIELD

The address field contains addresses assigned to paging devices. Addresses are used to identify information sent to individual paging devices and/or groups of paging devices. An address may be either a "short" one word address or a "long" two word address. Information in the FLEX signal may indicate that an address is a priority address. An address may be a "tone only" address, in which case there is no additional information associated with the address.

## **VECTOR FIELD**

The vector field consists of a series of vector words. Depending upon the type of message, a vector word (or words in the case of a long address) may either contain all of the information necessary for the message, or indicate the location of message words in the message field comprising the message information. If an address is not a tone only address, then there is an associated vector word in the vector field. Information in the FLEX signal indicates the location of the vector word. Short addresses have one associated vector word and long addresses two associated vector words. A pager may go to low power mode at the end of the address field if its address(es) is (are) not detected, thus resulting in battery savings.

## **MESSAGE FIELD**

The message field consists of a series of information words containing message information. The message information may be formatted in ASCII, BCD, or binary depending upon the message type. The following sections provide a detailed description of the various types of information words that may be used in the message field.

## **IDLE FIELD**

The idle field is used to separate blocks.

**FLEX Message Word Definitions**

## FLEX MESSAGE WORD DEFINITIONS

## **Numeric Data Message**

The following tables describe the bit format of the numeric messages. The 4-bit numeric characters of the message are designated as lower case letters a, b, c, d, etc.

**Table A-1** Standard (V = 011) or Special Format (V = 100) Numeric Vectors

| Message<br>Word | i0               | i1             | i2               | i3             | i4             | i5             | i6             | i7             | i8                    | i9                    | i10            | i11            | i12              | i13                       | i14                       | i15            | i16            | i17            | i18            | i19            | i20            |

|-----------------|------------------|----------------|------------------|----------------|----------------|----------------|----------------|----------------|-----------------------|-----------------------|----------------|----------------|------------------|---------------------------|---------------------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 1st             | K <sub>4</sub>   | K <sub>5</sub> | a <sub>0</sub>   | a <sub>1</sub> | a <sub>2</sub> | a <sub>3</sub> | $\mathbf{b_0}$ | b <sub>1</sub> | b <sub>2</sub>        | $b_3$                 | $c_0$          | $c_1$          | $c_2$            | c <sub>3</sub>            | $d_0$                     | $\mathbf{d}_1$ | $\mathbf{d}_2$ | $d_3$          | $\mathbf{e_0}$ | $\mathbf{e}_1$ | e2             |

| 2nd             | $e_3$            | $f_0$          | f <sub>1</sub>   | f <sub>2</sub> | $f_3$          | g <sub>0</sub> | g <sub>1</sub> | $g_2$          | $g_3$                 | h <sub>0</sub>        | h <sub>1</sub> | h <sub>2</sub> | h <sub>3</sub>   | $i_0$                     | i <sub>1</sub>            | i <sub>2</sub> | $i_3$          | j <sub>0</sub> | j <sub>1</sub> | $\mathbf{j}_2$ | $\mathbf{j}_3$ |

| 3rd             | $k_0$            | k <sub>1</sub> | k <sub>2</sub>   | k <sub>3</sub> | $l_0$          | l <sub>1</sub> | l <sub>2</sub> | $l_3$          | m <sub>0</sub>        | m <sub>1</sub>        | m <sub>2</sub> | m <sub>3</sub> | n <sub>0</sub>   | n <sub>1</sub>            | n <sub>2</sub>            | n <sub>3</sub> | $o_0$          | o <sub>1</sub> | 02             | $o_3$          | $q_0$          |

| 4th             | $q_1$            | $\mathbf{q}_2$ | $q_3$            | r <sub>0</sub> | r <sub>1</sub> | r <sub>2</sub> | r <sub>3</sub> | s <sub>0</sub> | s <sub>1</sub>        | s <sub>2</sub>        | $s_3$          | t <sub>0</sub> | t <sub>1</sub>   | t <sub>2</sub>            | t <sub>3</sub>            | $u_0$          | u <sub>1</sub> | u <sub>2</sub> | $u_3$          | $\mathbf{v}_0$ | $\mathbf{v}_1$ |

| 5th             | $\mathbf{v}_2$   | $\mathbf{v}_3$ | $\mathbf{w}_0$   | $\mathbf{w}_1$ | w <sub>2</sub> | $w_3$          | y <sub>0</sub> | y <sub>1</sub> | <b>y</b> <sub>2</sub> | <b>y</b> <sub>3</sub> | $z_0$          | $\mathbf{z}_1$ | $\mathbf{z}_2$   | $\mathbf{z}_3$            | A <sub>0</sub>            | A <sub>1</sub> | A <sub>2</sub> | $A_3$          | B <sub>0</sub> | B <sub>1</sub> | B <sub>2</sub> |

| 6th             | B <sub>3</sub>   | $C_0$          | C <sub>1</sub>   | C <sub>2</sub> | C <sub>3</sub> | $D_0$          | D <sub>1</sub> | $D_2$          | $D_3$                 | E <sub>0</sub>        | E <sub>1</sub> | E <sub>2</sub> | $E_3$            | F <sub>0</sub>            | F <sub>1</sub>            | F <sub>2</sub> | F <sub>3</sub> | $G_0$          | $G_1$          | $G_2$          | $G_3$          |

| 7th             | $H_0$            | H <sub>1</sub> | H <sub>2</sub>   | $H_3$          | I <sub>0</sub> | I <sub>1</sub> | I <sub>2</sub> | $I_3$          | $J_0$                 | J <sub>1</sub>        | J <sub>2</sub> | $J_3$          | $V_0$            | $V_1$                     | $V_2$                     | $V_3$          | L <sub>0</sub> | L <sub>1</sub> | L <sub>2</sub> | $L_3$          | $M_0$          |

| 8th             | $\overline{M_1}$ | $M_2$          | $\overline{M_3}$ | $O_0$          | O <sub>1</sub> | $O_2$          | $O_3$          | P <sub>0</sub> | P <sub>1</sub>        | P <sub>2</sub>        | P <sub>3</sub> | $Q_0$          | $\overline{Q_1}$ | $\overline{\mathrm{Q}_2}$ | $\overline{\mathrm{Q}_3}$ | T <sub>0</sub> | T <sub>1</sub> | T <sub>2</sub> | T <sub>3</sub> | $U_0$          | $U_1$          |

**Table A-2** Numbered (V = 111) Numeric Vector

| Message<br>Word | i0             | i1             | i2             | i3             | i4             | i5             | i6             | i7                    | i8             | i9             | i10            | i11            | i12            | i13                   | i14                   | i15                   | i16            | i17                   | i18            | i19            | i20            |

|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|----------------|----------------|----------------|----------------|----------------|-----------------------|-----------------------|-----------------------|----------------|-----------------------|----------------|----------------|----------------|

| 1st             | K <sub>4</sub> | K <sub>5</sub> | N <sub>0</sub> | N <sub>1</sub> | N <sub>2</sub> | N <sub>3</sub> | N <sub>4</sub> | N <sub>5</sub>        | R <sub>0</sub> | S <sub>0</sub> | a <sub>0</sub> | a <sub>1</sub> | a <sub>2</sub> | <b>a</b> <sub>3</sub> | $\mathbf{b_0}$        | b <sub>1</sub>        | b <sub>2</sub> | <b>b</b> <sub>3</sub> | $c_0$          | c <sub>1</sub> | c <sub>2</sub> |

| 2nd             | $c_3$          | $d_0$          | $d_1$          | $d_2$          | $d_3$          | $\mathbf{e_0}$ | e <sub>1</sub> | $\mathbf{e_2}$        | $e_3$          | $f_0$          | f <sub>1</sub> | f <sub>2</sub> | $f_3$          | g <sub>0</sub>        | g <sub>1</sub>        | g <sub>2</sub>        | g <sub>3</sub> | h <sub>0</sub>        | h <sub>1</sub> | h <sub>2</sub> | h <sub>3</sub> |

| 3rd             | i <sub>0</sub> | i <sub>1</sub> | i <sub>2</sub> | $i_3$          | j <sub>0</sub> | j <sub>1</sub> | j <sub>2</sub> | <b>j</b> <sub>3</sub> | $\mathbf{k_0}$ | k <sub>1</sub> | k <sub>2</sub> | k <sub>3</sub> | $l_0$          | l <sub>1</sub>        | l <sub>2</sub>        | $l_3$                 | m <sub>0</sub> | m <sub>1</sub>        | m <sub>2</sub> | m <sub>3</sub> | n <sub>0</sub> |

| 4th             | n <sub>1</sub> | n <sub>2</sub> | n <sub>3</sub> | $o_0$          | o <sub>1</sub> | $o_2$          | $o_3$          | $q_0$                 | $\mathbf{q}_1$ | $\mathbf{q}_2$ | $q_3$          | r <sub>0</sub> | r <sub>1</sub> | r <sub>2</sub>        | r <sub>3</sub>        | $s_0$                 | s <sub>1</sub> | $s_2$                 | $s_3$          | t <sub>0</sub> | t <sub>1</sub> |

| 5th             | t <sub>2</sub> | $t_3$          | $u_0$          | $\mathbf{u}_1$ | $u_2$          | $u_3$          | $\mathbf{v_0}$ | $\mathbf{v}_1$        | $\mathbf{v}_2$ | $\mathbf{v}_3$ | $\mathbf{w_0}$ | $\mathbf{w}_1$ | $\mathbf{w}_2$ | $w_3$                 | <b>y</b> <sub>0</sub> | <b>y</b> <sub>1</sub> | $y_2$          | у3                    | $z_0$          | $\mathbf{z}_1$ | $\mathbf{z}_2$ |

| 6th             | $z_3$          | A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | B <sub>0</sub> | B <sub>1</sub> | B <sub>2</sub>        | B <sub>3</sub> | C <sub>0</sub> | C <sub>1</sub> | C <sub>2</sub> | $C_3$          | $D_0$                 | D <sub>1</sub>        | $D_2$                 | $D_3$          | E <sub>0</sub>        | E <sub>1</sub> | E <sub>2</sub> | E <sub>3</sub> |

| 7th             | F <sub>0</sub> | F <sub>1</sub> | F <sub>2</sub> | F <sub>3</sub> | $G_0$          | $G_1$          | $G_2$          | $G_3$                 | H <sub>0</sub> | H <sub>1</sub> | H <sub>2</sub> | H <sub>3</sub> | I <sub>0</sub> | I <sub>1</sub>        | I <sub>2</sub>        | $I_3$                 | J <sub>0</sub> | J <sub>1</sub>        | J <sub>2</sub> | $J_3$          | V              |

| 8th             | V <sub>1</sub> | $V_2$          | $V_3$          | L <sub>0</sub> | L <sub>1</sub> | L <sub>2</sub> | L <sub>3</sub> | $M_0$                 | M <sub>1</sub> | M <sub>2</sub> | $M_3$          | $O_0$          | O <sub>1</sub> | O <sub>2</sub>        | $O_3$                 | P <sub>0</sub>        | P <sub>1</sub> | P <sub>2</sub>        | P <sub>3</sub> | $Q_0$          | $Q_1$          |

## **FLEX Message Word Definitions**

**Table A-3** Numeric Message Bit Definitions

| Symbol | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K      | <b>6-bit Message Check Character (First 4 bits are in the vector word)</b> —This check character is calculated by initializing the message check character ( <b>K</b> ) to 0 and summing the information bits of each code word in the message, (including control information and termination characters and bits in the last message word) to a check sum register. The information bits of each word are broken into three groups: the first is the 8 bits comprising <b>i</b> <sub>0</sub> through <b>i</b> <sub>7</sub> , the second group comprises bits <b>i</b> <sub>8</sub> through <b>i</b> <sub>15</sub> , and the third group comprises bits <b>i</b> <sub>16</sub> through <b>i</b> <sub>20</sub> . Bits <b>i</b> <sub>0</sub> , <b>i</b> <sub>8</sub> , and <b>i</b> <sub>16</sub> are the LSBs of each group. The binary sum is calculated, and the result is shortened to the eight Least Significant Bits. The two Most Significant Bits are shifted 6 bits to the right and summed with the six Least Significant Bits to form a new sum. This resultant sum is one's complemented with the six LSBs of the result being transmitted as the message check character. |

| N      | Message Number—When the system supports message retrieval, the system controller assigns message numbers (for each paging address separately) starting at zero and progressing up to a maximum of sixty-three in consecutive order. The actual maximum roll over number is defined in the pager code plug to accommodate values set in the system infrastructure. When message numbers are not received in order, the subscriber should assume a message has been missed. The subscriber or the pager may determine the missing message number(s) allowing a request to be made for retrieval. When a normal unnumbered numeric message is received (Message Retrieval Flag = 0), it is not to be included in the missed message calculation.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R      | <b>Message Retrieval Flag</b> —When this bit is set to 1, the pager expects to see messages numbered in order (each address numbered separately). Detection of a missing number indicates a missed message. A message received with $R=0$ is allowed to be out of order and shall not cause the pager to indicate that a message has been missed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| S      | <b>Special Format</b> —In the numbered message format, this bit set to 1 indicates that a special display format should be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## **MESSAGE FILL RULES**

For numeric messages of thirty-six characters or less (thirty-four characters if numbered), fewer than eight code words on the channel are required. Only code words containing the numeric message are to be transmitted. The space character (\$C) should be used to fill any unused 4-bit characters in the last word and zeros to fill any remaining partial characters. The check sum is correspondingly shortened to include only the code words comprising the shortened message along with the space and fill characters used to fill in the last word.

## SPECIAL FORMAT NUMERIC

Spaces and dashes as specified by the host are inserted into the received message. This feature in certain markets saves the transmission of an additional word on the channel. As an example, in the U.S. market a 10-character string (area code plus telephone number) fits into two message words; if the dashes or parentheses are to be

included in the message, a third message word on the channel is required. The actual placement can be programmed into the paging device and can vary between markets.

# **Hex/Binary Message**

The following tables describe the bit format of the Hex/Binary messages. The data of the message is designated as lower case letters a, b, c, d, etc. Hex/binary messages can be sent as fragments. The service provider has the option of dividing the message into several pieces and sending the separate pieces at any time within a given time period.

**Table A-4** Vector Type V = 110 First Only Fragment

| Message<br>Word | i <sub>0</sub> | <b>i</b> <sub>1</sub> | $\mathbf{i}_2$ | $\mathbf{i_3}$ | <b>i</b> <sub>4</sub> | <b>i</b> <sub>5</sub> | i <sub>6</sub> | i <sub>7</sub>        | i <sub>8</sub>        | i <sub>9</sub> | i <sub>10</sub> | i <sub>11</sub> | i <sub>12</sub> | i <sub>13</sub> | i <sub>14</sub> | i <sub>15</sub> | i <sub>16</sub> | i <sub>17</sub> | i <sub>18</sub> | i <sub>19</sub> | i <sub>20</sub> |

|-----------------|----------------|-----------------------|----------------|----------------|-----------------------|-----------------------|----------------|-----------------------|-----------------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 1st             | K <sub>0</sub> | K <sub>1</sub>        | K <sub>2</sub> | K <sub>3</sub> | K <sub>4</sub>        | K <sub>5</sub>        | K <sub>6</sub> | K <sub>7</sub>        | K <sub>8</sub>        | K <sub>9</sub> | K <sub>10</sub> | K <sub>11</sub> | C <sub>0</sub>  | F <sub>0</sub>  | F <sub>1</sub>  | N <sub>0</sub>  | N <sub>1</sub>  | N <sub>2</sub>  | N <sub>3</sub>  | N <sub>4</sub>  | N <sub>5</sub>  |

| 2nd             | R <sub>0</sub> | M <sub>0</sub>        | $D_0$          | H <sub>0</sub> | B <sub>0</sub>        | B <sub>1</sub>        | B <sub>2</sub> | B <sub>3</sub>        | s <sub>0</sub>        | s <sub>1</sub> | s <sub>2</sub>  | $s_3$           | s <sub>4</sub>  | S <sub>0</sub>  | S <sub>1</sub>  | S <sub>2</sub>  | $S_3$           | S <sub>4</sub>  | S <sub>5</sub>  | S <sub>6</sub>  | S <sub>7</sub>  |

| 3rd             | a <sub>0</sub> | a <sub>1</sub>        | a <sub>2</sub> | $a_3$          | $b_0$                 | b <sub>1</sub>        | b <sub>2</sub> | <b>b</b> <sub>3</sub> | c <sub>0</sub>        | $c_1$          | $c_2$           | c <sub>3</sub>  | $d_0$           | $d_1$           | $d_2$           | $d_3$           | $e_0$           | $\mathbf{e_1}$  | $e_2$           | $e_3$           | $f_0$           |

| 4th             | f <sub>1</sub> | f <sub>2</sub>        | $f_3$          | g <sub>0</sub> | g <sub>1</sub>        | g <sub>2</sub>        | g <sub>3</sub> | h <sub>0</sub>        | h <sub>1</sub>        | h <sub>2</sub> | h <sub>3</sub>  | $i_0$           | i <sub>1</sub>  | i <sub>2</sub>  | i <sub>3</sub>  | j <sub>0</sub>  | j <sub>1</sub>  | j <sub>2</sub>  | j <sub>3</sub>  | k <sub>0</sub>  | k <sub>1</sub>  |

| 5th             | k <sub>2</sub> | k <sub>3</sub>        | l <sub>0</sub> | l <sub>1</sub> | l <sub>2</sub>        | $l_3$                 | m <sub>0</sub> | m <sub>1</sub>        | m <sub>2</sub>        | m <sub>3</sub> | n <sub>0</sub>  | n <sub>1</sub>  | n <sub>2</sub>  | n <sub>3</sub>  | $o_0$           | o <sub>1</sub>  | 02              | 03              | $q_0$           | $q_1$           | $\mathbf{q}_2$  |

| 6th             | $q_3$          | r <sub>0</sub>        | r <sub>1</sub> | r <sub>2</sub> | r <sub>3</sub>        | s <sub>0</sub>        | s <sub>1</sub> | s <sub>2</sub>        | <b>s</b> <sub>3</sub> | t <sub>0</sub> | t <sub>1</sub>  | t <sub>2</sub>  | t <sub>3</sub>  | u <sub>0</sub>  | u <sub>1</sub>  | u <sub>2</sub>  | u <sub>3</sub>  | $\mathbf{v}_0$  | $\mathbf{v}_1$  | $\mathbf{v}_2$  | $\mathbf{v}_3$  |

|                 |                |                       |                |                |                       |                       |                |                       |                       |                |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |

| nth             | i              | i                     | i              | i              | i                     | i                     | i              | i                     | i                     | i              | i               | i               | i               | i               | i               | i               | i               | i               | i               | i               | i               |

**Table A-5** Vector Type V=110 All Other Fragments

| Message<br>Word | i0             | i1             | i2             | i3             | i4             | i5             | i6             | i7             | i8             | i9             | i10             | i11             | i12            | i13            | i14            | i15            | i16            | i17            | i18                   | i19            | i20            |

|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|----------------|----------------|

| 1st             | K <sub>0</sub> | K <sub>1</sub> | K <sub>2</sub> | K <sub>3</sub> | K <sub>4</sub> | K <sub>5</sub> | K <sub>6</sub> | K <sub>7</sub> | K <sub>8</sub> | K <sub>9</sub> | K <sub>10</sub> | K <sub>11</sub> | $C_0$          | F <sub>0</sub> | F <sub>1</sub> | N <sub>0</sub> | N <sub>1</sub> | N <sub>2</sub> | N <sub>3</sub>        | N <sub>4</sub> | N <sub>5</sub> |

| 2nd             | a <sub>0</sub> | a <sub>1</sub> | $a_2$          | $a_3$          | $b_0$          | b <sub>1</sub> | b <sub>2</sub> | $b_3$          | $c_0$          | $c_1$          | $c_2$           | c <sub>3</sub>  | $d_0$          | $\mathbf{d}_1$ | $\mathbf{d}_2$ | $d_3$          | $\mathbf{e_0}$ | $\mathbf{e}_1$ | $\mathbf{e_2}$        | $\mathbf{e_3}$ | $f_0$          |

| 3rd             | f <sub>1</sub> | $f_2$          | $f_3$          | g <sub>0</sub> | g <sub>1</sub> | $g_2$          | $g_3$          | h <sub>0</sub> | h <sub>1</sub> | h <sub>2</sub> | h <sub>3</sub>  | $i_0$           | i <sub>1</sub> | i <sub>2</sub> | $i_3$          | j <sub>0</sub> | j <sub>1</sub> | $\mathbf{j}_2$ | <b>j</b> <sub>3</sub> | $\mathbf{k}_0$ | k <sub>1</sub> |

| 4th             | k <sub>2</sub> | $\mathbf{k}_3$ | $l_0$          | l <sub>1</sub> | l <sub>2</sub> | $l_3$          | m <sub>0</sub> | m <sub>1</sub> | m <sub>2</sub> | $m_3$          | n <sub>0</sub>  | n <sub>1</sub>  | n <sub>2</sub> | n <sub>3</sub> | $o_0$          | o <sub>1</sub> | 02             | $o_3$          | $q_0$                 | $q_1$          | $\mathbf{q}_2$ |

| 5th             | $q_3$          | $r_0$          | r <sub>1</sub> | r <sub>2</sub> | $r_3$          | $s_0$          | $s_1$          | $s_2$          | $s_3$          | $t_0$          | t <sub>1</sub>  | t <sub>2</sub>  | t <sub>3</sub> | $u_0$          | u <sub>1</sub> | u <sub>2</sub> | $u_3$          | $\mathbf{v}_0$ | $\mathbf{v}_1$        | $\mathbf{v}_2$ | $v_3$          |

|                 |                |                |                |                |                |                |                |                |                |                |                 |                 |                |                |                |                |                |                |                       |                |                |

| nth             | i              | i              | i              | i              | i              | i              | i              | i              | i              | i              | i               | i               | i              | i              | i              | i              | i              | i              | i                     | i              | i              |

**Table A-6** Hex/Binary Message Bit Definitions

| Symbol <sup>1</sup> | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K                   | <b>12-bit Fragment Check Sum</b> —This check sum is calculated by initializing the Fragment Check Sum field ( $\mathbf{K}$ ) to 0 and calculating a sum over the information bits of each code word in the message fragment (including control information and termination characters/bits in the last fragment word). This sum requires that the information bits of each word be broken into three groups: the first is the 8 bits comprising $\mathbf{i_0}$ through $\mathbf{i_7}$ , the second group comprises bits $\mathbf{i_8}$ through $\mathbf{i_{15}}$ , and the third group comprises bits $\mathbf{i_16}$ through $\mathbf{i_{20}}$ . Bits $\mathbf{i_0}$ , $\mathbf{i_8}$ , and $\mathbf{i_{16}}$ are the LSBs of each group. The binary sum is calculated over all code words in the fragment, the one's complement of the sum is determined, and the twelve LSBs of the result is placed into the Fragment Check Sum field to be transmitted at the beginning of the fragment.              |

| С                   | <b>1-bit Message Continued Flag</b> —When set to 1, this flag indicates fragments of this message are to be expected in any or possibly all of the following frames until a fragment with $C=0$ is found. The longest message that fits into a frame is eighty-four code words. Three alpha characters per word yields a maximum message of 252 characters in a frame, assuming no other traffic. Messages longer than this value must be sent as several fragments.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| F                   | <b>2-bit Message Fragment Number</b> —This is a modulo 3 message fragment number that is incremented by 1 in successive message fragments. The initial fragment starts at 11 and each following fragment is incremented by 1 modulo 3, (11, 00, 01, 10, 00, 01, 10, 00, etc.). The 11 state (after the initial fragment) is skipped in this process to avoid confusion with the single fragment of a non-continued message. The final fragment is indicated by the Message Continued Flag being reset to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

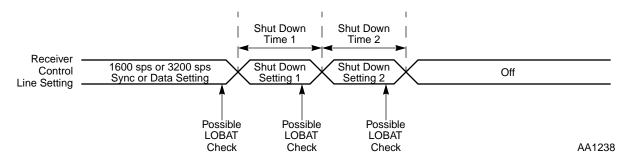

| N                   | Message Number—When the system supports message retrieval the system controller assigns message numbers (for each paging address separately) starting at 0 and progressing up to a maximum of 63 in consecutive order. The actual maximum roll over number is defined in the pager code plug to accommodate values set in the system infrastructure. When message numbers are not received in order, the subscriber should assume a message has been missed. The subscriber or the pager may determine the missing message number(s) allowing a request to be made for retrieval. When a normal unnumbered numeric message is received (message retrieval flag is equal to 0), it is not to be included in the missed message calculation. This number is also used to identify fragments of the same message. Multiple messages to the same address must have separate message numbers. An exception to this rule is the header message tied to a transparent message, each with the same message number. |