# APC Amplifier with Integrated Photodiode and Gain Adjust Capability

#### **FEATURES**

- Dual wavelength 650nm and 780nm

- 13 ns Settling Time to 2%

- 100 MHz Bandwidth at -3dB

- 10 mV Output Offset Voltage

- 25 μV/°C Output Offset Voltage Drift

- ± 6 dB External Gain Adjust

- Small 8-pin OPLGA package

- Power-down mode

#### **APPLICATIONS**

- CD-R, and CD-RW

- DVD+/-R, DVD+/-RW, and DVD-RAM

#### GENERAL DESCRIPTION

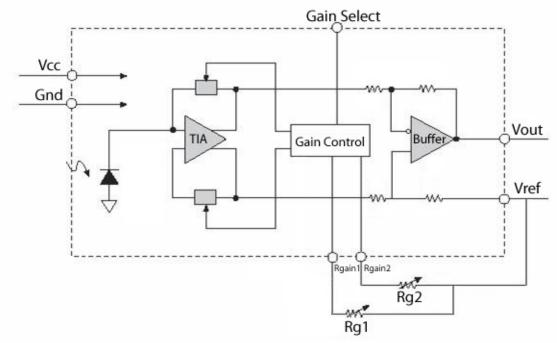

The SP8036 represents the next generation in Automatic Power Control (APC) amplifiers designed specifically for demanding pick-up head applications. With its integrated photo detector, the SP8036 monitors light intensity of the laser diode in CD-R, CD-RW, DVD+/-R, DVD+/-RW, and DVD-RAM assemblies and converts this light to an output voltage. The magnitude of this voltage signal corresponds to the laser power intensity and is subsequently fed back to the laser diode driver to control the laser output power.

The SP8036 on-chip photo detector transforms incident laser light into a proportional current, which is then converted to a voltage through a transimpedance amplifier. Adjustable gain is provided in the transimpedance amplifier by means of a gain control loop that is controlled by an external resistor. This external resistor is not a part of the signal path, which greatly reduces the effects of all parasitic capacitances and inductances on the flex cable at these pins. The signal is then buffered to provide reactive load drive capability.

The SP8036 achieves an unparalleled level of performance by combining excellent DC stability and low noise with outstanding AC performance. This level of performance is achieved using a proprietary fully complimentary BICMOS process with fully integrated, on-board photo detector.

The SP8036 is offered with a nominal sensitivity 4450 V/W and is packaged in a  $3.0 \times 3.5$  mm, 8-lead OPLGA package. All input logic levels should not be left open at any time.

The SP8036 offers power-down capability with the new active-low chip enable pin,  $\overline{CE}$ . The chip operates normally when this pin is connected to GND and powers down when connected to Vcc.

Figure 1: Functional Diagram

### **ABSOLUTE MAXIMUM RATINGS**

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| Supply Voltage (Vcc)                   | 6.0V   |

|----------------------------------------|--------|

| All Other Pins                         | 6.0V   |

| Junction Temperature (T <sub>J</sub> ) | 120°C  |

| Storage Temperature                    |        |

| Soldering Temperature                  | +235°C |

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage (Vcc)     | 4.5V to 5.5V |

|--------------------------|--------------|

| Reference Voltage (VREF) | 1.9V to 2.3V |

| Operating temperature    | -20 to +85°C |

#### THERMAL SPECIFICATIONS

8-pin OPLGA (3 x 3.5mm) Package Thermal Resistance......90°C/W

# ELECTRICAL/OPTICAL SPECIFICATIONS

Unless otherwise noted:  $4.5V \le Vcc \le 5.5V$ , VREF =2.1V, output load:  $R_L = 1k\Omega$  to VREF,  $C_L = 20pF$  to GND, RGAIN = 400ohm, ambient temperature -20  $^{\circ}C \le TA \le +85 ^{\circ}C$

| Parameter                                                   |             | Conditions                                                                       | Min  | Тур  | Max | Units           |  |

|-------------------------------------------------------------|-------------|----------------------------------------------------------------------------------|------|------|-----|-----------------|--|

| Supply Voltage                                              |             |                                                                                  | 4.5  | 5    | 5.5 | V               |  |

| Supply Current                                              |             | TA = 25 °C, no signal                                                            |      | 13   | 18  | mA              |  |

|                                                             |             | -20 ≤Ta ≤ +85 °C, no signal                                                      |      |      | 25  |                 |  |

| Voltage Reference                                           | e Range     | RGAIN = 400ohm                                                                   | 1.9  | 2.1  | 2.3 | V               |  |

| Output Offset Voltage                                       |             | Referenced to VREF                                                               | -10  |      | 10  | mV              |  |

| Output Offset Voltage Drift                                 |             | RGAIN = 400ohm                                                                   | -25  |      | 25  | //°C            |  |

| Output Offset vo                                            | itage Driit | RGAIN = 950ohm                                                                   | -50  |      | 50  | μV/°C           |  |

| Power Supply Rejection Ratio                                |             | RGAIN = 400ohm, 4.5V ≤ Vcc ≤ 5.5V                                                | 55   | 73   |     | -ID             |  |

| (PSRR) *                                                    |             | RGAIN = 950ohm, 4.5V ≤ Vcc ≤ 5.5V                                                | 50   | 75   |     | dB              |  |

| Onin Ossitala Lani                                          | - 11-       | Logic level low                                                                  |      |      | 0.8 | V               |  |

| Gain Switch Logi                                            | c Leveis    | Logic level high                                                                 | 2.4  |      |     |                 |  |

| Output Sensitivity                                          |             | Any Select Mode.  Laser Beam Diameter = 0.70mm, uniform density (RGAIN = 4000hm) |      | 4450 |     | V/W             |  |

| Input Optical Power required to produce a 1.5V output swing |             | Any Select Mode<br>RGAIN = 400ohm                                                |      | 0.34 |     | mW              |  |

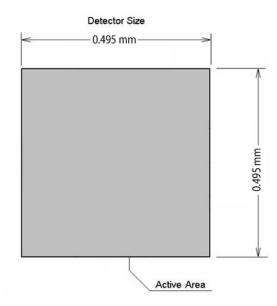

| Photo Detector Active Area                                  |             |                                                                                  |      | 0.25 |     | mm <sup>2</sup> |  |

| Output Sensitivity Change vs. Vcc                           |             | RGAIN = 950ohm                                                                   |      |      | 5   | %/V             |  |

| Output Sensitivity Change vs. Temperature                   |             | RGAIN = 950ohm                                                                   |      |      | 0.1 | %/°C            |  |

| Output Noise (+6 dB)                                        |             | 1kHz ≤ BW ≤ 1MHz                                                                 |      | 0.14 | 2   | mV              |  |

| Output Noise (+0                                            | db)         | 1kHz ≤ BW ≤ 100MHz                                                               |      | 1.28 | 5   | ] IIIV          |  |

| Output Slew Rate                                            | e           |                                                                                  |      | 190  |     | V/µs            |  |

| Output Settling Time to 2% of finale value (1.5V step)      |             | -6dB                                                                             |      | 12.6 | 15  |                 |  |

|                                                             |             | 0dB                                                                              |      | 13.1 | 15  | ns              |  |

|                                                             |             | +6dB                                                                             |      | 14.0 | 15  |                 |  |

| Full Scale Output Voltage Swing                             |             | Referenced to VREF                                                               | -1.5 | -1.7 |     | Vp-p            |  |

| Output Overshoo                                             |             | Vout=1.5V step                                                                   |      |      | 5   | %               |  |

| Bandwidth (-3dB)                                            |             | RGAIN = 400ohm                                                                   | 70   | 100  |     | MHz             |  |

| Gain Adjust                                                 | Vcc = 5.0V  | 150ohm≤Rgain≤950ohm                                                              | -6   |      | +6  | dB              |  |

| Range at                                                    | Vcc = 4.5V  | 250ohm≤RGAIN≤950ohm                                                              | -3   |      | +6  | GD.             |  |

<sup>\*</sup> PSRR = 20log (ΔVcc/ΔVout), where Vout is the output voltage without signal (offset voltage)

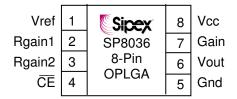

## **PIN ASSIGNMENTS**

| Pin# | Pin Name | Pin Function                                                                           |

|------|----------|----------------------------------------------------------------------------------------|

| 1    | Vref     | Reference Voltage                                                                      |

| 2    | Rgain1   | Gain Adjust Resistor Rgain1 connection point                                           |

| 3    | Rgain2   | Gain Adjust Resistor Rgain2 connection point                                           |

| 4    | CE       | Active low Chip enable                                                                 |

| 5    | GND      | Power Ground                                                                           |

| 6    | Vout     | Output Voltage                                                                         |

| 7    | Gain     | Gain Switch Input. Low level or Open selects pin Rgain1, high level selects pin Rgain2 |

| 8    | Vcc      | Supply Voltage. Bypass to GND with ceramic capacitor 0.1µF                             |

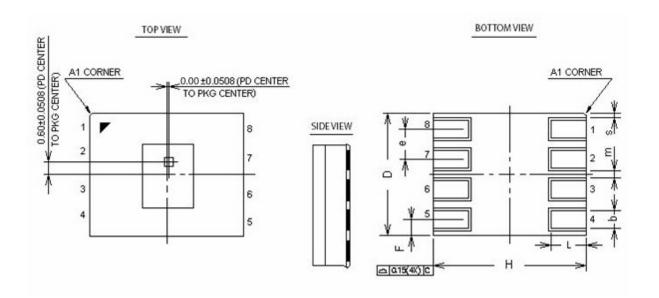

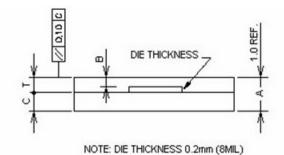

# **OPLGA 8-pin PACKAGE DIMENSIONS**

| 0140010 | DIMEN | SIONS IN MILLIME | TERS |

|---------|-------|------------------|------|

| SYMBOLS | MIN   | NOM              | MAX  |

| A       | 0.90  | 1.00             | 1.10 |

| В       | 0.19  | _                | 0.25 |

| b       | 0.30  | 0.40             | 0.50 |

| С       | _     | 0.56             | _    |

| Н       | 3.40  | 3.50             | 3.60 |

| D       | 2.90  | 3.00             | 3.10 |

| е       | _     | 0.75             | _    |

| L       | 0.50  | 0.60             | 0.70 |

| T       | _     | 0.45             | _    |

| F       | 0.28  | 0.38             | 0.48 |

| s       | 0.075 | -                | _    |

| m       | 0.10  | _                | _    |

| Part number | Temperature range | Package Type |

|-------------|-------------------|--------------|

| SP8036DG4   | -20 + 85°C        | 8-pin OPLGA  |

Sipex Corporation

Headquarters and Sales Office 233 South Hillview Drive Milpitas, CA 95035 TEL: (408) 934-7500 FAX: (408) 935-7600

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.