# 12-Channel Gamma Buffers with VCOM Buffer

ADD8701

#### **FEATURES**

Single-Supply Operation: 7 V to 16 V Dual-Supply Operation:  $\pm 3.5$  V to  $\pm 8$  V

Supply Current: 13 mA Max

Upper/Lower Buffers Swing to V<sub>DD</sub>/GND Continuous Output Current: 10 mA VCOM Peak Output Current: 250 mA

Offset Voltage: 15 mV Max

Slew Rate: 6 V/μs

Fast Settling Time with Large C-Load

APPLICATIONS

TFT LCD Panels

#### **GENERAL DESCRIPTION**

The ADD8701 is a low cost, 12-channel buffer amplifier and VCOM driver that operates from a single supply. The part is designed for high resolution TFT LCD panels, and is built on an advanced, high voltage, CBCMOS process.

The buffers have high slew rate, 10 mA continuous output current, and high capacitive load drive capability. The VCOM buffer has increased drive of 35 mA and can drive large capacitive loads. The ADD8701 offers wide supply range and offset voltages below 15 mV.

#### **FUNCTIONAL BLOCK DIAGRAM**

The ADD8701 is specified over the -40°C to +85°C temperature range and is available in a 32-lead lead frame chip scale package (LFCSP).

All inputs and outputs incorporate internal ESD protection circuits.

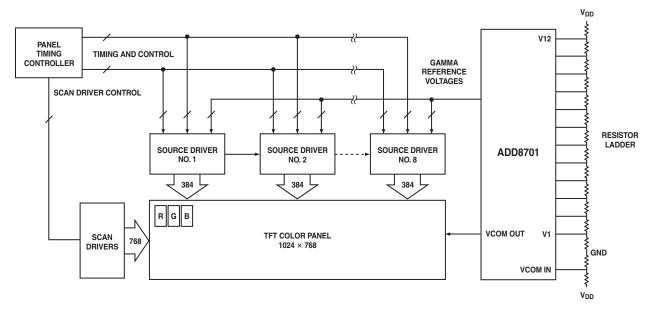

Figure 1. Typical SVGA TFT-LCD Application

#### REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

## ADD8701-SPECIFICATIONS

### **ELECTRICAL CHARACTERISTICS** (7 V $\leq$ V<sub>DD</sub> $\leq$ 16 V, T<sub>A</sub> = 25°C, unless otherwise specified.)

| Parameter                                                                                                                            | Symbol                                                   | Condition                                                                                                                                                                                                                                                                                                                                                                           | Min                            | Typ                                | Max                                       | Unit                                           |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------|-------------------------------------------|------------------------------------------------|

| INPUT CHARACTERISTICS Offset Voltage Offset Voltage Drift Input Bias Current Input Voltage Range                                     | $V_{OS} \ \Delta V_{OS}/\Delta T \ I_{B}$                | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$<br>$-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$                                                                                                                                                                                                                                      | -0.5                           | 4<br>5<br>0.5                      | 15<br>1.1<br>1.5<br>V <sub>DD</sub> + 0.5 | mV<br>μV/°C<br>μA<br>μA<br>V                   |

| Input Impedance Input Capacitance                                                                                                    | Z <sub>IN</sub><br>C <sub>IN</sub>                       |                                                                                                                                                                                                                                                                                                                                                                                     |                                | 400<br>1                           |                                           | kΩ<br>pF                                       |

| OUTPUT CHARACTERISTICS Output Voltage High (V11, V12)                                                                                | V <sub>OUT</sub>                                         | $\begin{split} I_L &= 100 \; \mu A \\ V_{DD} &= 16 \; V,  I_L = 5 \; m A \\ -40^{\circ} C &\leq T_A \leq +85^{\circ} C \\ V_{DD} &= 7 \; V,  I_L = 5 \; m A \\ -40^{\circ} C &\leq T_A \leq +85^{\circ} C \end{split}$                                                                                                                                                              | 15.85<br>15.75<br>6.75<br>6.65 | 15.995<br>15.9<br>6.85             |                                           | V<br>V<br>V<br>V                               |

| Output Swing (V3 to V10) Output Swing (V3 to V10) Output Voltage Low (V1, V2)                                                        | V <sub>OUT</sub><br>V <sub>OUT</sub><br>V <sub>OUT</sub> | $\begin{split} &I_{L} = 5 \text{ mA}, V_{DD} = 16 \text{ V} \\ &I_{L} = 5 \text{ mA}, V_{DD} = 7 \text{ V} \\ &I_{L} = 100 \mu\text{A} \\ &V_{DD} = 16 \text{ V}, I_{L} = 5 \text{ mA} \\ &-40^{\circ}\text{C} \leq T_{A} \leq +85^{\circ}\text{C} \\ &V_{DD} = 7 \text{ V}, I_{L} = 5 \text{ mA} \\ &-40^{\circ}\text{C} \leq T_{A} \leq +85^{\circ}\text{C} \end{split}$          | 0.05                           | 14.6<br>5.6<br>5<br>85<br>140      | 150<br>250<br>300<br>400                  | V<br>V<br>W<br>mV<br>mV<br>mV<br>mV            |

| Continuous Output Current<br>Peak Output Current                                                                                     | $I_{ m OUT} \ I_{ m PK}$                                 | V <sub>DD</sub> = 16 V                                                                                                                                                                                                                                                                                                                                                              |                                | 10<br>150                          |                                           | mA<br>mA                                       |

| VCOM CHARACTERISTICS Continuous Output Current Peak Output Current                                                                   | $I_{ m OUT} \ I_{ m PK}$                                 | V <sub>DD</sub> = 16 V                                                                                                                                                                                                                                                                                                                                                              |                                | 35<br>250                          |                                           | mA<br>mA                                       |

| TRANSFER CHARACTERISTICS Gain Gain Linearity                                                                                         | A <sub>VCL</sub>                                         | $R_{L} = 2 \text{ k}\Omega$ $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$ $R_{L} = 10 \text{ k}\Omega$ $V_{O} = 0.5 \text{ to } (V_{DD} - 0.5 \text{ V})$                                                                                                                                                                                                                 | 0.995<br>0.995                 | 0.9985<br>0.9980<br>0.01           | 1.005<br>1.005                            | V/V<br>V/V                                     |

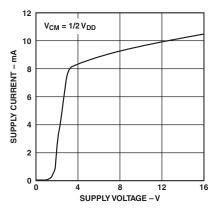

| SUPPLY CHARACTERISTICS Supply Voltage Power Supply Rejection Ratio Supply Current                                                    | V <sub>DD</sub><br>PSRR<br>I <sub>SYS</sub>              | $V_{DD}$ = 6 V to 17 V<br>-40°C $\leq$ T <sub>A</sub> $\leq$ +85°C<br>No Load<br>-40°C $\leq$ T <sub>A</sub> $\leq$ +85°C                                                                                                                                                                                                                                                           | 7 70                           | 90<br>10                           | 16<br>13<br>15                            | V<br>dB<br>mA<br>mA                            |

| DYNAMIC PERFORMANCE Slew Rate Bandwidth Settling Time to 0.1% (Buffers) Settling Time to 0.1% (VCOM) Phase Margin Channel Separation | SR<br>BW<br>t <sub>S</sub><br>t <sub>S</sub><br>fo       | $R_{L} = 10 \text{ k}\Omega, C_{L} = 200 \text{ pF}$ $-3 \text{ dB}, R_{L} = 10 \text{ k}\Omega, C_{L} = 200 \text{ pF}$ $1 \text{ V}, R_{L} = 10 \text{ k}\Omega, C_{L} = 200 \text{ pF}$ $1 \text{ V}, R_{L} = 10 \text{ k}\Omega, C_{L} = 200 \text{ pF}$ $1 \text{ V}, R_{L} = 10 \text{ k}\Omega, C_{L} = 200 \text{ pF}$ $R_{L} = 10 \text{ k}\Omega, C_{L} = 200 \text{ pF}$ | 4                              | 6<br>4.5<br>1.1<br>0.7<br>55<br>75 |                                           | V/µs<br>MHz<br>µs<br>µs<br>Degrees<br>dB       |

| NOISE PERFORMANCE Voltage Noise Density  Current Noise Density                                                                       | $e_n$ $e_n$ $i_n$                                        | f = 1 kHz<br>f = 10 kHz<br>f = 10 kHz                                                                                                                                                                                                                                                                                                                                               |                                | 26<br>25<br>0.8                    |                                           | $nV/\sqrt{Hz} \\ nV/\sqrt{Hz} \\ pA/\sqrt{Hz}$ |

Specifications subject to change without notice.

-2- REV. 0

#### **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage (V <sub>DD</sub> )        | 18 V                                         |

|------------------------------------------|----------------------------------------------|

| Input Voltage                            | $-0.5 \text{ V}$ to $V_{DD} + 0.5 \text{ V}$ |

| Storage Temperature Range                | 65°C to +150°C                               |

| Operating Temperature Range              | 40°C to +85°C                                |

| Junction Temperature Range               | 65°C to +150°C                               |

| Lead Temperature Range (Soldering, 60 se | ec) 300°C                                    |

| ESD Tolerance (HBM)                      | ±1,000 V                                     |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Package Type       | $\theta_{JA}^{1}$ | $\Psi_{\mathrm{JB}}^{2}$ | Unit |

|--------------------|-------------------|--------------------------|------|

| 32-Lead LFCSP (CP) | 35                | 13                       | °C/W |

#### NOTES

#### **ORDERING GUIDE**

| Model      | Temperature<br>Range |               | Package<br>Option |  |

|------------|----------------------|---------------|-------------------|--|

| ADD8701ACP | -40°C to +85°C       | 32-Lead LFCSP | CP-32             |  |

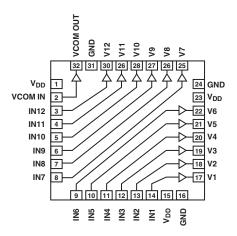

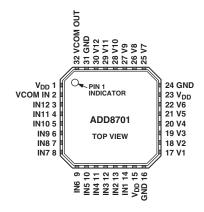

#### PIN CONFIGURATION

#### PIN FUNCTION DESCRIPTION

| Pin No.      | Mnemonic          | Description          |

|--------------|-------------------|----------------------|

| 1, 15, 23    | $V_{\mathrm{DD}}$ | Power (+)            |

| 2            | VCOM IN           | VCOM Buffer Input    |

| 3–14         | IN12-IN1          | Gamma Buffer Inputs  |

| 16, 24, 31   | GND               | Power (–)            |

| 17-22, 25-30 | V1-V12            | Gamma Buffer Outputs |

| 32           | VCOM OUT          | VCOM Buffer Output   |

#### **CAUTION** \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADD8701 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0 -3-

$<sup>^1\</sup>theta_{JA}$  is specified for worst-case conditions, i.e.,  $\theta_{JA}$  is specified for device soldered in circuit board for surface-mount packages.

$<sup>^2\</sup>psi_{IB}$  is applied for calculating the junction temperature by reference to the board temperature.

### **ADD8701-Typical Performance Characteristics**

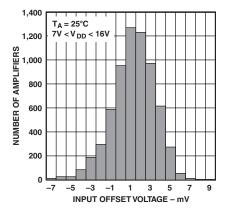

TPC 1. Input Offset Voltage Distribution

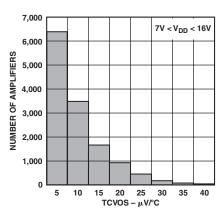

TPC 2. TCVOS Distribution

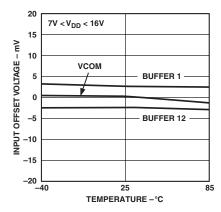

TPC 3. Input Offset Voltage vs. Temperature

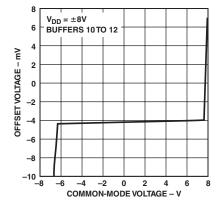

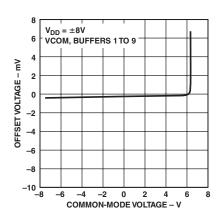

TPC 4. Offset Voltage vs. Common-Mode Voltage

TPC 5. Offset Voltage vs. Common-Mode Voltage

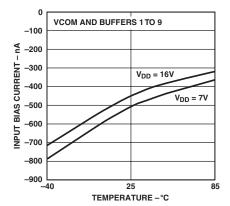

TPC 6. Input Bias Current vs. Temperature

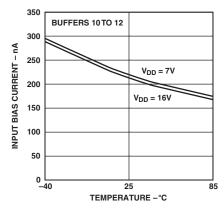

TPC 7. Input Bias Current vs. Temperature

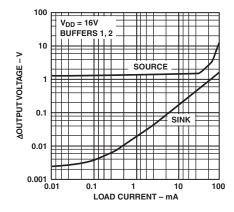

TPC 8. Output Voltage to Supply Rail vs. Load Current

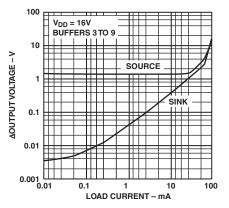

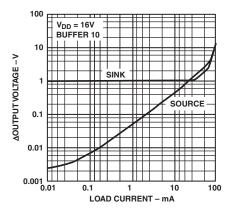

TPC 9. Output Voltage to Supply Rail vs. Load Current

-4- REV. 0

### **ADD8701**

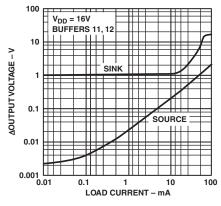

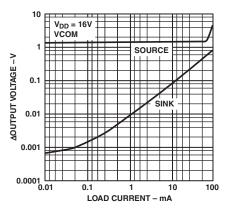

TPC 10. Output Voltage to Supply Rail vs. Load Current

TPC 11. Output Voltage to Supply Rail vs. Load Current

TPC 12. Output Voltage to Supply Rail vs. Load Current

TPC 13. Supply Current vs. Supply Voltage

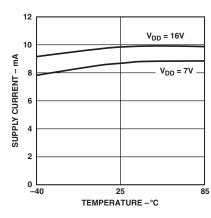

TPC 14. Supply Current vs. Temperature

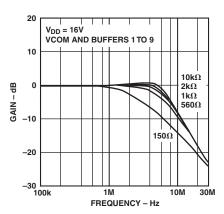

TPC 15. Frequency Response vs. Resistive Loading

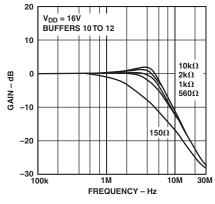

TPC 16. Frequency Response vs. Resistive Loading

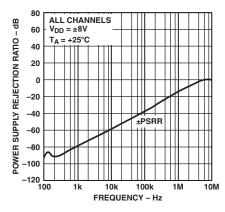

TPC 17. Power Supply Rejection Ratio vs. Frequency

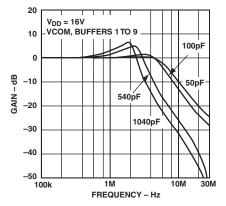

TPC 18. Frequency Response vs. Capacitive Loading

REV. 0 –5–

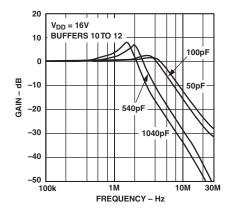

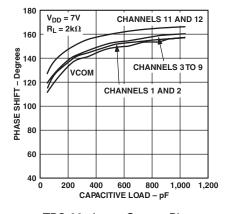

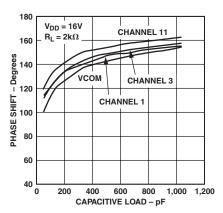

### ADD8701

TPC 19. Frequency Response vs. Capacitive Loading

TPC 20. Input-Output Phase Shift vs. Capacitive Load

TPC 21. Input-Output Phase Shift vs. Capacitive Load

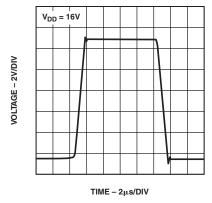

TPC 22. Large-Signal Transient Response

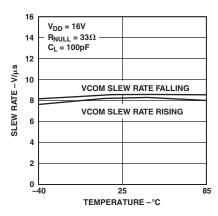

TPC 23. Slew Rate vs. Temperature

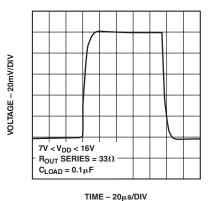

TPC 24. Small Signal Transient Response

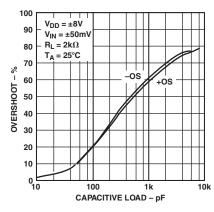

TPC 25. Small-Signal Overshoot vs. Capacitive Load

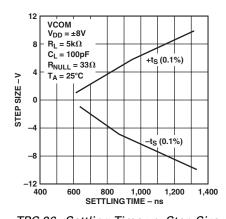

TPC 26. Settling Time vs. Step Size

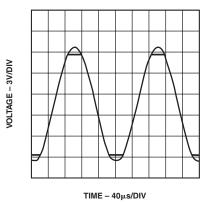

TPC 27. No Phase Reversal

-6- REV. 0

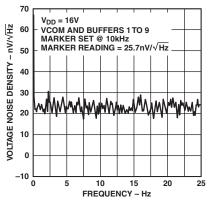

TPC 28. Voltage Noise Density vs. Frequency

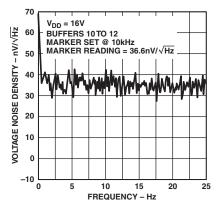

TPC 29. Voltage Noise Density vs. Frequency

#### **APPLICATIONS**

#### **LCD Gamma Reference Buffers**

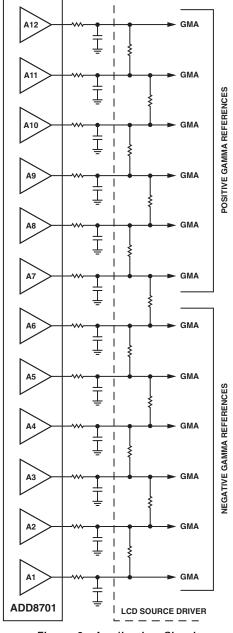

In high resolution TFT-LCD displays, gamma correction must be performed to correct the nonlinearity in the LCD panel's transmission characteristics. A typical TFT-LCD panel consisting of 256 grayscale levels takes an 8-bit digital word to select an appropriate gamma reference voltage. An 8-bit source driver may use 12 analog voltages that match the characteristic gamma curve for optimum panel picture quality. The ADD8701 is specifically designed to generate analog reference voltages to meet the gamma characteristics of an LCD panel used by the source driver. The gamma reference buffers offer 10 mA drive capability.

The ADD8701 is designed to meet the rail-to-rail capability needed by the application and yet offers a low cost-per-channel solution. The design maximizes the die area by offering channels to swing to the positive and negative rails. It is imperative that the channels swinging close to the supply rail be used for the positive gamma references and that the channels swinging close to GND be used for the negative gamma references. See Figure 2 for an example of the application circuit.

#### **LCD VCOM Buffer**

The output of the VCOM buffer is designed to control the voltage on the back plate of the LCD display. The buffer must be capable of sinking and sourcing capacitive pulse current. The amplifier stability is designed for high load capacitance. A high quality ceramic capacitor is recommended to supply short duration current pulses at the output. The VCOM buffer of the ADD8701 can handle up to 35 mA of continuous output current and can drive up to 1,000 nF of pure capacitive load.

#### **Unused Buffers**

Inputs of any unused buffer should be tied to the ground plane.

Figure 2. Application Circuit

REV. 0

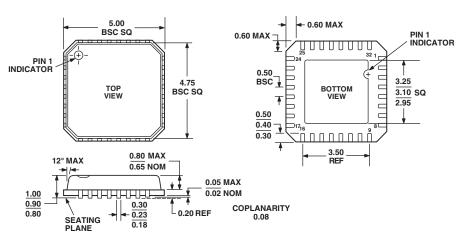

#### **OUTLINE DIMENSIONS**

# 32-Lead Lead Frame Chip Scale Package [LFCSP] (CP-32)

Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MO-220-VHHD-2

-8- REV. 0