# HI-8382, HI-8383

August 2006

# ARINC 429 DIFFERENTIAL LINE DRIVER

## **GENERAL DESCRIPTION**

The HI-8382 and HI-8383 bus interface products are silicon gate CMOS devices designed as a line driver in accordance with the ARINC 429 bus specifications.

Inputs are provided for clocking and synchronization. These signals are AND'd with the DATA inputs to enhance system performance and allow the HI-8382 to be used in a variety of applications. Both logic and synchronization inputs feature built-in 2,000V minimum ESD input protection as well as TTL and CMOS compatibility.

The differential outputs of the HI-8382 are independently programmable to either the high speed or low speed ARINC 429 output rise and fall time specifications through the use of two external capacitors. The output voltage swing is also adjustable by the application of an external voltage to the VREF input. The HI-8382 has on-chip Zener diodes in series with a fuse to each differential output protecting the ARINC bus from an overvoltage failure. The outputs each have a series resistance of 37.5 ohms. The HI-8383 is identical to the HI-8382 except that the series resistors are 13 ohms and the overvoltage protection circuitry has been eliminated.

The updated HI-318X and HI-8585 ARINC 429 line drivers are recommended for all new designs where logic signals must be converted to ARINC 429 levels such as a user ASIC, the HI-3282 or HI-8282A ARINC 429 Serial Transmitter/Dual Receiver, the HI-6010 ARINC 429 Transmitter/Receiver or the HI-8783 ARINC interface device. Holt products are readily available for both industrial and military applications. Please contact the Holt Sales Department for additional information, including data sheets for any of the Holt products mentioned above.

# **FEATURES**

- Low power CMOS

- TTL and CMOS compatible inputs

- Programmable output voltage swing

- · Adjustable ARINC rise and fall times

- Operates at data rates up to 100 Kbits

- Overvoltage protection

- Industrial and Military temperature ranges

- DSCC SMD part number

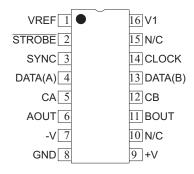

# PIN CONFIGURATION (Top View)

HI-8382C / CT / CM-01 / CM-03 SMD # 5962-8687901EA

16 - PIN CERAMIC SIDE-BRAZED DIP

(See Page 6 for additional package pin configurations)

#### **FUNCTION**

**ARINC 429 DIFFERENTIAL LINE DRIVER**

# TRUTH TABLE

| SYNC | СГОСК | DATA(A) | DATA(B) | AOUT  | BOUT  | COMMENTS |

|------|-------|---------|---------|-------|-------|----------|

| Х    | L     | Х       | Х       | 0V    | 0V    | NULL     |

| L    | Х     | Х       | Х       | 0V    | 0V    | NULL     |

| Н    | Н     | L       | L       | 0V    | 0V    | NULL     |

| Н    | Н     | L       | Н       | -VREF | +VREF | LOW      |

| Н    | Н     | Н       | L       | +VREF | -VREF | HIGH     |

| Н    | Н     | Н       | Н       | 0V    | 0V    | NULL     |

#### FUNCTIONAL DESCRIPTION

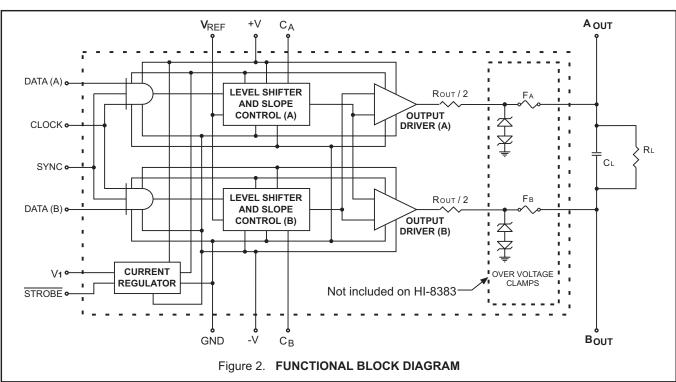

The SYNC and CLOCK inputs establish data synchronization utilizing two AND gates, one for each data input. Each logic input, including the power enable (STROBE) input, are TTL/CMOS compatible. Besides reducing chip current drain, STROBE also floats each output. However the overvoltage fuses and diodes of the HI-8382 are not switched out.

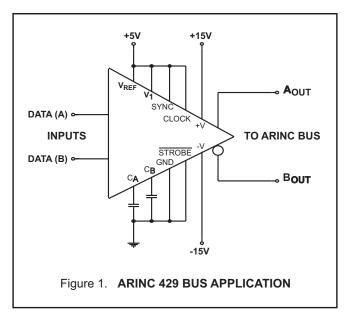

Figure 1 illustrates a typical ARINC 429 bus application. Three power supplies are necessary to operate the HI-8382; typically +15V, -15V and +5V. The chip also works with ±12V supplies. The +5V supply can also provide a reference voltage that determines the output voltage swing. The differential output voltage swing will equal 2VREF. If a value of VREF other than +5V is needed, a separate +5V power supply is required for pin V1.

With the DATA (A) input at a logic high and DATA (B) input at a logic low, AOUT will switch to the +VREF rail and BOUT will switch to the -VREF rail (ARINC HIGH state). With both data input signals at a logic low state, the outputs will both switch to OV (ARINC NULL state).

The driver output impedance, Rout, is nominally 75 ohms. The rise and fall times of the outputs can be calibrated through the selection of two external capacitor values that are connected to the CA and CB input pins. Typical values for high-speed operation (100KBPS) are CA = CB = 75pF and for low-speed operation (12.5 to 14KBPS) CA = CB = 500pF. The driver can be externally powered down by applying a logic high to the  $\overline{\text{STROBE}}$  input pin. If this feature is not being used, the pin should be tied to ground.

The CA and CB pins are inputs to unity gain amplifiers. Therefore they must be allowed to swing to -5V. Provision to

switch capacitors must be done with analog switches that allow voltages below their ground.

Both ARINC outputs of the HI-8382 are protected by internal fuses capable of sinking between 800 - 900 mA for short periods of time (125µs).

#### POWER SUPPLY SEQUENCING

The power supplies should be controlled to prevent large currents during supply turn-on and turn-off. The recommended sequence is +V followed by V1, always ensuring that +V is the most positive supply. The -V supply is not critical and can be asserted at any time.

#### **PIN DESCRIPTIONS**

| SYMBOL   | FUNCTION | DESCRIPTION                                                      |

|----------|----------|------------------------------------------------------------------|

| VREF     | POWER    | THE REFERENCE VOLTAGE USED TO DETERMINE THE OUTPUT VOLTAGE SWING |

| STROBE   | INPUT    | A LOGIC HIGH ON THIS INPUT PLACES THE DRIVER IN POWER DOWN MODE  |

| SYNC     | INPUT    | SYNCHRONIZES DATA INPUTS                                         |

| DATA (A) | INPUT    | DATA INPUT TERMINAL A                                            |

| СА       | INPUT    | CONNECTION FOR DATA (A) SLEW-RATE CAPACITOR                      |

| Аоит     | OUTPUT   | ARINC OUTPUT TERMINAL A                                          |

| -V       | POWER    | -12V to -15V                                                     |

| GND      | POWER    | 0.0V                                                             |

| +V       | POWER    | +12V to +15V                                                     |

| Воит     | OUTPUT   | ARINC OUTPUT TERMINAL B                                          |

| Св       | INPUT    | CONNECTION FOR DATA (B) SLEW-RATE CAPACITOR                      |

| DATA (B) | INPUT    | DATA INPUT TERMINAL B                                            |

| CLOCK    | INPUT    | SYNCHRONIZES DATA INPUTS                                         |

| V1       | POWER    | +5V ±5%                                                          |

#### **ABSOLUTE MAXIMUM RATINGS**

All Voltages referenced to GND, TA = Operating Temperature Range (unless otherwise specified)

| PARAMETER                                    | SYMBOL         | CONDITIONS                                                                                                                        | OPERATING RANGE                            | MAXIMUM                          | UNIT                         |

|----------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------|------------------------------|

| Differential Voltage                         | VDIF           | Voltage between +V and -V terminals                                                                                               |                                            | 40                               | V                            |

| Supply Voltage                               | +V<br>-V<br>V1 |                                                                                                                                   | +10.8 to +16.5<br>-10.8 to -16.5<br>+5 ±5% | +7                               | V<br>V<br>V                  |

| Voltage Reference                            | VREF           | For ARINC 429<br>For Applications other than ARINC                                                                                | +5 ±5%<br>0 to 6                           | 6<br>6                           | V                            |

| Input Voltage Range                          | VIN            |                                                                                                                                   |                                            | ≥ GND -0.3<br>≤ V1 +0.3          | V                            |

| Output Short-Circuit Duration                |                | See Note: 1                                                                                                                       |                                            |                                  |                              |

| Output Overvoltage Protection                |                | See Note: 2                                                                                                                       |                                            |                                  |                              |

| Operating Temperature Range                  | Та             | Hi-temp & Military<br>Industrial                                                                                                  | -55 to +125<br>-40 to +85                  |                                  | သို့                         |

| Storage Temperature Range                    | Тѕтс           | Ceramic & Plastic                                                                                                                 | -65 to +150                                |                                  | °C                           |

| Lead Temperature                             |                | Soldering, 10 seconds                                                                                                             |                                            | +275                             | °C                           |

| Junction Temperature                         | TJ             |                                                                                                                                   |                                            | +175                             | °C                           |

| Power Dissipation                            | PD             | 16-Pin Ceramic DIP See Note: 3<br>28-Pin Ceramic LCC See Note: 3<br>28-Pin Plastic PLCC See Note: 3<br>32-Pin CERQUAD See Note: 3 |                                            | 1.725<br>1.120<br>2.143<br>1.725 | W<br>W<br>W                  |

| Thermal Resistance,<br>(Junction-to-Ambient) | ØJA            | 16-Pin Ceramic DIP<br>28-Pin Ceramic LCC<br>28-Pin Plastic PLCC<br>32-Pin CERQUAD                                                 |                                            | 86.5<br>133.7<br>70.0<br>86.5    | °C/W<br>°C/W<br>°C/W<br>°C/W |

Heatsinking may be required for Output Short Circuit at +125°C and for 100KBPS at +125°C. Note 1.

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

The fuses used for Output Overvoltage Protection may be blown by the presence of a voltage at either output that is greater than ±12.0V with respect to GND. (HI-8382 only)

Derate above +25°C, 11.5mW/°C for 16-PIN DIP and 32-PIN CERQUAD, 7.5 mW/°C for 28-PIN LCC, 14.2 mW/°C for 28-PIN PLCC Note 2.

## DC ELECTRICAL CHARACTERISTICS

+V = +15V, -V = -15V,  $V_1 = V_{REF} = +5.0V$ ,  $T_A = Operating Temperature Range (unless otherwise specified).$

| PARAMETER                                     | SYMBOL       | CONDITION                            | MIN         | TYP | MAX           | UNITS |

|-----------------------------------------------|--------------|--------------------------------------|-------------|-----|---------------|-------|

| Supply Current +V (Operating)                 | ICCOP (+V)   | No Load (0 - 100KBPS)                |             |     | +11           | mA    |

| Supply Current -V (Operating)                 | ICCOP (-V)   | No Load (0 - 100KBPS)                | -11         |     |               | mA    |

| Supply Current V1 (Operating)                 | ICCOP (V1)   | No Load (0 - 100KBPS)                |             |     | 500           | μΑ    |

| Supply Current VREF (Operating)               | ICCOP (VREF) | No Load (0 - 100KBPS)                |             |     | 500           | μΑ    |

| Supply Current +V (Power Down)                | ICCPD (+V)   | STROBE = HIGH                        |             |     | 475           | uA    |

| Supply Current -V (Power Down)                | ICCPD (-V)   | STROBE = HIGH                        | -475        |     |               | uA    |

| Supply Current +V (During Short Circuit Test) | Isc (+V)     | Short to Ground (See Note: 1)        |             |     | 150           | mA    |

| Supply Current -V (During Short Circuit Test) | Isc (-V)     | Short to Ground (See Note: 1)        | -150        |     |               | mA    |

| Output Short Circuit Current (Output High)    | Ionsc        | Short to Ground VMIN=0 (See Note: 2) |             |     | -80           | mA    |

| Output Short Circuit Current (Output Low)     | lolsc        | Short to Ground VMIN=0 (See Note: 2) | +80         |     |               | mA    |

| Input Current (Input High)                    | IIН          |                                      |             |     | 1.0           | μΑ    |

| Input Current (Input Low)                     | liL          |                                      |             |     | -1.0          | μA    |

| Input Voltage High                            | VIH          |                                      | 2.0         |     |               | V     |

| Input Voltage Low                             | VIL          |                                      |             |     | 0.5           | V     |

| Output Voltage High (Output to Ground)        | Voн          | No Load (0 -100KBPS)                 | +VREF<br>25 |     | +VREF<br>+.25 | V     |

| Output Voltage Low (Output to Ground)         | Vol          | No Load (0 -100KBPS)                 | -VREF<br>25 |     | -VREF<br>+.25 | V     |

| Output Voltage Null                           | VNULL        | No Load (0-100KBPS)                  | -250        |     | +250          | mV    |

| Input Capacitance                             | CIN          | See Note 1                           |             | 15  |               | pF    |

Note 1. Not tested, but characterized at initial device design and after major process and/or design change which affects this parameter.

# **AC ELECTRICAL CHARACTERISTICS**

+V = +15V, -V = -15V,  $V_1 = V_{REF} = +5.0V$ ,  $T_A = Operating Temperature Range (unless otherwise specified).$

| PARAMETER                        | SYMBOL | CONDIT           | ION           | MIN | TYP | MAX | UNITS |

|----------------------------------|--------|------------------|---------------|-----|-----|-----|-------|

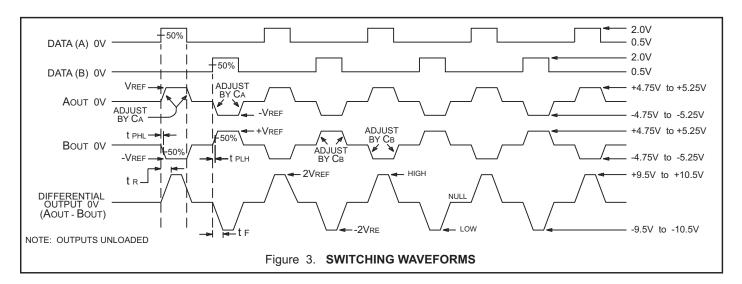

| Rise Time (AOUT, BOUT)           | t R    | CA = CB = 75pF S | See Figure 3. | 1.0 |     | 2.0 | μs    |

| Fall Time (AOUT, BOUT)           | t F    | CA = CB = 75pF S | See Figure 3. | 1.0 |     | 2.0 | μs    |

| Propagtion Delay Input to Output | t PLH  | CA = CB = 75pF S | See Figure 3. |     |     | 3.0 | μs    |

| Propagtion Delay Input to Output | t PHL  | CA = CB = 75pF S | See Figure 3. |     |     | 3.0 | μs    |

Note 2. Interchangeability of force and sense is acceptable.

#### HI-8382 PACKAGE THERMAL CHARACTERISTICS

#### MAXIMUM ARINC LOAD 7

| PACKAGE STYLE 1        | ARINC 429               | SUPPLY CURRENT (mA) <sup>2</sup> |           |            | JUNCTION TEMP, Tj (°C) |           |            |  |

|------------------------|-------------------------|----------------------------------|-----------|------------|------------------------|-----------|------------|--|

| PACKAGE STILE          | DATA RATE               | Ta = 25°C                        | Ta = 85°C | Ta = 125°C | Ta = 25°C              | Ta = 85°C | Ta = 125°C |  |

| 20   22   10   10      | Low Speed <sup>3</sup>  | 17.6                             | 17.2      | 17.0       | 48                     | 107       | 142        |  |

| 28 Lead PLCC           | High Speed <sup>4</sup> | 25.4                             | 24.5      | 24.2       | 56                     | 110       | 150        |  |

| 16 Load Caramia SP DID | Low Speed               | 17.9                             | 17.4      | 17.1       | 41                     | 103       | 145        |  |

| 16 Lead Ceramic SB DIP | High Speed              | 25.8                             | 24.8      | 24.4       | 47                     | 112       | 147        |  |

# AOUT and BOUT Shorted To Ground 5, 6, 7

| PACKAGE STYLE 1        | ARINC 429               | SUPPLY CURRENT (mA) <sup>2</sup> |           |            | JUNCTION TEMP, Tj (°C) |           |            |  |

|------------------------|-------------------------|----------------------------------|-----------|------------|------------------------|-----------|------------|--|

| PACKAGE STILE          | DATA RATE               | Ta = 25°C                        | Ta = 85°C | Ta = 125°C | Ta = 25°C              | Ta = 85°C | Ta = 125°C |  |

| 001 1 D1 00            | Low Speed <sup>3</sup>  | 60.1                             | 55.7      | 52.4       | 110                    | 157       | 194        |  |

| 28 Lead PLCC           | High Speed <sup>4</sup> | 63.1                             | 56.3      | 52.3       | 100                    | 150       | 182        |  |

| 16 Lead Ceramic SB DIP | Low Speed               | 62.1                             | 56.2      | 53.0       | 90                     | 145       | 180        |  |

|                        | High Speed              | 64.0                             | 56.2      | 52.2       | 86                     | 144       | 176        |  |

#### Notes:

- 1. All data taken in still air on devices soldered to a single layer copper PCB (3" X 4.5" X .062").

- 2. At 100% duty cycle, 15V power supplies. For 12V power supplies multiply all tabulated values by 0.8.

- 3. Low Speed: Data Rate = 12.5 Kbps, Load: R = 400 Ohms, C = 30 nF.

- 4. High Speed: Data Rate = 100 Kbps, Load: R = 400 Ohms, C = 10 nF. Data not presented for C = 30 nF as this is considered unrealistic for high speed operation.

- 5. Similar results would be obtained with AOUT shorted to BOUT.

- 6. For applications requiring survival with continuous short circuit, operation above Tj = 175°C is not recommended.

- 7. Data will vary depending on air flow and the method of heat sinking employed.

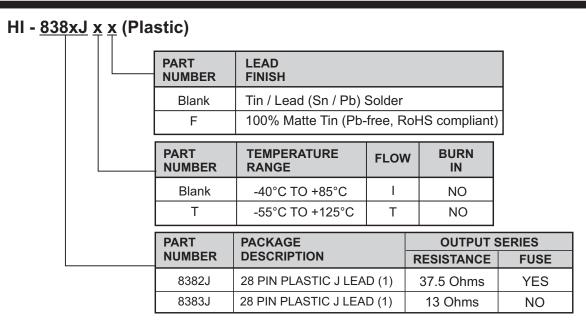

## ORDERING INFORMATION

HI - <u>838x x x - xx</u> (Ceramic)

| PART<br>NUMBER | TEMPERATURE<br>RANGE | FLOW | BURN<br>IN |

|----------------|----------------------|------|------------|

| Blank          | -40°C TO +85°C       | I    | NO         |

| Т              | -55°C TO +125°C      | Т    | NO         |

| M-01           | -55°C TO +125°C      | М    | YES        |

| M-03 (1)       | -55°C TO +125°C      | DSCC | YES        |

| PART<br>NUMBER | PACKAGE<br>DESCRIPTION                       | LEAD<br>FINISH (2)      |

|----------------|----------------------------------------------|-------------------------|

| С              | 16 PIN CERAMIC SIDE BRAZED DIP               | Gold ('M' flow: solder) |

| S              | 28 PIN CERAMIC LEADLESS CHIP CARRIER         | Gold ('M' flow: solder) |

| U              | 32 PIN CERQUAD (not available with 'M' flow) | Solder                  |

| PART   | OUTPUT S   | SERIES |

|--------|------------|--------|

| NUMBER | RESISTANCE | FUSE   |

| 8382   | 37.5 Ohms  | YES    |

| 8383   | 13 Ohms    | NO     |

- (1) Only available in '8382C' package. SMD# 5962-8687901EA

- (2) Gold terminal finish is Pb-Free, RoHS compliant.

(1) NOT RECOMMENDED FOR NEW DESIGNS. The newer HI-3182PJxx and HI-3183PJxx are drop-in replacements for the older HI-8382Jxx and HI-8383Jxx respectively. The HI-318x parts are rated as Moisture Sensitive Level 1 (MSL 1) and do not require any special handling. The older HI-8382Jxx and HI-8383Jxx are rated as MSL 3 and require dry-packaging and /or bake-out in accordance with IPC/JEDEC J-STD-020A.

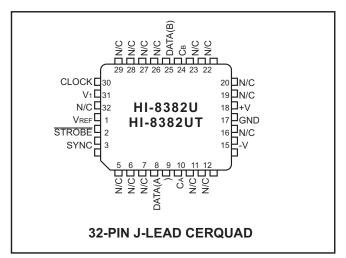

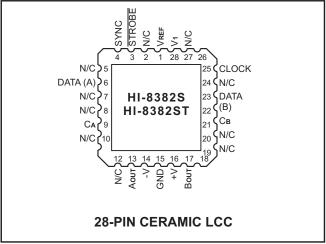

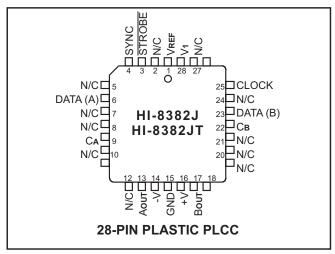

# **ADDITIONAL PIN CONFIGURATIONS**

(See page 1 for the 16-pin Ceramic Side-Brazed DIP Package)

HOLT INTEGRATED CIRCUITS

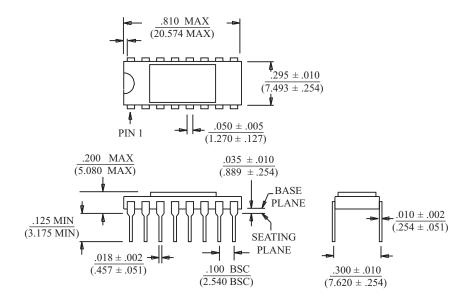

# HI-8382 PACKAGE DIMENSIONS

inches (millimeters)

#### 16-PIN CERAMIC SIDE-BRAZED DIP

Package Type: 16C

#### 28-PIN PLASTIC PLCC

Package Type: 28J

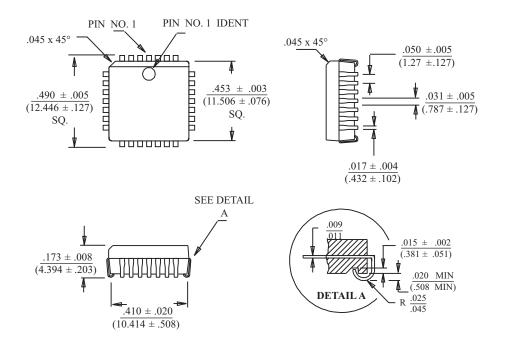

# **HI-8382 PACKAGE DIMENSIONS**

inches (millimeters)

#### 28-PIN CERAMIC LEADLESS CHIP CARRIER

Package Type: 28S

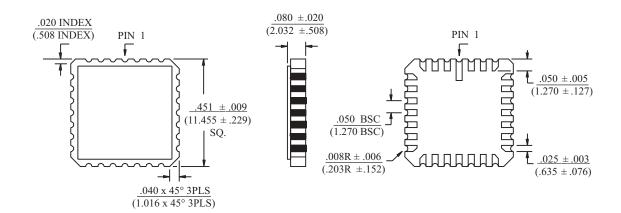

# 32-PIN J-LEAD CERQUAD