# 3628A 8K (1K x 8) BIPOLAR PROM

| 3628A-1 | 50 | ns | Max. |

|---------|----|----|------|

| 3628A-3 | 70 | ns | Max. |

| 3628A-4 | 90 | ns | Max. |

- Fast Access Time: 50 ns for 3628A-1

- Low Power Dissipation: 0.08 mW/Bit Typically

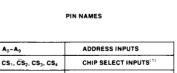

- Four Chip Select Inputs for Easy Memory Expansion

- **■** ±10% Power Supply Tolerance

- **■** Three-State Outputs

- Hermetic 24-Pin DIP

- Polycrystalline Silicon Fuses for Higher Fuse Reliability/Higher Programmability

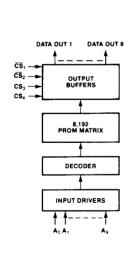

The Intel 3628A is a fully decoded 8192-bit PROM organized as 1024 words by 8 bits. The worst case access time of 35 ns is specified over the 0°C to 75°C temperature range and 10%  $V_{CC}$  power supply tolerances. There are four chip selects provided to facilitate expansion into larger PROM arrays. The PROMs use the Schottky clamped TTL technology with polycrystalline silicon fuses. All outputs are initially high, and logic low levels can be electrically programmed in selected bit locations.

The 3628A is a super-fast, high-density PROM. This 8192-bit PROM uses the most advanced technology available. As a result the 3628A combines higher performance and lower power in a smaller die than the 3628. The 3628A is packaged in a hermetic 24-pin dual in-line package with the exact pin configuration as the 3628.

**DATA OUTPUTS**

0.-0

Figure 1. Block Diagram

Figure 2. Pin Configuration

Figure 3. Logic Symbol

| <b>—</b> ○ | cs,                   | o,             |

|------------|-----------------------|----------------|

|            | CS <sub>2</sub>       | 02             |

| -          | CS <sub>3</sub>       | O <sub>3</sub> |

|            | CS <sub>4</sub>       | O <sub>4</sub> |

|            | <b>A</b> <sub>0</sub> | O <sub>5</sub> |

|            | <b>A</b> 1            | O <sub>6</sub> |

|            | <b>A</b> <sub>2</sub> | O,             |

|            | <b>A</b> <sub>3</sub> | 08             |

|            | <b>A</b> 4            |                |

|            | <b>A</b> 5            |                |

|            | <b>A</b> <sub>6</sub> |                |

| _          | <b>A</b> 7            |                |

|            | A <sub>B</sub>        |                |

|            | <b>A</b> 9            |                |

|            |                       |                |

## **PROGRAMMING**

The programming specifications are described in the PROM programming section of the Data Catalog.

### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias65°C to +125°C     |

|------------------------------------------|

|                                          |

| Storage Temperature65°C to +160°C        |

| Output or Supply Voltages0.5V to 7 Volts |

| All Input Voltages1.5V to 5.5V           |

| Output Currents                          |

\*NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# D.C. CHARACTERISTICS (All Limits Apply for V<sub>CC</sub> = +5.0V)± 10%, T<sub>A</sub> = 0°C to +75°C)

| Symbol Parame                  | Parameter                               | Limits |                     |       |      | Test Conditions                                                                                     |

|--------------------------------|-----------------------------------------|--------|---------------------|-------|------|-----------------------------------------------------------------------------------------------------|

|                                | , arameter                              | Min.   | Typ. <sup>[1]</sup> | Max.  | Unit |                                                                                                     |

| IFA                            | Address Input Load Current              |        | -0.05               | -0.25 | mA   | $V_{CC} = 5.5V, V_A = 0.45V$                                                                        |

| IFS                            | Chip Select Input Load Current          |        | -0.05               | -0.25 | mA   | $V_{CC} = 5.5V, V_{S} = 0.45V$                                                                      |

| IRA                            | Address Input Leakage Current           |        |                     | 40    | μΑ   | V <sub>CC</sub> = 5.5V, V <sub>A</sub> = 5.5V                                                       |

| l <sub>RS</sub>                | Chip Select Input Leakage Current       |        |                     | 40    | μΑ   | $V_{CC} = 5.5V, V_{S} = 5.5V$                                                                       |

| Io                             | Output Leakage for High Impedance State |        |                     | 40    | μА   | V <sub>O</sub> = 5.5V or 0.45V,<br>V <sub>CC</sub> = 5.5V, CS <sub>1</sub> = CS <sub>2</sub> = 2.4V |

| I <sub>SC</sub> <sup>[2]</sup> | Output Short Circuit Current            | -20    | -40                 | -100  | mA   | V <sub>O</sub> = 0V                                                                                 |

| V <sub>CA</sub>                | Address Input Clamp Voltage             |        | -0.9                | -1.5  | ٧    | V <sub>CC</sub> = 4.5V, I <sub>A</sub> = -10 mA                                                     |

| V <sub>CS</sub>                | Chip Select Input Clamp Voltage         |        | -0.9                | -1.5  | V    | V <sub>CC</sub> = 4.5V, I <sub>S</sub> = -10 mA                                                     |

| V <sub>OH</sub>                | Output High Voltage                     | 2.4    | 3.2                 |       | V    | $I_{OH} = -2.4 \text{ mA}, V_{CC} = 4.5 \text{V}$                                                   |

| VOL                            | Output Low Voltage                      |        | 0.3                 | 0.45  | ٧    | V <sub>CC</sub> = 4.5V, I <sub>OL</sub> = 10 mA                                                     |

| lcc                            | Power Supply Current                    |        | 120                 | 170   | mA   | V <sub>CC</sub> = 5.5V                                                                              |

| VIL                            | Input "Low" Voltage                     |        |                     | 0.85  | ٧    |                                                                                                     |

| V <sub>IH</sub>                | Input "High" Voltage                    | 2.0    |                     |       | ٧    |                                                                                                     |

#### NOTES:

- 1. Typical values are for T<sub>A</sub> = 25°C and nominal supply voltages.

- 2. Unmeasured outputs are open during this test.

# CAPACITANCE<sup>(1)</sup> (T<sub>A</sub> = 25°C, f = 1 MHz)

| Symbol           | Parameter                     | Limits |      | Unit | Test Conditions                              |  |

|------------------|-------------------------------|--------|------|------|----------------------------------------------|--|

|                  |                               | Тур.   | Max. | John | rest Conditions                              |  |

| CINA             | Address Input Capacitance     | 4      | 10   | pF   | V <sub>CC</sub> = 5V V <sub>IN</sub> = 2.5V  |  |

| CINS             | Chip-Select Input Capacitance | 4      | 10   | ρF   | V <sub>CC</sub> = 5V V <sub>IN</sub> = 2.5V  |  |

| C <sub>OUT</sub> | Output Capacitance            | 6      | 12   | pF   | V <sub>CC</sub> = 5V V <sub>OUT</sub> = 2.5\ |  |

#### NOTES

<sup>1.</sup> This parameter is only periodically sampled and is not 100% tested.

# A.C. CHARACTERISTICS ( $V_{CC} = +5V \pm 10\%$ , $T_{A} = 0^{\circ}C$ to $+75^{\circ}C$ )

| Symbol           | Parameter               |         | Max. Limits |         |      |                                                         |

|------------------|-------------------------|---------|-------------|---------|------|---------------------------------------------------------|

|                  |                         | 3628A-1 | 3628A-3     | 3628A-4 | Unit | Test Conditions                                         |

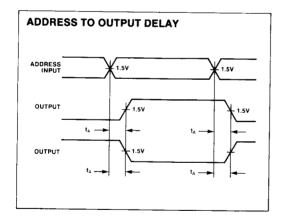

| t <sub>A</sub>   | Address to Output Delay | 50      | 70          | 90      | ns   | CS <sub>1</sub> = CS <sub>2</sub> = V <sub>II</sub> and |

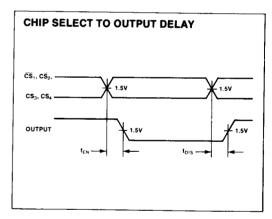

| t <sub>EN</sub>  | Output Enable Time      | 30      | 30          | 30      | ns   | $CS_3 = CS_4 = V_{IH}$ to                               |

| t <sub>DIS</sub> | Output Disable Time     | 30      | 30          | 30      | ns   | select the PROM.                                        |

## **SWITCHING CHARACTERISTICS**

## **Conditions of Test:**

Input pulse amplitudes: 2.5V

Input pulse rise and fall times of 5 nanoseconds between 1 volt and 2 volts

Speed measurements are made at 1.5 volt levels

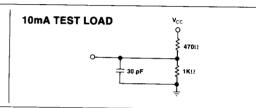

Output loading is 10 mA and 30 pF

Frequency of test: 2.5 MHz

## **WAVEFORMS**