Data Sheet July 26, 2004 FN7349.1

# Ultra-High Current Pin Driver

# élantec.

The EL7158 high performance pin driver with three-state is suited to many ATE and level-shifting

applications. The 12A peak drive capability makes this part an excellent choice when driving high capacitance loads.

The output pin OUT is connected to input pins  $V_H$  or  $V_L$  respectively, depending on the status of the IN pin. When the OE pin is active low, the output is placed in the three-state mode. The isolation of the output FETs from the power supplies enables  $V_H$  and  $V_L$  to be set independently, enabling level-shifting to be implemented. Related to the EL7155, the EL7158 adds a lower supply pin  $V_S$ - and makes  $V_L$  an isolated and independent input. This feature adds applications flexibility and improves switching response due to the increased enhancement of the output FETs.

This pin driver has improved performance over existing pin drivers. It is specifically designed to operate at voltages down to 0V across the switch elements while maintaining good speed and on-resistance characteristics.

Available in the 8-pin SO package, the EL7158 is specified for operation over the full -40°C to +85°C temperature range.

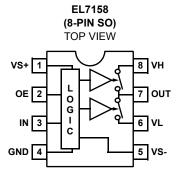

#### **Pinout**

#### Features

- · Clocking speeds up to 40MHz

- 12ns t<sub>R</sub>/t<sub>F</sub> at 2000pF C<sub>LOAD</sub>

- · 0.2ns rise and fall times mismatch

- 0.5ns T<sub>ON</sub>-T<sub>OFF</sub> prop delay mismatch

- · 3.5pF typical input capacitance

- 12A peak drive

- Low on resistance of  $0.5\Omega$

- High capacitive drive capability

- · Operates from 4.5V to 12V

- · Pb-free available

### **Applications**

- · ATE/burn-in testers

- · Level shifting

- · IGBT drivers

- · CCD drivers

# Ordering Information

| PART NUMBER                 | PACKAGE               | TAPE & REEL | PKG. DWG. # |

|-----------------------------|-----------------------|-------------|-------------|

| EL7158IS                    | 8-Pin SO              | -           | MDP0027     |

| EL7158IS-T7                 | 8-Pin SO              | 7"          | MDP0027     |

| EL7158IS-T13                | 8-Pin SO              | 13"         | MDP0027     |

| EL7158ISZ<br>(See Note)     | 8-Pin SO<br>(Pb-free) | -           | MDP0027     |

| EL7158ISZ-T7<br>(See Note)  | 8-Pin SO<br>(Pb-free) | 7"          | MDP0027     |

| EL7158ISZ-T13<br>(See Note) | 8-Pin SO<br>(Pb-free) | 13"         | MDP0027     |

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which is compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J Std-020B.

# **Absolute Maximum Ratings** (T<sub>A</sub> = 25°C)

| Supply Voltage (V <sub>S</sub> + to V <sub>S</sub> -) | Storage Temperature Range65°C to +150°C |

|-------------------------------------------------------|-----------------------------------------|

| Input Voltage                                         | Ambient operating Temperature           |

| Continuous Output Current                             | Operating Junction Temperature          |

|                                                       | Power Dissipation see curves            |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# **Electrical Specifications** $V_S$ + = +12V, $V_H$ = +12V, $V_L$ = 0V, $V_{S^-}$ = 0V, $T_A$ = 25°C, unless otherwise specified.

| PARAMETER        | DESCRIPTION                                         | CONDITION                                     | MIN    | TYP | MAX | UNIT |

|------------------|-----------------------------------------------------|-----------------------------------------------|--------|-----|-----|------|

| INPUT            |                                                     | -                                             |        | II. | l.  |      |

| V <sub>IH</sub>  | Logic '1' Input Voltage                             |                                               | 2.4    |     |     | V    |

| I <sub>IH</sub>  | Logic '1' Input Current                             | V <sub>IH</sub> = V <sub>S</sub> +            |        | 0.1 | 10  | μA   |

| V <sub>IL</sub>  | Logic '0' Input Voltage                             |                                               |        |     | 0.8 | V    |

| I <sub>IL</sub>  | Logic '0' Input Current                             | V <sub>IL</sub> = 0V                          |        | 0.1 | 10  | μA   |

| C <sub>IN</sub>  | Input Capacitance                                   |                                               |        | 3.5 |     | pF   |

| R <sub>IN</sub>  | Input Resistance                                    |                                               |        | 50  |     | MΩ   |

| OUTPUT           | 1                                                   | <u>'</u>                                      |        | 1   | 1   |      |

| R <sub>OVH</sub> | ON Resistance V <sub>H</sub> to OUT                 | I <sub>OUT</sub> = -500mA                     |        | 0.5 | 1   | Ω    |

| R <sub>OVL</sub> | ON Resistance V <sub>L</sub> to OUT                 | I <sub>OUT</sub> = +500mA                     |        | 0.5 | 1   | Ω    |

| lout             | Output Leakage Current                              | OE = 0V, OUT = V <sub>H</sub> /V <sub>L</sub> |        | 0.1 | 10  | μA   |

| I <sub>PK</sub>  | Peak Output Current<br>(linear resistive operation) | Source                                        |        | 12  |     | Α    |

|                  |                                                     | Sink                                          |        | 12  |     | Α    |

| I <sub>DC</sub>  | Continuous Output Current                           | Source/Sink                                   | 500    |     |     | mA   |

| POWER SUPPLY     |                                                     | <u>'</u>                                      |        | 1   | 1   |      |

| Is               | Power Supply Current                                | ver Supply Current Inputs = V <sub>S</sub> +  |        | 1.3 | 3   | mA   |

| I <sub>VH</sub>  | Off Leakage at V <sub>H</sub> and V <sub>L</sub>    | V <sub>H</sub> , V <sub>L</sub> = 0V          |        | 4   | 10  | μA   |

| SWITCHING CHA    | RACTERISTICS                                        | <u>'</u>                                      |        | 1   | 1   |      |

| t <sub>R</sub>   | Rise Time                                           | C <sub>L</sub> = 2000pF                       | F 12.0 |     |     | ns   |

| t <sub>F</sub>   | Fall Time                                           | C <sub>L</sub> = 2000pF                       | 12.2   |     |     | ns   |

| $t_{RF\Delta}$   | t <sub>R</sub> , t <sub>F</sub> Mismatch            | C <sub>L</sub> = 2000pF                       |        | 0.2 |     | ns   |

| t <sub>D-1</sub> | Turn-Off Delay Time                                 | C <sub>L</sub> = 2000pF                       | 22.5   |     |     | ns   |

| t <sub>D-2</sub> | Turn-On Delay Time                                  | C <sub>L</sub> = 2000pF                       | 22.0   |     |     | ns   |

| $t_{D\Delta}$    | t <sub>D-1</sub> -t <sub>D-2</sub> Mismatch         | C <sub>L</sub> = 2000pF                       | 0.5    |     |     | ns   |

| t <sub>D-3</sub> | Three-State Delay Enable                            |                                               | 22     |     | ns  |      |

| t <sub>D-4</sub> | Three-State Delay Disable                           |                                               | 22     |     | ns  |      |

| SR+              | V <sub>OUT</sub> + Slew Rate                        | $R_{LOAD} = 6\Omega$                          |        | 800 |     | V/µs |

| SR-              | V <sub>OUT</sub> - Slew Rate                        | $R_{LOAD} = 6\Omega$                          |        | 800 |     | V/µs |

# EL7158

# **Electrical Specifications** $V_S$ + = +12V, $V_H$ = +1.2V, $V_L$ = 0V, $V_{S^-}$ = 0V, $T_A$ = 25°C, unless otherwise specified

| PARAMETER        | DESCRIPTION CONDITION MIN                        |                                               | MIN      | TYP  | MAX | UNIT |

|------------------|--------------------------------------------------|-----------------------------------------------|----------|------|-----|------|

| INPUT            |                                                  | ·                                             | <u> </u> | "    |     |      |

| V <sub>IH</sub>  | Logic '1' Input Voltage 2.0                      |                                               | 2.0      |      |     | V    |

| I <sub>IH</sub>  | Logic '1' Input Current                          | V <sub>IH</sub> = V <sub>S</sub> +            |          | 0.1  | 10  | μA   |

| V <sub>IL</sub>  | Logic '0' Input Voltage                          |                                               |          |      | 0.8 | V    |

| I <sub>IL</sub>  | Logic '0' Input Current                          | V <sub>IL</sub> = 0V                          |          | 0.1  | 10  | μΑ   |

| C <sub>IN</sub>  | Input Capacitance                                |                                               |          | 3.5  |     | pF   |

| R <sub>IN</sub>  | Input Resistance                                 |                                               |          | 50   |     | ΜΩ   |

| OUTPUT           |                                                  |                                               | <u>'</u> |      |     |      |

| R <sub>OVH</sub> | ON Resistance V <sub>H</sub> to OUT              | I <sub>OUT</sub> = -500mA                     |          | 0.5  | 1   | Ω    |

| R <sub>OVL</sub> | ON Resistance V <sub>L</sub> to OUT              | I <sub>OUT</sub> = +500mA                     |          | 0.5  | 1   | Ω    |

| lout             | Output Leakage Current                           | OE = 0V, OUT = V <sub>H</sub> /V <sub>L</sub> |          | 0.1  | 10  | μA   |

| I <sub>PK</sub>  | Peak Output Current                              | Source                                        |          | 1.2  |     | Α    |

|                  | (linear resistive operation)                     | Sink                                          |          | 1.2  |     | Α    |

| I <sub>DC</sub>  | Continuous Output Current                        | Source/Sink                                   | 500      |      |     | mA   |

| POWER SUPPL      | Y                                                |                                               | <u>'</u> |      |     |      |

| Is               | Power Supply Current                             | Inputs = V <sub>S</sub> +                     |          | 1    | 2.5 | mA   |

| VH               | Off Leakage at V <sub>H</sub> and V <sub>L</sub> | V <sub>H</sub> , V <sub>L</sub> = 0V          |          | 4    | 10  | μA   |

| SWITCHING CH     | ARACTERISTICS                                    |                                               | <u>'</u> |      |     |      |

| t <sub>R</sub>   | Rise Time                                        | C <sub>L</sub> = 2000pF                       |          | 11   |     | ns   |

| t <sub>F</sub>   | Fall Time                                        | C <sub>L</sub> = 2000pF                       |          | 11   |     | ns   |

| $t_{RF\Delta}$   | t <sub>R</sub> , t <sub>F</sub> Mismatch         | C <sub>L</sub> = 2000pF                       | 0        |      |     | ns   |

| t <sub>D-1</sub> | Turn-Off Delay Time                              | C <sub>L</sub> = 2000pF                       | 20.5     |      |     | ns   |

| t <sub>D-2</sub> | Turn-On Delay Time                               | C <sub>L</sub> = 2000pF                       | 20.0     |      |     | ns   |

| $t_{D\Delta}$    | t <sub>D-1</sub> -t <sub>D-2</sub> Mismatch      | C <sub>L</sub> = 2000pF                       | 0.5      |      | ns  |      |

| t <sub>D-3</sub> | Three-State Delay Enable                         |                                               | 20       |      | ns  |      |

| t <sub>D-4</sub> | Three-State Delay Disable                        |                                               | 20 ns    |      | ns  |      |

| SR+              | V <sub>OUT</sub> + Slew Rate                     | $R_{LOAD} = 6\Omega$                          |          | 80   |     | V/µs |

| SR-              | V <sub>OUT</sub> - Slew Rate                     | $R_{LOAD} = 6\Omega$ 80                       |          | V/µs |     |      |

# **Typical Performance Curves**

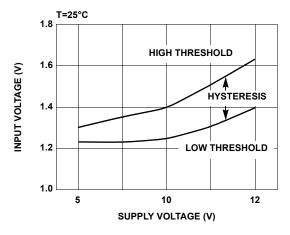

FIGURE 1. INPUT THRESHOLD vs SUPPLY VOLTAGE

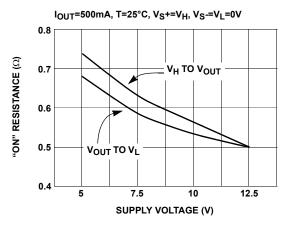

FIGURE 3. "ON" RESISTANCE vs SUPPLY VOLTAGE (VS+)

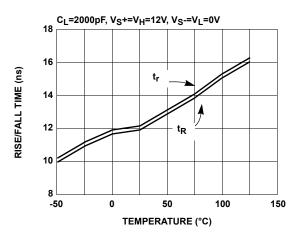

FIGURE 5. RISE/FALL TIME vs TEMPERATURE

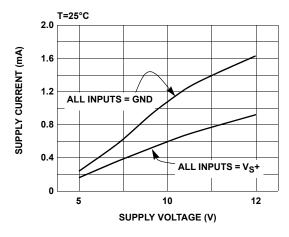

FIGURE 2. QUIESCENT SUPPLY CURRENT vs SUPPLY VOLTAGE

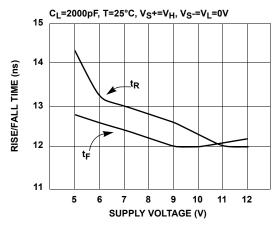

FIGURE 4. RISE/FALL TIME vs SUPPLY VOLTAGE

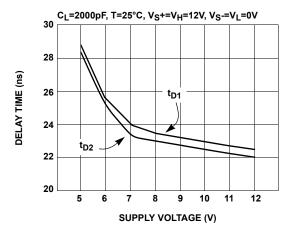

FIGURE 6. PROPAGATION DELAY vs SUPPLY VOLTAGE

# Typical Performance Curves (Continued)

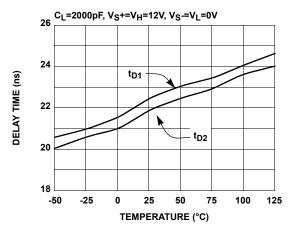

FIGURE 7. PROPAGATION DELAY vs TEMPERATURE

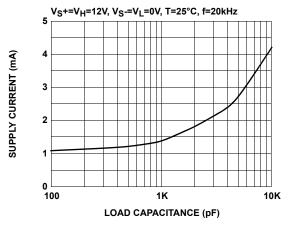

FIGURE 9. SUPPLY CURRENT vs LOAD CAPACITANCE

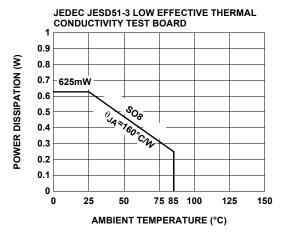

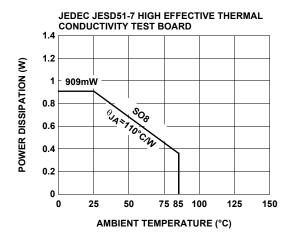

FIGURE 11. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

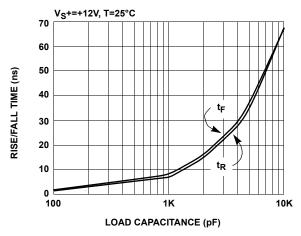

FIGURE 8. RISE/FALL TIME vs LOAD CAPACITANCE

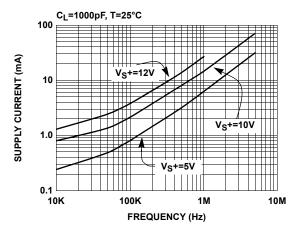

FIGURE 10. SUPPLY CURRENT vs FREQUENCY

FIGURE 12. PACKAGE POWER DISSIPATION VS AMBIENT TEMPERATURE

**TABLE 1. TRUTH TABLE**

| OE | IN | OUT            |

|----|----|----------------|

| 0  | 0  | Three-State    |

| 0  | 1  | Three-State    |

| 1  | 0  | V <sub>H</sub> |

| 1  | 1  | V <sub>L</sub> |

**TABLE 2. OPERATING VOLTAGE RANGE**

| PIN                                 | MIN            | MAX            |  |

|-------------------------------------|----------------|----------------|--|

| GND - V <sub>S</sub> -              | -5             | 0              |  |

| V <sub>S</sub> + - V <sub>S</sub> - | 5              | 18             |  |

| V <sub>H</sub> - V <sub>L</sub>     | 0              | 12             |  |

| V <sub>S</sub> + - V <sub>H</sub>   | 0              | 12             |  |

| V <sub>S</sub> + - GND              | 5              | 12             |  |

| V <sub>L</sub> - V <sub>S</sub> -   | 0              | 12             |  |

| Three-State Output                  | V <sub>L</sub> | V <sub>H</sub> |  |

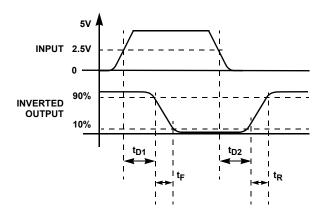

FIGURE 13. TIMING DIAGRAM

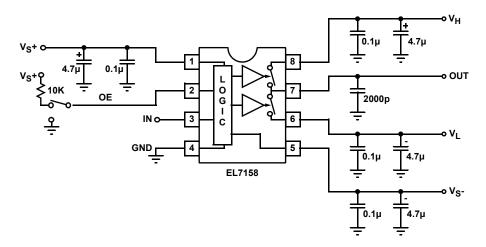

FIGURE 14. STANDARD TEST CONFIGURATION

# Pin Descriptions

| PIN | NAME | FUNCTION                | EQUIVALENT CIRCUIT                                                                                |

|-----|------|-------------------------|---------------------------------------------------------------------------------------------------|

| 1   | VS+  | Positive Supply Voltage |                                                                                                   |

| 2   | OE   | Output Enable           | INPUT O VS-O Circuit 1                                                                            |

| 3   | IN   | Input                   | Reference Circuit 1                                                                               |

| 4   | GND  | Ground                  |                                                                                                   |

| 5   | VS-  | Negative Supply Voltage |                                                                                                   |

| 6   | VL   | Lower Output Voltage    |                                                                                                   |

| 7   | OUT  | Output                  | V <sub>S</sub> -O <sub>V</sub> S-V <sub>OUT</sub> V <sub>OUT</sub> V <sub>S</sub> -V <sub>L</sub> |

| 8   | VH   | High Output Voltage     |                                                                                                   |

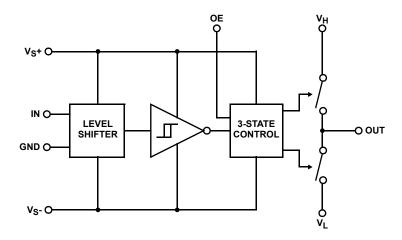

FIGURE 15. BLOCK DIAGRAM

# **Applications Information**

### **Product Description**

The EL7158 is a high performance 40MHz pin driver. It contains two analog switches connecting  $V_H$  and  $V_L$  to OUT. Depending on the value of the IN pin, one of the two switches will be closed and the other switch open. An output enable (OE) is also supplied which opens both switches simultaneously.

Due to the topology of the EL7158, both the  $V_H$  and  $V_L$  pins can be connected to any voltage between the  $V_S$ + and  $V_S$ -pins, but  $V_H$  must be greater than  $V_L$  in order to prevent turning on the body diode at the output stage.

### Three-State Operation

When the OE pin is low, the output is three-state (floating.) The output voltage is the parasitic capacitance's voltage. It can be any voltage between  $V_H$  and  $V_L$ , depending on the previous state. At three-state, the output voltage can be pushed to any voltage between  $V_H$  and  $V_L$ . The output voltage can't be pushed higher than  $V_H$  or lower than  $V_L$  since the body diode at the output stage will turn on.

### Supply Voltage Range and Input Compatibility

The EL7158 is designed for operation on supplies from 5V to 18V (4.5V to 18V maximum). Table 2 shows the specifications for the relationship between the  $V_S^+$ ,  $V_{S^-}$ ,  $V_H$ ,  $V_L$ , and GND pins.

All input pins are compatible with both 3V and 5V CMOS signals. With a positive supply ( $V_S+$ ) of 5V, the EL7158 is also compatible with TTL inputs.

#### Power Supply Bypassing

When using the EL7158, it is very important to use adequate power supply bypassing. The high switching currents developed by the EL7158 necessitate the use of a bypass capacitor between the supplies (V $_{\rm S}+$  & V $_{\rm S}-$ ) and GND pins. It is recommended that a 2.2µF tantalum capacitor be used in parallel with a 0.1µF low-inductance ceramic MLC capacitor. These should be placed as close to the supply pins as possible. It is also recommended that the V $_{\rm H}$  and V $_{\rm L}$  pins have some level of bypassing, especially if the EL7158 is driving highly capacitive loads.

### Power Dissipation Calculation

When switching at high speeds, or driving heavy loads, the EL7158 drive capability is limited by the rise in die temperature brought about by internal power dissipation. For reliable operation die temperature must be kept below  $T_{\mbox{\scriptsize JMAX}}$  (125°C). It is necessary to calculate the power dissipation for a given application prior to selecting the package type.

Power dissipation may be calculated:

$$PD = (V_S \times I_S) + (C_{INT} \times V_S^2 \times f) + (C_I \times V_{OLIT}^2 \times f)$$

where:

$V_S$  is the total power supply to the EL7158 (from  $V_S$ + to GND)

V<sub>OUT</sub> is the swing on the output (V<sub>H</sub> - V<sub>L</sub>)

C<sub>I</sub> is the load capacitance

C<sub>INT</sub> is the internal load capacitance (100pF max)

I<sub>S</sub> is the quiescent supply current (3mA max)

f is frequency

Having obtained the application's power dissipation, a maximum package thermal coefficient may be determined, to maintain the internal die temperature below T<sub>.IMAX</sub>:

$$\theta_{JA} = \frac{T_{JMAX} - T_{MAX}}{PD}$$

where

T<sub>JMAX</sub> is the maximum junction temperature (125°C)

T<sub>MAX</sub> is the maximum operating temperature

PD is the power dissipation calculated above

$\theta_{JA}$  thermal resistance on junction to ambient

$\theta_{JA}$  is 160°C/W for the SO8 package when using a standard JEDEC JESD51-3 single-layer test board. If  $T_{JMAX}$  is greater than 125°C when calculated using the equation above, then one of the following actions must be taken:

Reduce  $\theta_{JA}$  the system by designing more heat-sinking into the PCB (as compared to the standard JEDEC JESD51-3)

De-rate the application either by reducing the switching frequency, the capacitive load, or the maximum operating (ambient) temperature (T<sub>MAX</sub>)

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com