# Digitally Programmable 8 to 25 Multiplex LCD Controller & Driver

### **Features**

- Slim IC for chip-on-board, with gold bumps for Chip-On-Glas and Chip-On-Flex technologies

- Very simple 2-wire interface

- Digitally programmable multiplex rates: 8 x 113, 9 x 112, 16 x 105, 17 x 104, 20 x 101, 21 x 100, 24 x 97, 25 x 96

- No lost pads while row driver from 8 up to 25

- On chip: Voltage multiplier, V<sub>LCD</sub> up to 7 V (3 to 6 V at 25 °C), 64 V<sub>LCD</sub> digitally programming steps, 4 V<sub>LCD</sub> temperature compensation factors, bias generation, V<sub>ON</sub> / V<sub>OFF</sub> generation, frame frequency, display refresh RAM

- No busy state

- High noise immunity in inputs

- No external components needed, except a V<sub>LCD</sub> capacitor

- Digitally reversing row data

- Digitally reversing column data

- Inverting data function

- Blank function

- Set function

- Checker and Inverted Checker functions

- Sleep modes

- Low LCD operating current consumption

- Wide V<sub>DD</sub> voltage supply range, 2 to 5 V

- Wide temperature range: -40 to + 85 °C

- Direct display of RAM data through the display data

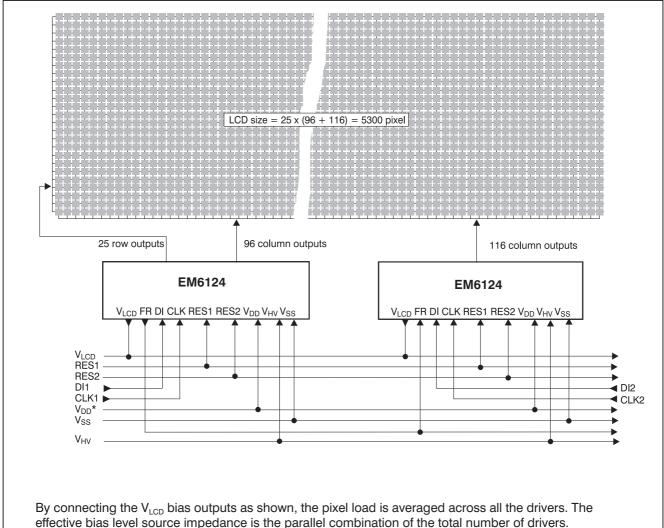

(To cascade ICs, please see Fig. 19 and contact EM-Marin.)

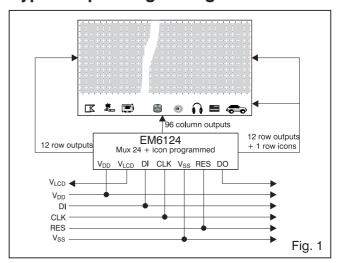

### Description

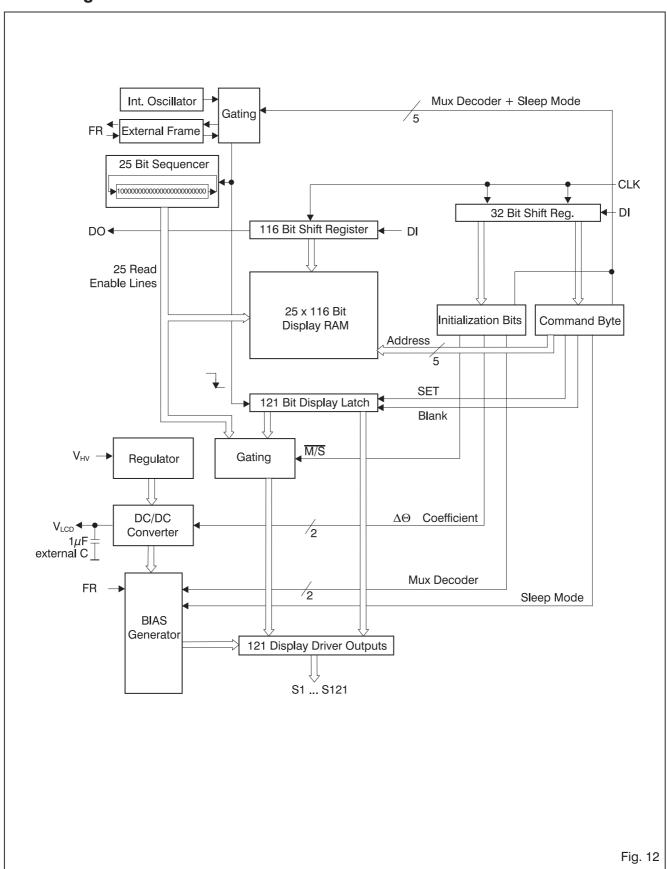

The EM6124 is a low power CMOS LCD controller and driver. The 8, 16, 20 and 24 way multiplex are digitally programmable by the command byte. One additional line can be added for Icons or Inverted Video by programming 9, 17, 21 or 25 way multiplex. The display refresh is handled on chip by an internal RC oscillator via one selectable 25 x 116 RAM which holds the LCD content driven by the driver. LCD pixels (or segments) are addressed on a one to one basis with the 25 x 116 bit RAM (a set bit corresponds to an activated LCD pixel). The EM6124 has very low dynamic current consumption, typically 70  $\mu$ A at  $V_{DD}$ = 2 V, V<sub>ICD</sub> = 7 V making it particularly attractive for portable and battery powered products. The wide operating range on supply voltages and temperature offers much application flexibility. The LCD voltage, bias generation and frame frequency are generated on chip. The clock signal can be used to shift and to latch the data into the RAM.

### **Applications**

- Mobile phones (GSM, DECT)

- Smart cards

- Automotive displays

- Portable, battery operated products

- Balances and scales, utility meters

### **Typical Operating Configuration**

### **Pad Assignment**

### **Absolute Maximum Ratings**

|                                     | _                |                                             |

|-------------------------------------|------------------|---------------------------------------------|

| Parameter                           | Symbol           | Conditions                                  |

| Supply voltage range                | $V_{DD1.2}$      | -0.3 V to 6 V                               |

| Supply high voltage range           | $V_{HV}$         | -0.3 V to 6 V                               |

| Internal generated V <sub>LCD</sub> | $V_{LCD}$        | 7 V                                         |

| Voltage at DI, DO, CLK, FR, RES     | $V_{LOGIC}$      | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$  |

| Voltage at S1 to S121               | $V_{DISP}$       | $-0.3 \text{ V to V}_{LCD} + 0.3 \text{ V}$ |

| Storage temperature range           | T <sub>STO</sub> | -65 to +150 °C                              |

| Electrostatic discharge max.        |                  |                                             |

| to MIL-STD-883C method 3015         | $V_{Smax}$       | 1000 V                                      |

| Maximum soldering conditions        | $T_{Smax}$       | 250 °C x 10 s                               |

Table 1

Stresses above these listed maximum ratings may cause permanent damage to the device. Exposure beyond specified operating conditions may affect device reliability or cause malfunction.

### **Handling Procedures**

This device has built-in protection against high static voltages or electric fields; however, anti-static precautions must be taken as for any other CMOS component. Unless otherwise specified, proper operation can only occur when all terminal voltages are kept within the supply voltage range. Unused inputs must always be tied to a defined logic voltage level.

### **Operating Conditions**

| Parameter             | Symbol         | Min. | Тур. | Max. | Unit |

|-----------------------|----------------|------|------|------|------|

| Operating temperature | T <sub>A</sub> | -40  |      | +85  | °C   |

| Logic supply voltage  | $V_{DD1,2}$    | 2    | 3    | 5.5  | V    |

| Supply high voltage   | $V_{HV}$       | 2.5  | 3    | 5.5  | V    |

Table 2

### **Electrical Characteristics**

$V_{DD1} = V_{DD2} = 3$  V,  $V_{HV} = 2.5$  to 5 V, and  $T_A = -40$  to +85 °C, unless otherwise specified

| Parameter                               | Symbol                | Test Conditions                              | Min.                   | Тур.        | Max.                 | Units |  |

|-----------------------------------------|-----------------------|----------------------------------------------|------------------------|-------------|----------------------|-------|--|

| Standby supply current                  | I <sub>DD</sub>       | See note 1)                                  |                        | 16          | 22                   | μΑ    |  |

| Standby supply current                  | I <sub>HV</sub>       | See note1), V <sub>LCD</sub> step 30 (hexa)  |                        | 65          | 170                  | μA    |  |

| Dynamic supply current                  | I <sub>DD</sub>       | See note 2)                                  |                        | 57          | 75                   | μA    |  |

| Standby supply current                  | I <sub>HV</sub>       | See note 3), V <sub>ICD</sub> step 00 (hexa) |                        | 35          | 140                  | μA    |  |

| Sleep mode supply current               | I <sub>DD</sub>       |                                              |                        | 0.1         |                      | μA    |  |

| Sleep mode supply current               | I <sub>HV</sub>       |                                              |                        | 0.1         |                      | μA    |  |

| Control Signals DI, CLK, FR,            |                       |                                              |                        |             |                      |       |  |

| RES1,RES2                               |                       |                                              |                        |             |                      |       |  |

| Input leakage                           | I <sub>IN</sub>       | V <sub>DD1,2</sub> or V <sub>SS</sub>        | -1                     |             | 1                    | μΑ    |  |

| Input capacitance                       | C <sub>IN</sub>       | at $T_A = 25 ^{\circ}\text{C}$               |                        | 8           |                      | pF    |  |

| Low level input voltage                 | V <sub>IL</sub>       |                                              | 0                      |             | $0.3\ V_{DD1,2}$     | V     |  |

| High level input voltage                | V <sub>IH</sub>       |                                              | 0.7 V <sub>DD1,2</sub> |             | $V_{\mathrm{DD1,2}}$ | V     |  |

| DC output component                     | ± VDC                 | See table 4                                  |                        | 30          | 100                  | mV    |  |

| V <sub>LCD</sub> (internally generated) | V <sub>LCD</sub>      | See note 4)                                  |                        | 6.15        |                      |       |  |

| $V_{LCD}$                               | V <sub>LCD</sub>      | See note 5)                                  |                        | 3.15 - 7.09 |                      | V     |  |

|                                         | V <sub>LCD</sub> step |                                              |                        | 62.5        |                      | mV    |  |

$<sup>^{1)}</sup>$  All outputs open, DI and CLK at  $V_{\text{SS}}$ , mux ratio = 24, checker pattern.

### **DC Output Component**

| Output        | Frame | Logic Data | Measured*                         | Guaranteed                                     |

|---------------|-------|------------|-----------------------------------|------------------------------------------------|

| Row Driver    | n     | OL         | V <sub>LCD</sub> - V <sub>1</sub> | $V_1 = 0.83 \times V_{LCD} \pm 100 \text{ mV}$ |

|               | n + 1 | OL         | V <sub>4</sub> - V <sub>SS</sub>  | $V_2 = 0.66 \times V_{LCD} \pm 100 \text{ mV}$ |

| Column Driver | n     | OL         | V <sub>LCD</sub> - V <sub>2</sub> | $V_3 = 0.34 \times V_{LCD} \pm 100 \text{ mV}$ |

|               | n + 1 | OL         | V <sub>3</sub> - V <sub>SS</sub>  | $V_4 = 0.17 \times V_{LCD} \pm 100 \text{ mV}$ |

\*

$$V_X = V_X (load = +1 \mu A) + V_X (load = -1 \mu A)$$

, mux 24 or 25 programmed,  $V_{LCD} = 6 \text{ V}$ ,  $T_A = 25 \, ^{\circ}\text{C}$ .

Table 4

Table 3

Test is performed for multiplex rate = 25. All multiplex rate  $\neq$  25 are guaranteed by design. If multiplex rate  $\neq$  25, test will be performed on request.

$<sup>^{2)}</sup>$  All outputs open, DI at  $V_{SS}$ ,  $f_{CLK}=1$  MHz, mux ratio = 24, checker pattern.

<sup>&</sup>lt;sup>3)</sup> DI and CLK at V<sub>SS</sub>, checker pattern, mux ratio = 8.

$<sup>^{4)}</sup>$  Initialization bits 18 to 23 = 110000 and initialization bits 10, 11 = 00; laser trimming on request.

$<sup>^{5)}</sup>$  Initialization bits 18 to 23 = 000000/111111.

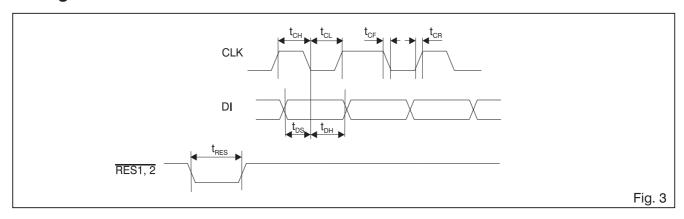

Timing Characteristics  $V_{DD1} = V_{DD2} = 2 \ to \ 3 \ V, \ V_{HV} = 2.5 \ to \ 5 \ V, \ and \ T_A = -40 \ ^{\circ}C \ to \ +85 \ ^{\circ}C$

| Parameter                     | Symbol             | Test Conditions | Min. | Тур. | Max. | Units |

|-------------------------------|--------------------|-----------------|------|------|------|-------|

| Clock high pulse width        | t <sub>CH</sub>    |                 | 70   |      |      | ns    |

| Clock low pulse width         | t <sub>CL</sub>    |                 | 110  |      |      | ns    |

| Clock period                  | t <sub>per</sub>   |                 | 550  |      |      | ns    |

| Reset 1 pulse width           | t <sub>RES1</sub>  |                 | 10   |      |      | μs    |

| Reset 2 pulse width           | t <sub>RES2</sub>  |                 | 130  |      |      | ns    |

| Clock and FR rise time        | t <sub>CR</sub>    |                 |      |      | 200  | ns    |

| Clock and FR fall time        | t <sub>CF</sub>    |                 |      |      | 200  | ns    |

| Data input setup time         | t <sub>DS</sub>    |                 | 20   |      |      | ns    |

| Data input hold time          | t <sub>DH</sub>    |                 | 260  |      |      | ns    |

| FR (internal frame frequency) | f <sub>FR</sub> 1) |                 |      | 75   |      | Hz    |

<sup>1)</sup> EM6124 (n), FR = n times the desired LCD refresh rate where n is the EM6124 mux mode number; laser trimming on request.

Table 5a

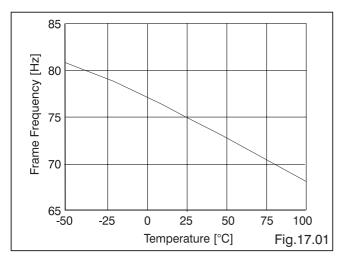

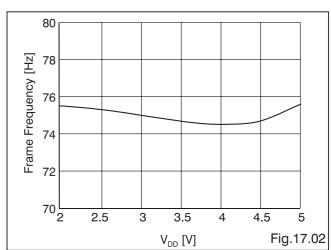

See Fig. 17.01 and 17.02 for more details concerning the frame frequency

$V_{DD1} = V_{DD2} = 3$  to 5 V,  $V_{HV} = 2.5$  to 5 V, and  $T_A =$  -40 °C to +85 °C

| Parameter                     | Symbol                        | Test Conditions | Min. | Тур. | Max. | Units |

|-------------------------------|-------------------------------|-----------------|------|------|------|-------|

| Clock high pulse width        | t <sub>CH</sub>               |                 | 50   |      |      | ns    |

| Clock low pulse width         | t <sub>CL</sub>               |                 | 55   |      |      | ns    |

| Clock period                  | t <sub>per</sub>              |                 | 350  |      |      | ns    |

| Reset 1 pulse width           | t <sub>RES1</sub>             |                 | 10   |      |      | μs    |

| Reset 2 pulse width           | t <sub>RES2</sub>             |                 | 80   |      |      | ns    |

| Clock and FR rise time        | t <sub>CR</sub>               |                 |      |      | 200  | ns    |

| Clock and FR fall time        | t <sub>CF</sub>               |                 |      |      | 200  | ns    |

| Data input setup time         | t <sub>DS</sub>               |                 | 20   |      |      | ns    |

| Data input hold time          | t <sub>DH</sub>               |                 | 140  |      |      | ns    |

| FR (internal frame frequency) | f <sub>FR</sub> <sup>1)</sup> |                 |      | 75   |      | Hz    |

<sup>&</sup>lt;sup>1)</sup> EM6124 (n), FR = n times the desired LCD refresh rate where n is the EM6124 mux mode number; laser trimming on request.

Table 5b

### **Timing Waveforms**

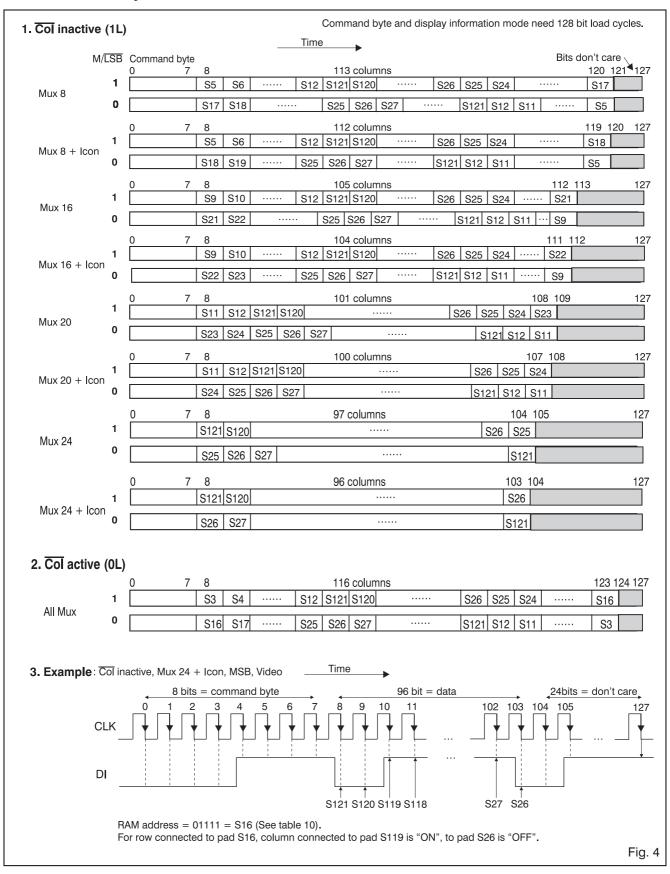

### 1 Bit Interface Description

This 1 bit interface is very simple to use. There are three modes to load data into the EM6124.

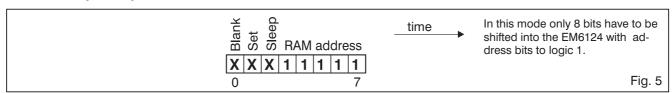

### Command byte only mode

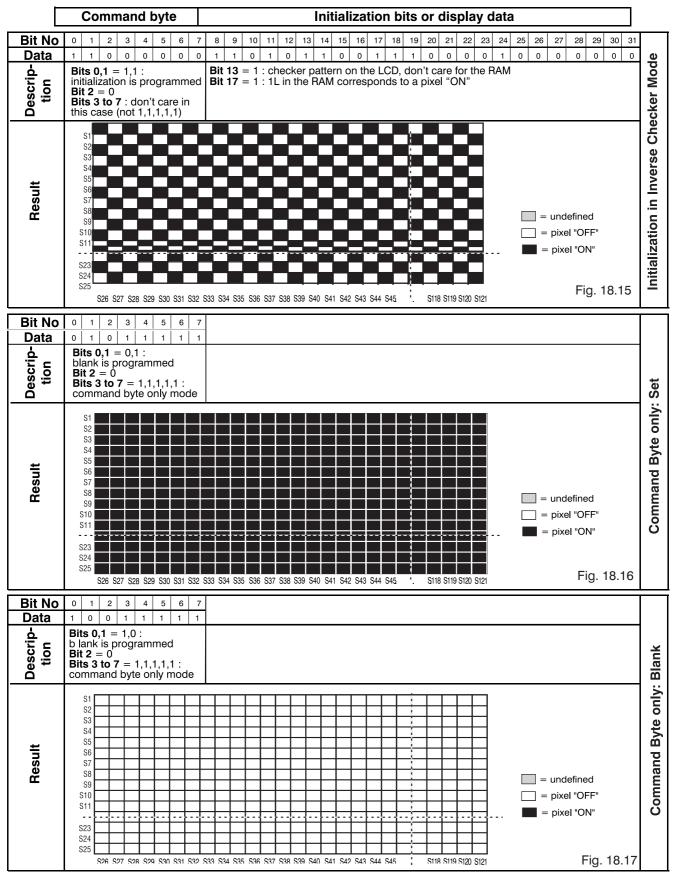

To validate this mode, 8 bits must be shifted with bit 3 to bit 7 setted to 1L. This mode is used for blank, set or sleep mode functions.

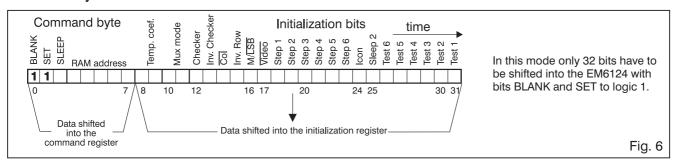

#### Command byte and initialization mode

To validate this mode, 32 bits must be shifted with bit 0 and bit 1 setted to 1L. Bit 2 (sleep) can be active or inactive. Bit 3 to bit 7 (RAM address) can be in any state but it is important that they are not all simultaneously setted to 1L, otherwise the chip will be in command byte only mode.

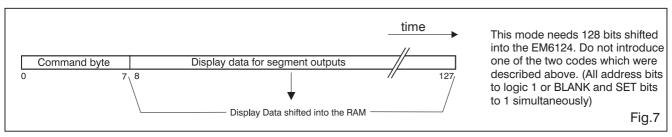

#### Command byte and display information mode

To validate this mode, 128 bits must be shifted, eight first bits are for command byte, all the other are RAM data depending of col bit mode and multiplex ratio. There are also x bits don't care in each loading depending on the programmation of the chip (see Fig. 4 for more details). In each RAM's data loading, the command byte has to be introduced for the RAM address. Before loading any data into the RAM the chip has to be initialized.

#### **Command Byte**

|       | Commmand Bits 0 to 7 |       |                   |  |  |  |  |  |  |  |  |  |

|-------|----------------------|-------|-------------------|--|--|--|--|--|--|--|--|--|

| 0     | 0 1 2 3 4 5 6 7      |       |                   |  |  |  |  |  |  |  |  |  |

| Blank | Set                  | Sleep | Sleep RAM address |  |  |  |  |  |  |  |  |  |

Table 6

Cmdbit 0: Blank bit forces all column outputs off.

Cmdbit 1: Set bit forces all column output on.

Note: If bit 0 and bit 1 are both to 1L, the chip will be in initialization mode. See remarks below.

$\label{eq:condition} \textbf{Cmdbit 2: Sleep mode bit, $\underline{sto}$ ps the voltage booster and the internal oscillator, active bit <math>\overline{col}$  forces all outputs to  $V_{ss}$ .

Cmdbits 3-7: RAM address bits. See table 6.

If Cmdbits 3-7 are set to 1L, EM6124 is in Cmd byte only mode.

### Initialization Bits

|                              | Initialization Bits 8 to 15  |      |          |      |       |        |      |         |     |         |  |        |        |        |        |        |

|------------------------------|------------------------------|------|----------|------|-------|--------|------|---------|-----|---------|--|--------|--------|--------|--------|--------|

| 8                            | 9                            | 10 1 |          | 1 12 |       | 2      |      | 13 14   |     | 15      |  |        |        |        |        |        |

| Mux M                        | lode                         | Tem  | p. Coeff | f.   | Chec  | ker    | Inv. | Checker | Col | Inv.Row |  |        |        |        |        |        |

| Initialization Bits 16 to 23 |                              |      |          |      |       |        |      |         |     |         |  |        |        |        |        |        |

| 16                           | 17                           | 7    | 18       |      | 19    | 2      | 0    | 21      | 22  | 23      |  |        |        |        |        |        |

| M/LSB                        | Vid                          | eo : | Step 1   | St   | ep 2  | Step 3 |      | Step 3  |     | Step 3  |  | Step 3 |        | Step 4 | Step 5 | Step 6 |

|                              | Initialization Bits 24 to 31 |      |          |      |       |        |      |         |     |         |  |        |        |        |        |        |

| 24                           | 2                            | 5    | 26       |      | 27    | 28     |      | 29      | 30  | 31      |  |        |        |        |        |        |

| Icon                         | Slee                         | p 2  | Test 6   | Te   | est 5 | Test 4 |      | Test 4  |     | Test 4  |  | Test 3 | Test 2 | Test 1 |        |        |

Table 7

| Mu | Mux ratio (Init. bit 8, 9) |          |  |  |  |  |  |  |  |  |

|----|----------------------------|----------|--|--|--|--|--|--|--|--|

| 8  | 9                          | mux mode |  |  |  |  |  |  |  |  |

| 0  | 0                          | 8        |  |  |  |  |  |  |  |  |

| 0  | 1                          | 16       |  |  |  |  |  |  |  |  |

| 1  | 0                          | 20       |  |  |  |  |  |  |  |  |

| 1  | 1                          | 24       |  |  |  |  |  |  |  |  |

Table 8

**Init.bit 8-9:** Mux mode bits. The multiplex ratio is selected by these two bits. Table 8 shows the corresponding values.

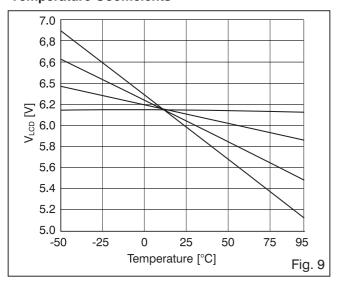

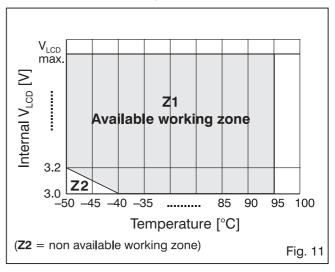

Init.bit 10-11: V<sub>LCD</sub> temperature coefficient is selected by these two bits. Table 11 shows the corresponding values.

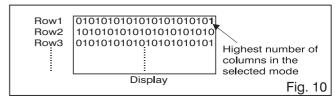

Init.bit 12: Checker bit gives the possibility to force all outputs segments in checked form (see Fig. 10 and Fig. 18.14).

Init.bit 13: Inverse Checker bit gives the possibility to force all outputs segments in inverse checked form (see Fig. 10 and Fig. 18.15).

Init.bit 14: Col bit configures the EM6124 on row and column driver or column driver only. In this mode the frame frequency must be external.

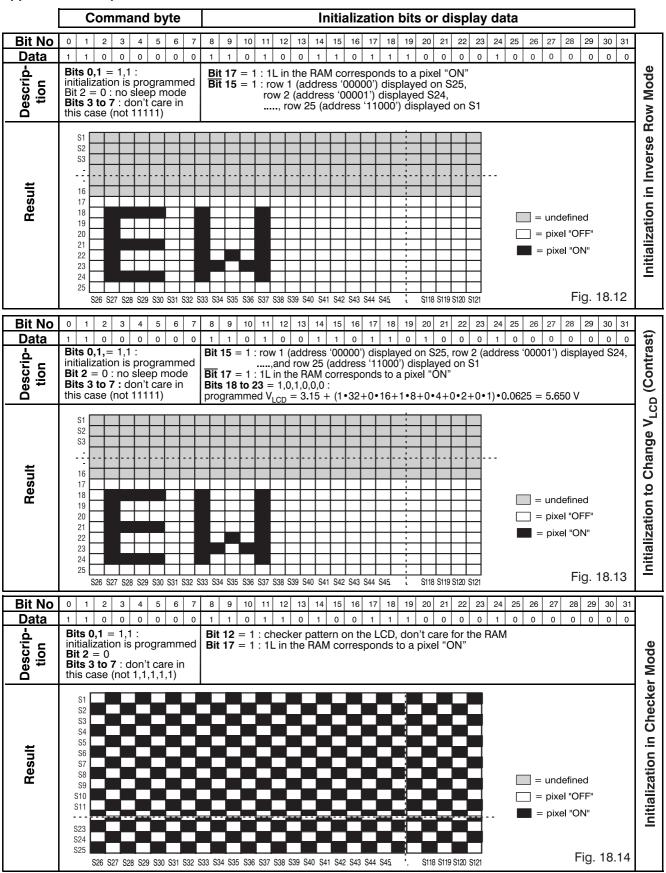

**Init.bit 15**: Row inversion, possibility to inverse the order of the row outputs (see Table 10 and Fig. 18.12).

Init.bit 16: M/LSB, possibility to inverse the order loading for RAM data (see Fig. 4).

Init.bit 17: Video bit, possibility to inverse the content of the RAM. All the 0L pass to 1L and all the 1L pass to 0L (see Fig. 18.11).

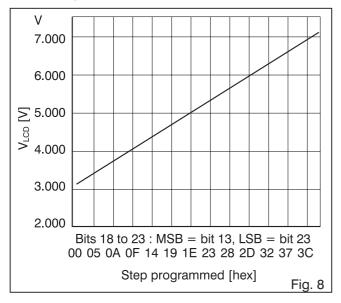

Init.bit 18-23: V<sub>LCD</sub> 64 steps programmation bits. See Fig. 8. Bit 18 (step 1) for MSB and bit 23 (step 6) for LSB.

Init.bit 24: Icon bit adds one line more to the selected mux mode ratio for icon segments outputs.

Init.bit 25: Sleep 2. Set all outputs at Vss.

Init.bit 26-31: Must be setted to 0L.

#### Reset 1

**Power-up**: Must be followed by a RESET cycle. After the reset 1 pulse the LCD controller driver is set to the following status:

- All outputs at V<sub>ss</sub>

- Blank & Set (cmdbits 0,1) = 0L

- Sleep mode (cmdbit 2) = 0L

- RAM address (cmdbits 3 to 7) = 0L

- Multiplex ratio (init.bits 8, 9) = 0L

- Temperature coefficient (init.bits 10,11) = 0L

- Checker & Inv.Checker (init.bits 12, 13) = 0L

- Col Mode (init.bit 14) = 1L

- Inv. Row (init.bit 15) = 0L

- $M/\overline{LSB}$  (init.bit 16) = 1L

- Video (init.bit 17) = 1L

- $V_{LCD}$  step (init.bits 18 to 23) = 0L

- Icon (init.bit 24) = 0L

- Sleep 2 (init.bit 25) = 1L

- The content of the RAM remains unchanged An initialization should take place after reset (32 bits sent).

### **Pin Assignment**

| Name             | Function                            |

|------------------|-------------------------------------|

| S1S121           | LCD outputs, see Fig.4              |

| FR               | AC I/O signal for LCD driver output |

| DI               | Serial data input                   |

| DO               | Serial data output                  |

| CLK              | Data clock input                    |

| RES1             | General reset                       |

| RES2             | Reset the serial interface counter  |

| V <sub>LCD</sub> | Internal generated voltage output   |

| $V_{DD1}$        | Power supply for logic              |

| $V_{DD2}$        | Power supply for analogic           |

| $V_{HV}$         | Power supply for high voltage       |

| V <sub>SS</sub>  | Supply GND                          |

Table 9

### **Data Transfer Cycle**

# **Output Row Assignments**

|     |   |       |      |     |     |          |             |          |            |          |            |          | Mux        | Mode     |            |                    |            |                                                  |            |                    |            |

|-----|---|-------|------|-----|-----|----------|-------------|----------|------------|----------|------------|----------|------------|----------|------------|--------------------|------------|--------------------------------------------------|------------|--------------------|------------|

| Row |   | RAM   | Addr | ess |     | Mu       | Mux 8 Mux 8 |          | I I I      |          |            | Mux 20   |            |          | x 20       | Mu                 | x 24       | Mu                                               |            |                    |            |

|     |   |       |      |     |     | Inv      | Row         |          | con<br>Row | Inv      | Row        |          | con<br>Row | Inv      | Row        | + Icon<br>Inv. Row |            | Inv. Row                                         |            | + Icon<br>Inv. Row |            |

|     |   |       |      |     |     |          |             |          |            |          | _          |          |            |          |            |                    |            | <del>                                     </del> |            | <del></del>        |            |

|     |   | Bit 4 |      |     |     | 0        | 1           | 0        | 1          | 0        | 1          | 0        | 1          | 0        | 1          | 0                  | 1          | 0                                                | 1          | 0                  | 1          |

| 1   | 0 | 0     | 0    | 0   | 0   | S1<br>S2 | S16         | S1<br>S2 | S17        | S1<br>S2 | S20        | S1<br>S2 | S21        | S1<br>S2 | S22        | S1<br>S2           | S23        | S1<br>S2                                         | S24        | S1<br>S2           | S25        |

| 2 3 | 0 | 0     | 0    | 0   | 0   | S2<br>S3 | S15<br>S14  | S2<br>S3 | S16<br>S15 | S2<br>S3 | S19<br>S18 | S2<br>S3 | S20<br>S19 | S2<br>S3 | S21<br>S20 | S2<br>S3           | S22<br>S21 | S2<br>S3                                         | S23<br>S22 | S2<br>S3           | S24<br>S23 |

| 4   | 0 | 0     | 0    | 1   | 1   | S4       | S14         | S4       | S14        | S4       | S17        | S4       | S19        | S4       | S20        | S4                 | S21        | S4                                               | S22        | S4                 | S23        |

| 5   | 0 | 0     | 1    | 0   | 0   | S13      | S4          | S13      | S14        | S5       | S17        | S5       | S17        | S5       | S18        | S5                 | S19        | S5                                               | S21        | S5                 | S21        |

| 6   | 0 | 0     | 1    | 0   | 1 1 | S14      | S3          | S14      | S4         | S6       | S15        | S6       | S16        | S6       | S17        | S6                 | S18        | S6                                               | S19        | S6                 | S20        |

| 7   | 0 | 0     | 1    | 1   | انا | S15      | S2          | S15      | S3         | S7       | S14        | S7       | S15        | S7       | S16        | S7                 | S17        | S7                                               | S18        | S7                 | S19        |

| 8   | 0 | 0     | 1    | 1   | 1 1 | S16      | S1          | S16      | S2         | S8       | S13        | S8       | S14        | S8       | S15        | S8                 | S16        | S8                                               | S17        | S8                 | S18        |

| 9   | Ö | 1     | 0    | 0   | 0   | 0.0      |             | S17      | S1         | S13      | S8         | S13      | S13        | S9       | S14        | S9                 | S15        | S9                                               | S16        | S9                 | S17        |

| 10  | 0 | 1     | 0    | 0   | 1   |          |             |          |            | S14      | S7         | S14      | S8         | S10      | S13        | S10                | S14        | S10                                              | S15        | S10                | S16        |

| 11  | 0 | 1     | 0    | 1   | 0   |          |             |          |            | S15      | S6         | S15      | S7         | S13      | S10        | S13                | S13        | S11                                              | S14        | S11                | S15        |

| 12  | 0 | 1     | 0    | 1   | 1   |          |             |          |            | S16      | S5         | S16      | S6         | S14      | S9         | S14                | S10        | S12                                              | S13        | S12                | S14        |

| 13  | 0 | 1     | 1    | 0   | 0   |          |             |          |            | S17      | S4         | S17      | S5         | S15      | S8         | S15                | S9         | S13                                              | S12        | S13                | S13        |

| 14  | 0 | 1     | 1    | 0   | 1   |          |             |          |            | S18      | S3         | S18      | S4         | S16      | S7         | S16                | S8         | S14                                              | S11        | S14                | S12        |

| 15  | 0 | 1     | 1    | 1   | 0   |          |             |          |            | S19      | S2         | S19      | S3         | S17      | S6         | S17                | S7         | S15                                              | S10        | S15                | S11        |

| 16  | 0 | 1     | 1    | 1   | 1   |          |             |          |            | S20      | S1         | S20      | S2         | S18      | S5         | S18                | S6         | S16                                              | S9         | S16                | S10        |

| 17  | 1 | 0     | 0    | 0   | 0   |          |             |          |            |          |            | S21      | S1         | S19      | S4         | S19                | S5         | S17                                              | S8         | S17                | S9         |

| 18  | 1 | 0     | 0    | 0   | 1   |          |             |          |            |          |            |          |            | S20      | S3         | S20                | S4         | S18                                              | S7         | S18                | S8         |

| 19  | 1 | 0     | 0    | 1   | 0   |          |             |          |            |          |            |          |            | S21      | S2         | S21                | S3         | S19                                              | S6         | S19                | S7         |

| 20  | 1 | 0     | 0    | 1   | 1   |          |             |          |            |          |            |          |            | S22      | S1         | S22                | S2         | S20                                              | S5         | S20                | S6         |

| 21  | 1 | 0     | 1    | 0   | 0   |          |             |          |            |          |            |          |            |          |            | S23                | S1         | S21                                              | S4         | S21                | S5         |

| 22  | ] | 0     | 1    | 0   | 1   |          |             |          |            |          |            |          |            |          |            |                    |            | S22                                              | S3         | S22                | S4         |

| 23  | 1 | 0     | 1    | 1   | 0   |          |             |          |            |          |            |          |            |          |            |                    |            | S23                                              | S2         | S23                | S3         |

| 24  | 1 | 0     | 1    | 1   | 1   |          |             |          |            |          |            |          |            |          |            |                    |            | S24                                              | S1         | S24                | S2<br>S1   |

| 25  |   |       | 0    | 0   | 0   |          |             |          |            |          |            |          |            |          |            |                    |            |                                                  |            | S25                | ১।         |

Table 10

### **Command Byte Only Mode**

### **Command Byte and Initialization Mode**

### **Command Byte and Display Information Mode**

### Typical V<sub>LCD</sub> Programming

#### **Temperature Control**

Due to the temperature dependency of liquid cristals viscosity the LCD controlling voltage  $V_{\text{LCD}}$  must be increased for lower temperatures to maintain optimal contrast. The EM6124 is available with 4 different temperature coefficients (see Fig. 9). The coefficient is selected by 2 bits in the initialization code TC bits 10 and 11. Table 11 shows the typical values of the different temperature coefficients. They are proportional to the programmed  $V_{\text{LCD}}$ .

#### **Typical Values of the Temperature Coefficients**

|                | <u> </u>                  |       |  |  |  |

|----------------|---------------------------|-------|--|--|--|

| Bit 10, Bit 11 | Value                     | Unit  |  |  |  |

| 0 0            | - 0.02 x V <sub>LCD</sub> | mV/°C |  |  |  |

| 0 1            | - 0.52 x V <sub>LCD</sub> | mV/°C |  |  |  |

| 1 0            | - 1.16 x V <sub>LCD</sub> | mV/°C |  |  |  |

| 11             | - 1.82 x V <sub>LCD</sub> | mV/°C |  |  |  |

Table 11

#### **Temperature Coefficients**

#### **Checker and Checker Inverse**

A fast check display can be easily created setting initialization bits 12 and 13 (called "Checker" and "Inv. Checker"). The display is completely checked with only 2 initialization sequences, one "Checker" and one "Inv. Checker". For Checker, the pattern fills the display with alternately ON and OFF pixels as shown in Fig. 10. For Inv. Checker, everything is inverted (see Fig.18.14 and 18.15).

#### **Pattern of Checker Mode**

### Internally Generated V<sub>LCD</sub> versus Temperature

### **Display Functions**

| Bit                            | State                         |                                        |  |

|--------------------------------|-------------------------------|----------------------------------------|--|

|                                | Logic 0                       | Logic 1                                |  |

| 8 - 9: Mux Mode                | See table 8                   |                                        |  |

| 10 -11:Temp.Coeff.             | See table 11                  |                                        |  |

| 12: Checker                    | Inactive                      | Chess display                          |  |

| 13: Inv. Checker               | Inactive                      | Inverse chess display                  |  |

| 14: <del>Col</del>             | Colum driver only             | Row and column driver                  |  |

| 15: Inv. Row                   | Increment rows Decrement rows |                                        |  |

|                                | (example for mux 24:          | (example for mux 24:                   |  |

|                                | row 1, 2, 3,, 24, 1, 2,)      | row 24, 23, 22,, 2, 1, 24, 23,)        |  |

| 16: M/ <del>LSB</del>          | Loading in LSB mode           | Loading in MSB mode                    |  |

| 17: Video                      | Inverse content of RAM        | Inactive                               |  |

| 18 - 23: V <sub>LCD</sub> step | See Fig. 8                    |                                        |  |

| 24: Icon                       | Inactive                      | Add one line more to seledted mux mode |  |

| 25: Sleep                      | Inactive                      | All outputs at V <sub>ss</sub>         |  |

| 26 - 31:                       | Must be at 0L                 |                                        |  |

Table 12

### **Block Diagram**

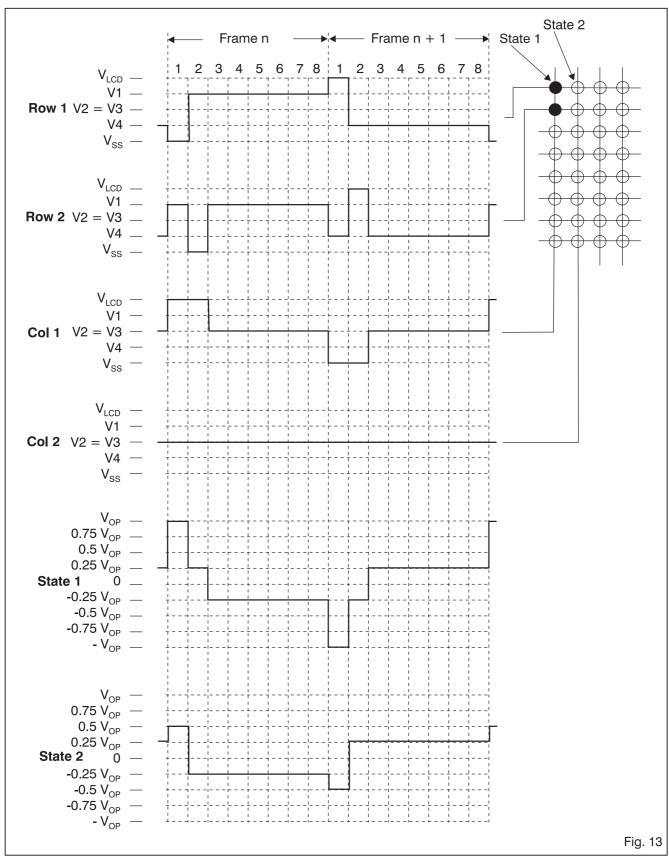

# **LCD Voltage Bias Levels**

| LCD Drive<br>Type               | LCD Bias<br>Configuration | V <sub>OP</sub><br>V <sub>OFF</sub> (rms)                         | V <sub>ON</sub> (rms)<br>V <sub>OFF</sub> (rms) |

|---------------------------------|---------------------------|-------------------------------------------------------------------|-------------------------------------------------|

| EM6124 (24)<br>n=24<br>1:24 MUX | 6 Levels                  | $\sqrt{\frac{\sqrt{n} (\sqrt{n} + 1)^2}{2(\sqrt{n} - 1)}} = 4.68$ | $\sqrt{\frac{\sqrt{n}+1}{\sqrt{n}-1}} = 1.230$  |

| EM6124 (20)<br>n=20<br>1:20 MUX | 6 Levels                  | $\sqrt{\frac{\sqrt{n}(\sqrt{n}+1)^2}{2(\sqrt{n}-1)}} = 4.39$      | $\sqrt{\frac{\sqrt{n+1}}{\sqrt{n-1}}} = 1.255$  |

| EM6124 (16)<br>n=16<br>1:16 MUX | 1/5 Bias<br>6 Levels      | $\sqrt{\frac{\sqrt{n}(\sqrt{n}+1)^2}{2(\sqrt{n}-1)}^2} = 4.08$    | $\sqrt{\frac{\sqrt{n+1}}{\sqrt{n-1}}} = 1.291$  |

| EM6124 (8)<br>n=8<br>1:8 MUX    | 1/4 Bias<br>5 Levels      | $\frac{4}{\sqrt{1+\frac{3}{n}}}=3.4$                              | $\sqrt{\frac{n-15}{n+3}} = 1.446$               |

Table 13

# **Optimum LCD Bias Voltages**

| Multiplex<br>Rate | V <sub>LCD</sub> | V1    | V2    | V3    | V4    | V <sub>ss</sub> |

|-------------------|------------------|-------|-------|-------|-------|-----------------|

| 1:24              | 1                | 0.830 | 0.660 | 0.340 | 0.170 | 0               |

| 1:20              | 1                | 0.817 | 0.634 | 0.366 | 0.183 | 0               |

| 1:16              | 1                | 0.800 | 0.600 | 0.400 | 0.200 | 0               |

| 1:8               | 1                | 0.750 | 0.500 | 0.250 | -     | 0               |

$V_{LCD} > V1 > V2 > V3 > V4 > V_{SS}$

The values in the above table are given in reference to  $V_{\text{\tiny LCD}}\,$  e.g. 0.5 means 0.5 x  $V_{\text{\tiny LCD}}\,$

Table 14

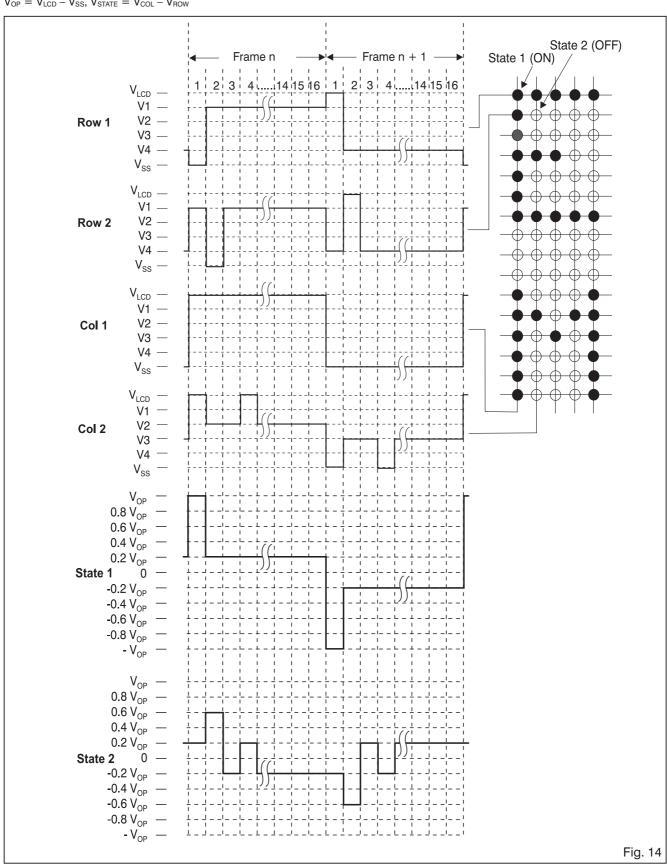

### Row and Column Multiplexing Waveform EM6124 (8)

$V_{\text{OP}} = V_{\text{LCD}} - V_{\text{SS}}, V_{\text{STATE}} = V_{\text{COL}} - V_{\text{ROW}}$

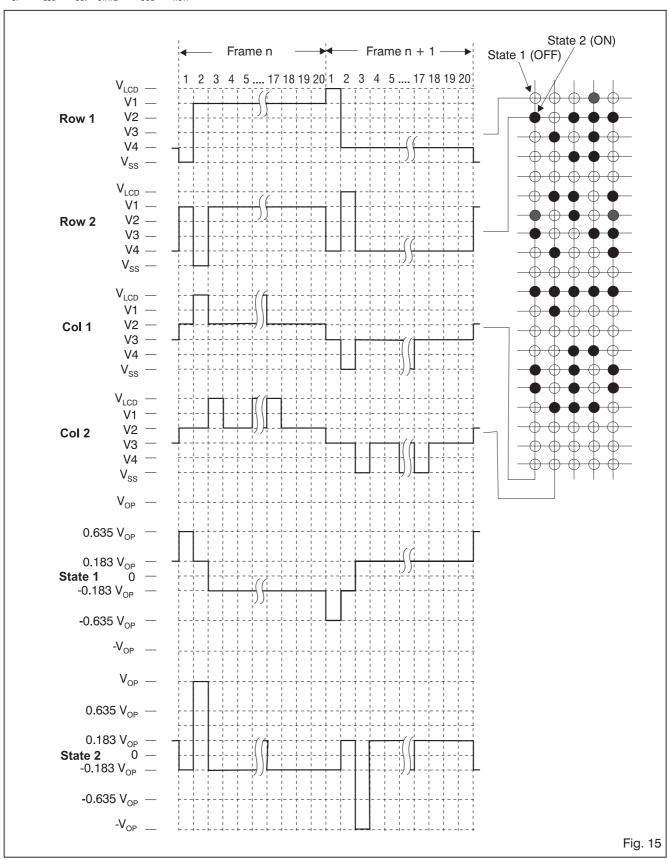

### Row and Column Multiplexing Waveform EM6124 (16)

$V_{OP} = V_{LCD} - V_{SS}, V_{STATE} = V_{COL} - V_{ROW}$

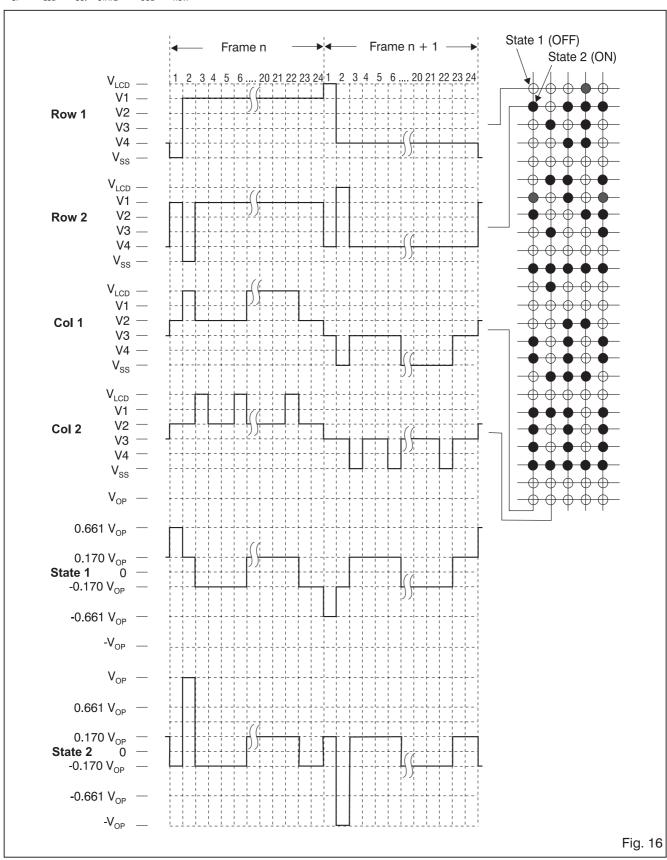

### Row and Column Multiplexing Waveform EM6124 (20)

$V_{\text{OP}} = V_{\text{LCD}} - V_{\text{SS}}, V_{\text{STATE}} = V_{\text{COL}} - V_{\text{ROW}}$

### Row and Column Multiplexing Waveform EM6124 (24)

$V_{OP} = V_{LCD} - V_{SS}, V_{STATE} = V_{COL} - V_{ROW}$

### **Functional Description**

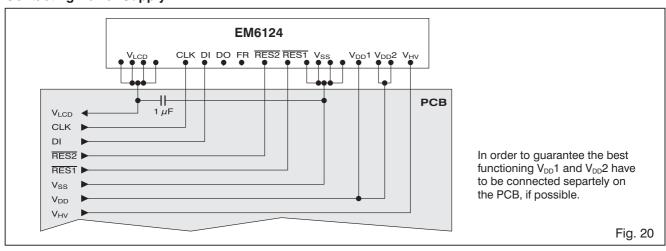

Supply Voltage  $V_{DD1}$ ,  $V_{DD2}$ ,  $VH_V$ ,  $V_{LCD}$ ,  $V_{SS}$ The voltage between  $V_{DD1}$  and  $V_{SS}$  is the supply voltage for the logic and the interface. The voltage between  $V_{\text{DD2}}$  and  $V_{\text{SS}}$  is the supply voltage for the analogic.  $V_{\text{DD1}}$  and  $V_{\text{DD2}}$ must be the same voltage and, in order to guarantee the best functioning,  $V_{\text{DD1}}$  and  $V_{\text{DD2}}$  have to be separately connected to the PCB (see Fig. 19). The voltage  $V_{LCD}$  is internally generated for the supply voltage of the LCD and is used for the generation of the internal LCD bias level. An external capacitor of 1 µF must be connected between  $V_{LCD}$  and  $V_{SS}$ . Table 15 shows the relationship between V1, V2, V3, V4 for a programmed multiplex rate. Note that V<sub>LCD</sub> > V1 > V2 > V3 > V $_{\rm SS}$  for the EM6124 8 mux programmed, and for the EM6124 16, 20, 24 mux programmed  $V_{LCD} > V1 > V2 > V3 > V4 > V_{SS}$ . The voltage between  $V_{\text{HV}}$  and  $V_{\text{SS}}$  is the supply voltage for high voltage part of the EM6124. An external V<sub>LCD</sub> may also be used by connecting a power supply and programming a lower V<sub>LCD</sub> voltage during initialization.

#### **Data Input**

The data input pin, DI, is used to load serial data into the EM6124. The normal serial data word length is 128 bits. 32 and 8 bits are also available in a special mode (see 1 Bit Interface Description). The command byte is loaded first and then the segment data bits (see Fig. 4).

### **RES1** Input

Reset is accomplished by applying an external RES1 pulse (active low). When reset occurs within the specified time, all internal register are reset however the content of the RAM is still unchanged. The state after reset is described on page 4.

#### **RES2** Input

Reset is accomplished by applying an external RES2 pulse (active low). When reset occurs within the specified time, the internal counter for serial interface is reset. The counter of the serial interface for data inputs is ready for a new loading of data. This reset 2 does not change the content of the RAM neither the content of the command and the initialization bits. To avoid trouble in case of software interrupt of the MPU during data loading, this function can be used.

### Power-Up

On power up the data in the shift registers, the display RAM, the sequencer driving the 8/16/20/24 rows and the 121 bit display latches are undefined.

#### **CLK Input**

The clock input is used to clock the DI serial data into the EM6124.

### FR Input / Output

The frame frequency is realized by an internal oscillator with a typical value of 75 Hz. The internal row frequency changes with the number of rows ( $F_{row} = 75 x n$ , where n = 8, 16, 20, 24). When bit 14 ( $\overline{\text{Col}}$ ) is inactive (active low), the frame frequency is given by the internal oscillator. This frequency can be measured on the I/O FR. When bit 14 (Col) is active (active low), the frame frequency is external then the frequency is given directly by the FR input to the row and column driver (see Fig. 16 and 17 for more details concerning the frame frequency).

#### **Driver Outputs S1 to S116**

There are 121 LCD driver outputs on the EM6124. The output assignments depend on the chosen mux mode ratio (init. bits 8, 9) and the Col function (init. bit 14).

When init. bit 14 (Col) is active, all 116 outputs function as column drivers. Table "Output Row Assignments" and Fig. 4 describe exactly the correspondent data to the output of the chip. There is one to one relationship between the display RAM and the LCD driver outputs. Each pixel (segment) driven by the EM6124 on the LCD has a display RAM bit which corresponds to it. Setting the bit turns the pixel "on" and Clearing it turns "off".

For chip-on-glass better performances can be obtained by covering the backside of the chip.

#### Typical Frame Frequency at $V_{DD} = 3 \text{ V}$

#### Typical Frame Frequency at $T_A = 25$ °C

### **Application Example**

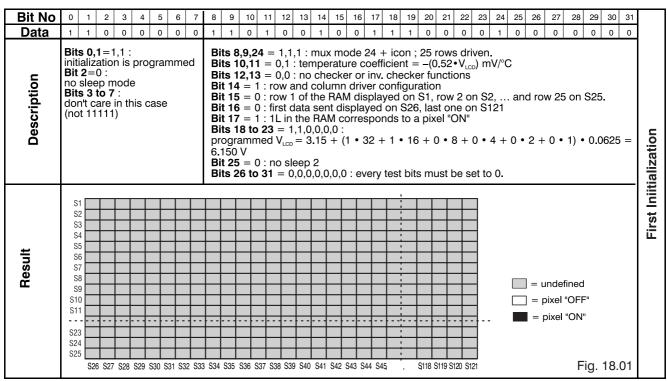

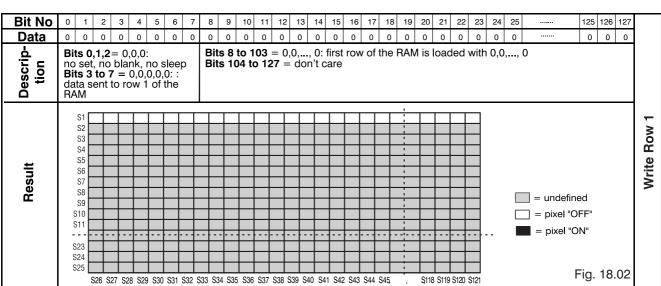

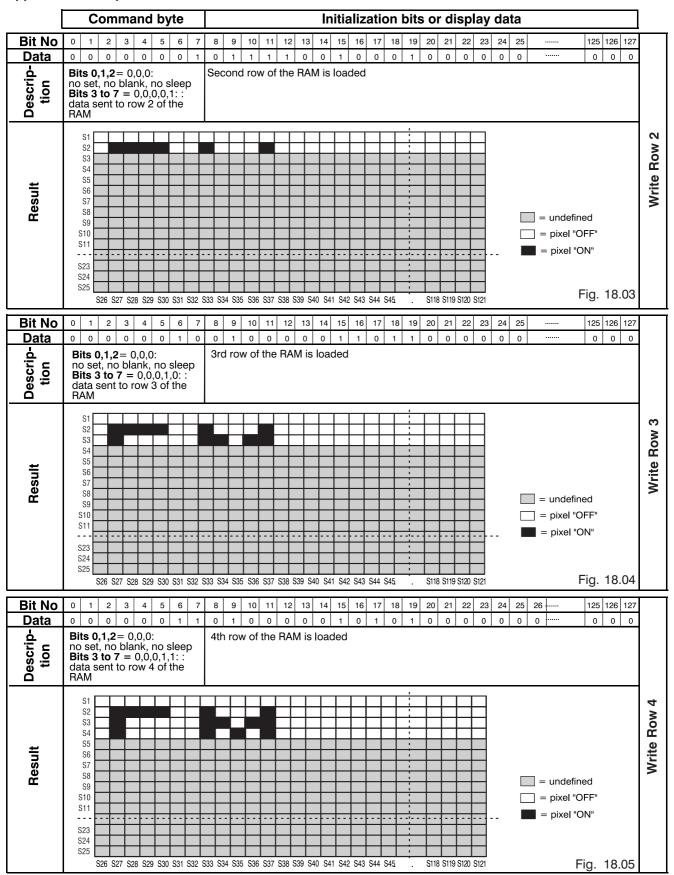

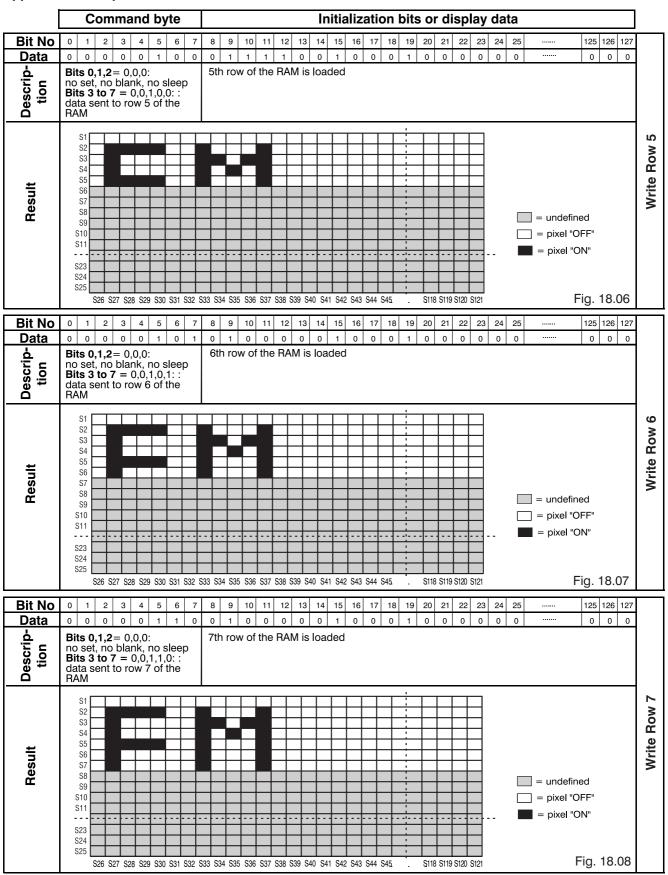

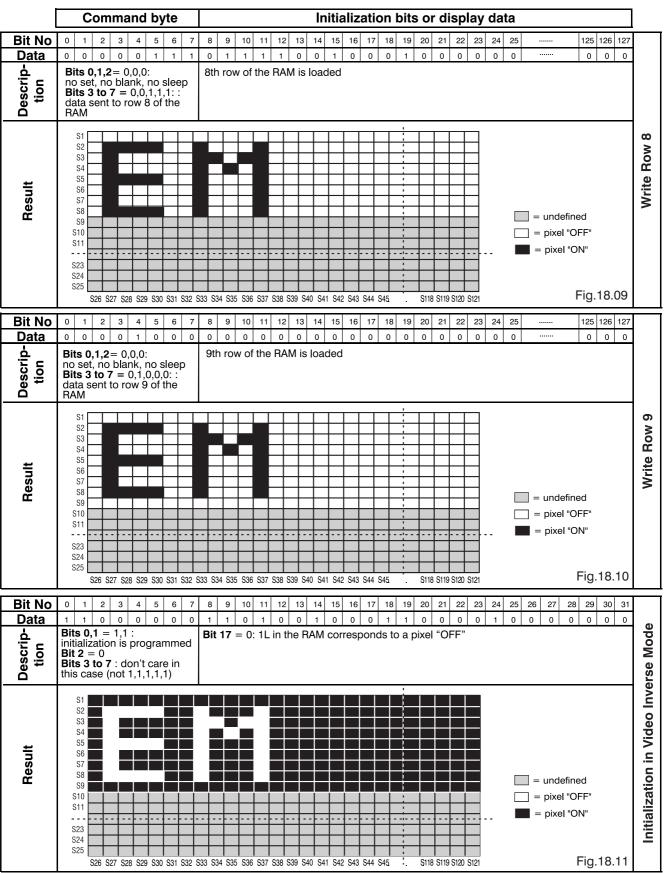

These tables/figures show how to use the EM6124 with a given initialization. Rows "Data" show the logical value to affect pad DI for each falling edge of pad CLK. A reset cycle pad RES1 at OL is required before sending data.

| Command byte | Initialization bits or display data |

|--------------|-------------------------------------|

|--------------|-------------------------------------|

Table 15 (continued on next pages)

### **Applications**

Two EM6124 work in parallel to drive up to 50 rows x 96 columns or 25 rows x 212 columns as below

effective bias level source impedance is the parallel combination of the total number of drivers. \*  $V_{\text{DD1}}$  and  $V_{\text{DD2}}$  have been connected together.

Fig. 19

### **Contacting Power Supply**

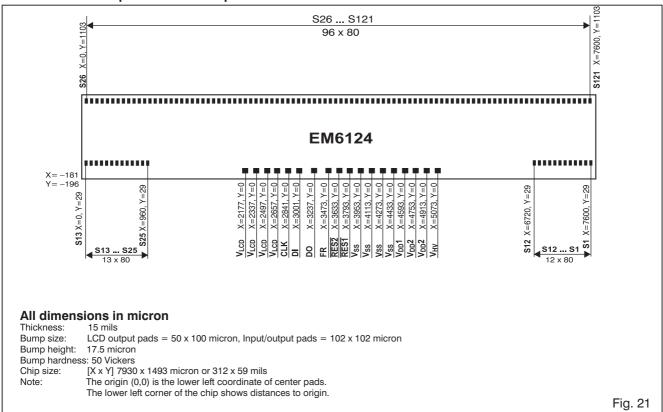

### **Dimensions of Chip Form and Bumped Die**

### **Ordering Information**

When ordering, please specify the complete Part Number

| Part Number | Die Form                              | Bumping         |

|-------------|---------------------------------------|-----------------|

| EM6124WP15E | Die in waffle pack, 15 mils thickness | With gold bumps |

For other delivery form in die (with or without bumps), please contact EM Microelectronic-Marin S.A. Minimum order quantity might apply.

EM Microelectronic-Marin SA cannot assume any responsibility for use of any circuitry described other than entirely embodied in an EM Microelectronic-Marin SA product. EM Microelectronic-Marin SA reserves the right to change the circuitry and specifications without notice at any time. You are strongly urged to ensure that the information given has not been superseded by a more up-to-date version.

E. & O.E. Printed in Switzerland, Th

© 2002 EM Microelectronic-Marin SA, 03/02, Vers. D/436