# International **ICR** Rectifier

PRELIMINARY

Data Sheet No. PD60303

IRS20955(S)PbF

## PROTECTED DIGITAL AUDIO DRIVER

### Features

- Floating PWM input enables easy half-bridge • implementation

- Programmable bidirectional over-current protection with self-reset function

- Programmable preset deadtime for improved THD • performances

- High noise immunity •

- $\pm 100$  V ratings deliver up to 500 W in output power •

- 3.3 V/5 V logic compatible input •

- Operates up to 800 kHz •

- **RoHS** compliant

### Description

The IRS20955 is a high voltage, high speed MOSFET driver with a floating PWM input designed for Class D audio amplifier applications.

Bi-directional current sensing detects over-current conditions during positive and negative load currents without any external shunt resistors. A built-in protection control block provides a secure protection sequence against overcurrent conditions and a programmable reset timer.

The internal deadtime generation block enables accurate gate switching and optimum deadtime setting for better audio performance, such as lower THD and lower audio noise floor.

### **Typical Connection**

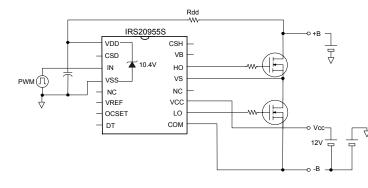

#### IRS20955 (S) ססע CSH CSD VB IN HO vss VS PWM(Л) Speaker NC NC VCC VREF OCSET LO (Please refer to Lead COM DT Assignments for correct Vcc pin configuration. This 12V diagram shows electrical connections •о -В

## **Product Summary**

| V <sub>OFFSET</sub> (max)   | ± 100 V             |       |  |

|-----------------------------|---------------------|-------|--|

| Gate driver                 | I <sub>o+</sub>     | 1.0 A |  |

| Gale unver                  | l <sub>o-</sub>     | 1.2 A |  |

| Selectable deadtime         | Selectable deadtime |       |  |

| Propagation delay           | 90 ns               |       |  |

| OC protection delay         | 500 ns (max)        |       |  |

| Shutdown propagati<br>delay | 250 ns (max)        |       |  |

Package

only)

### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to  $V_{SS}$ ; all currents are defined positive into any lead. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol                | Definition                                                        | Min.                    | Max.                 | Units |

|-----------------------|-------------------------------------------------------------------|-------------------------|----------------------|-------|

| VB                    | High-side floating supply voltage                                 | -0.3                    | 220                  |       |

| Vs                    | High-side floating supply voltage (Note1)                         | V <sub>B</sub> -20      | V <sub>B</sub> +0.3  |       |

| V <sub>HO</sub>       | High-side floating output voltage                                 | Vs-0.3                  | V <sub>B</sub> +0.3  |       |

| V <sub>CSH</sub>      | CSH pin input voltage                                             | Vs-0.3                  | V <sub>B</sub> +0.3  |       |

| V <sub>CC</sub>       | Low-side fixed supply voltage (Note1)                             | -0.3                    | 20                   |       |

| V <sub>LO</sub>       | Low-side output voltage                                           | -0.3                    | V <sub>CC</sub> +0.3 |       |

| $V_{DD}$              | Floating input supply voltage                                     | -0.3                    | 210                  | V     |

| V <sub>SS</sub>       | Floating input supply voltage (Note1)                             | (See I <sub>DDZ</sub> ) | V <sub>DD</sub> +0.3 |       |

| V <sub>IN</sub>       | PWM input voltage                                                 | V <sub>SS</sub> -0.3    | V <sub>DD</sub> +0.3 |       |

| V <sub>CSD</sub>      | CSD pin input voltage                                             | V <sub>SS</sub> -0.3    | V <sub>DD</sub> +0.3 |       |

| V <sub>DT</sub>       | DT pin input voltage                                              | -0.3                    | V <sub>CC</sub> +0.3 |       |

| V <sub>OCSET</sub>    | OCSET pin input voltage                                           | -0.3                    | V <sub>CC</sub> +0.3 |       |

| $V_{REF}$             | VREF pin voltage                                                  | -0.3                    | V <sub>CC</sub> +0.3 |       |

| I <sub>DDZ</sub>      | Floating input supply Zener clamp current (Note1)                 | -                       | 10                   |       |

| I <sub>ccz</sub>      | Low side supply Zener clamp current (Note1)                       | -                       | 10                   |       |

| I <sub>BSZ</sub>      | Floating supply Zener clamp current (Note1)                       | -                       | 10                   | - mA  |

| I <sub>OREF</sub>     | Reference output current                                          | -                       | 5                    |       |

| d V <sub>S</sub> /dt  | Allowable V <sub>S</sub> voltage slew rate                        | -                       | 50                   |       |

| d V <sub>SS</sub> /dt | Allowable V <sub>SS</sub> voltage slew rate (Note2)               | -                       | 50                   | V/ns  |

| d V <sub>SS</sub> /dt | Allowable V <sub>SS</sub> voltage slew rate upon power-up (Note3) | -                       | 50                   |       |

| PD                    | Maximum power dissipation                                         | -                       | 1.0                  | W     |

| $R_{th,JA}$           | Thermal resistance, junction to ambient                           | -                       | 115                  | °C/W  |

| TJ                    | Junction temperature                                              | -                       | 150                  |       |

| Τs                    | Storage temperature                                               | -55                     | 150                  | °C    |

| TL                    | Lead temperature (soldering, 10 seconds)                          | -                       | 300                  |       |

Note1:  $V_{DD}$  -  $V_{SS}$ ,  $V_{CC}$  -COM and  $V_B$  -  $V_S$  contain internal shunt Zener diodes. Please note that the voltage ratings of these can be limited by the clamping current.

Note2: For the rising and falling edges of step signal of 10 V.  $V_{ss}$ =15 V to 200 V. Note3:  $V_{ss}$  ramps up from 0 V to 200 V.

## IRS20955(S)PbF PRELIMINARY

### **Recommended Operating Conditions**

For proper operation, the device should be used within the recommended conditions below. The V<sub>S</sub> and COM offset ratings are tested with supplies biased at  $I_{DD}$ =5 mA,  $V_{CC}$ =12 V and  $V_B$ -V<sub>S</sub>=12 V.

| Symbol             | Definition                                 | Min.              | Max.            | Units |

|--------------------|--------------------------------------------|-------------------|-----------------|-------|

| VB                 | High-side floating supply absolute voltage | Vs+10             | Vs+18           | V     |

| Vs                 | High-side floating supply offset voltage   | Note 1            | 100             | v     |

| I <sub>DDZ</sub>   | Floating input supply zener clamp current  | 1                 | 5               | mA    |

| V <sub>SS</sub>    | Floating input supply absolute voltage     | 0                 | 200             |       |

| V <sub>HO</sub>    | High-side floating output voltage          | Vs                | V <sub>B</sub>  |       |

| V <sub>CC</sub>    | Low-side fixed supply voltage              | 10                | 18              |       |

| V <sub>LO</sub>    | Low-side output voltage                    | 0                 | V <sub>CC</sub> | V     |

| V <sub>IN</sub>    | PWM input voltage                          | N                 | N/              |       |

| V <sub>CSD</sub>   | CSD pin input voltage                      | – V <sub>SS</sub> | V <sub>DD</sub> |       |

| V <sub>DT</sub>    | DT pin input voltage                       | 0                 | V <sub>CC</sub> |       |

| I <sub>OREF</sub>  | Reference output current to COM (Note 2)   | 0.3               | 0.8             | mA    |

| V <sub>OCSET</sub> | OCSET pin input voltage                    | 0.5               | 5               | V     |

| T <sub>A</sub>     | Ambient temperature                        | -40               | 125             | °C    |

Note 1: Logic operational for  $V_S$  equal to -5 V to +200 V. Logic state held for  $V_S$  equal to -5 V to  $-V_{BS}$ .

Note 2: Nominal voltage for V<sub>REF</sub> is 5 V. I<sub>OREF</sub> of 0.3 mA – 0.8 mA dictates total external resistor value on V<sub>REF</sub> to be 6.3 k $\Omega$  to 16.7 k $\Omega$ .

## IRS20955(S)PbF PRELIMINARY

### **Electrical Characteristics**

$V_{CC}$ ,  $V_{BS}$ = 12 V,  $I_{DD}$ =5 mA,  $V_{SS}$ =20 V,  $V_{S}$ =0 V,  $C_{L}$ =1 nF and  $T_{A}$ =25 °C unless otherwise specified.

| Symbol              | Definition                                                                     | Min                    | Тур                    | Max                    | Units | Test Conditions                           |

|---------------------|--------------------------------------------------------------------------------|------------------------|------------------------|------------------------|-------|-------------------------------------------|

| Low-Side            | e Supply                                                                       | •                      | •                      |                        |       |                                           |

| UV <sub>CC+</sub>   | V <sub>CC</sub> supply UVLO positive threshold                                 | 8.4                    | 8.9                    | 9.4                    | 14    |                                           |

| UV <sub>CC-</sub>   | V <sub>CC</sub> supply UVLO negative threshold                                 | 8.2                    | 8.7                    | 9.2                    | V     |                                           |

| IQCC                | Low-side quiescent current                                                     | -                      | -                      | 3                      | mA    | $V_{DT} = V_{CC}$                         |

| VCLAMPL             | Low-side Zener diode clamp voltage                                             | 19.6                   | 20.4                   | 21.6                   | V     | I <sub>CC</sub> =5 mA                     |

|                     | e Floating Supply                                                              |                        |                        |                        |       | 00 -                                      |

| UV <sub>BS+</sub>   | High-side well UVLO positive                                                   | 0.0                    | 0.5                    | 0.0                    |       |                                           |

| -                   | threshold                                                                      | 8.0                    | 8.5                    | 9.0                    | v     |                                           |

| $UV_{BS}$           | High-side well UVLO negative<br>threshold                                      | 7.8                    | 8.3                    | 8.8                    | v     |                                           |

| I <sub>QBS</sub>    | High-side quiescent current                                                    | _                      | -                      | 1                      | mA    |                                           |

| ILKH                | High-side to low-side leakage current                                          | _                      | _                      | 50                     | μA    | V <sub>B</sub> =V <sub>S</sub> =200 V     |

|                     | High-side Zener diode clamp voltage                                            | 19.6                   | 20.4                   | 21.6                   | V     | I <sub>BS</sub> =5 mA                     |

|                     | Input Supply                                                                   | 10.0                   | 20.4                   | 21.0                   | v     | 182-0 1117                                |

| UV <sub>DD+</sub>   | V <sub>DD</sub> , V <sub>SS</sub> floating supply UVLO                         |                        |                        |                        |       |                                           |

|                     | positive threshold                                                             | 8.2                    | 8.7                    | 9.2                    |       | V <sub>SS</sub> =0 V                      |

| $UV_{DD}$           | V <sub>DD</sub> , V <sub>SS</sub> floating supply UVLO<br>negative threshold   | 7.7                    | 8.2                    | 8.7                    | V     | V <sub>SS</sub> =0 V                      |

|                     | Floating input quiescent current                                               | -                      | -                      | 1                      | mA    | $V_{DD}$ =9.5 V + $V_{SS}$                |

| VCLAMPM             | Floating input Zener diode clamp<br>voltage                                    | 9.8                    | 10.2                   | 10.8                   | V     | I <sub>DD</sub> =5 mA                     |

| I <sub>LKM</sub>    | Floating input side to low-side leakage current                                | -                      | -                      | 50                     | μA    | V <sub>DD</sub> =V <sub>SS</sub> =200 V   |

| Floating            | PWM Input                                                                      |                        |                        |                        |       |                                           |

| VIH                 | Logic high input threshold voltage                                             | 2.3                    | 1.9                    | -                      |       |                                           |

| VIII                | Logic low input threshold voltage                                              | -                      | 1.9                    | 1.5                    | V     |                                           |

| I <sub>IN+</sub>    | Logic "1" input bias current                                                   | -                      | -                      | 40                     |       | V <sub>IN</sub> =3.3 V                    |

| I <sub>IN-</sub>    | Logic "0" input bias current                                                   | -                      | -                      | 1                      | μA    | $V_{IN} = V_{SS}$                         |

| •IIN-               |                                                                                |                        |                        | •                      |       | • 11 • 33                                 |

| Protectio           | on                                                                             |                        |                        |                        |       |                                           |

| V <sub>REF</sub>    | Reference output voltage                                                       | 4.8                    | 5.1                    | 5.4                    |       | I <sub>OREF</sub> =0.5 mA                 |

| V <sub>th,OCL</sub> | Low-side OC threshold in Vs                                                    | 1.1                    | 1.2                    | 1.3                    | -     | OCSET=1.2 V,<br>Fig. 3                    |

| $V_{\text{th,OCH}}$ | High-side OC threshold in $V_{CSH}$                                            | 1.1+ V <sub>S</sub>    | 1.2+ V <sub>S</sub>    | 1.3+ V <sub>S</sub>    | V     | V <sub>s</sub> =200 V,<br>Fig. 4          |

| V <sub>th,1</sub>   | CSD pin shutdown release threshold                                             | 0.62 x V <sub>DD</sub> | 0.70 x V <sub>DD</sub> | 0.78 x V <sub>DD</sub> |       | 0                                         |

| V <sub>th,2</sub>   | CSD pin self reset threshold                                                   | 0.26 x V <sub>DD</sub> | 0.30 x V <sub>DD</sub> | 0.34 x V <sub>DD</sub> |       | $V_{SS}$ =0 V                             |

| I <sub>CSD+</sub>   | CSD pin discharge current                                                      | 70                     | 100                    | 130                    |       | · · · · · · · · · · · · · · · · · · ·     |

| I <sub>CSD-</sub>   | CSD pin charge current                                                         | 70                     | 100                    | 130                    | μA    | $V_{SD}$ = $V_{SS}$ +5 V                  |

|                     | Shutdown propagation delay from                                                |                        |                        |                        |       |                                           |

| t <sub>SD</sub>     | $V_{CSD} > V_{SS} + V_{th,OCH}$ to shutdown                                    | -                      | -                      | 250                    | -     | Fig. 2                                    |

| t <sub>осн</sub>    | Propagation delay time from V <sub>CSH</sub> > V <sub>th,OCH</sub> to shutdown | -                      | -                      | 500                    | ns    | Fig. 4                                    |

| t <sub>OCL</sub>    | Propagation delay time from Vs><br>V <sub>th,OCL</sub> to shutdown             | -                      | -                      | 500                    |       | Fig. 3                                    |

| Gate Driv           | ver                                                                            |                        |                        |                        |       |                                           |

| I <sub>0+</sub>     | Output high short circuit current (source)                                     | -                      | 1.0                    | -                      | А     | V <sub>O</sub> =0 V, PW <u>&lt;</u> 10 μ  |

| I <sub>o-</sub>     | Output low short circuit current (sink)                                        | -                      | 1.2                    | -                      |       | V <sub>0</sub> =12 V, PW <u>&lt;</u> 10 μ |

| V <sub>OL</sub>     | Low level output voltage<br>LO – COM, HO – VS                                  | -                      | _                      | 0.1                    | V     |                                           |

**Electrical Characteristics (cont.)**  $V_{CC}$ ,  $V_{BS}$ = 12 V,  $I_{DD}$ =5 mA,  $V_{SS}$ =20 V,  $V_S$ =0 V,  $C_L$ =1 nF and  $T_A$ =25 °C unless otherwise specified.

| V <sub>OH</sub>    | High level output voltage<br>VCC – LO, VB – HO                                                                                            | -                      | -                      | 1.4                    | V  | I <sub>O</sub> =0 A                                                            |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|----|--------------------------------------------------------------------------------|

| tr                 | Turn-on rise time                                                                                                                         | -                      | 15                     | -                      |    |                                                                                |

| t <sub>f</sub>     | Turn-off fall time                                                                                                                        | -                      | 10                     | -                      |    |                                                                                |

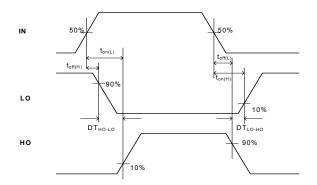

| t <sub>on,1</sub>  | High-side and low-side turn-on<br>propagation delay, floating inputs                                                                      | -                      | 105                    | -                      |    | $V_{DT} = V_{CC,}$<br>$V_{S} = 100 V,$                                         |

| t <sub>off,1</sub> | High-side and low-side turn-off<br>propagation delay, floating inputs                                                                     | -                      | 90                     | -                      |    | $V_{SS} = 100 V$ ,<br>$V_{SS} = 100 V$                                         |

| t <sub>on,2</sub>  | High-side and low-side turn-on<br>propagation delay, non-floating inputs                                                                  | -                      | 105                    | -                      |    | V <sub>DT</sub> = V <sub>CC,</sub><br>V <sub>S</sub> = 100V,                   |

| t <sub>off,2</sub> | High-side and low-side turn-off<br>propagation delay, non-floating inputs                                                                 | -                      | 90                     | -                      |    | $V_{SS} = COM$                                                                 |

| DT1                | Deadtime: LO turn-off to HO turn-on<br>(DT <sub>LO-HO</sub> ) & HO turn-off to LO turn-on<br>(DT <sub>HO-LO</sub> )                       | 8                      | 15                     | 22                     | ns | V <sub>DT</sub> >V <sub>DT1,</sub><br>V <sub>SS</sub> = COM                    |

| DT2                | Deadtime: LO turn-off to HO turn-on<br>(DT <sub>LO-HO</sub> ) & HO turn-off to LO turn-on<br>(DT <sub>HO-LO</sub> )                       | 15                     | 25                     | 35                     |    | V <sub>DT1</sub> >V <sub>DT</sub> > V <sub>DT2,</sub><br>V <sub>SS</sub> = COM |

| DT3                | Deadtime: LO turn-off to HO turn-on<br>( $DT_{LO-HO}$ ) & HO turn-off to LO turn-on<br>( $DT_{HO-LO}$ )                                   | 20                     | 35                     | 50                     |    | V <sub>DT2</sub> >V <sub>DT</sub> > V <sub>DT3,</sub><br>V <sub>SS</sub> = COM |

| DT4                | Deadtime: LO turn-off to HO turn-on<br>( $DT_{LO:HO}$ ) & HO turn-off to LO turn-on<br>( $DT_{HO-LO}$ )V <sub>DT</sub> = V <sub>DT4</sub> | 25                     | 45                     | 60                     |    | V <sub>DT3</sub> >V <sub>DT</sub> > V <sub>DT4,</sub><br>V <sub>SS</sub> = COM |

| V <sub>DT1</sub>   | DT mode select threshold 2                                                                                                                | 0.51(V <sub>cc</sub> ) | 0.57(V <sub>cc</sub> ) | 0.63(V <sub>cc</sub> ) |    |                                                                                |

| V <sub>DT2</sub>   | DT mode select threshold 3                                                                                                                | 0.32(V <sub>cc</sub> ) | 0.36(V <sub>cc</sub> ) | 0.40(V <sub>cc</sub> ) | V  |                                                                                |

| V <sub>DT3</sub>   | DT mode select threshold 4                                                                                                                | 0.21(V <sub>cc</sub> ) | 0.23(V <sub>cc</sub> ) | 0.25(V <sub>cc</sub> ) |    |                                                                                |

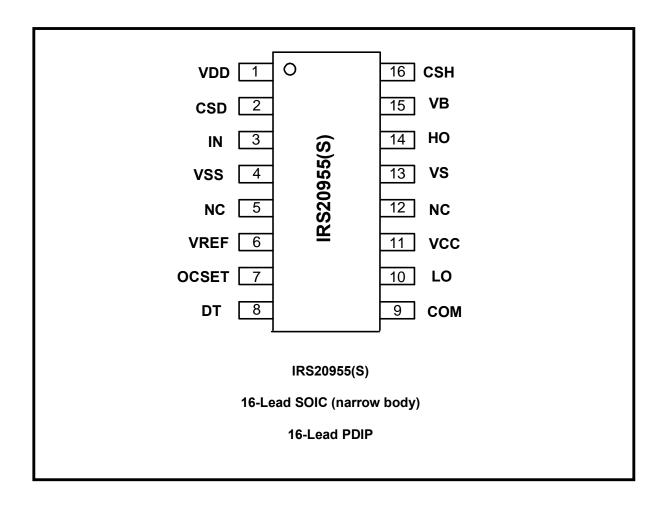

### Lead Definitions

| Pin # | Symbol | Description                                                |  |

|-------|--------|------------------------------------------------------------|--|

| 1     | VDD    | Floating input positive supply                             |  |

| 2     | CSD    | Shutdown timing capacitor, referenced to VSS               |  |

| 3     | IN     | PWM non-inverting input, in phase with HO                  |  |

| 4     | VSS    | Floating input supply return                               |  |

| 5     | NC     |                                                            |  |

| 6     | VREF   | 5 V reference output for setting OCSET                     |  |

| 7     | OCSET  | Low-side over current threshold setting, referenced to COM |  |

| 8     | DT     | Input for programmable deadtime, referenced to COM         |  |

| 9     | COM    | Low-side supply return                                     |  |

| 10    | LO     | Low-side output                                            |  |

| 11    | VCC    | Low-side logic supply                                      |  |

| 12    | NC     |                                                            |  |

| 13    | VS     | High-side floating supply return                           |  |

| 14    | HO     | High-side output                                           |  |

| 15    | VB     | High-side floating supply                                  |  |

| 16    | CSH    | High-side over current sensing input, referenced to VS     |  |

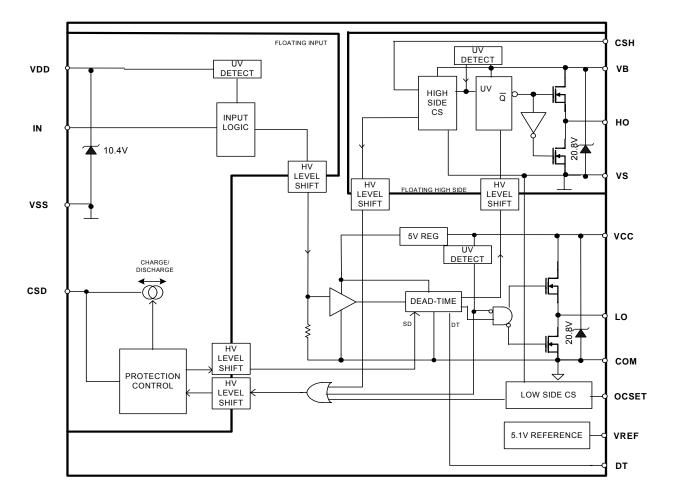

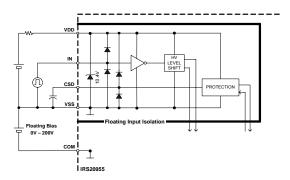

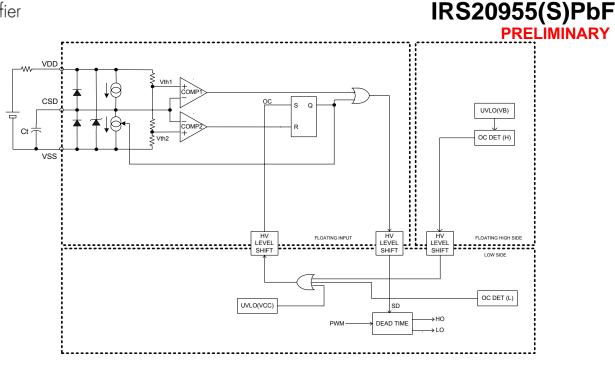

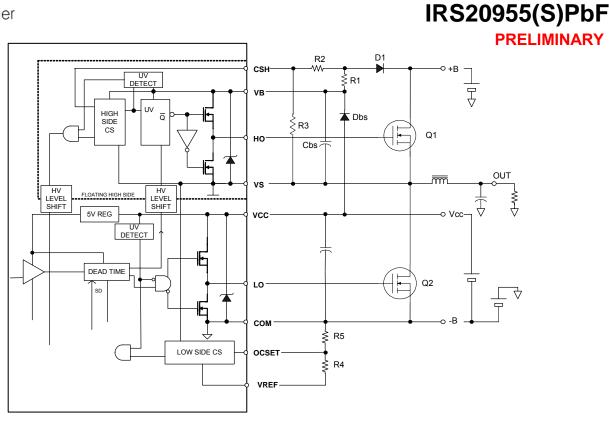

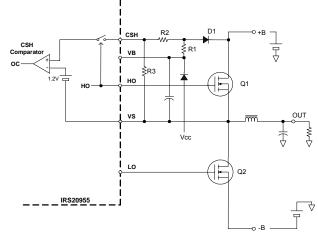

### **Block Diagram**

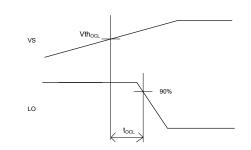

Figure 3.  $V_S > V_{TH,OCL}$  to Shutdown Waveform

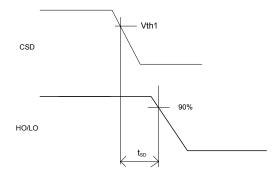

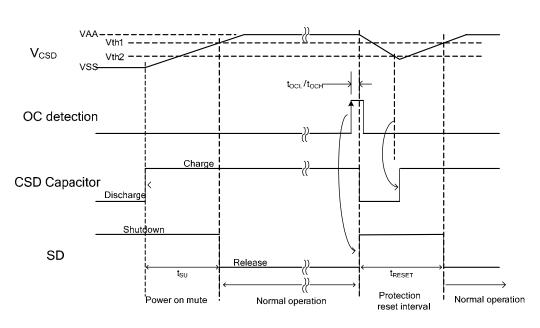

Figure 2. CSD to Shutdown Waveform Definitions

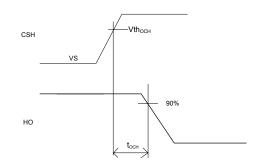

Figure 4.  $V_S > V_{TH,OCL}$  to Shutdown Waveform

## IRS20955(S)PbF PRELIMINARY

### **Functional Description**

#### Floating PWM Input

The IRS20955S accepts floating inputs, enabling easy half-bridge implementation.  $V_{DD}$ , CSD and IN refer to  $V_{SS}$ . As a result, the PWM input signal can directly feed into IN while referencing  $V_{SS}$ , which is typically the midpoint between the positive and negative DC bus voltages in a half-bridge configuration.

The IRS20955S also accepts a non-floating input when  $V_{\text{SS}}$  is tied to COM.

Figure 5. Floating PWM Input Structure

#### **Over-Current Protection (OCP)**

The IRS20955S features over-current protection to protect the power MOSFETs during abnormal load conditions. The IRS20955S engages a sequence of events when it detects the over-current condition during high-side or low-side turn on.

As soon as either the high-side or low-side current sensing block detects over-current:

- 1. The OC Latch (OCL) flips logic states and shutdowns the outputs LO and HO.

- 2. The CSD pin starts discharging the external capacitor Ct.

- 3. When V<sub>CSD</sub>, the voltage across Ct, falls below the lower threshold Vth2, an output signal from COMP2 resets OCL.

- 4. The CSD pin starts charging the external capacitor Ct.

- 5. When  $V_{CSD}$  goes above the upper threshold  $V_{th1}$ , the logic on COMP1 flips and the IC resumes operation.

As long as the over current condition exists, the IC will repeat the over current protection sequence.

Figure 6. Over-Current Protection Timing Chart

Figure 7. Shutdown Functional Block Diagram

### **Protection Control**

The internal protection control block dictates the operational mode-norma, or shutdown, using the input of the CSD pin. The IC functions as expected in the normal mode. In shutdown mode, the IC forces LO and HO to output 0 V with respect to COM and VS to turn off the power MOSFETs.

The CSD pin provides five functions.

- 1. Power up delay timer

- 2. Self-reset timer

- 3. Shutdown input

- 4. Latched protection configuration

- 5. Shutdown status output (host I/F)

#### Self Reset Protection

By putting a capacitor between CSD and  $V_{\rm SS},$  the IRS20955S can reset itself after entering shutdown mode.

Figure 8. Self Reset Protection Configuration

### **Designing Ct**

The timing capacitor, Ct, is used to program  $t_{\mbox{\scriptsize RESET}}$  and  $t_{\mbox{\scriptsize SU}}.$

- $t_{RESET,}$  is the amount of time that elapses from when the IC enters shutdown mode to the time when the IC resumes operation.  $t_{RESET}$  should be long enough to avoid over heating the MOSFET from the repetitive sequence of shutting down and resuming operation during over current conditions. In most of applications, the minimum recommended time for  $t_{RESET}$  is 0.1.

- t<sub>SU</sub> is the amount of time between powering up the IC in shutdown mode to the moment the IC releases shutdown to begin normal operation.

The values chosen for  $t_{\text{RESET}}$  and  $t_{\text{SU}}$  will determine the capacitance of Ct using the given equations:

$$Ct = \frac{t_{RESET} \cdot I_{CSD}}{1.1 \cdot V_{DD}} \quad [F]$$

$$Ct = \frac{t_{SU} \cdot I_{CSD}}{0.7 \cdot V_{DD}} \quad [F]$$

where  $~~I_{\text{CSD}}$  = the charge/discharge current at the CSD pin

$V_{DD}$  = the supply voltage with respect to  $V_{SS}$ .

## IRS20955(S)PbF PRELIMINARY

#### Shutdown Input

When  $V_{CSD}$  falls below  $V_{th2}$ , the IRS20955S begins to charge Ct in an attempt to resume operation. Once the voltage of the CSD pin rises above the upper threshold,  $V_{th1}$ , the IC begins to operate normally again.

Figure 9. Shutdown Input

#### Latched Protection

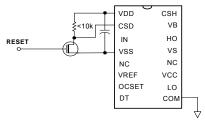

Connecting CSD to V<sub>DD</sub> through a 10 k $\Omega$  or less resistor configures the over current protection latch. The latch locks the IC in shutdown mode after over current is detected. An external reset switch can be used to bring CSD below the lower threshold V<sub>th2</sub> for a minimum of 200 ns to properly reset the latch. After the power up sequence, a reset signal to the CSD pin is required to release the IC from shutdown mode.

Figure 10. Latched Protection Configuration

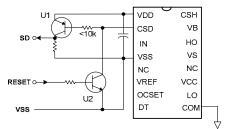

#### Interfacing with System Controller

The IRS20955S can communicate with an external system controller through a simple interfacing circuit such as the one shown in Figure 11. A generic PNP transistor, shown as U1, can detect the sink current at the CSD pin during an OCP event and output a shutdown signal to an external system controller. Another generic NPN transistor, shown as U2, can then reset the internal protection logic by pulling the CSD voltage below  $V_{th2}$  for a minimum of 200 ns. Note that the CSD pin is configured to operate in latched OCP. After the power up sequence, a reset signal to the CSD pin is required to release the IC from shutdown mode.

Figure 11. Interfacing with System Controller

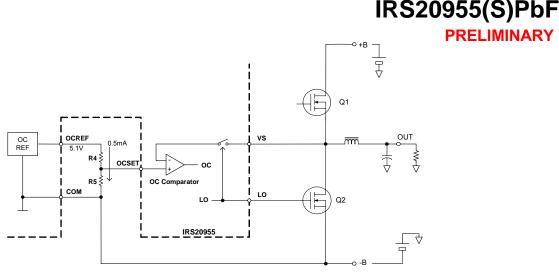

#### Programming OCP Trip Level

In a Class D audio amplifier, the direction of the load current alternates with the audio input signal. An over-current condition can therefore occur during either a positive current cycle or a negative current cycle. The IRS20955 uses the  $R_{DS(ON)}$  of the output MOSFETs as current sensing resistors. Due to the structural constraints of high voltage ICs, current sensing is implemented differently for high side and low side. If the measured current exceeds a predetermined threshold, the OCP block outputs a signal to the protection block to shutdown the MOSFET to protect the switching devices.

Figure 12. Bi-directional Over Current Protection

#### Low-side Over Current Sensing

For negative load currents, low-side over current sensing monitors the load condition and shuts down switching operation if the load current exceeds the preset trip level.

Low-side current sensing is based on the measurement of  $V_{DS}$  across the low side MOFET during low-side turn on. In order to avoid triggering OCP from overshoot, a blanking interval inserted after LO turn on disables over current detection for 450 ns.

The OCSET pin is used to program the threshold for low-side over current sensing. When the  $V_{DS}$  measured across the low-side MOSFET exceeds the voltage at the OCSET pin with respect COM, the IRS20955S begins the OCP sequence described earlier.

Since the voltage from  $V_S$  to COM is compared to the voltage at the OCSET pin, the voltage at OCSET determines the trip level for over-current detection. By selecting the trip level for over-current, the voltage at OCSET can be calculated using the equation below.

$V_{OCSET} = V_{DS(LOW SIDE)} = I_{TRIP+} \times R_{DS(ON)}$

In order to minimize the effect of the input bias current at the OCSET pin, select resistor values for R4 and R5 such that the current through the voltage divider is 0.5 mA or more.

\* Note: Using  $V_{\text{REF}}$  to generate an input to OCSET through a resistive divider provides improved immunity from fluctuations in  $V_{\text{CC}}$ .

Figure 13. Low-side Over-Current Sensing

#### Low-Side Over-Current Setting

Let the low-side MOSFET have an  $R_{\text{DS}(\text{ON})}$  of 100  $m\Omega$  and set the current trip level to 30 A. V<sub>OCSET</sub> is given by:

$V_{OCSET} = I_{TRIP+} \times R_{DS(ON)} = 30 \text{ A} \times 100 \text{ m}\Omega = 3.0 \text{ V}$

Choose R4+R5=10 k $\Omega$  to properly load the VREF pin.

$$R_{5} = \frac{V_{OCSET}}{V_{REF}} \cdot 10 k\Omega$$

$$= \frac{3.0 V}{5.1 V} \cdot 10 k\Omega$$

$$= 5.8 k\Omega$$

where  $V_{REF} = 5.1 V$

Based on the E-12 series of resistor values, choose R5 to be 5.6 k $\Omega$  and R4 to be 3.9 k $\Omega$  to complete the design.

In general, R<sub>DS(ON)</sub> has a positive temperature coefficient that needs to be considered when setting the threshold level. Variations in R<sub>DS(ON)</sub> will affect the selection of external or internal component values.

#### **High-Side Over-Current Sensing**

For positive load currents, high-side over current sensing also monitors the load condition and shuts down the switching operation if the load current exceeds the preset trip level.

High-side current sensing is based on the measurement of V<sub>DS</sub> across the high-side MOFET during high-side turn on through pins CSH and VS. In order to avoid triggering OCP from overshoot, a blanking interval inserted after HO turn on disables over current detection for 450 ns.

PRELIMINARY

In contrast to low-side current sensing, the threshold at which the CSH pin engages OC protection is internally fixed at 1.2 V. An external resistive divider R2 and R3 can be used to program a higher threshold.

An external reverse blocking diode, D1, is required to block high voltages from feeding into the CSH pin while the high-side is off. Due to a forward voltage drop of 0.6 V across D1, the minimum threshold required for high-side over current protection is 0.6 V.

$$V_{CSH} = \frac{R3}{R2 + R3} \cdot \left( V_{DS(HIGHSIDE)} + V_{F(D1)} \right)$$

where  $V_{DS(HIGH SIDE)}$  = the drain to source voltage of the high-side MOSFET during high-side turn on  $V_{F(D1)}$  = the forward drop voltage of D1

Since  $V_{\text{DS(HIGH SIDE)}}$  is determined by the product of drain current I<sub>D</sub> and R<sub>DS(ON)</sub> of the high-side MOSFET. V<sub>CSH</sub> can be rewritten as:

$$V_{CSH} = \frac{R3}{R2 + R3} \cdot \left( R_{DS(ON)} \cdot I_D + V_{F(D1)} \right)$$

Note: The reverse blocking diode D1 is forward biased by a 10 k $\Omega$  resistor R1 when the high-side MOSFET is on.

Figure 14. Programming High-Side Over-Current Threshold

#### High-Side Over-Current Setting

Figure 14 demonstrates the typical circuitry used for high-side current sensing. In the following example, the over current protection level is set to trip at 30 A using a MOSFET with an  $R_{DS(ON)}$  of 100 m $\Omega$ . The component values of R2 and R3 can be calculated using the following formula:

Let R2 + R3=10 kΩ.

$$R_3 = 10 \ k\Omega \cdot \frac{Vth_{OCH}}{V_{DS} + V_F}$$

where  $Vth_{OCL} = 1.2 V$

$V_F$  = the forward voltage of reverse blocking diode D1 = 0.6 V.

$V_{\text{DS@ID=30A}}$  = the voltage drop across the high-side MOSFET when the MOSFET current is 30 A.

Therefore,  $V_{DS@ID=30A} = I_D \times R_{DS(ON)} = 30 \text{ A} \times 100 \text{ m}\Omega$ = 3 V

Based on the formulas above, R2 = 6.8 k $\Omega$  and R3 = 3.3 k $\Omega$ .

#### Choosing the Right Reverse Blocking Diode

The selection of the appropriate reverse blocking diode used in place of D1 depends on its voltage rating and speed. To effectively block bus voltages, the reverse voltage must be higher than the voltage difference between +B and -B and the reverse recovery time must be as fast as the boot strap charging diode. A diode such as the Philips BAV21 W, a 200 V, 50 ns high speed switching diode, is more than sufficient.

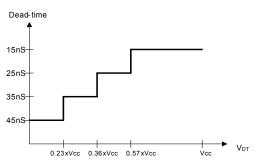

#### **Deadtime Generator**

Deadtime is a blanking period inserted between high-side turn on and low-side turn on to prevent shoot through. In the IRS20955S, an internal deadtime generation block allows the user to select the optimum deadtime from a range of preset values. Selecting a preset deadtime through the DT/SD pin voltage can easily be done through an external voltage divider. This way of setting deadtime prevents outside noise from modulating the switching timing, which is critical to the audio performances.

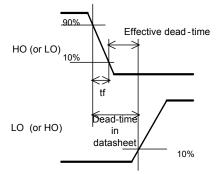

#### How to Determine Optimal Deadtime

The effective deadtime in an actual application differs from the deadtime specified in this datasheet due to the switching fall time,  $t_{\rm f.}$ . The deadtime value in this datasheet is defined as the time period between the beginning of turn-off on one side of the switching stage and the beginning of turn-on on the other side as shown in Figure 15. The fall time of MOSFET gate voltage must be subtracted from the deadtime value in the datasheet to determine the effective deadtime of a Class D audio amplifier.

(Effective deadtime) = (Deadtime in datasheet)  $- t_{f}$ .

## IRS20955(S)PbF

PRELIMINARY

Figure 15. Effective Deadtime

A longer deadtime period is required for a MOSFET with a larger gate charge value because of the longer  $t_{f.}$ . Although a shorter effective deadtime setting is beneficial to achieving better linearity in Class D amplifiers, the likelihood of shoot-through current increases with narrower deadtime settings. Negative values of effective deadtime may cause excessive heat dissipation in the MOSFETs, leading to potentially serious damage.

To calculate the optimal deadtime in a given application, the fall time tf for both HO and LO in the actual circuit need to be taken into account. In addition, variations in temperature and device parameters could also affect the effective deadtime in the actual circuit. Therefore, a minimum effective deadtime of 10 ns is recommended to avoid shootthrough current over the range of operating temperatures and supply voltages.

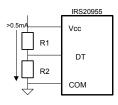

#### Programming Deadtime

The IRS20955S selects the deadtime from a range of preset deadtime values based on the voltage applied at the DT pin. An internal comparator translates the DT input to a predetermined dead-time by comparing the input with internal reference voltages. These internal reference voltages are set in the IC through a resistive voltage divider using  $V_{CC}$ . The relationship between the operation mode and the voltage at DT pin is illustrated in the Figure 16 below.

Figure 16. Deadtime vs. V<sub>DT</sub>

Table 1 suggests pairs of resistor values used in the voltage divider for selecting deadtime. Resistors with up to 5% tolerance are acceptable when using these values.

Figure 17. External Voltage Divider

| Table 1 Recommended Resistor values for Deadtime Selection |        |        |                        |  |  |  |

|------------------------------------------------------------|--------|--------|------------------------|--|--|--|

| Deadtime Mode                                              | R1     | R2     | DT/SD Voltage          |  |  |  |

| DT1                                                        | <10 kΩ | Open   | 1.00(V <sub>CC</sub> ) |  |  |  |

| DT2                                                        | 3.3 kΩ | 8.2 kΩ | 0.71(V <sub>CC</sub> ) |  |  |  |

| DT2                                                        | 5.6 kΩ | 4.7 kΩ | 0.46(V <sub>CC</sub> ) |  |  |  |

| DT4                                                        | 8.2 kΩ | 3.3 kΩ | 0.29(V <sub>CC</sub> ) |  |  |  |

#### Table 1 Recommended Resistor Values for Deadtime Selection

#### Supplying V<sub>DD</sub>

$V_{\text{DD}}$  is designed to be supplied with an internal Zener diode clamp.  $I_{\text{DD}},$  the supply current for  $V_{\text{DD}},$  can be estimated by:

$I_{DD} \approx 1.5 \text{ mA x } 300 \text{ x } 10^{-9} \text{ x switching frequency +} 0.5 \text{ mA + } 0.5 \text{ mA}$

(Dynamic power consumption) (Static) (Zener bias)

The value of  $R_{DD}$  used to supply  $I_{DD}$  should meet the following requirement:

$$R_{DD} \le \frac{V_{+B} - 10.8 V}{I_{DD}} \quad [\Omega]$$

Example: In the case where the average PWM switching frequency is 400 kHz, the required  $I_{DD}$  is 1.18 mA. Based on this calculation, a 50 V power supply voltage would require  $R_{DD}$  to be 33 k $\Omega$  or less.

Furthermore, make sure  $I_{\text{DD}}$  is below the maximum zener diode bias current,  $I_{\text{DDZ}},$  during static state conditions.

$$I_{DDZ} \ge \frac{V_{+B} - 10.8 V}{Rdd} - 0.5 mA$$

Figure 18. Supplying V<sub>DD</sub>

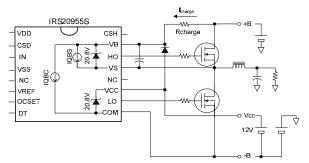

#### Charging V<sub>BS</sub> Prior to Start

The high-side bootstrap capacitor can be charged through a resistor from the positive supply bus to the  $V_B$  pin by utilizing an internal 20.8 V Zener diode between  $V_B$  and  $V_S$ . This scheme eliminates the need to charge the boot strap capacitor through low-side turn on during start-up.

#### www.irf.com

The value of this charging resistor is subject to several constraints:

IRS20955(S)PbF

PRELIMINARY

- The minimum value of R<sub>CHARGE</sub> is limited by the leakage current of the bootstrap voltage supply through <sub>RCHARGE</sub>, which would limit the maximum PWM modulation index of the system.

- The maximum value of R<sub>CHARGE</sub> is limited by the current charge capability of the resistor during startup:

$$I_{CHARGE} > I_{QBS}$$

where  $I_{CHARGE}$  = the current through  $R_{CHARGE}$

$I_{\text{QBS}}$  = the high side quiescent current.

Figure 19. Boot Strap Supply Pre-charging

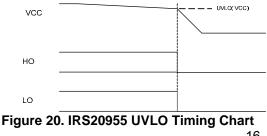

#### Start-up Sequence (UVLO)

The protection control block in the IRS20955S monitors the status of V<sub>DD</sub> and V<sub>CC</sub> to ensure that both voltage supplies are above the UVLO (undervoltage lockout) threshold before beginning normal operation. If either V<sub>DD</sub> or V<sub>CC</sub> is below the under voltage threshold, LO and HO are disabled in shutdown mode until both V<sub>DD</sub> and V<sub>CC</sub> rise above the voltage threshold.

#### Power-down Sequence

As soon as  $V_{DD}$  or  $V_{CC}$  falls below the UVLO threshold, protection logic in the IRS20955S turns off LO and HO, shutting off the power MOSFETs.

#### Power Supply Decoupling

As the IRS20955S contains analog circuitry, careful attention must be given to decoupling the power supplies for proper operation. Ceramic capacitors of 0.1  $\mu$ F or more should be placed close to the power supply pins of the IC on the board.

Please refer to the application note AN-978 for general design considerations of a high voltage gate driver IC.

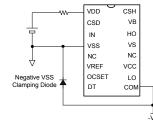

### V<sub>ss</sub> Negative Bias Clamping

$V_{\rm SS}$  can go below COM when a negative supply is missing in a dual supply configuration. In this case, excessive negative  $V_{\rm SS}$  voltage with respect to COM could damage the IRS20955S. Having a diode to clamp potential negative biases to  $V_{\rm SS}$  is recommended to protect the IC. A standard recovery diode with a current rating of 1 A such as the 1N4002 is sufficient for this purpose.

Figure 21. Negative V<sub>SS</sub> Clamping

### Junction Temperature Estimation

The power dissipation in the IRS20955S is dominated by the following items:

- P<sub>MID</sub>: Power dissipation of the floating input logic and protection circuitry

- P<sub>LSM</sub>: Power dissipation of the input level shifter

- P<sub>LOW</sub>: Power dissipation in low-side

- P<sub>LSH</sub>: Power dissipation of the high-side level shifter

- P<sub>HIGH</sub>: Power dissipation in high-side

### 1. P<sub>MID</sub>: Power Dissipation of the Floating Input Logic and Protection Circuitry

The power dissipation of the floating input section is given by:

$$P_{MID} = P_{ZDD} + P_{LDD} \approx \frac{V_{+BUS} - V_{DD}}{R_{DD}} \cdot V_{DD}$$

IRS20955(S)

where

$P_{\text{ZDD}}$  = the power dissipation from the internal Zener diode clamping  $V_{\text{DD}}$

$P_{LDD}$  = the power dissipation from the internal logic circuitry

$V_{+BUS}$  = the positive bus voltage feeding  $V_{DD}$

$R_{DD}$  = the resistor feeding  $V_{DD}$  from  $V_{+BUS}$

\*For obtaining the value of  $R_{\text{DD}},$  refer to the section "Supplying  $V_{\text{DD}}.$ "

## 2. P<sub>LSM</sub>: Power Dissipation of the Input Level Shifter

$$P_{LSM}$$

= 2 nC x  $f_{sw}$  x  $V_{SS,BIAS}$

where

f<sub>SW</sub> = the PWM switching frequency

$V_{\rm SS,BIAS}$  = the bias voltage of  $V_{\rm SS}$  with respect to COM

#### 3. PLOW: Power Dissipation in Low-Side

The power dissipation in low-side comes from the losses of the logic circuitry and the losses of driving LO.

$$\begin{aligned} P_{LOW} &= P_{LDD} + P_{LO} \\ &= \left( I_{QCC} \cdot V_{CC} \right) + \left( Vcc \cdot Q_g \cdot f_{SW} \cdot \frac{R_O}{R_O + R_g + R_{g(\text{int})}} \right) \end{aligned}$$

where

$P_{LDD}$  = the power dissipation from the internal logic circuitry

$P_{LO}$  = the power dissipation from the gate drive stage to LO

$R_{\rm O}$  = the output impedance of LO, typically 10  $\Omega$  for the IRS20955S

$R_{g(int)}$  = the internal gate resistance of the low side MOSFET driver, typically 10  $\Omega$  for the IRS20955S

$R_g$  = the external gate resistance of the low side MOSFET

Qg = total gate charge of the low side MOSFET

#### 4. P<sub>LSH</sub>: Power Dissipation of the High-Side Level Shifter

$P_{LSH}$  = 0.4 nC x f<sub>sw</sub> x V<sub>BUS</sub>

where

$f_{SW}$  = the PWM switching frequency

$V_{BUS}$  = the difference between the positive bus voltage and negative bus voltage

#### 5. P<sub>HIGH</sub>: Power Dissipation in High-side

The power dissipation in high-side comes from the losses of the logic circuitry and the losses of driving LO.

$$\begin{split} P_{HIGH} &= P_{LDD} + P_{HO} \\ &= \left( I_{QBS} \cdot V_{BS} \right) + \left( V_{BS} \cdot Q_g \cdot f_{SW} \cdot \frac{R_O}{R_O + R_g + R_{g(\text{int})}} \right) \end{split}$$

where

$P_{LDD}$  = the power dissipation from the internal logic circuitry

$P_{LO}$  = the power dissipation from the gate drive stage to HO

$R_0$  = equivalent output impedance of HO, typically 10  $\Omega$  for the IRS20955S

$R_{g(int)}$  = the internal gate resistance of the highside MOSFET driver, typically 10  $\Omega$  for the IRS20955S

$R_{\rm g}$  = external gate resistance of the high-side MOSFET

Q g = total gate charge of the high- side MOSFET

Total power dissipation, P<sub>d</sub>, is given by

$$P_d = P_{MID} + P_{LSM} + P_{LOW} + P_{HSM} + P_{HIGH} \,.$$

IRS20955(S)PbF

PRELIMINARY

Given  $R_{th,JA}$ , the thermal resistance between the ambient and junction temperature,  $T_J$ , the junction temperature, can be calculated from the formula provided below.

$$T_J = R_{th,JA} \cdot P_d + T_A < 150 \,^{\circ}C$$

IRS20955(S)PbF

PRELIMINARY

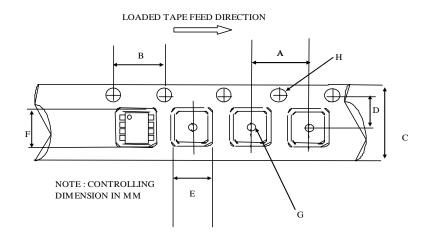

#### CARRIER TAPE DIMENSION FOR 16SOICN

|      | Metric |       | Imperial |       |  |

|------|--------|-------|----------|-------|--|

| Code | Min    | Max   | Min      | Max   |  |

| А    | 7.90   | 8.10  | 0.311    | 0.318 |  |

| В    | 3.90   | 4.10  | 0.153    | 0.161 |  |

| С    | 15.70  | 16.30 | 0.618    | 0.641 |  |

| D    | 7.40   | 7.60  | 0.291    | 0.299 |  |

| E    | 6.40   | 6.60  | 0.252    | 0.260 |  |

| F    | 10.20  | 10.40 | 0.402    | 0.409 |  |

| G    | 1.50   | n/a   | 0.059    | n/a   |  |

| Н    | 1.50   | 1.60  | 0.059    | 0.062 |  |

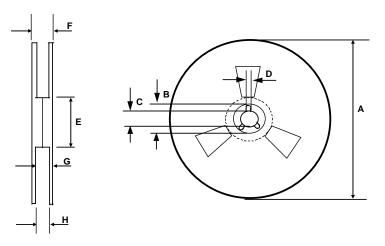

#### **REEL DIMENSIONS FOR 16SOICN**

|      | Metric |        | Imperial |        |  |

|------|--------|--------|----------|--------|--|

| Code | Min    | Max    | Min      | Max    |  |

| A    | 329.60 | 330.25 | 12.976   | 13.001 |  |

| В    | 20.95  | 21.45  | 0.824    | 0.844  |  |

| С    | 12.80  | 13.20  | 0.503    | 0.519  |  |

| D    | 1.95   | 2.45   | 0.767    | 0.096  |  |

| E    | 98.00  | 102.00 | 3.858    | 4.015  |  |

| F    | n/a    | 22.40  | n/a      | 0.881  |  |

| G    | 18.50  | 21.10  | 0.728    | 0.830  |  |

| Н    | 16.40  | 18.40  | 0.645    | 0.724  |  |

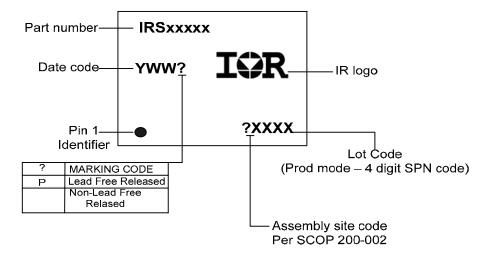

### LEAD-FREE PART MARKING INFORMATION

### **ORDER INFORMATION**

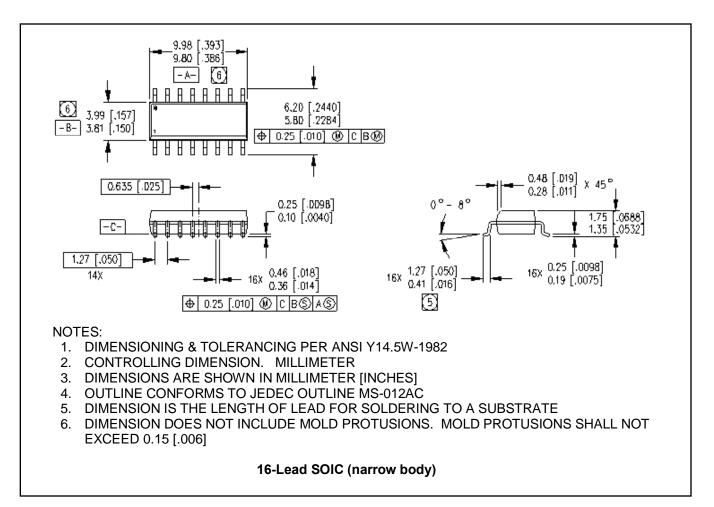

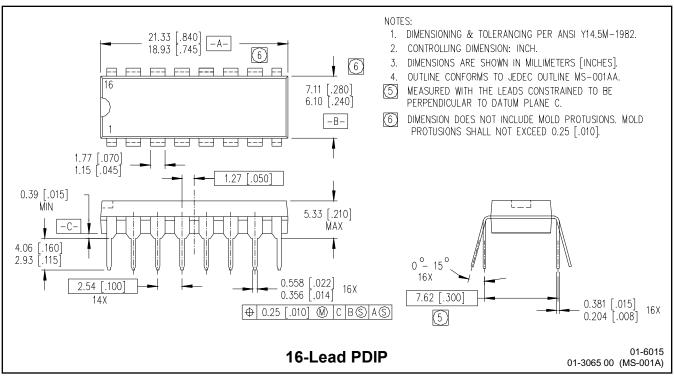

16-Lead PDIP IRS20955PbF

16-Lead SOIC IRS20955SPbF

16-Lead SOIC Tape & Reel IRS20955STRPbF

International IOR Rectifier SO-16 package is MSL3 qualified. This product has been designed and qualified for the industrial level. Qualification standards can be found at <u>IR's</u> Web Site <u>http://www.irf.com/</u> WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105 Data and specifications subject to change without notice 12/11/2006