# SIM Card Supply and **Level Shifter**

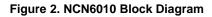

The NCN6010 is a level shifter analog circuit designed to translate the voltages between a SIM Card and an external microcontroller. A built-in DC-DC converter makes the NCN6010 useable to drive any type of SIM card. The device fulfills the GSM 11.11 specification. The external MPU has an access to a dedicated input STOP pin, providing a way to switch off the power applied to the SIM card in case of failure or when the card is removed.

#### Features

- Supports 3.0 V or 5.0 V Operating SIM Card

- Built-in Pull Up Resistor for I/O Pin in Both Directions

- All Pins are Fully ESD Protected, According to GSM Specification

- Supports 10 MHz Clock

- 6.0 kV ESD Proof on SIM Card Pins

- These are Pb–Free Devices\*\*

### **Typical Applications**

- Cellular Phone SIM Interface

- Identification Module

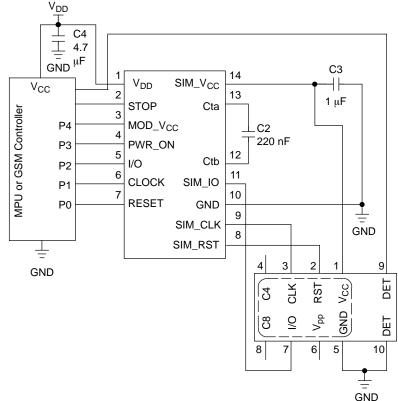

Figure 1. Typical Interface Application

\*\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## **ON Semiconductor®**

http://onsemi.com

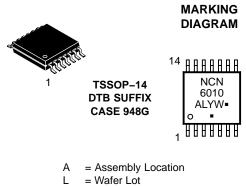

- Υ

- = Year = Work Week W

- = Pb-Free Package

(Note: Microdot may be in either location)

## ORDERING INFORMATION

| Device        | Package   | Shipping <sup>†</sup> |  |

|---------------|-----------|-----------------------|--|

| NCN6010DTB    | TSSOP-14* | 96 Units / Rail       |  |

| NCN6010DTBG   | TSSOP-14* | 96 Units / Rail       |  |

| NCN6010DTBR2  | TSSOP-14* | 2500/Tape & Reel      |  |

| NCN6010DTBR2G | TSSOP-14* | 2500/Tape & Reel      |  |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*This package is inherently Pb-Free.

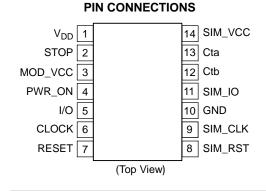

## PIN DESCRIPTIONS

| Pin | Name                | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|---------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>DD</sub>     | POWER  | This pin is connected to the system controller power supply suitable to operate from a 3.6 V typical battery. A low ESR ceramic capacitor (4.7 $\mu$ F typical) shall be used to bypass the power supply voltage.                                                                                                                                                                                                                                                                                                                            |

| 2   | STOP                | INPUT  | A Low level on this pin resets the SIM interface, switching off the SIM_VCC, according to the ISO7816–3 Power Down procedure (See Table 1 and Figure 3).                                                                                                                                                                                                                                                                                                                                                                                     |

| 3   | MOD_V <sub>CC</sub> | INPUT  | The signal present on this pin programs the SIM_VCC value (See Table 1):<br>MOD_VCC = L $\rightarrow$ SIM_VCC = 5.0 V<br>MOD_VCC = H $\rightarrow$ SIM_VCC = 3.0 V                                                                                                                                                                                                                                                                                                                                                                           |

| 4   | PWR_ON              | INPUT  | The signal present on this pin controls the SIM_VCC state (See Table 1):<br>$PWR_ON = L \rightarrow SIM_VCC = Open$ , no supply connected to the SIM card.<br>$PWR_ON = H \rightarrow SIM_VCC = Active$ , the card is powered.                                                                                                                                                                                                                                                                                                               |

| 5   | I/O                 | INPUT  | This pin is connected to an external microcontroller or GSM management unit. A bi–directional level translator adapts the serial I/O signal between the smart card and the external controller. A built–in constant 20 k $\Omega$ (typical) resistor provides a high impedance state when not activated.                                                                                                                                                                                                                                     |

| 6   | CLOCK               | INPUT  | The clock signal, coming from the external controller, must have a Duty Cycle within the Min/Max values defined by the specification (typically 50%). The built–in level shifter translates the input signal to the external SIM card CLK input.                                                                                                                                                                                                                                                                                             |

| 7   | RESET               | INPUT  | The RESET signal present at this pin is connected to the SIM card. The internal level shifter translates the level according to the voltages present at pin 1 and the SIM_VCC programmed value.                                                                                                                                                                                                                                                                                                                                              |

| 8   | SIM_RST             | OUTPUT | This pin is connected to the RESET pin of the card connector. A level translator adapts the external RESET signal to the SIM card. A built–in active pull down connects this pin to ground when the device is in a nonoperating mode.                                                                                                                                                                                                                                                                                                        |

| 9   | SIM_CLK             | OUTPUT | This pin is connected to the CLK pin of the card connector. The CLOCK signal comes from the external clock generator, the internal level shifter being used to adapt the voltage defined for the SIM_VCC. A built–in active pull down connects this pin to ground when the device is in a nonoperating mode.                                                                                                                                                                                                                                 |

| 10  | GND                 | GROUND | This pin is the GROUND reference for the integrated circuit and associated signals. Cares must be observed to avoid voltage spikes when the device operates in a normal operation.                                                                                                                                                                                                                                                                                                                                                           |

| 11  | SIM_I/O             |        | This pin handles the connection to the serial I/O of the card connector. A bi–directional level translator adapts the serial I/O signal between the card and the microcontroller. A 20 k $\Omega$ (typical) pull up resistor provides a High impedance state for the SIM card I/O link.                                                                                                                                                                                                                                                      |

| 12  | Cta                 | POWER  | This pin is connected to the external capacitor used by the internal Charge Pump converter. Using Low ESR ceramic type is recommended (X5R or X7R).                                                                                                                                                                                                                                                                                                                                                                                          |

| 13  | Ctb                 | POWER  | This pin is connected to the external capacitor used by the internal Charge Pump converter. Using Low ESR ceramic type is recommended (X5R or X7R).                                                                                                                                                                                                                                                                                                                                                                                          |

| 14  | SIM_VCC             | POWER  | This pin is connected to the SIM card power supply pin. An internal Charge Pump converter is programmable by the external MPU to supply either 3.0 V or 5.0 V output voltage. An external 1.0 $\mu F$ minimum ceramic capacitor (ESR < 100 m $\Omega$ , X5R or X7R recommended) must be connected across SIM_VCC and GND.                                                                                                                                                                                                                    |

|     |                     |        | During a normal operation, the SIM_VCC voltage can be set to 3.0 V followed by a 5.0 V value, or can start directly to any of these two values. When the voltage is adjusted downward (from 5.0 V to 3.0 V) cares must be observed as reverse peak current can flow from the external capacitors to the battery during a short amount of time (in the 1.0 $\mu$ s range). When such a voltage adjustment is necessary, it is recommended to force SIM_VCC to zero, wait 350 $\mu$ s minimum, then reprogram the chip to get SIM_VCC = 3.0 V. |

#### MAXIMUM RATINGS (Note 1)

| Rating                                                                                                    | Symbol                               | Value                          | Unit       |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------|------------|

| Power Supply                                                                                              | V <sub>DD</sub>                      | 7.0                            | V          |

| External Card Power Supply and Level Shifter                                                              | SIM_VCC                              | 7.0                            | V          |

| Digital Input Voltage<br>Digital Input Current                                                            | STOP                                 | $-0.3 \le V \le V_{DD}$ $1.0$  | V<br>mA    |

| Digital Input Voltage<br>Digital Input Current                                                            | RESET                                | $-0.3 \le V \le V_{DD}$ $1.0$  | V<br>mA    |

| Digital Input Voltage<br>Digital Input Current                                                            | CLOCK                                | $-0.3 \le V \le V_{DD}$ $1.0$  | V<br>mA    |

| Digital Input Voltage<br>Digital Input Current                                                            | I/O                                  | $-0.3 \le V \le V_{DD}$ $1.0$  | V<br>mA    |

| Digital Output Voltage<br>Digital Output Current                                                          | SIM_RST                              | $-0.3 \le V \le SIM_VCC$<br>25 | V<br>mA    |

| Digital Input/Output Voltage<br>Digital Input/Output Current                                              | SIM_I/O                              | $-0.3 \le V \le SIM_VCC$<br>25 | V<br>mA    |

| Digital Output Voltage<br>Digital Output Current                                                          | SIM_CLK                              | $-0.3 \le V \le SIM_VCC$       | V<br>mA    |

| Human Body Model: $R = 1500 \Omega$ , $C = 100 pF$<br>SIM card side, pins 8, 9, 11 & 14<br>All other pins | ESD                                  | 6.0<br>2.0                     | kV<br>kV   |

| TSSOP-14 Package<br>Power Dissipation @ T <sub>A</sub> = +85°C<br>Thermal Resistance, Junction-to-Air     | P <sub>D</sub><br>R <sub>THhja</sub> | 275<br>145                     | mW<br>°C/W |

| Operating Ambient Temperature Range                                                                       | T <sub>A</sub>                       | -25 to +85                     | °C         |

| Operating Junction Temperature Range                                                                      | TJ                                   | -25 to +125                    | °C         |

| Maximum Junction Temperature                                                                              | T <sub>Jmax</sub>                    | +150                           | °C         |

| Storage Temperature Range                                                                                 | T <sub>stg</sub>                     | -65 to +150                    | °C         |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. Maximum electrical ratings are defined as those values beyond which damage to the device may occur at  $T_A = +25^{\circ}C$ .

### POWER SUPPLY SECTION (-25°C to +85°C)

| Rating                                                                                                                                                                                                                                                                                                                                                    | Symbol              | Pin | Min                            | Тур                     | Max                    | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|--------------------------------|-------------------------|------------------------|------|

| Power Supply                                                                                                                                                                                                                                                                                                                                              | V <sub>DD</sub>     | 1   | 2.7                            | _                       | 3.6                    | V    |

| Standby Supply Current @ No Input Clock, All Input Logic to H, No Load Connected to the SIM Interface.                                                                                                                                                                                                                                                    | I V <sub>DD</sub>   | 1   | -                              | 500                     | -                      | nA   |

| $      Ground Current, @ V_{DD} = 3.0 \text{ V}, \text{ Operating Conditions:} \\ PWR_ON = 0 \\ SIM_VCC = 5.0 \text{ V}, I_{CC} = 0 \text{ mA} \\ SIM_VCC = 5.0 \text{ V}, I_{CC} = 10 \text{ mA} \text{ (Note 2)} \\ SIM_VCC = 3.0 \text{ V}, I_{CC} = 0 \text{ mA} \\ SIM_VCC = 3.0 \text{ V}, I_{CC} = 6.0 \text{ mA} \text{ (Note 2)} \\            $ | I V <sub>DD</sub>   | 1   | -                              | 200<br>40               | 5.0<br>125<br>25       | μΑ   |

| External Card Power Supply at 5.0 V<br>@ 2.7 V $\leq V_{DD} \leq 3.6$ V, $I_{CC} = 10$ mA<br>External Card Power Supply at 3.0 V<br>@ 2.7 V $\leq V_{DD} \leq 3.6$ V, $I_{CC} = 10$ mA                                                                                                                                                                    | SIM_VCC             | 14  | 4.5<br>V <sub>DD</sub> – 50 mV | V <sub>DD</sub> – 25 mV | 5.5<br>V <sub>DD</sub> | V    |

| Output SIM Card Supply Voltage Turn On Time<br>Ct = 220 nF, Cout1 = 1.0 $\mu$ F $\pm$ 20%<br>V <sub>DD</sub> = 3.0 V, SIM_VCC = 5.0 V<br>V <sub>DD</sub> = 3.0 V, SIM_VCC = 3.0 V                                                                                                                                                                         | VCC <sub>TON</sub>  | 14  | -                              | 0.5                     | 1.0                    | ms   |

| $\begin{array}{l} \mbox{Output SIM Card Supply Voltage Turn Off Time} \\ \mbox{Ct} = 220 \ nF, \mbox{Cout1} = 1.0 \ \mu F \ \pm 20\% \ (Note 3) \\ \mbox{V}_{DD} = 2.7 \ V, \ \mbox{SIM}_V CC = 5.0 \ V, \ \mbox{@} \ \ V_{LOW} = 0.4 \ V \\ \mbox{V}_{DD} = 2.7 \ V, \ \ \mbox{SIM}_V CC = 3.0 \ V, \ \ \mbox{@} \ \ \ V_{LOW} = 0.4 \ V \end{array}$    | VCC <sub>TOFF</sub> | 14  | _                              | -                       | 300<br>300             | μs   |

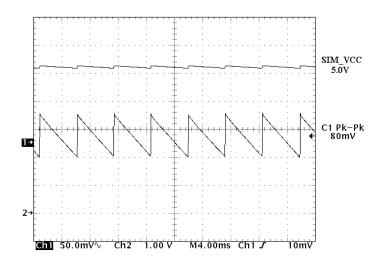

| Output Voltage Ripple (Note 4)<br>Ct = 220 nF, Cout1 = 1.0 $\mu$ F, Cout2 = 100 nF<br>V <sub>DD</sub> = 3.0 V, SIM_VCC = 5.0 V, I <sub>CC</sub> = 10 mA<br>(Not Relevant at SIM_VCC = 3.0 V)                                                                                                                                                              | VCC <sub>RIP</sub>  | 14  | -                              | -                       | 200                    | mV   |

| Input Peak Current During DC–DC Startup<br>@ $V_{DD}$ = 3.0 V, SIM_VCC = 5.0 V                                                                                                                                                                                                                                                                            | I <sub>DDpk</sub>   | 1   | -                              | 300                     | -                      | mA   |

| Input Average Current During Normal Operation,<br>@ $V_{DD} = 3.0 \text{ V}, \text{ SIM}_VCC = 5.0 \text{ V}$                                                                                                                                                                                                                                             | I <sub>DDavg</sub>  | 1   | _                              | 20                      | -                      | mA   |

| DC-DC Internal Oscillator                                                                                                                                                                                                                                                                                                                                 | Fosc                | _   | -                              | 800                     | _                      | kHz  |

The I<sub>DD</sub> current represents the absolute difference between the current absorbed by the load and the one absorbed by the chip.

A 350 μs delay must be observed by the external MPU prior to reactivate the SIM\_VCC output.

Using low ESR capacitors type (max 100 mΩ) is mandatory for Ct, Cout1 and Cout2 to reach the NCN6010 specifications. Ceramic type (VCP are V2D) approximate to the second (X5R or X7R) are recommended.

## DIGITAL INPUT SECTION CLOCK, RESET, I/O, STOP, MOD\_VCC, PWR\_ON

| Rating                                                                                                         | Symbol                                                | Pin                  | Min                   | Тур | Max                                                        | Unit                     |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------|-----------------------|-----|------------------------------------------------------------|--------------------------|

| High Level Input Voltage<br>Low Level Input Voltage<br>Input Rise Time<br>Input Fall Time<br>Input Capacitance | V <sub>IH</sub><br>V <sub>IL</sub><br>tr<br>tf<br>Cin | 2, 3<br>4, 5<br>6, 7 | 0.7 * V <sub>DD</sub> | _   | V <sub>DD</sub><br>0.3 * V <sub>DD</sub><br>50<br>50<br>10 | V<br>V<br>ns<br>ns<br>pF |

| Input @ 45% < Duty Cycle < 55%<br>Clock Rise Time<br>Clock Fall Time<br>Input Clock Capacitance                | CLOCK                                                 | 6                    | -                     | -   | 5.0<br>50<br>50<br>10                                      | MHz<br>ns<br>ns<br>pF    |

| Input/Output Data Transfer Frequency<br>I/O Rise Time<br>I/O Fall Time<br>Input I/O Capacitance                | I/O                                                   | 5                    | -                     | 15  | 160<br>0.8<br>0.8<br>10                                    | kHz<br>μs<br>μs<br>pF    |

#### SIM INTERFACE SECTION (Note 7)

| Rating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Symbol                      | Pin | Min                      | Тур | Max                                               | Unit                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|--------------------------|-----|---------------------------------------------------|--------------------------------|

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SIM_RST<br>Note 5           | 8   | SIM_VCC - 0.7<br>0       | -   | SIM_VCC<br>0.6<br>400<br>400                      | V<br>V<br>ns<br>ns             |

| $\begin{array}{l} SIM\_VCC = +3.0 \ V \\ Output \ RESET \ V_{OH} \ @ \ Isim\_rst = +200 \ \mu A \\ Output \ RESET \ V_{OL} \ @ \ Isim\_rst = -200 \ \mu A \\ Output \ RESET \ Rise \ Time \ @ \ Cout = 50 \ pF \\ Output \ RESET \ Fall \ Time \ @ \ Cout = 50 \ pF \end{array}$                                                                                                                                                                                                                                                                    |                             |     | 0.8 * SIM_VCC<br>0       |     | SIM_VCC<br>0.2 * SIM_VCC<br>400<br>400            | V<br>V<br>ns<br>ns             |

| $\begin{array}{l} SIM\_VCC = +5.0 \ V \\ Output Duty Cycle \\ Output Frequency \\ Output SIM\_CLK \ Rise \ Time \ @ \ Cout = 50 \ pF \\ Output \ SIM\_CLK \ Fall \ Time \ @ \ Cout = 50 \ pF \\ Output \ V_{OH} \ @ \ Isim\_clk = +20 \ \muA \\ Output \ V_{OL} \ @ \ Isim\_clk = -200 \ \muA \end{array}$                                                                                                                                                                                                                                          | SIM_CLK<br>Note 5<br>Note 6 | 9   | 40<br>0.7 * SIM_VCC<br>0 | _   | 60<br>5.0<br>18<br>18<br>SIM_VCC<br>0.5           | %<br>MHz<br>ns<br>ns<br>V<br>V |

| $\label{eq:simple} \begin{array}{l} SIM\_VCC = +3.0 \ V \\ Output \ Duty \ Cycle \\ Output \ Frequency \\ Output \ SIM\_CLK \ Rise \ Time \ @ \ Cout = 50 \ pF \\ Output \ SIM\_CLK \ Fall \ Time \ @ \ Cout = 50 \ pF \\ Output \ V_{OH} \ @ \ Isim\_clk = +20 \ \muA \\ Output \ V_{OL} \ @ \ Isim\_clk = -20 \ \muA \end{array}$                                                                                                                                                                                                                 |                             |     | 40<br>0.7 * SIM_VCC<br>0 |     | 60<br>5.0<br>18<br>18<br>SIM_VCC<br>0.2 * SIM_VCC | %<br>MHz<br>ns<br>Ns<br>V<br>V |

| $\label{eq:simple} \begin{array}{ c c c c c } SIM_VCC = +5.0 \ V \\ SIM_I/O \ Data \ Transfer \ Frequency \\ SIM_I/O \ Rise \ Time \ @ \ Cout = 50 \ pF \\ SIM_I/O \ Fall \ Time \ @ \ Cout = 50 \ pF \\ Output \ V_{OH} \ @ \ I_{SIM_IO} = +20 \ \mu\text{A}, \ V_{IH} = V_{DD} \\ Output \ V_{OL} \ @ \ I_{SIM_IO} = -1.0 \ \text{mA}, \\ V_{IL} \ I/O = 0 \ V \end{array}$                                                                                                                                                                       | SIM_I/O                     | 11  | 0.7 * SIM_VCC<br>0       | 15  | 160<br>0.8<br>0.8<br>SIM_VCC<br>0.4               | kHz<br>μs<br>μs<br>V<br>V      |

| $\begin{split} & \text{SIM}\_\text{VCC} = +3.0 \text{ V} \\ & \text{SIM}\_\text{I/O} \text{ Data Transfer Frequency} \\ & \text{SIM}\_\text{I/O} \text{ Rise Time } @ \text{ Cout} = 50 \text{ pF} \\ & \text{SIM}\_\text{I/O} \text{ Fall Time } @ \text{ Cout} = 50 \text{ pF} \\ & \text{Output V}_{OH} @ \text{ I}_{\text{SIM}\_IO} = +20  \mu\text{A}, \text{ V}_{\text{IH}} = \text{V}_{\text{DD}} \\ & \text{Output V}_{OL} @ \text{ I}_{\text{SIM}\_IO} = -1.0 \text{ mA}, \\ & \text{V}_{\text{IL}} \text{ I/O} = 0 \text{ V} \end{split}$ |                             |     | 0.7 * SIM_VCC<br>0       | 15  | 160<br>0.8<br>0.8<br>SIM_VCC<br>0.4               | kHz<br>μs<br>μs<br>V<br>V      |

| I/O Pull Up Resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I/O_RP                      | 5   | 13                       | 20  | _                                                 | kΩ                             |

| Card I/O Pull Up Resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SIM_I/O_RP                  | 11  | 13                       | 20  | -                                                 | kΩ                             |

5. Internal NMOS device, biased to V<sub>DD</sub>, provides low impedance when SIM\_V<sub>CC</sub> is disconnected to sustain GSM 11.11–200 µA input current test.

6. The SIM\_CLK clock can operate up to 10 MHz, but the rise and fall time are not guaranteed to be fully within the ISO7816 specification over the temperature range. Typically, tr and tf are 12 ns @ CRD\_CLK = 10 MHz.

7. Digital inputs undershoot < -0.30 V, Digital inputs overshoot < 0.30 V.</li>

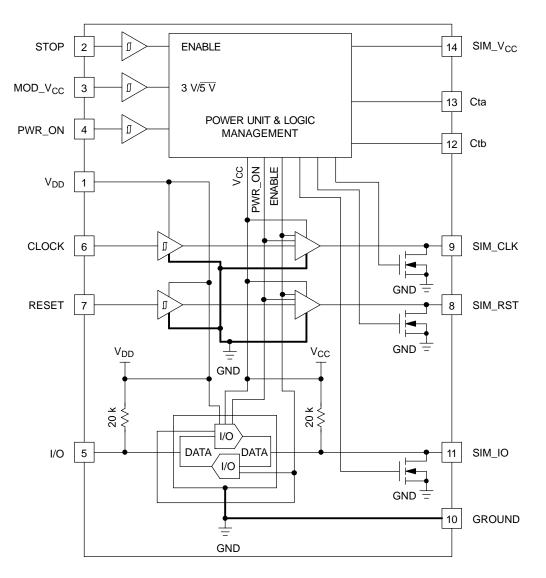

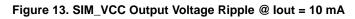

### Card Supply Charge Pump Converter

The NCN6010 device provides three pins to control the operation of the interface as depicted in Table 1. The built–in charge pump converter circuit provides either a 3.0 V or a 5.0 V output voltage as defined by the programming mode. The external capacitor connected across pins 12 and 13 is used to generate the step up voltage. Since the device operates at 800 kHz typically, one must use high quality, Low ESR type, ceramic capacitor (220 nF recommended). The second external capacitor, connected across pin 14 and GND, smooths the output voltage coming from the Charge Pump. A high quality, Low ESR capacitor is necessary to achieve the SIM\_VCC ripple voltage (1.0  $\mu$ F Ceramic type is recommended).

The setting of the SIM\_VCC voltage, using MOD\_VCC = 0 or 1, can only be made when PWR\_ON is Low. Consequently, a new supply voltage adjustment is performed by first deactivating the SIM card, followed by reactivating it with the new supply voltage. The SIM\_VCC voltage can be reprogrammed straightforward when the output voltage increases from 3.0 V to 5.0 V. On the other

hand, although it is possible to change the SIM\_VCC voltage from 5.0 V to 3.0 V, it is recommended to switch off the Charge Pump prior to reprogram the SIM\_VCC voltage from the high 5.0 V to a low 3.0 V.

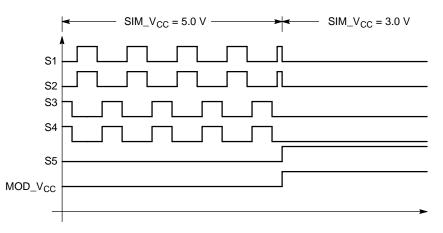

The DC–DC converter operates under two modes as defined by the logic level present at MOD\_VCC/pin 3:

- MOD\_VCC = 0 SIM\_CC =  $5.0 \text{ V}, \pm 10\%$ . This is the default condition at start up.

- $\label{eq:MOD_VCC} \begin{array}{l} \text{MOD}\_\text{VCC} = 1 & \text{The Charge Pump is not activated and the} \\ & \text{SIM}\_\text{VCC voltage is equal to the } V_{\text{DD}} \\ & \text{supply minus the internal maximum} \\ & 50 \text{ mV drop.} \end{array}$

The NCN6010 provides a POWER DOWN sequence, according to the ISO7816–3 specification.

Since a built–in active pull down MOS pull the SIM\_VCC pin to ground when the smart card is deactivated, a 350  $\mu$ s minimum delay must be observed prior to reactivate the power supply. This timing assumes a 1.0  $\mu$ F external reservoir capacitor connected across SIM\_VCC and Ground.

| STOP | MOD_VCC | PWR_ON | Operation Mode                                                                                                                                                                  |

|------|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | X       | Х      | The SIM card supply is disabled, the SIM_VCC pin is Open, SIM_RST = L, SIM_I/O = L, SIM_CLK = L                                                                                 |

| 1    | 0       | 0      | The NCN6010 is in the power down mode. The SIM card supply is disabled,<br>SIM_VCC = Open, SIM_RST = L, SIM_CLK = L, SIM_IO = L.<br>The SIM_VCC voltage is programmed to 5.0 V. |

| 1    | 1       | 0      | The NCN6010 is in the power down mode. The SIM card supply is disabled,<br>SIM_VCC = Open, SIM_RST = L, SIM_CLK = L, SIM_IO = L.<br>The SIM_VCC voltage is programmed to 3.0 V. |

| 1    | X       | 1      | The NCN6010 is in normal operating mode. The SIM card supply is enabled, SIM_VCC voltage is the one previously programmed, all the SIM interface pins are active.               |

#### **Table 1. Programming Functions**

#### **Table 1: Programming Mode**

When the card is removed, the STOP pin shall be asserted Low to disable the NCN6010. A mechanical switch, or equivalent, can be either sensed by the MPU, or directly connected to pin 2, to handle the procedure.

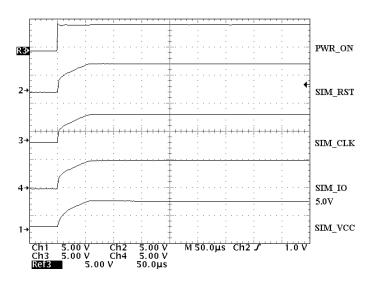

#### **Power Up Sequence**

When the charge pump is activated,  $MOD_VCC = Low$ , the SIM card related level shifter pins are biased to the 5.0 V

voltage. When the output voltage starts from zero, as depicted in Figure 3, a 50  $\mu$ s stabilization delay (typical) is necessary to make sure all the output signals are biased at the nominal 5.0 V voltage. To avoid a card transaction error, the user must take this delay into account and program the chip accordingly.

Figure 3. Power On Sequence

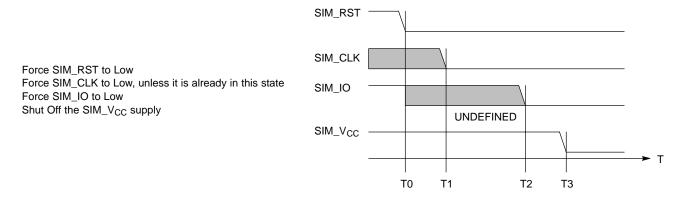

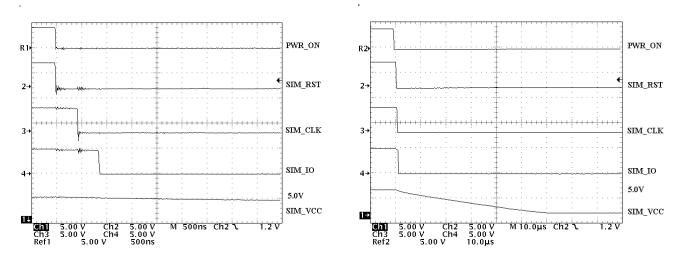

#### **Power Down Operation**

The power down mode can be initiated by either the PWR\_ON or by the STOP pin condition. In both cases, the communication I/O session is terminated immediately, according to the ISO7816–3 sequence as depicted in Figure 4. When the PWR\_ON signal is set Low, the NCN6010 goes to the power down mode. According to the ISO7816–3 procedure defined to deactivate the SIM contacts, the input pins I/O, CLOCK and RESET must be Low before the PWR\_ON is taken Low. When the

PWR\_ON is Low, the SIM\_IO, SIM\_CLK and SIM\_RST pins are forced to Low and the SIM\_VCC pin is left floating.

When the STOP signal is Low, the SIM\_IO, SIM\_CLK and SIM\_RST are forced Low, the SIM\_VCC being left floating, until the STOP pin is taken High again.

When the card is extracted, the external MPU shall detect the operation and run the Power Down of the card by forcing PWR\_ON input to Low. The NCN6010 fulfills the power sequence as defined by the ISO/CEI 7816–3 norm (see oscillogram given in Figure 5).

Figure 4. ISO7816-3 Power Down Sequence

Figure 5. Power Down Sequence Oscillogram

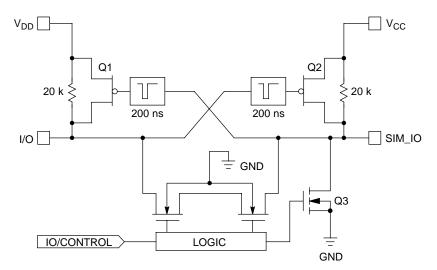

#### Level Shifters

When the SIM card voltage is either higher or lower than the MPU  $V_{DD}$  supply, the level shifters can be reprogrammed to cope with the expected output voltage. When the MPU and the SIM card operate under the same supply voltage, the DC–DC converter is not activated (SIM\_VCC =  $V_{DD}$  –50 mV) and the signals go directly through the level shifters. The bi-directional I/O line provides a way to automatically adapt the voltage difference between the  $\mu$ CU and the SIM card. In addition with the pull up resistor, an active pull up circuit (Figure 6 Q1 and Q2) provides a fast charge of the stray capacitance, yielding a rise time fully within the ISO/EMV specifications.

Figure 6. Basic I/O Line Interface

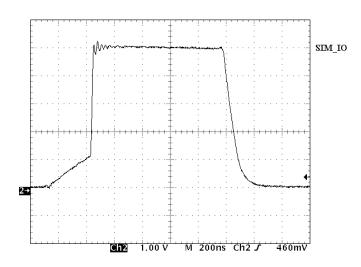

The typical waveform provided in Figure 7 shows how the accelerator operates. During the first 200 ns (typical), the slope of the rise time is solely a function of the pull up resistor associated with the stray capacitance. During this period, the PMOS devices are not activated since the input voltage is below their Vgs threshold. When the input slope

crosses the Vgsth, the opposite one shot is activated, providing a low impedance to charge the capacitance, thus increasing the rise time as depicted in Figure 7. The same mechanism applies for the opposite side of the line to make sure the system is optimum.

Figure 7. SIM\_IO Rise and Fall Time Oscillogram

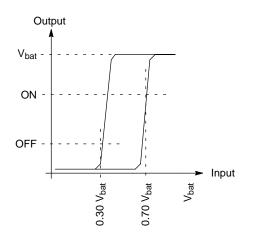

#### **Input Schmitt Triggers**

All the Logic Input pins have built–in Schmitt trigger circuits to prevent the NCN6010 against uncontrolled operation. The typical dynamic characteristics of the related pins are depicted in Figure 8.

The output signal is guaranteed to go High when the input voltage is above 0.70\*Vbat, and will go Low when the input voltage is below 0.30 \* Vbat.

Figure 8. Typical Schmitt Trigger Characteristic

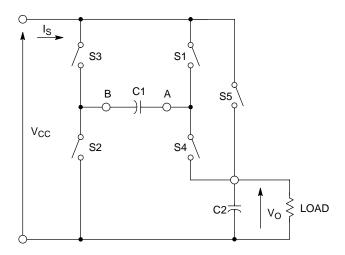

#### **Charge Pump Converter**

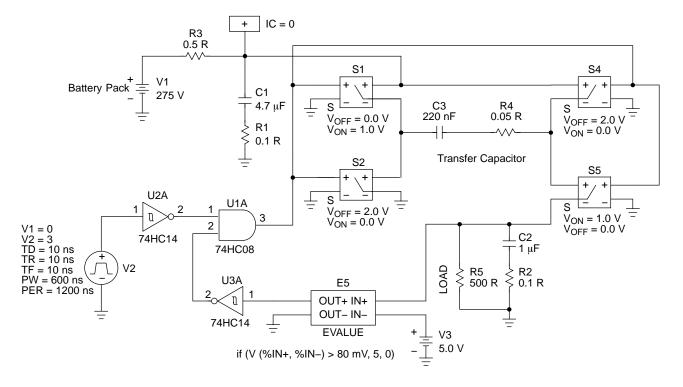

The converter uses a switched capacitor technique to increase the SIM\_VCC voltage up to 5.0 V from a 3.3 V typical battery. The concept, depicted in Figure 9, charges the transfer capacitor C1 up to the Vcc value, then connects this capacitor is series with the input voltage–output

reservoir network. The voltage developed across the load is, theoretically, twice the battery voltage, but the system must takes into account the losses associated with the power switches and the internal ohmic drops.

Figure 9. Basic Charge Pump Converter

When the output voltage is programmed to 3.0 V, the clocks are inactive and the load is directly connected to the battery by means of switch S5. The SIM\_VCC voltage follows the input value, minus the drop coming from the internal resistance. The current is limited by the Ron of the power device S5 and t he output voltage will decrease as the load current increases above 20 mA (typical). Figure 10 illustrates the theoretical waveforms.

Figure 10. Basic Charge Pump Operating Timings

When the NCN6010 is programmed in the 5.0 V output voltage, the clocks are activated, switch S5 is disconnected and the output voltage is the result of the C1 charge transfer into the output load. The current is limited by three mains parameters:

- the Ron of the switching MOS (S1 through S4)

- the operating frequency

- the C1/C2 ratio and their ESR

The first parameters are depending upon the internal structure and size of the NMOS/PMOS devices used to

design the chip. The third parameter is adjustable by the user and, beside the micro farad values, the type of capacitors plays a significant role. As a matter of fact, using a low cost electrolytic model will ruin the efficiency due to the high ESR of such a capacitor. It is highly recommended to use ceramic types, preferably from the X5R or X7R series, to achieve the efficiency and the SIM\_VCC output voltage ripple. Table 2 summarizes the characteristics of the most common type of capacitors.

| Manufacturers | Type/Serie         | Format | Max Value   | Tolerance | Typ. Z @ 500 kHz     |

|---------------|--------------------|--------|-------------|-----------|----------------------|

| MURATA        | CERAMIC/GRM225     | 0805   | 10 μF/6.3 V | +80%/-20% | $30 \text{ m}\Omega$ |

| VISHAY        | Tantalum/594C/593C | 1206   | 10 μF/16 V  | -         | 450 mΩ               |

| VISHAY        | Electrolytic/94SV  | 1206   | 10 μF/10 V  | -20%/+20% | 400 mΩ               |

#### Table 2. Comparison of Capacitor Types

It is clear that, with nearly half an ohm of resistance is series with the pure capacitor, the tantalum or the electrolytic type will generate high voltage spikes and poor regulation in the high frequency operating charge pump built into the NCN6010. Moreover, with ESR in the 3.0 Ohm range, low cost capacitors are not suitable for this application.

Figure 11 provides the schematic diagram of the simulated charge pump circuit. Although this schematic does not

represent the accurate internal structure of the NCN6010, it can be used for engineering purpose. The ABM devices S1, S2, S4 and S5 have been defined in the PSPICE model to represent the NMOS and PMOS used in the silicon. The ESR value of C2 and C3 can be adjusted, at PSPICE level, to cope with any type of external capacitors and are useful to double check the behavior of the system as a function of the external passives components.

Figure 11. Charge Pump Simulation Schematic Diagram

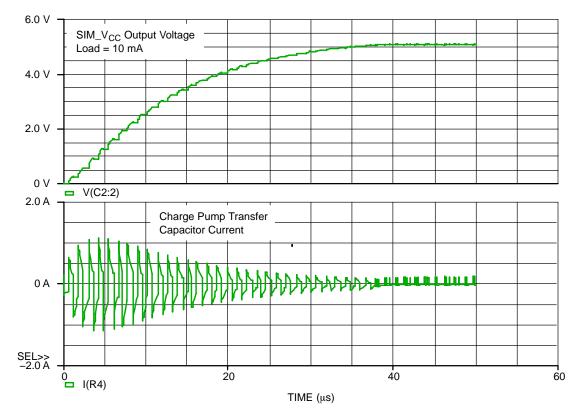

The operating waveforms are given in Figure 12 to illustrate the high peak current flowing in the transfer

capacitor. The real ripple voltage, coming from the engineering board, is given in Figure 13.

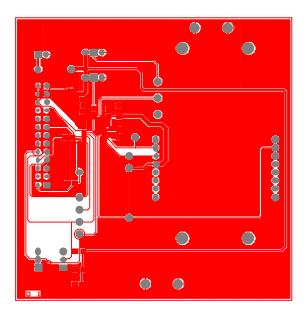

The layout of the PCB is a key parameter to avoid the voltage spikes that could pollute the rest of the system. Figure 16 represents a typical printed circuit lay out, based on the schematic diagram given in Figure 14, highlighting the large ground plane used in this engineering tool.

Obviously, a GSM application will use much less area, but cares must be observed to locate the capacitors as close as possible to the integrated circuit associated pins.

Capacitors C1, C2, C3, C4 and C5 are ceramic, X7R, 10 V, surface mount.

Figure 15. Engineering Test Board Silk Layer

Figure 16. Engineering Test Board Top Layer

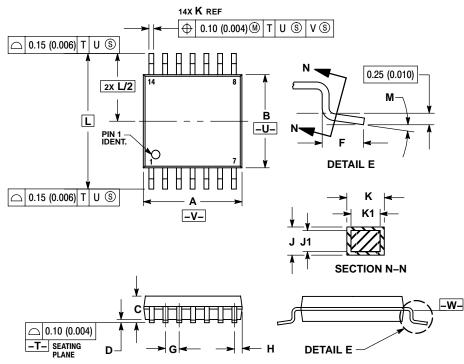

#### PACKAGE DIMENSIONS

TSSOP-14 DTB SUFFIX CASE 948G-01 ISSUE A

NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE. 4. DIMENSION B DOES NOT INCLUDE

- DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL

- NOT EXCEED 0.25 (0.010) PER SIDE. 5. DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 6. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY. 7. DIMENSION A AND B ARE TO BE

- DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE –W–.

|     | MILLIN   | IETERS | INC       | HES   |  |

|-----|----------|--------|-----------|-------|--|

| DIM | MIN      | MAX    | MIN       | MAX   |  |

| Α   | 4.90     | 5.10   | 0.193     | 0.200 |  |

| В   | 4.30     | 4.50   | 0.169     | 0.177 |  |

| С   |          | 1.20   |           | 0.047 |  |

| D   | 0.05     | 0.15   | 0.002     | 0.006 |  |

| F   | 0.50     | 0.75   | 0.020     | 0.030 |  |

| G   | 0.65     | BSC    | 0.026 BSC |       |  |

| Н   | 0.50     | 0.60   | 0.020     | 0.024 |  |

| J   | 0.09     | 0.20   | 0.004     | 0.008 |  |

| J1  | 0.09     | 0.16   | 0.004     | 0.006 |  |

| κ   | 0.19     | 0.30   | 0.007     | 0.012 |  |

| K1  | 0.19     | 0.25   | 0.007     | 0.010 |  |

| L   | 6.40 BSC |        | 0.252 BSC |       |  |

| М   | 0 °      | 8 °    | 0 °       | 8 °   |  |

ON Semiconductor and IIII are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use persons, and reasonable attorney fees andising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use persons and sensing out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized to applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 61312, Phoenix, Arizona 85082–1312 USA Phone: 480–829–7710 or 800–344–3860 Toll Free USA/Canada Fax: 480–829–7709 r800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850 ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.