# LC708728V

## High-Performance 24-Bit 192 kHz D/A Converter Features Built-in Electronic Volume Control and DSD Support

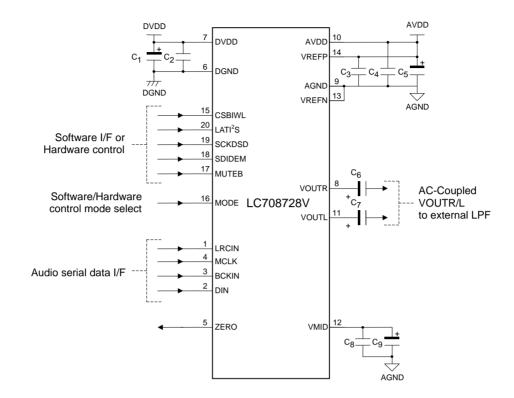

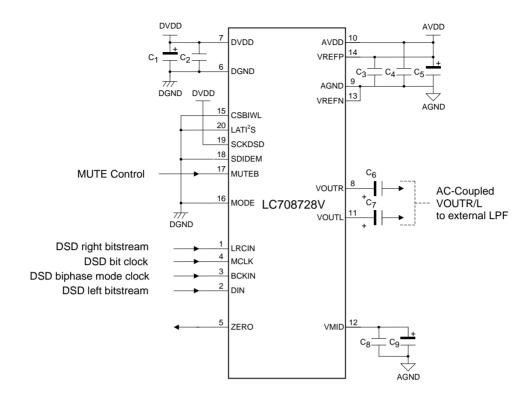

The LC708728V is a high-performance stereo D/A converter developed for high-end audio applications such as DVD systems, home theater systems, and digital TV sets. It supports 16 to 32-bit word length PCM data as its digital input format, and supports sampling rates up to 192 kHz. It can also be used in a DSD (Direct Stream Digital) compatible mode by supplying a 64-bit stream for each input channel.

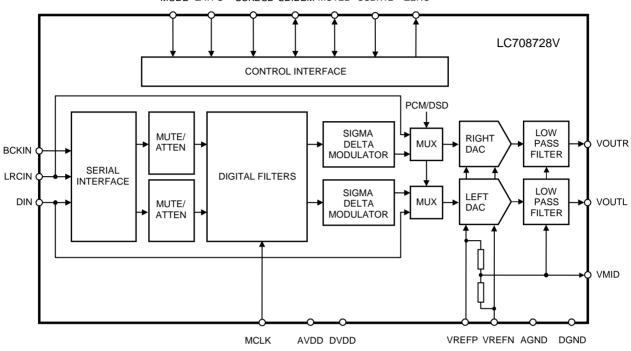

This IC is formed from serial interface port, digital interpolation filter, multi-bit  $\sum \Delta$  converter, and stereo D/A converter functions. It includes muting and attenuator circuits that can be controlled individually for each channel.

The operating mode can be selected to be either software control mode or hardware control mode. In software control mode, the IC can be controlled by a microcontroller over a 2-wire or 3-wire serial port. In this mode, a wide range of functions, including muting, attenuation, and phase inversion can be controlled. DSD mode can only be used in hardware control mode.

This IC is optimal for use as an interface for AC-3, DTS, and MPEG audio decoders for surround control, and for use in DVD players that support DVD-A.

## **Features**

• Stereo D/A converter that supports both 24-bit PCM and 1-bit DSD

ullison

- Signal-to-noise ratio: 106 dB (48 kHz, A weighted)

- Total harmonic distortion: -97 dB

- D/A converter sampling frequency: 8 kHz to 192 kHz

- Control modes: Either software or hardware mode can be selected.

- Built-in microprocessor interface (either 2-wire or 3-wire)

- Input data formats I<sup>2</sup>S, left/right justified, DSP 16, 20, 24, and 32 bits

- Built-in electronic volume control with independent left and right channel controls

0 to 127.5 dB in 0.5 dB steps

- Operating voltage range: 3.0 to 5.5 V

- Package: 20-pin SSOP

## **Applications**

- DVD audio and DVD "universal" players

- Home theater systems

- Digital TVs

- Digital broadcast receivers

- This LSI is designed and produced by Wolfson Microelectronics Ltd., and sold by SANYO Electric Co., Ltd. based on corroboration between Wolfson Microelectronics Ltd. and SANYO Electric Co., Ltd.

- CCB is the registered trademark of SANYO Electric Co., Ltd.

- CCB is the original bus format of SANYO Electric Co., Ltd. and all bus addresses are controlled by SANYO Electric Co., Ltd.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co.,Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

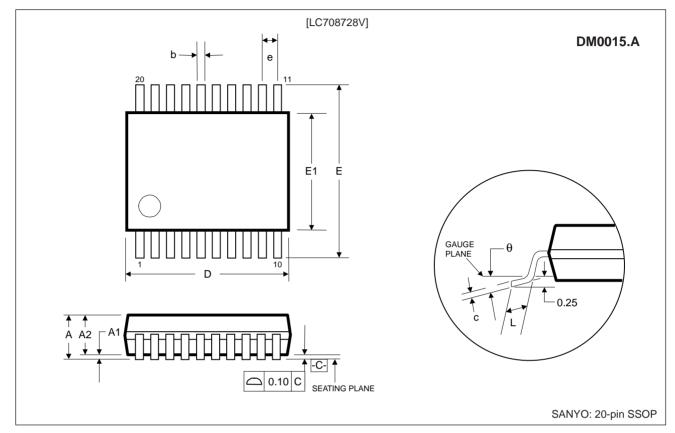

## **Package Dimensions**

unit: mm

## 20-pin SSOP

| Symbols        | Dimendions<br>(mm) |          |      |  |  |  |  |

|----------------|--------------------|----------|------|--|--|--|--|

| -              | MIN                | NOM      | MAX  |  |  |  |  |

| A              |                    |          | 2.0  |  |  |  |  |

| A <sub>1</sub> | 0.05               |          |      |  |  |  |  |

| A <sub>2</sub> | 1.65               | 1.75     | 1.85 |  |  |  |  |

| b              | 0.22               |          | 0.38 |  |  |  |  |

| С              | 0.09               |          | 0.25 |  |  |  |  |

| D              | 6.90               | 7.20     | 7.50 |  |  |  |  |

| е              |                    | 0.65 BSC |      |  |  |  |  |

| E              | 7.40               | 7.80     | 8.20 |  |  |  |  |

| E <sub>1</sub> | 5.00               | 5.30     | 5.60 |  |  |  |  |

| L              | 0.55               | 0.75     | 0.95 |  |  |  |  |

| θ              | 0°                 | 4°       | 8°   |  |  |  |  |

|                |                    |          |      |  |  |  |  |

| REF:           | JEDEC.95, MO-150   |          |      |  |  |  |  |

Notes: A. Linear dimensions are all stated in mm. B. This figure is subject to change without notification.

C. The body dimensions do not include burrs and protrusions of up to 0.20 mm.

D. Complies with JEDEC.95 MO-150, VARIATION=AE. Further details are provided in these specifications.

## **Block Diagram**

#### MODE LATI<sup>2</sup>S SCKDSD SDIDEM MUTEB CSBIWL ZERO

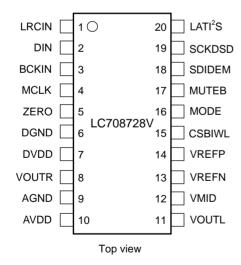

## **Pin Assignment**

## **Pin Functions**

| 1         LRCIN         Digital input         D/A converter sampling rate clock input: PCM input mode<br>Right channel DSD bit stream input: DSD input mode           2         DIN         Digital input         Serial audio data input: PCM input mode<br>Left channel DSD bit stream input: DSD input mode           3         BCKIN         Digital input         Audio data bit clock input         DSD input mode           4         MCLK         Digital output (open drain)         IZD detection flag         Digital cloupt (open drain)         IZD detection flag           6         DSDD         Power supply         Digital VD         Digital VD         Digital VD           7         DVDD         Power supply         Digital VD         Right channel D/A converter output         Audio data bit clock input           6         DSDN         Power supply         Digital VD         Analog GND           7         DVDD         Power supply         Analog VD         Analog VD           11         VOUT         Analog output         Left channel D/A converter output         Audio-rainee VD           13         VREFN         Power supply         D/A converter n-channel VREF pin. Connect this pin to AVDD.<br>(Do not supply a level lower than AVQD to this pin.)         D/A converter p-channel VREF pin. Connect this pin to AVDD.<br>(Do not supply a level lower than AVQD to this pin.)           14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pin No. | Pin     | Туре                        | Function                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-----------------------------|-----------------------------------------------------------------------------|

| Image: Constraint of the second sec | 4       |         | Disital issue               | D/A converter sampling rate clock input: PCM input mode                     |

| 2         DIN         Digital input         Left channel DSD bit stream input: DSD input mode           3         BCKIN         Digital input         Audio data bit clock input           4         MCLK         Digital input         Master clock input           5         ZERO         Digital output (open drain)         IZD detection flag           6         DGND         Power supply         Digital GND           7         DVDD         Power supply         Digital Chance D/A converter output           9         AGND         Power supply         Analog GND           10         AVDD         Power supply         Analog GND           11         VOUTL         Analog output         Left channel D/A converter output           12         VMID         Analog output         Left channel D/A converter output           13         VREFN         Power supply         Analog Vop           14         VREFP         Power supply         D/A converter n-channel VREF pin. Connect this pin to AVDD.           15         CSBIVL         Digital input (pulled up)         Software mode: 3-wire serial control this pelcet           16         MODE         Digital input (pulled down)         Control mode selection (Low: hardware, high: software)           17         MUTEB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1       | LRCIN   |                             | Right channel DSD bit stream input: DSD input mode                          |

| Image: Section of the section of th | 0       | DIN     | Disital issue               | Serial audio data input: PCM input mode                                     |

| 4       MCLK       Digital input       Master clock input         5       ZERO       Digital output (open drain)       IZD detection flag         6       DGND       Power supply       Digital GND         7       DVDD       Power supply       Digital VDD         8       VOUTR       Analog output       Right channel D/A converter output         9       AGND       Power supply       Analog GND         10       A/VDD       Power supply       Analog VDD         11       VOUTL       Analog output       Left channel D/A converter output         12       VMID       Analog output       Left channel D/A converter output         13       VREFN       Power supply       D/A converter n-channel VREF pin. Connect this pin to AGND.<br>(Do not supply a level lower than ACND to this pin.)         14       VREFP       Power supply       D/A converter p-channel VREF pin. Connect this pin to AVDD.<br>(Do not supply a level lower than AVDD to this pin.)         15       CSBIWL       Digital input (pulled up)       Software mode: 3-wire serial control chip select<br>Hardware mode: Input word length         16       MODE       Digital input (pulled down)       Control mode selection (Low: hardware, high: software)         17       MUTEB       Bidirectional digital       Muting control<br>(Low: muting on, high: mut                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2       | DIN     |                             | Left channel DSD bit stream input: DSD input mode                           |

| 5       ZERO       Digital output (open drain)       IZD detection flag         6       DGND       Power supply       Digital GND         7       DVDD       Power supply       Digital VDD         8       VOUTR       Analog output       Right channel D/A converter output         9       AGND       Power supply       Analog GND         10       AVDD       Power supply       Analog VDD         11       VOUTL       Analog output       Left channel D/A converter output         12       VMID       Analog output       Left channel D/A converter output         13       VREFN       Power supply       D/A converter n-channel VREF pin. Connect this pin to AGND.<br>(Do not supply a level lower than AGND to this pin.)         14       VREFP       Power supply       D/A converter p-channel VREF pin. Connect this pin to AVDD.<br>(Do not supply a level lower than AVDD to this pin.)         15       CSBIWL       Digital input (pulled up)       Software mode: 3-wire serial control chip select<br>Hardware mode: Input word length         16       MODE       Digital input (pulled down)       Control mode selection (Low: hardware, high: software)         17       MUTEB       Bidirectional digital       Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)         18       SDIDEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3       | BCKIN   | Digital input               | Audio data bit clock input                                                  |

| 6         DGND         Power supply         Digital GND           7         DVDD         Power supply         Digital GND           8         VOUTR         Analog output         Right channel D/A converter output           9         AGND         Power supply         Analog GND           10         AVDD         Power supply         Analog GND           11         VOUTL         Analog output         Left channel D/A converter output           12         VMID         Analog output         Left channel D/A converter output           13         VREFN         Power supply         Mid-rail decoupling point           14         VREFP         Power supply         D/A converter n-channel VREF pin. Connect this pin to AGND.<br>(Do not supply a level lower than AGND to this pin.)           15         CSBIWL         Digital input (pulled up)         D/A converter p-channel VREF pin. Connect this pin to AV <sub>DD</sub> .<br>(Do not supply a level lower than AV <sub>DD</sub> to this pin.)           16         MODE         Digital input (pulled down)         Software mode: 3-wire serial control chip select<br>Hardware mode: 1nput word length           17         MUTEB         Bidirectional digital         Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)           18         SDIDEM         Bidirectional digital         Software mode: 3-wire o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4       | MCLK    | Digital input               | Master clock input                                                          |

| 7         DVDD         Power supply         Digital V <sub>DD</sub> 8         VOUTR         Analog output         Right channel D/A converter output           9         AGND         Power supply         Analog GND           10         AVDD         Power supply         Analog V <sub>DD</sub> 11         VOUTL         Analog output         Left channel D/A converter output           12         VMID         Analog output         Left channel D/A converter output           13         VREFN         Power supply         D/A converter n-channel VREF pin. Connect this pin to AGND.<br>(Do not supply a level lower than AGND to this pin.)           14         VREFP         Power supply         D/A converter p-channel VREF pin. Connect this pin to AV <sub>DD</sub> .<br>(Do not supply a level lower than AV <sub>DD</sub> to this pin.)           15         CSBIWL         Digital input (pulled up)         D/A converter p-channel VREF pin. Connect this pin to AV <sub>DD</sub> .<br>(Do not supply a level lower than AV <sub>DD</sub> to this pin.)           16         MODE         Digital input (pulled down)         Control mode selection (Low: hardware, high: software)           17         MUTEB         Bidirectional digital         Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)           18         SDIDEM         Bidirectional digital         Software mode: 3-wire or 2-wire serial control lock input<br>Hardware mode: D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5       | ZERO    | Digital output (open drain) | IZD detection flag                                                          |

| 8       VOUTR       Analog output       Right channel D/A converter output         9       AGND       Power supply       Analog GND         10       AVDD       Power supply       Analog VD         11       VOUTL       Analog output       Left channel D/A converter output         12       VMID       Analog output       Left channel D/A converter output         13       VREFN       Power supply       Mid-rail decoupling point         13       VREFN       Power supply       D/A converter n-channel VREF pin. Connect this pin to AGND.<br>(Do not supply a level lower than AGND to this pin.)         14       VREFP       Power supply       D/A converter p-channel VREF pin. Connect this pin to AVDD.<br>(Do not supply a level lower than AVDD to this pin.)         15       CSBIWL       Digital input (pulled up)       Software mode: 3-wire serial control chip select<br>Hardware mode: Input word length         16       MODE       Digital input (pulled down)       Control mode selection (Low: hardware, high: software)         17       MUTEB       Bidirectional digital       Software mode: 3-wire or 2-wire serial control data input<br>Hardware mode: Deemphasis selection         18       SDIDEM       Bidirectional digital       Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: DSD bit stream operation selection         19       SCKDSD       Di                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6       | DGND    | Power supply                | Digital GND                                                                 |

| 9       AGND       Power supply       Analog GND         10       AVDD       Power supply       Analog GND         11       VOUTL       Analog output       Left channel D/A converter output         12       VMID       Analog output       Left channel D/A converter output         13       VREFN       Power supply       D/A converter n-channel VREF pin. Connect this pin to AGND.<br>(Do not supply a level lower than AGND to this pin.)         14       VREFP       Power supply       D/A converter p-channel VREF pin. Connect this pin to AV <sub>DD</sub> .<br>(Do not supply a level lower than AGND to this pin.)         15       CSBIWL       Digital input (pulled up)       Software mode: 3-wire serial control chip select<br>Hardware mode: Input word length         16       MODE       Digital input (pulled down)       Control mode selection (Low: hardware, high: software)         17       MUTEB       Bidirectional digital       Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)         18       SDIDEM       Bidirectional digital       Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: Deemphasis selection         19       SCKDSD       Digital input (pulled down)       Software mode: 3-wire serial control load input         20       LATI2S       Digital input (pulled down)       Software mode: 3-wire serial control load input <td>7</td> <td>DVDD</td> <td>Power supply</td> <td>Digital V<sub>DD</sub></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7       | DVDD    | Power supply                | Digital V <sub>DD</sub>                                                     |

| 10         AVDD         Power supply         Analog V <sub>DD</sub> 11         VOUTL         Analog output         Left channel D/A converter output           12         VMID         Analog output         Mid-rail decoupling point           13         VREFN         Power supply         D/A converter n-channel VREF pin. Connect this pin to AGND.<br>(Do not supply a level lower than AGND to this pin.)           14         VREFP         Power supply         D/A converter p-channel VREF pin. Connect this pin to AV <sub>DD</sub> .<br>(Do not supply a level lower than AGND to this pin.)           15         CSBIWL         Digital input (pulled up)         Software mode: 3-wire serial control chip select<br>Hardware mode: Input word length           16         MODE         Digital input (pulled down)         Control mode selection (Low: hardware, high: software)           17         MUTEB         Bidirectional digital         Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)           18         SDIDEM         Bidirectional digital         Software mode: 3-wire or 2-wire serial control data input<br>Hardware mode: Deemphasis selection           19         SCKDSD         Digital input (pulled down)         Software mode: SWire or 2-wire serial control lock input<br>Hardware mode: DSD bit stream operation selection           20         LATI2S         Digital input (pulled down)         Software mode: 3-wire serial control load input <td>8</td> <td>VOUTR</td> <td>Analog output</td> <td>Right channel D/A converter output</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8       | VOUTR   | Analog output               | Right channel D/A converter output                                          |

| 11       VOUTL       Analog output       Left channel D/A converter output         12       VMID       Analog output       Mid-rail decoupling point         13       VREFN       Power supply       D/A converter n-channel VREF pin. Connect this pin to AGND.<br>(Do not supply a level lower than AGND to this pin.)         14       VREFP       Power supply       D/A converter p-channel VREF pin. Connect this pin to AV <sub>DD</sub> .<br>(Do not supply a level lower than AV <sub>DD</sub> to this pin.)         15       CSBIWL       Digital input (pulled up)       Software mode: 3-wire serial control chip select<br>Hardware mode: Input word length         16       MODE       Digital input (pulled down)       Control mode selection (Low: hardware, high: software)         17       MUTEB       Bidirectional digital       Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)         18       SDIDEM       Bidirectional digital       Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: 0-wire serial control clock input<br>Hardware mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: 3-wire serial control clock input         19       SCKDSD       Digital input (pulled down)       Software mode: 3-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9       | AGND    | Power supply                | Analog GND                                                                  |

| 12VMIDAnalog outputMid-rail decoupling point13VREFNPower supplyD/A converter n-channel VREF pin. Connect this pin to AGND.<br>(Do not supply a level lower than AGND to this pin.)14VREFPPower supplyD/A converter p-channel VREF pin. Connect this pin to AV <sub>DD</sub> .<br>(Do not supply a level lower than AV <sub>DD</sub> to this pin.)15CSBIWLDigital input (pulled up)Software mode: 3-wire serial control chip select<br>Hardware mode: Input word length16MODEDigital input (pulled down)Control mode selection (Low: hardware, high: software)17MUTEBBidirectional digitalMuting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)18SDIDEMBidirectional digitalSoftware mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: Deemphasis selection19SCKDSDDigital input (pulled down)Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: DSD bit stream operation selection20LATI2SDigital input (pulled up)Software mode: 3-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10      | AVDD    | Power supply                | Analog V <sub>DD</sub>                                                      |

| 13       VREFN       Power supply       D/A converter n-channel VREF pin. Connect this pin to AGND.<br>(Do not supply a level lower than AGND to this pin.)         14       VREFP       Power supply       D/A converter p-channel VREF pin. Connect this pin to AV <sub>DD</sub> .<br>(Do not supply a level lower than AV <sub>DD</sub> to this pin.)         15       CSBIWL       Digital input (pulled up)       Software mode: 3-wire serial control chip select<br>Hardware mode: Input word length         16       MODE       Digital input (pulled down)       Control mode selection (Low: hardware, high: software)         17       MUTEB       Bidirectional digital       Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)         18       SDIDEM       Bidirectional digital       Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: Deemphasis selection         19       SCKDSD       Digital input (pulled down)       Software mode: S-wire or 2-wire serial control clock input<br>Hardware mode: DSD bit stream operation selection         20       LATI2S       Digital input (pulled up)       Software mode: 3-wire or 2-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11      | VOUTL   | Analog output               | Left channel D/A converter output                                           |

| 13       VREFN       Power supply       (Do not supply a level lower than AGND to this pin.)         14       VREFP       Power supply       D/A converter p-channel VREF pin. Connect this pin to AV <sub>DD</sub> .<br>(Do not supply a level lower than AV <sub>DD</sub> to this pin.)         15       CSBIWL       Digital input (pulled up)       Software mode: 3-wire serial control chip select<br>Hardware mode: Input word length         16       MODE       Digital input (pulled down)       Control mode selection (Low: hardware, high: software)         17       MUTEB       Bidirectional digital       Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)         18       SDIDEM       Bidirectional digital       Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: 3-wire or 2-wire serial control clock input         19       SCKDSD       Digital input (pulled down)       Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: DSD bit stream operation selection         20       LATI2S       Dioital input (pulled up)       Software mode: 3-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12      | VMID    | Analog output               | Mid-rail decoupling point                                                   |

| 14       VREFP       Power supply       D/A converter p-channel VREF pin. Connect this pin to AV <sub>DD</sub> .<br>(Do not supply a level lower than AV <sub>DD</sub> to this pin.)         15       CSBIWL       Digital input (pulled up)       Software mode: 3-wire serial control chip select<br>Hardware mode: Input word length         16       MODE       Digital input (pulled down)       Control mode selection (Low: hardware, high: software)         17       MUTEB       Bidirectional digital       Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)         18       SDIDEM       Bidirectional digital       Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: 3-wire or 2-wire serial control clock input         19       SCKDSD       Digital input (pulled down)       Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: DSD bit stream operation selection         20       LATI2S       Digital input (pulled up)       Software mode: 3-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12      |         | EFN Power supply            | D/A converter n-channel VREF pin. Connect this pin to AGND.                 |

| 14       VREFP       Power supply       (Do not supply a level lower than AV <sub>DD</sub> to this pin.)         15       CSBIWL       Digital input (pulled up)       Software mode: 3-wire serial control chip select<br>Hardware mode: Input word length         16       MODE       Digital input (pulled down)       Control mode selection (Low: hardware, high: software)         17       MUTEB       Bidirectional digital       Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)         18       SDIDEM       Bidirectional digital       Software mode: 3-wire or 2-wire serial control data input<br>Hardware mode: 0eemphasis selection         19       SCKDSD       Digital input (pulled down)       Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: DSD bit stream operation selection         20       LATI2S       Digital input (pulled up)       Software mode: 3-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15      | VKEFIN  |                             | (Do not supply a level lower than AGND to this pin.)                        |

| 15       CSBIWL       Digital input (pulled up)       Software mode: 3-wire serial control chip select<br>Hardware mode: Input word length         16       MODE       Digital input (pulled down)       Control mode selection (Low: hardware, high: software)         17       MUTEB       Bidirectional digital       Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)         18       SDIDEM       Bidirectional digital       Software mode: 3-wire or 2-wire serial control data input<br>Hardware mode: 3-wire or 2-wire serial control clock input         19       SCKDSD       Digital input (pulled down)       Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: DSD bit stream operation selection         20       LATI2S       Digital input (pulled up)       Software mode: 3-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.4     |         | Power aupply                | D/A converter p-channel VREF pin. Connect this pin to AV <sub>DD</sub> .    |

| 15       CSBIWL       Digital input (pulled up)       Hardware mode: Input word length         16       MODE       Digital input (pulled down)       Control mode selection (Low: hardware, high: software)         17       MUTEB       Bidirectional digital       Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)         18       SDIDEM       Bidirectional digital       Software mode: 3-wire or 2-wire serial control data input<br>Hardware mode: Deemphasis selection         19       SCKDSD       Digital input (pulled down)       Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: DSD bit stream operation selection         20       LATI2S       Dioital input (pulled up)       Software mode: 3-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14      | VKEFF   |                             | (Do not supply a level lower than AV <sub>DD</sub> to this pin.)            |

| 16       MODE       Digital input (pulled down)       Control mode selection (Low: hardware, high: software)         17       MUTEB       Bidirectional digital       Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)         18       SDIDEM       Bidirectional digital       Software mode: 3-wire or 2-wire serial control data input<br>Hardware mode: 0 Eemphasis selection         19       SCKDSD       Digital input (pulled down)       Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: DSD bit stream operation selection         20       LATI2S       Digital input (pulled up)       Software mode: 3-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15      | CODIMI  | Digital input (pulled up)   | Software mode: 3-wire serial control chip select                            |

| 17       MUTEB       Bidirectional digital       Muting control<br>(Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)         18       SDIDEM       Bidirectional digital       Software mode: 3-wire or 2-wire serial control data input<br>Hardware mode: Deemphasis selection         19       SCKDSD       Digital input (pulled down)       Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: DSD bit stream operation selection         20       LATI2S       Digital input (pulled up)       Software mode: 3-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15      | CODIVL  | Digital liput (pulled up)   | Hardware mode: Input word length                                            |

| 17       MUTEB       Bidirectional digital       (Low: muting on, high: muting off, high impedance (Z) : enable auto-muting)         18       SDIDEM       Bidirectional digital       Software mode: 3-wire or 2-wire serial control data input         18       SDIDEM       Bidirectional digital       Software mode: 0eemphasis selection         19       SCKDSD       Digital input (pulled down)       Software mode: 0eemphasis selection         20       LATI2S       Digital input (pulled up)       Software mode: 0eemphase serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16      | MODE    | Digital input (pulled down) | Control mode selection (Low: hardware, high: software)                      |

| 18       SDIDEM       Bidirectional digital       Software mode: 3-wire or 2-wire serial control data input         19       SCKDSD       Digital input (pulled down)       Software mode: Deemphasis selection         20       LATI2S       Digital input (pulled up)       Software mode: 3-wire or 2-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17      | MUTER   | Ridiractional digital       | Muting control                                                              |

| 18     SDIDEM     Bidirectional digital     Hardware mode: Deemphasis selection       19     SCKDSD     Digital input (pulled down)     Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: DSD bit stream operation selection       20     LATI2S     Digital input (pulled up)     Software mode: 3-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17      | WOTED   | Didirectional digital       | (Low: muting on, high: muting off, high impedance (Z) : enable auto-muting) |

| 19     SCKDSD     Digital input (pulled down)     Software mode: Deemphasis selection       20     LATI2S     Digital input (pulled up)     Software mode: 3-wire or 2-wire serial control clock input<br>Hardware mode: DSD bit stream operation selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19      | SDIDEM  | Ridiractional digital       | Software mode: 3-wire or 2-wire serial control data input                   |

| 19     SCKDSD     Digital input (pulled down)     Hardware mode: DSD bit stream operation selection       20     LATI2S     Digital input (pulled up)     Software mode: 3-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10      | SDIDLIM | Didirectional digital       | Hardware mode: Deemphasis selection                                         |

| 20 LATI2S Digital input (pulled up) Software mode: 3-wire serial control load input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10      | SCKDSD  | Digital input (pulled down) | Software mode: 3-wire or 2-wire serial control clock input                  |

| 20 LATI2S Digital input (pulled up)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13      | 301030  |                             | Hardware mode: DSD bit stream operation selection                           |

| Hardware mode: Input data format selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20      |         | Digital input (pulled up)   | Software mode: 3-wire serial control load input                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20      | 241123  |                             | Hardware mode: Input data format selection                                  |

Note: Each digital input pin is provided with a Schmitt trigger input buffer.

#### **Absolute Maximum Ratings**

The absolute maximum ratings given here are only stress ratings. This device may be permanently damaged if it is operated continuously above any of these limits. Device function operating limits under the specified test conditions and the guaranteed performance specifications are shown in the electrical characteristics.

ESD Sensitive Device. This device is fabricated in a CMOS process. As a result, it can be easily damaged by excessive electrostatic voltages. Appropriate anti-static measures must be taken when handling or storing this device.

| Parameter                                              | Symbol | Conditions |            | Unit |            |      |

|--------------------------------------------------------|--------|------------|------------|------|------------|------|

| Falameter                                              | Symbol | Conditions | min        | typ  | max        | Unit |

| Digital system supply voltage                          |        |            | -0.3       |      | +7         | V    |

| Analog system supply voltage                           |        |            | -0.3       |      | +7         | V    |

| Digital input voltage range                            |        |            | DGND - 0.3 |      | DVDD + 0.3 | V    |

| Analog input voltage range                             |        |            | AGND - 0.3 |      | AVDD + 0.3 | V    |

| Master clock frequency                                 |        |            |            |      | 50         | MHz  |

| Operating temperature                                  | Topr   |            | -25        |      | +85        | °C   |

| Storage temperature                                    | Tstg   |            | -65        |      | +150       | °C   |

| Maximum mounting temperature<br>(soldering time: 10 s) |        |            |            |      | +240       | °C   |

| Maximum mounting temperature<br>(soldering time: 2 m)  |        |            |            |      | +183       | °C   |

Note: The potential difference between the analog system ground and the digital system ground must be 0.3 V or less.

## **Allowable Operating Ranges**

| Parameter                                  | Symbol     | Test Conditions | Ratings |     |      |      |  |

|--------------------------------------------|------------|-----------------|---------|-----|------|------|--|

| Farameter                                  | Symbol     | Test Conditions | min     | typ | max  | Unit |  |

| Digital system supply voltage              | DVDD       |                 | 3.0     |     | 5.5  | V    |  |

| Analog system supply voltage               | AVDD       |                 | 3.0     |     | 5.5  | V    |  |

| GND                                        | AGND, DGND |                 |         | 0   |      | V    |  |

| Potential difference between DGND and AGND |            |                 | -0.3    | 0   | +0.3 | V    |  |

| Analog system supply current               |            | AVDD = 5 V      |         | 19  |      | mA   |  |

| Digital system supply current              |            | DVDD = 5 V      |         | 8   |      | mA   |  |

| Analog system supply current               |            | AVDD = 3.3 V    |         | 18  |      | mA   |  |

| Digital system supply current              |            | DVDD = 3.3 V    |         | 4   |      | mA   |  |

## **Electrical Characteristics**

Test conditions at Ta = 25°C, AVDD, DVDD = 5 V, AGND = 0 V, DGND = 0 V, fs = 48 kHz, MCLK = 256 fs (Unless otherwise specified.)

| Parameter                           | Cumhal                 | Test Conditions        |                                   | Ratings                | tings                             |      |  |

|-------------------------------------|------------------------|------------------------|-----------------------------------|------------------------|-----------------------------------|------|--|

|                                     | Symbol Test Conditions |                        | min                               | typ                    | max                               | Unit |  |

| [Digital Logic Levels (TTL levels)] |                        |                        |                                   |                        |                                   |      |  |

| Low-level input voltage             | VIL                    |                        |                                   |                        | 0.8                               | V    |  |

| High-level input voltage            | V <sub>IH</sub>        |                        | 2.0                               |                        |                                   | V    |  |

| Low-level output voltage            | V <sub>OL</sub>        | I <sub>OL</sub> = 1 mA |                                   |                        | AGND + 0.3 V                      | V    |  |

| High-level output voltage           | V <sub>OH</sub>        | I <sub>OH</sub> = 1 mA | AVDD - 0.3 V                      |                        |                                   | V    |  |

| [Analog Reference Levels]           |                        |                        |                                   |                        |                                   |      |  |

| Reference voltage                   |                        | VMID                   | (VREFP –<br>VREFN) /<br>2 – 50 mV | (VREFP –<br>VREFN) / 2 | (VREFP –<br>VREFN) /<br>2 + 50 mV | v    |  |

| Voltage divider resistance          | R <sub>VMID</sub>      |                        |                                   | 12                     |                                   | kΩ   |  |

Continued on next page.

Continued from preceding page.

| Parameter                                          | Symbol  | Test Conditions                                                    | Ratings |                        |     |                  |

|----------------------------------------------------|---------|--------------------------------------------------------------------|---------|------------------------|-----|------------------|

| Parameter                                          | Symbol  |                                                                    | min     | typ                    | max | - Unit           |

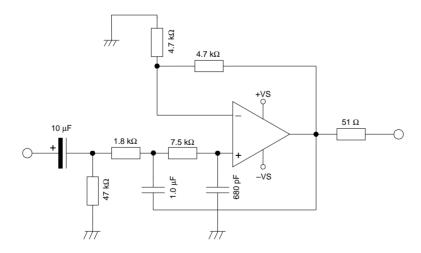

| [D/A Converter Output (Load = $10 \text{ k}\Omega$ | 50 pF)] | · ·                                                                |         |                        |     |                  |

| 0 dB Fs, Full scale output voltage                 |         | At DAC outputs                                                     |         | 1.1 × AVDD/5           |     | Vrms             |

| SNR (*1, 2, 3)                                     |         | A-weighted when fs = 48 kHz                                        | 100     | 106                    |     | dB               |

| SNR (*1, 2, 3)                                     |         | A-weighted when fs = 96 kHz                                        |         | 106                    |     | dB               |

| SNR (*1, 2, 3)                                     |         | A-weighted when fs = 192 kHz                                       |         | 106                    |     | dB               |

| SNR (*1, 2, 3)                                     |         | A-weighted when fs = 48 kHz<br>AVDD, DVDD = 3.3 V                  |         | 105                    |     | dB               |

| SNR (*1, 2, 3)                                     |         | A-weighted when fs = 96 kHz<br>AVDD, DVDD = 3.3 V                  |         | 103                    |     | dB               |

| SNR (*1, 2, 3)                                     |         | Not 'A' weighted<br>when fs = 48 kHz                               |         | 106                    |     | dB               |

| THD (*1, 2, 3)                                     |         | 1 kHz, 0 dBFs                                                      |         | -97                    |     | dB               |

| THD + N (Dynamic range, *2)                        |         | 1 kHz, –60 dBFs                                                    | 100     | 106                    |     | dB               |

| D/A converter channel separation                   |         |                                                                    |         | 100                    |     | dB               |

| [Analog Output Levels]                             | ·       | · · ·                                                              |         | ·                      |     |                  |

|                                                    |         | Load = 10 k $\Omega$ , 0 dBFs                                      |         | 1.1                    |     | V <sub>RMS</sub> |

| Output level                                       |         | Load = $10 \text{ k}\Omega$ , 0 dBFs,<br>(AVDD = $3.3 \text{ V}$ ) |         | 0.726                  |     | V <sub>RMS</sub> |

| Inter-channel gain mismatch                        |         |                                                                    |         | ±1                     |     | %FSR             |

|                                                    |         | To midrail or a.c. coupled                                         |         | 1                      |     | kΩ               |

| Minimum load resistance                            |         | To midrail or a.c. coupled<br>(AVDD = 3.3 V)                       |         | 600                    |     | Ω                |

| Maximum load capacitance                           |         | 5 V or 3.3 V                                                       |         | 100                    |     | pF               |

| DC output level                                    |         |                                                                    |         | (VREFP –<br>VREFN) / 2 |     | V                |

| [Power On Reset (POR)]                             |         |                                                                    | 1       | l                      |     |                  |

| POR threshold value                                |         |                                                                    |         | 2.4                    |     | V                |

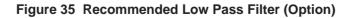

Notes:\*1.SNR is measured for the 20 to 20 kHz bandwidth with a 1 kHz full scale input and a silent input (all bits 0) and with an A-weighting filter inserted. \*2. All characteristics measurements are performed with both a 20 kHz low-pass filter and an A-weighting filter inserted. Measurement in this state results in a higher THD + N and a lower SNR than those of the normal electrical characteristics. The low-pass filter is also effective for out-of-band noise, and although it has no audible effect, it does influence the characteristics shown above.

\*3. VMID must be decoupled with 10  $\mu$ F and 0.1  $\mu$ F capacitors.

(Using values smaller than these will degrade the device characteristics.)

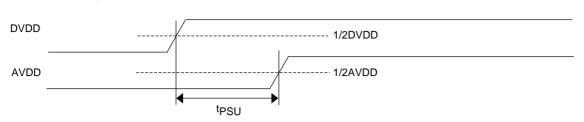

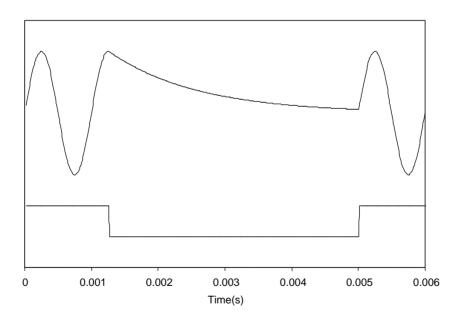

## **Power Supply Timing**

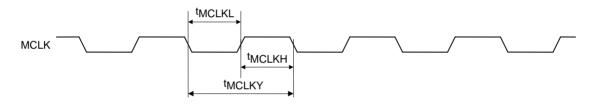

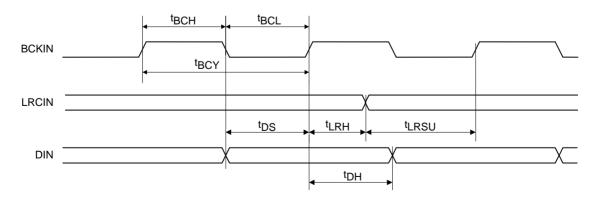

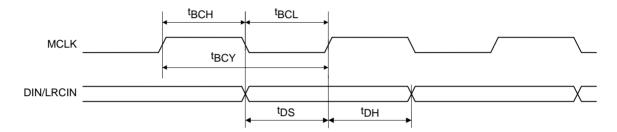

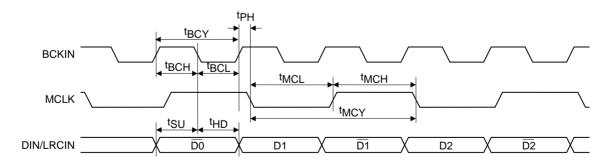

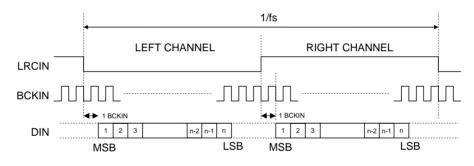

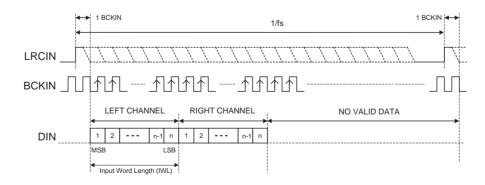

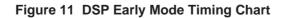

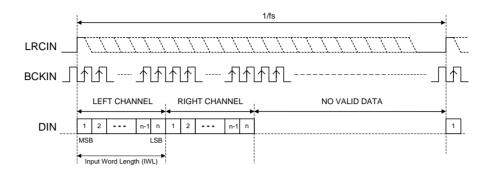

Figure 1 Power Supply Timing Requirements