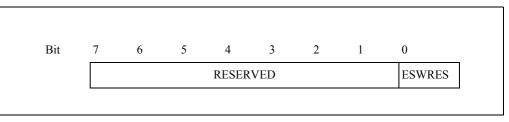

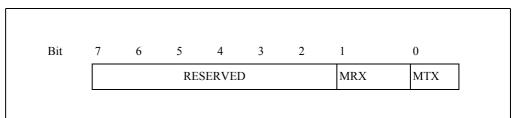

# GMS30C7201

# **Data Sheet**

Issued: December 1998 Copyright Advanced RISC Machines Ltd (ARM) 1998 Copyright Hynix Semiconductor Inc.1999 All rights reserved

#### **Proprietary Notice**

Hynix logo are trademarks of Hynix Semiconductor Inc.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by Hynix in good faith. However, all warranties implied or expressed, including but not limited to implied warranties or merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. Hynix Inc shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

#### **Document Status**

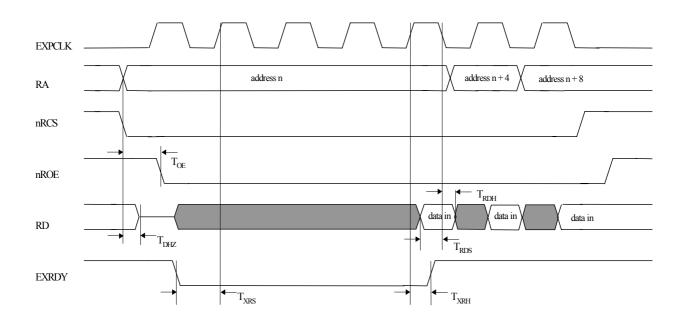

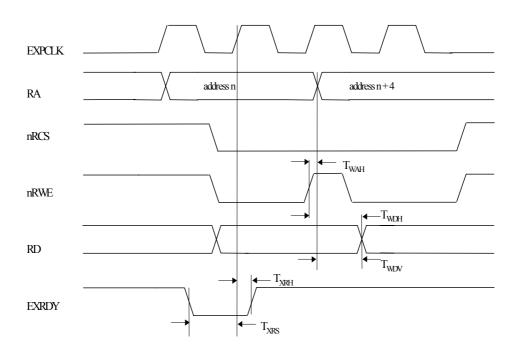

The document's status is displayed in a banner at the bottom of each page. This describes the document's confidentiality and its information status.

Information status is one of:

|                      | Information on a potential product                                                                |

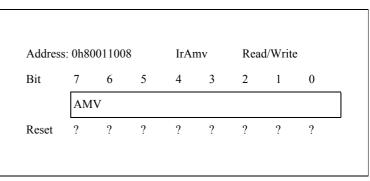

|----------------------|---------------------------------------------------------------------------------------------------|

| Preliminary<br>Final | Current information on a product under development<br>Complete information on a developed product |

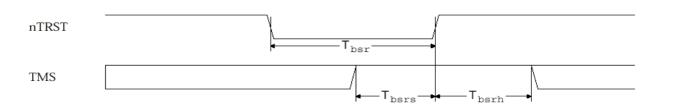

|                      | F                                                                                                 |

#### **Change Log**

| Issue                     | Date                                                          | By                               | Change                                                             |

|---------------------------|---------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------|

| A-01<br>A-02<br>A<br>B-01 | August 1997<br>December 1997<br>January 1998<br>December 1998 | PAW<br>JM, PG<br>JM, PG<br>PS,KC | First draft<br>Second draft<br>First Release<br>Add timing details |

| C-01                      | June 1999                                                     | NAMIL                            | Second Release                                                     |

Introduction

ii

#### Introduction

| Preface-ii | GMS30C7201 Data Sheet hynix                                                                                                                                                           |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | • 360-pin BGA package                                                                                                                                                                 |

|            | • 3.3V supply voltage                                                                                                                                                                 |

|            | 0.35mm process                                                                                                                                                                        |

|            | JTAG debug interface and boundary scan                                                                                                                                                |

|            | - PLL                                                                                                                                                                                 |

|            | - DAC and interface module (sound output)                                                                                                                                             |

|            | - ADC and interface module (touch panel)                                                                                                                                              |

|            | - USB (target)                                                                                                                                                                        |

|            | - Synchronous Serial Interface module for MMC Card                                                                                                                                    |

|            | - GPIO                                                                                                                                                                                |

|            | <ul> <li>Keyboard control interface</li> </ul>                                                                                                                                        |

|            | <ul> <li>AFE (Analog Front End or CODEC) interface</li> </ul>                                                                                                                         |

|            | <ul> <li>Infrared communications (IrDA support for 4Mbps and lower rates)</li> <li>2 UARTs (16C550 compatible)</li> </ul>                                                             |

|            | <ul> <li>Real-time clock (32.768kHz oscillator)</li> <li>Infrared communications (IrDA support for 4Mbps and lower rates)</li> </ul>                                                  |

|            | - VGA Controller with on-chip DACs (for direct drive of monitors)                                                                                                                     |

|            | - LCD Controller for mono/color STN and TFT LCD                                                                                                                                       |

|            | - Power management unit                                                                                                                                                               |

|            | - PCMCIA II and Compact Flash Controller                                                                                                                                              |

|            | - Memory controller for ROM, Flash, SRAM, SDRAM                                                                                                                                       |

|            | - Interrupt Controller                                                                                                                                                                |

|            | - Timer                                                                                                                                                                               |

|            | - Multi-channel DMA                                                                                                                                                                   |

|            | <ul> <li>On-chip peripherals with individual power-down:</li> </ul>                                                                                                                   |

|            | <ul> <li>Supports Little Endian operating system</li> </ul>                                                                                                                           |

|            | <ul> <li>512-byte instruction cache for Piccolo DSP</li> </ul>                                                                                                                        |

|            | <ul><li>Memory management unit for WindowsCE</li><li>Piccolo DSP(supports softmodem)</li></ul>                                                                                        |

|            | <ul> <li>8Kbytes combined instruction/data cache</li> <li>Momory management unit for WindowsCE</li> </ul>                                                                             |

|            | 32-bit ARM7TDMI RISC static CMOS CPU core                                                                                                                                             |

| Features   |                                                                                                                                                                                       |

| Factures   |                                                                                                                                                                                       |

|            | include smart phones, Internet appliances, car navigation, particularly where Windows CE support is required.                                                                         |

|            | and data terminal running the Microsoft Windows CE operating system. Other applications                                                                                               |

|            | The GMS30C7201 provides an excellent solution for personal digital assistants(PDAs)                                                                                                   |

|            | The power management features result in very low power consumption.                                                                                                                   |

|            | sound playback and a touch panel interface. Piccolo enables softmodems to be used, and an on chip CODEC interface enables a low-cost modem solution.                                  |

|            | DMA support for external SDRAM memory. The GMS30C7201 also supports voice recording,                                                                                                  |

|            | The on-chip peripherals include keyboard controller, VGA and LCD controller complete with                                                                                             |

|            | and system interface logic to interface with various types of devices. GMS30C7201 is a highly-<br>modular design based on the AMBA bus architecture between CPU and internal modules. |

|            | other applications described below. The device incorporates an ARM720T CPU, Piccolo DSP,                                                                                              |

|            | The GMS30C7201 is a highly-integrated microprocessor for personal digital assistants, and                                                                                             |

- 60MHz operation frequency

- Low power consumption

### GMS30C7201 System Overview

# Contents

| 1 | Introdu          | ction                             | 1-1 |

|---|------------------|-----------------------------------|-----|

|   | 1.1              | Introduction                      | 1-2 |

| 2 | Signal D         | Description                       | 2-1 |

|   | 2.1              | Signal Description for GMS30C7201 | 2-2 |

|   | 2.2              | Package Details                   | 2-7 |

|   | 2.3              | Pin List                          | 2-8 |

| 3 | Archited         | cture Overview                    | 3-1 |

|   | 3.1              | Internal bus structure            | 3-2 |

|   | 3.2              | SDRAM controller                  | 3-4 |

|   | 3.3              | Peripheral DMA                    | 3-5 |

|   | 3.4              | Power management                  | 3-7 |

|   | 3.5              | Performance                       | 3-8 |

| 4 | ARM72            | 0T Macrocell                      | 4-1 |

|   | 4.1              | ARM720T Macrocell                 | 4-2 |

| 5 | <b>Piccolo</b> 1 | Macrocell                         | 5-1 |

|   | 5.1              | Piccolo Macrocell                 | 5-2 |

| 6 | Memory           | у Мар                             | 6-1 |

|   | 6.1              | Introduction                      | 6-2 |

|   | 6.2              | Peripheral Register Map Summary   | 6-5 |

|   | 6.3              | High-speed APB Peripherals        | 6-7 |

| 7 | PMU              | & PLL                             |     |

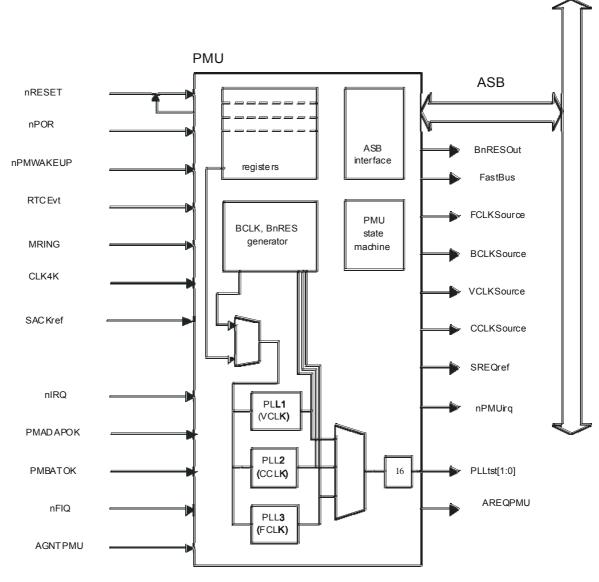

|   | 7.1              | Overview                          | 7-2 |

|   | 7.2              | Block Diagram                     | 7-3 |

Contents-1

7-

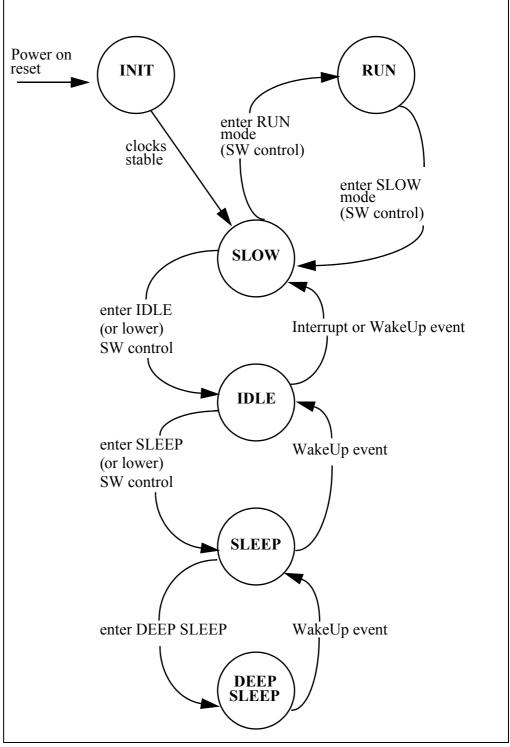

|    | 7.3          | Power management states                            | 7-5            |

|----|--------------|----------------------------------------------------|----------------|

|    | 7.4          | Power management                                   | 7-6            |

|    | 7.5          | PMU Registers                                      | 7-8            |

| 8  | SDRAM        | Controller                                         | 8-1            |

|    | 8.1          | SDRAM Controller Specification                     | 8-2            |

|    | 8.2          | Features                                           | 8-3            |

|    | 8.3          | Supported Memory Devices                           | 8-4            |

|    | 8.4          | SDRAM Control Registers                            | 8-5            |

|    | 8.5          | Power-up Initialization of the SDRAMs              | 8-10           |

|    | 8.6          | SDRAM Memory Map                                   | 8-11           |

|    | 8.7          | AMBA Accesses and Arbitration                      | 8-15           |

|    | 8.8          | Merging Write Buffer                               | 8-17           |

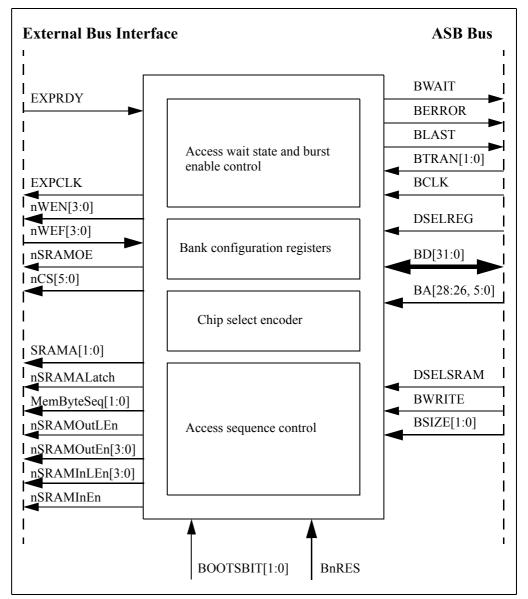

| 9  | Static Mo    | emory Interface                                    | 9-1            |

|    | 9.1          | Overview                                           | 9-2            |

|    | 9.2          | Hardware Interface and Signal Description          | 9-3            |

|    | 9.3          | Functional Description                             | 9-5            |

|    | 9.4          | Register Description                               | 9-7            |

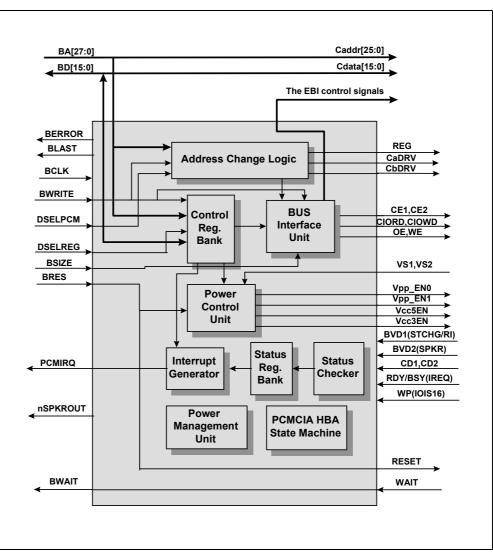

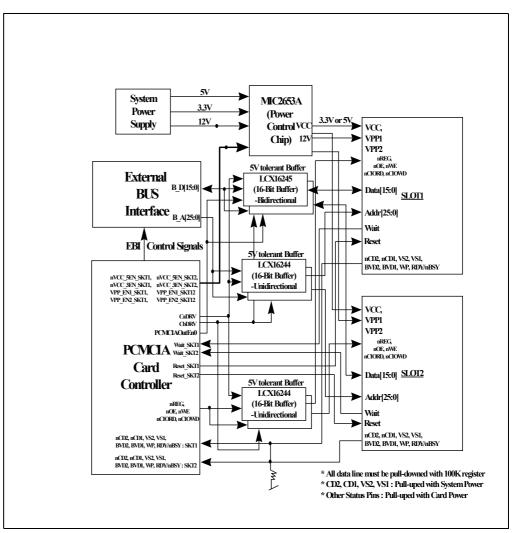

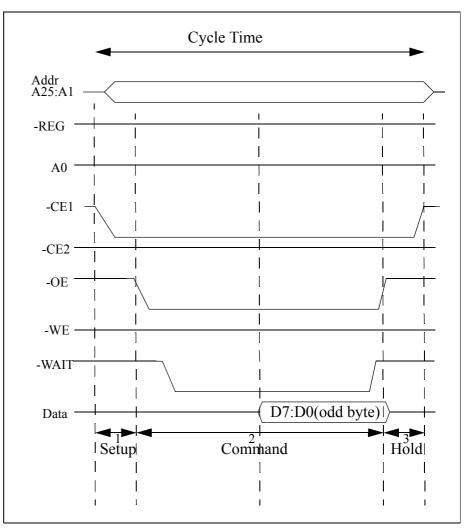

| 10 | PCMCIA       | Interface                                          | 10-1           |

|    | 10.1         | Overview                                           | 10-2           |

|    | 10.2         | Register Description and Map                       | 10-10          |

|    | 10.3         | Functional Description                             | 10-23          |

| 11 | LCD & V      | VGA Controllers                                    | 11-1           |

|    | 11.1         | Overview                                           | 11-2           |

|    | 11.2         | Video operation                                    | 11-3           |

|    | 11.3         | Video Control register                             | 11-7           |

|    | 11.4         | LCD Timing 0 Register                              | 11-9           |

|    | 11.5<br>11.6 | LCD Timing 1 Register<br>LCD Timing 2 Register     | 11-11<br>11-13 |

|    | 11.0         | VGA Timing 2 Register                              | 11-13          |

|    | 11.7         | VGA Timing 3 Register                              | 11-10          |

|    | 11.0         | LCD DMA Base Address Register                      | 11-18          |

|    | 11.10        | LCD DMA Channel Current Address Register           | 11-19          |

|    | 11.11        | LCD Controller Status/Mask and Interrupt Registers | 11-20          |

|    | 11.12        | LCD Palette registers                              | 11-22          |

|    | 11.13        | VGA Test Register                                  | 11-23          |

|    | 11.14        | Grayscaler Test Registers                          | 11-24          |

|    | 11.15        | Video Controller Register Locations                | 11-25          |

| 12 | Fast AM      | BA Peripherals                                     | 12-1           |

|    | 12.1         | Introduction                                       | 12-2           |

|    | 12.2         | Peripheral DMA Controller                          | 12-3           |

|    | 12.3         | Medium and Fast Infrared Module                    | 12-17          |

|    | 12.4         | General Configuration                              | 12-26          |

|    | 12.5         | Transmitting Data                                  | 12-27          |

|    |              | -                                                  |                |

|    | 12.6         | Receiving Data                                     | 12-29          |

|    |              | -                                                  |                |

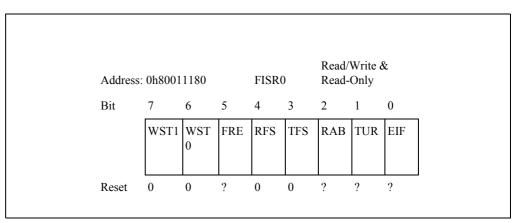

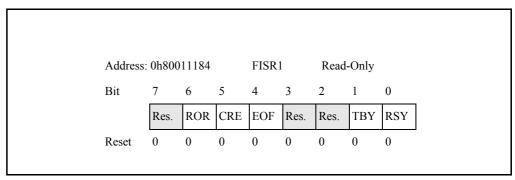

|    | 12.9      | Fast Infrared Port (FIr)                            | 12-40 |

|----|-----------|-----------------------------------------------------|-------|

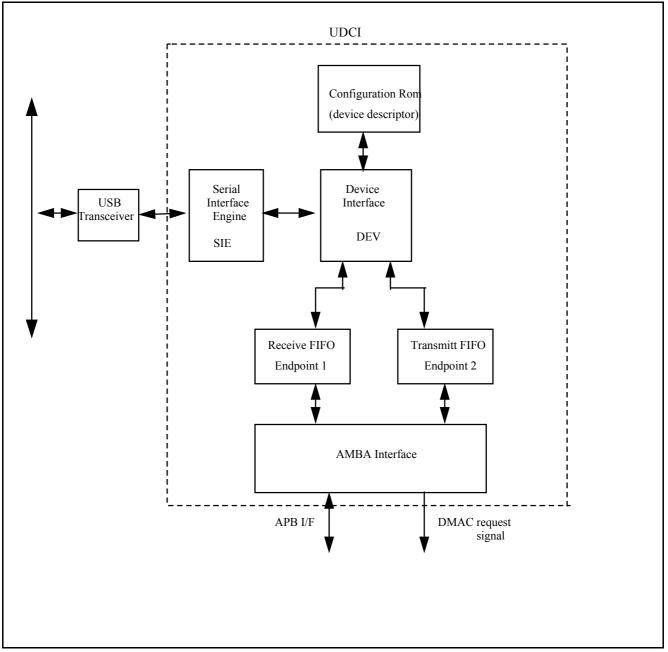

|    | 12.10     | Universal Serial Bus                                | 12-52 |

|    | 12.11     | Sound Interface                                     | 12-67 |

| 13 | Slow AM   | BA Peripherals                                      | 13-1  |

|    | 13.1      | Introduction                                        | 13-2  |

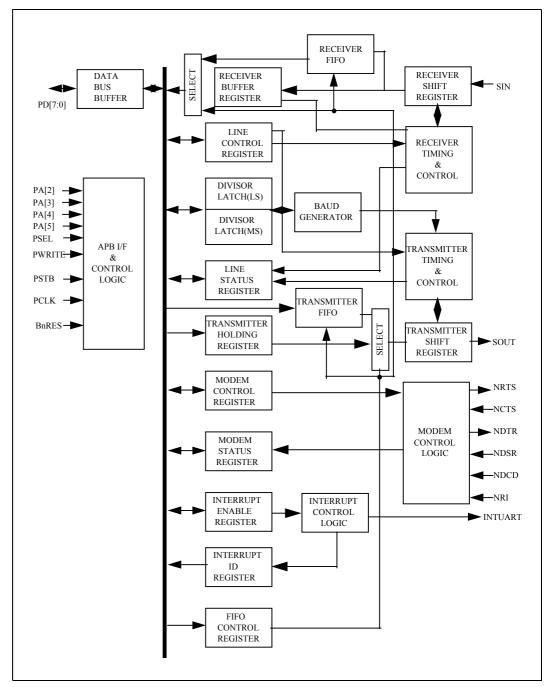

|    | 13.2      | UART                                                | 13-3  |

|    | 13.3      | SIR                                                 | 13-22 |

|    | 13.4      | Keyboard Interface                                  | 13-23 |

|    | 13.5      | GPIO                                                | 13-31 |

|    | 13.6      | Interrupt Controller                                | 13-38 |

|    | 13.7      | Timers                                              | 13-42 |

|    | 13.8      | Synchronous Serial Interface                        | 13-46 |

|    | 13.9      | Analog Front End, AFE (CODEC Interface)             | 13-56 |

|    | 13.10     | Real Time Clock                                     | 13-64 |

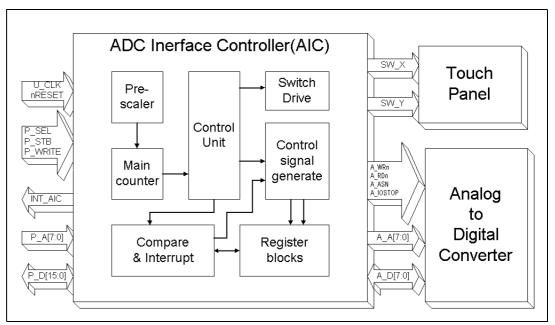

|    | 13.11     | Analog-Digital Converter Interface Controller (AIC) | 13-68 |

| 14 | Debug ar  | nd Test Interface                                   | 14-1  |

|    | 14.1      | Overview                                            | 14-2  |

|    | 14.2      | Software Development Debug and Test Interface       | 14-3  |

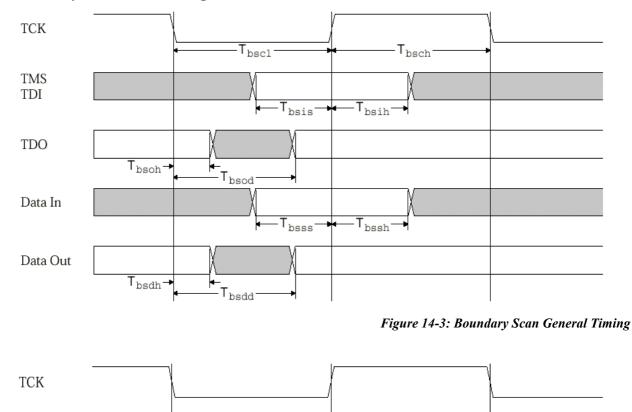

|    | 14.3      | Test Access Port and Boundary-Scan                  | 14-4  |

|    | 14.4      | Production Test Features                            | 14-26 |

| 15 | Electrica | l Characteristics                                   | 15-1  |

|    | 15.1      | Absolute Maximum Ratings                            | 15-2  |

|    | 15.2      | DC Characteristics                                  | 15-3  |

|    | 15.3      | A/D converter Electrical Characteristics            | 15-5  |

|    | 15.4      | D/A Converter characteristics                       | 15-6  |

|    | 15.5      | AC Characteristics                                  | 15-7  |

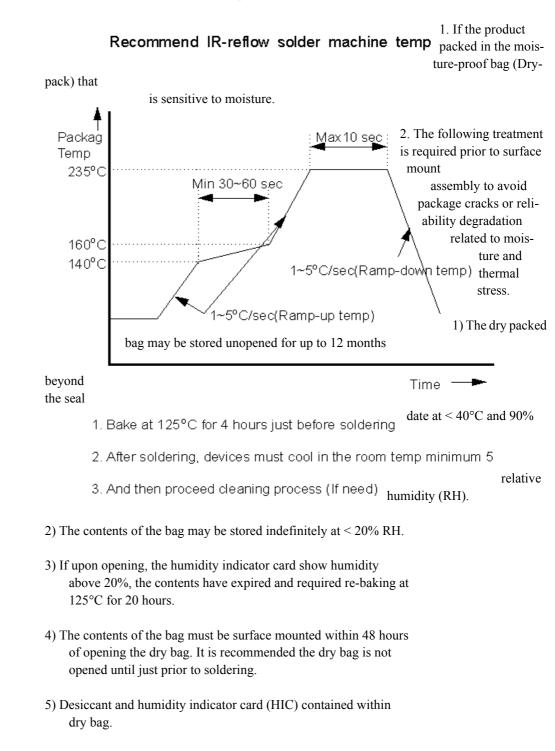

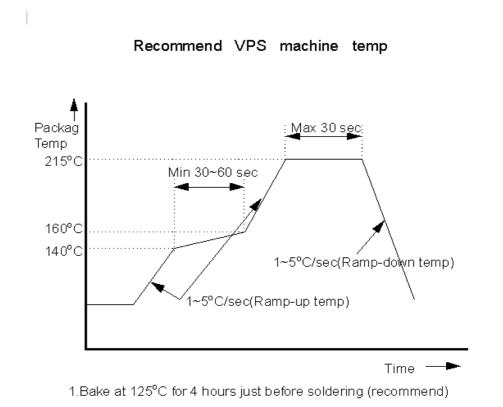

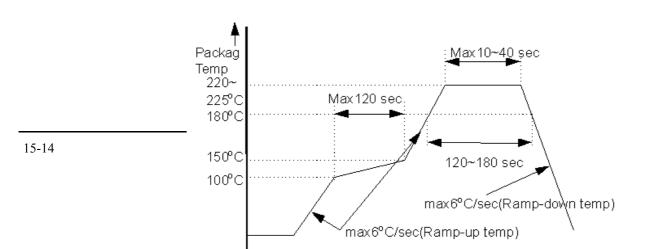

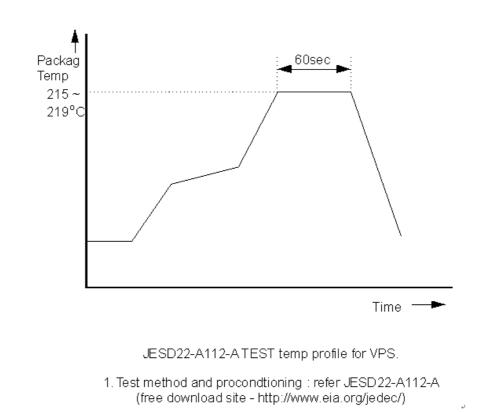

|    | 15.6      | Recommended soldering conditions                    | 15-13 |

1.1 Introduction

1-2

### Introduction

| 1.1   | Introduction  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |               | The GMS30C7201 is a high-performance, low-power, single-chip computer optimized for<br>WinCE applications. It incorporates the ARM720T WinCE-enabled core, which also<br>incorporates ARM's novel Thumb code compression mechanism. The GMS30C7201 also<br>incorporates ARM's unique Piccolo DSP coprocessor, which gives the GMS30C7201 enough<br>DSP horse-power to perform software modem functions simultaneously with WinCE operation.                                           |

| 1.1.1 | Processor     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               | The ARM720T core incorporates an 8K unified write-through cache, and an 8 data entry, 4 address entry write buffer. It also incorporates an MMU with a 64 entry TLB, and WinCE enhancements. The Piccolo SP7 core incorporates a 512-byte, instruction-only cache. Piccolo data is supplied by the ARM720T core, via the coprocessor interface, and hence may be cached in the ARM720T's 8K unified cache.                                                                            |

| 1.1.2 | Piccolo       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               | Piccolo is an ARM coprocessor that boosts the performance of the standard ARM720T CPU to state-of-the-art DSP levels. It integrates:                                                                                                                                                                                                                                                                                                                                                  |

|       |               | • DSP-oriented datapath                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |               | associated DSP instruction set                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       |               | in addition to the standard ARM 32-bit RISC/16-bit Thumb system.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |               | The design/implementation of the Piccolo coprocessor allows data re-use - both the ARM720T and the coprocessor share the same single system bus. The implementation is therefore cost-effective and power-efficient. Other advantages of this approach include integrated hardware and software development. The ARM software development toolkit and emulator support both the CPU and the coprocessor. The GMS30C7201 will run a V34bis (33k6bps) softmodem.                        |

| 1.1.3 | Video         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               | The GMS30C7201 has direct support for mono and color passive LCD displays, as well as color TFT LCD displays, with resolution programmable up to 640x480 VGA resolution. In addition, a separate independent VGA port allows simultaneous display on a VGA resolution monitor, of either the same image as the LCD, or alternatively an entirely different image. The GMS30C7201 has on-chip video DACs, allowing the chip to drive a monitor with the minimum of external circuitry. |

| 1.1.4 | Memory and PC | C-Cards                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

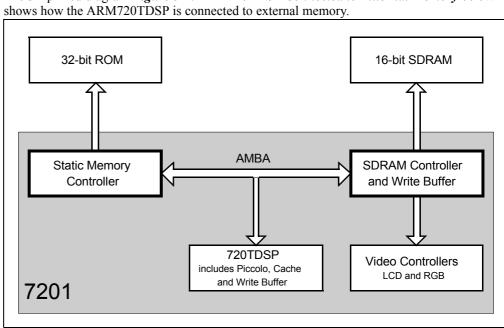

|       |               | GMS30C7201 incorporates two separate memory interfaces. A high speed 16-bit wide interface connects directly to one to four 16, 64 or 128MBit SDRAM devices, supporting DRAM memory sizes in the range 2 to 64MB. In addition, a separate lower speed 32-bit data path                                                                                                                                                                                                                |

GMS30C7201 incorporates two separate memory interfaces. A high speed 16-bit wide interface connects directly to one to four 16, 64 or 128MBit SDRAM devices, supporting DRAM memory sizes in the range 2 to 64MB. In addition, a separate lower speed 32-bit data path interfaces to ROM or Flash devices. Burst mode ROMs are supported, for increased performance, allowing operating system code to be executed directly from ROM. Since the ROM and SDRAM interfaces are separate, the ARM processor core can access O/S code in ROM simultaneously with video DMA access to the SDRAM, thus increasing total effective memory bandwidth, and hence overall performance. In addition, running code directly from ROM reduces total system cost, since ROM is significantly cheaper on a \$/bit basis than DRAM.

The ROM/Flash interface also allows control of one or two PC-Card interfaces, although in this case, external buffers and level translators are needed to interface to the card. The GMS30C7201 generates all signals to control these buffers directly. Since CompactFlash is a subset of the PC-Card standard, one of the PC-Card slots may be used as a CompactFlash interface. The PC-Card interface supports the 16-bit slave-only interface, with no DMA support. It does not support the CardBus 32-bit bus master option in the standard.

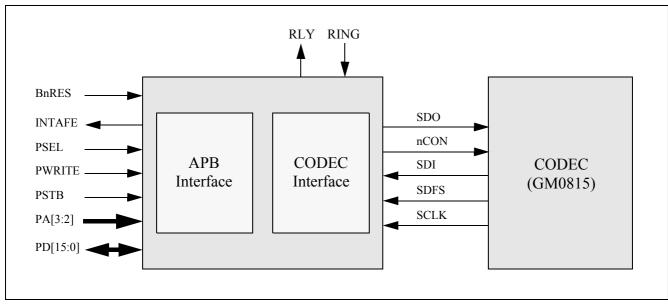

#### 1.1.5 Peripherals and communications

Communications are well-catered for, by two UARTs, an IrDA interface (supporting slow, medium and fast protocols), a serial interface to a modem CODEC chip, for use by the soft-modem, and an on-chip keyboard controller, which directly scans the key matrix. One of the two UARTs is used to implement the IrDA protocol. If IrDA is not being used, then this UART is available for general use. A synchronous serial interface allows connection to a variety of devices, such as an RF modem or a Multimedia Card. A slave USB port supports connection of an GMS30C7201-based PDA as a peripheral to a PC or other USB host controller. A group of general purpose I/O pins can be utilized as required in a PDA design. An on-chip DAC supports audio output, and an on-chip ADC supports microphone input, the digitizer tablet and battery status monitoring functions. Internally, three general-purpose timers and a real-time clock provide timer functionality to be used as required by the O/S, and a two-channel general purpose DMA controller can be allocated to the communications peripherals, as required.

#### 1.1.6 Power management

The GMS30C7201 incorporates advanced power management functions, allowing the whole device to be put into a standby mode, when only the real time clock runs. The SDRAM is put into low-power self refresh mode to preserve it's contents. The GMS30C7201 may be forced out of this state by either a real-time clock wake-up interrupt, a user wake-up event (which would generally be a user pressing the "on" key) or by the UART ring-indicate input. The power management unit (PMU) controls the safe exit from standby mode to operational mode, ensuring that SDRAM contents are preserved. In addition, halt and slow modes allow the processor to be halted, or run more slowly than usual, to reduce power consumption. The processor can be quickly brought out of the halted state by a peripheral interrupt. The advanced power management unit controls all this functionality. In addition, individual devices and peripherals may be powered down when they are not in use. For example, the VGA controller can be disabled when an external monitor is not in use (which saves not only the power of the digital controller, but also of the analog DACs), or the Piccolo DSP coprocessor can be powered.

#### 1.1.7 Test and debug

The GMS30C7201 incorporates the ARM standard test interface controller (TIC) allowing 32bit parallel test vectors to be passed onto the internal bus. This allows access to the ARM720T macro-cell core, and also to memory mapped devices and peripherals within the GMS30C7201. In addition, the ARM720T and Piccolo include support for the ARM debug architecture (Embedded ICE), which makes use of a JTAG boundary scan port to support debug of code on the embedded processor and DSP cores. The same boundary scan port is also used to support a normal pad-ring boundary scan for board level test applications.

### Introduction

2

# **Signal Description**

| 2.1 | Signal Description for GMS30C7201 | 2-2 |

|-----|-----------------------------------|-----|

| 2.2 | Package Details                   | 2-7 |

| 2.3 | Pin List                          | 2-8 |

### 2.1 Signal Description for GMS30C7201

| Output                                   |

|------------------------------------------|

| Input                                    |

| Analog output                            |

| Analog input                             |

| Input/output                             |

| Analog input/output                      |

| Input with Schmitt level input threshold |

| Power input                              |

| Suffix to indicate integral pullup       |

| Suffix to indicate integral pulldown     |

|                                          |

| Signal name  | Туре | Description                                                                      |

|--------------|------|----------------------------------------------------------------------------------|

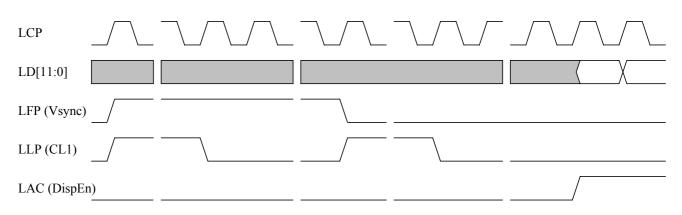

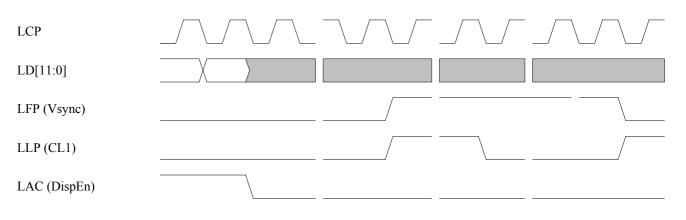

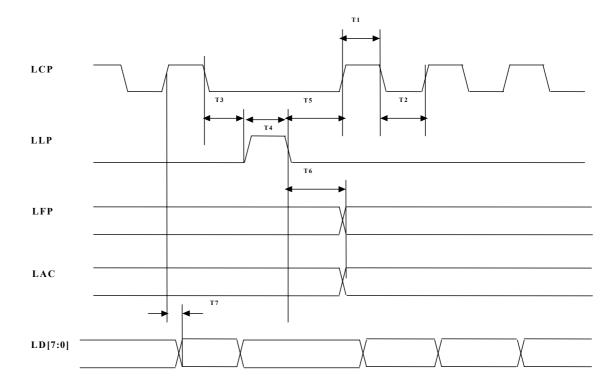

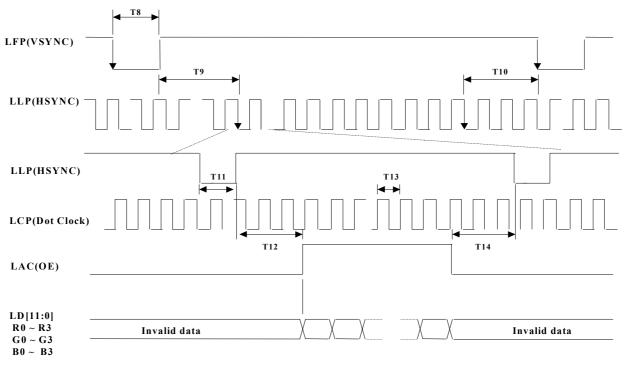

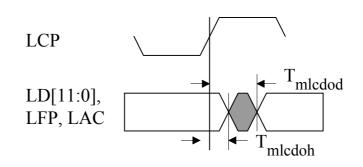

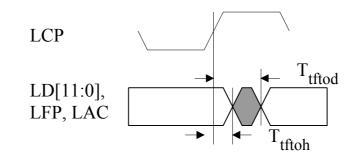

| LD[11:0]     | 0    | LCD data bus. Allow 4:4:4 TFT, color (using [7:0]) or mono, using [3:0] or [7:0] |

| LCP          | 0    | LCD clock pulse                                                                  |

| LLP          | 0    | LDC line pulse (HSync for TFT)                                                   |

| LFP          | 0    | LCD frame pulse (VSync for TFT)                                                  |

| LAC          | 0    | LCD AC bias (clock enable for TFT)                                               |

| LCDEN        | 0    | Display enable signal for LCD. Enables high voltage to LCD                       |

| LBLEN        | 0    | LCD backlight enable                                                             |

| VGAROUTP     | OA   | VGA red output. Drives 75 ohm terminated load directly                           |

| VGAROUTM     | OA   | VGA red output. Drives 75 ohm terminated load directly                           |

| VGAGOUTP     | OA   | VGA green output. Drives 75 ohm terminated load directly                         |

| VGAGOUTM     | OA   | VGA green output. Drives 75 ohm terminated load directly                         |

| VGABOUTP     | OA   | VGA blue output. Drives 75 ohm terminated load directly                          |

| VGABOUTM     | OA   | VGA blue output. Drives 75 ohm terminated load directly                          |

| VGAHS        | 0    | VGA HSync output                                                                 |

| VGAVS        | 0    | VGA VSync output                                                                 |

| VGAREF       | IA   | VGA DAC reference current input                                                  |

| VGAAVDD[1:0] | Р    | VGA DAC analog Vdd supply                                                        |

| VBIAS        | OA   | VGA DAC analog bias                                                              |

| VT[1:0]      | OA   | VGA voltage reference for comparator                                             |

| VGAAVSS      | Р    | VGA DAC analog Vss supply                                                        |

Table 2-1: Signal description table

GMS30C7201 Data Sheet Mynix

| Signal name                 | Туре | Description                                                                                    |

|-----------------------------|------|------------------------------------------------------------------------------------------------|

| RA[25:0]                    | 0    | ROM and PC-Card address bus                                                                    |

| RD[31:0]                    | Ю    | ROM and PC-Card data bus, plus test bus                                                        |

| nRCS[2:0]                   | 0    | ROM chip select outputs.                                                                       |

| nRCS[5:3], or<br>PORTD[3:1] | Ю    | ROM chip select outputs, or general IO pins controlled by the PMPS register in GPIO subsystem. |

| nROE                        | 0    | ROM and PC-Card output enable signal                                                           |

| nRWE[3:0]                   | 0    | ROM and PC-Card write enable signals. One per byte.                                            |

| EXPRDY                      | Ι    | Wait from external I/O                                                                         |

| EXBCLK, or PORTD[0]         | Ю    | Bus clock output, or general IO pin controlled by the PMPS register in GPIO subsystem.         |

| BOOTBIT[1:0]                | Ι    | 16/32 bit ROM selection                                                                        |

| nPCBCE[1:0]                 | 0    | PC-Card Card enable signals                                                                    |

| nPCACE[1:0]                 | 0    | PC-Card Card enable signals                                                                    |

| nPCBIORD                    | 0    | PC-Card I/O read enable                                                                        |

| nPCAIORD                    | 0    | PC-Card I/O read enable                                                                        |

| nPCBIOWR                    | 0    | PC-Card I/O write enable                                                                       |

| nPCAIOWR                    | 0    | PC-Card I/O write enable                                                                       |

| PCARESET                    | 0    | PC-Card A reset signal                                                                         |

| PCBRESET                    | 0    | PC-Card B reset signal                                                                         |

| nPCAWAIT                    | Ι    | PC-Card A wait signal                                                                          |

| nPCBWAIT                    | Ι    | PC-Card B wait signal                                                                          |

| nPCREG                      | 0    | PC-Card attribute memory select                                                                |

| PCAREADY                    | Ι    | PC-Card A ready input, or interrupt request in I/O mode                                        |

| PCBREADY                    | Ι    | PC-Card B ready input, or interrupt request in I/O mode                                        |

| PCABVD[1:0]                 | Ι    | PC-Card A battery status, or nSPKR/nSTSCHG in I/O mode                                         |

| PCBBVD[1:0]                 | Ι    | PC-Card B battery status, or nSPKR/nSTSCHG in I/O mode                                         |

| nPCACD[1:0]                 | Iu   | PC-Card A card detect signals                                                                  |

| nPCBCD[1:0]                 | Iu   | PC-Card B card detect signals                                                                  |

| PCCADRV                     | 0    | PC-Card A is selected                                                                          |

| PCCBDRV                     | 0    | PC-Card B is selected                                                                          |

| PCBIPORTE                   | 0    | PC-Card data buffer external bidirectional buffer control                                      |

| PCAWP                       | Ι    | PC-Card A write protect/IOIS16                                                                 |

Table 2-1: Signal description table (continued)

| Signal name   | Туре | Description                          |  |

|---------------|------|--------------------------------------|--|

| PCBWP         | I    | PC-Card B write protect/IOIS16       |  |

| PCAVS[1:0]    | Iu   | PC-Card A voltage sense signals      |  |

| PCBVS[1:0]    | Iu   | PC-Card B voltage sense signals      |  |

| PCAVPPEN[1:0] | 0    | PC-Card A Vpp control signals        |  |

| PCBVPPEN[1:0] | 0    | PC-Card B Vpp control signals        |  |

| nPCBOE        | 0    | PC-Card output enable detect signals |  |

| nPCAOE        | 0    | PC-Card output enable detect signals |  |

| nPCBWE        | 0    | PC-Card write enable for memory card |  |

| nPCAWE        | 0    | PC-Card write enable for memory card |  |

| PCAVCCEN[1:0] | 0    | PC-Card A Vcc control signals        |  |

| PCBVCCEN[1:0] | 0    | PC-Card B Vcc control signals        |  |

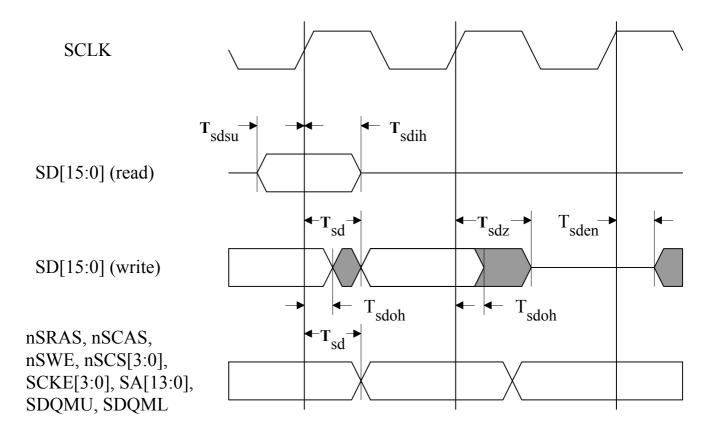

| SCLK          | 0    | SDRAM clock output                   |  |

| SCKE[3:0]     | 0    | SDRAM clock enable output            |  |

| nSRAS         | 0    | SDRAM RAS output                     |  |

| nSCAS         | 0    | SDRAM CAS output                     |  |

| nSWE          | 0    | SDRAM write enable output            |  |

| nSCS[3:0]     | 0    | SDRAM chip select outputs            |  |

| SDQML         | 0    | SDRAM lower data byte enable         |  |

| SDQMU         | 0    | SDRAM upper data byte enable         |  |

| SD[15:0]      | Ю    | SDRAM data bus                       |  |

| SA[13:0]      | 0    | SDRAM address bus                    |  |

| nUDCD[1:0]    | Iu   | UART data carrier detect inputs      |  |

| nUDSR[1:0]    | Iu   | UART data set ready inputs           |  |

| nUCTS[1:0]    | Iu   | UART clear to send inputs            |  |

| USIN[1:0]     | Iu   | UART serial data inputs              |  |

| USOUT[1:0]    | 0    | UART serial data outputs             |  |

| nUDTR[1:0]    | 0    | UART data terminal ready             |  |

| nURTS[1:0]    | 0    | UART request to send                 |  |

| SSDIN         | Ι    | Synchronous serial data input        |  |

| SSOUT         | 0    | Synchronous serial data output       |  |

| SSCLK         | 0    | Synchronous serial clock output      |  |

Table 2-1: Signal description table (continued)

GMS30C7201 Data Sheet Mynix

| Signal name                                                          | Туре                 | Description                                                                                                                                                                                  |  |

|----------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| nSSCS                                                                | 0                    | Synchronous serial chip select                                                                                                                                                               |  |

| IRDIN                                                                | Ι                    | IrDA infra-red data input                                                                                                                                                                    |  |

| IRDOUT                                                               | 0                    | IrDA infra-red data output                                                                                                                                                                   |  |

| <b>GPIO:</b><br>PORTA[7:0]<br>PORTB[7:6]<br>PORTC[7:0]<br>PORTD[7:4] | IO<br>IO<br>IO<br>IO | GPIO interface. 8 general-purpose I/O lines.<br>GPIO interface. 2 general-purpose I/O lines.<br>GPIO interface. 8 general-purpose I/O lines.<br>GPIO interface. 4 general-purpose I/O lines. |  |

| MRING                                                                | Ι                    | Ring indicator (wake-up signal to PMU)                                                                                                                                                       |  |

| MRLY                                                                 | 0                    | Modem relay control                                                                                                                                                                          |  |

| MCLK                                                                 | Ι                    | Modem clock input                                                                                                                                                                            |  |

| MDFR                                                                 | Ι                    | Modem data frame input                                                                                                                                                                       |  |

| MDIN                                                                 | Ι                    | Modem data input                                                                                                                                                                             |  |

| MDOUT                                                                | 0                    | Modem data output                                                                                                                                                                            |  |

| nMCON                                                                | 0                    | Modem control data select (HIGH for data, LOW for control)                                                                                                                                   |  |

| UVPO, or<br>PORTB[0]                                                 | Ю                    | USB output differential drive (+), or general IO pin controlled by the PMPS register in GPIO subsystem.                                                                                      |  |

| UVMO, or PORTB[1]                                                    | Ю                    | USB output differential drive (-), or general IO pin controlled by the PMPS register in GPIO subsystem.                                                                                      |  |

| nUSBOE, or<br>PORTB[2]                                               | Ю                    | USB output enable, or general IO pin controlled by the PMPS register in GPIO subsystem.                                                                                                      |  |

| URCVIN, or <b>PORTB[3]</b>                                           | Ю                    | USB receive data, or general IO pin controlled by the PMPS register in GPIO subsystem.                                                                                                       |  |

| UVP, or PORTB[4]                                                     | Ю                    | USB gated input differential drive (+), or general IO pin controlled<br>by the PMPS register in GPIO subsystem.                                                                              |  |

| UVM, or PORTB[5]                                                     | Ю                    | USB gated input differential drive (-), or general IO pin controlled by the PMPS register in GPIO subsystem.                                                                                 |  |

| USUSPEND                                                             | 0                    | USB low power state                                                                                                                                                                          |  |

| ATSXP                                                                | 0                    | Touch screen switch X output                                                                                                                                                                 |  |

| ATSXM                                                                | 0                    | Touch screen switch X output                                                                                                                                                                 |  |

| ATSYP                                                                | 0                    | Touch screen switch Y output                                                                                                                                                                 |  |

| ATSYM                                                                | 0                    | Touch screen switch Y output                                                                                                                                                                 |  |

| ADIN[4:0]                                                            | IA                   | ADC inputs for MIC and battery                                                                                                                                                               |  |

| AVDDDAC                                                              | Р                    | DAC Analog Vdd and reference                                                                                                                                                                 |  |

| AVSSDAC                                                              | Р                    | DAC Analog Vss                                                                                                                                                                               |  |

Table 2-1: Signal description table (continued)

| Signal name  | Туре | Description                                                   |  |

|--------------|------|---------------------------------------------------------------|--|

| AVREFADC     | IA   | ADC reference voltage                                         |  |

| AVDDADC      | Р    | ADC Analog Vdd                                                |  |

| AVSSADC      | Р    | ADC Analog Vss                                                |  |

| ADAC[1:0]    | OA   | Sound DAC outputs                                             |  |

| KSCANO[10:0] | 0    | Keyboard scan outputs                                         |  |

| KSCANI[7:0]  | Iu   | Keyboard scan inputs                                          |  |

| nPOR         | ISu  | Power on reset input. Schmitt level input, with pullup.       |  |

| nPMWAKEUP    | ISu  | Wake-up "on-key" input. Low causes PMU to exit standby state. |  |

| nRESET       | IOu  | Reset input (also driven out in POR, until the PLL is locked) |  |

| PMADAPOK     | Ι    | Adapter power OK.                                             |  |

| РМВАТОК      | Ι    | Main battery OK.                                              |  |

| RTCOSCIN     | IA   | RTC oscillator input                                          |  |

| RTCOSCOUT    | OA   | RTC oscillator output                                         |  |

| OSCIN        | IA   | Main oscillator input                                         |  |

| OSCOUT       | OA   | Main oscillator output                                        |  |

| nPLLENABLE   | Id   | Low to enable PLL. High to bypass PLL with clock from OSCIN.  |  |

| PLLVDD[1:0]  | Р    | PLL analog power supply                                       |  |

| PLLVSS[1:0]  | Р    | PLL analog ground input                                       |  |

| PLLFILT[2:0] | IOA  | External PLL loop filter input/output pins (1 per PLL)        |  |

| ТСК          | Iu   | JTAG boundary scan and debug test clock                       |  |

| nTRST        | Id   | JTAG boundary scan and debug test reset                       |  |

| TMS          | Iu   | JTAG boundary scan and debug test mode select                 |  |

| TDI          | Iu   | JTAG boundary scan and debug test data input                  |  |

| TDO          | 0    | JTAG boundary scan and debug test data output                 |  |

| nTEST        | Iu   | Test mode select                                              |  |

| VDDCore[3:0] | Р    | Core Vdd supply                                               |  |

| VSSCore[3:0] | Р    | Core Vss supply                                               |  |

| VDD[25:0]    | Р    | Pad Vdd supply                                                |  |

| VSS[25:0]    | Р    | Pad Vss supply                                                |  |

Table 2-1: Signal description table (continued)

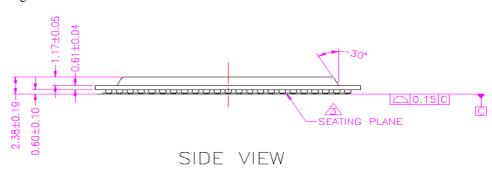

### 2.2 Package Details

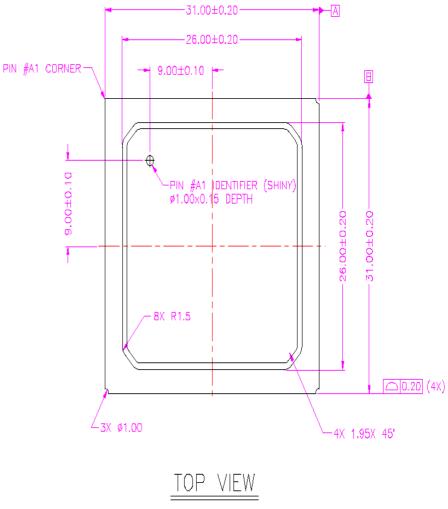

This diagram, *Figure 2-1: Side View of the PBGA Package*, gives a side view of the PBGA package.

Figure 2-1: Side View of the PBGA Package

This diagram, *Figure 2-2: Dimensions of the PBGA Package*, gives the dimensions of the package in millimeters.

Figure 2-2: Dimensions of the PBGA Package

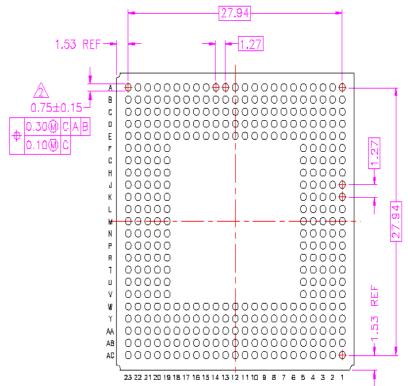

### 2.3 Pin List

Use *Figure 2-3: Pin Location and Signal Cross-References (Bottom View)* and *Table 2-2: Pin Reference Numbers and Signal Names* on page 2-8 to match pins and signals. Pin A1 (GND) is in the top right-hand corner of the diagram marked "PIN 1 CORNER". This is a bottom view of the package.

Figure 2-3: Pin Location and Signal Cross-References (Bottom View)

| Pin | Signal | Pin | Signal  |

|-----|--------|-----|---------|

| A1  | GND    | A8  | nSCS[3] |

| A2  | nTEST  | A9  | SCKE[3] |

| A3  | SA[3]  | A10 | SDQML   |

| A4  | SA[4]  | A11 | SD[8]   |

| A5  | SA[5]  | A12 | SD[9]   |

| A6  | SA[0]  | A13 | SD[10]  |

| A7  | SA[12] | A14 | SD[12]  |

Table 2-2: Pin Reference Numbers and Signal Names

GMS30C7201 Data Sheet **MUNIX**

| Pin | Signal   | Pin | Signal     |

|-----|----------|-----|------------|

| A15 | SD[14]   | B23 | USUSPEND   |

| A16 | PORTA[0] | C1  | TDI        |

| A17 | PORTA[1] | C2  | OSCIN      |

| A18 | PORTA[2] | C3  | GND        |

| A19 | PORTA[3] | C4  | nPLLENABLE |

| A20 | UVPO     | C5  | SA[6]      |

| A21 | UVMO     | C6  | SA[10]     |

| A22 | nUSBOE   | C7  | SA[13]     |

| A23 | GND      | C8  | nSCS[1]    |

| B1  | OSCOUT   | С9  | SCKE[1]    |

| B2  | GND      | C10 | SDQMU      |

| B3  | nPOR     | C11 | PMADAPOK   |

| B4  | SA[2]    | C12 | PMBATOK    |

| B5  | SA[1]    | C13 | SD[11]     |

| B6  | SA[7]    | C14 | SD[13]     |

| B7  | SA[9]    | C15 | SD[15]     |

| B8  | nSCS[2]  | C16 | PORTC[0]   |

| B9  | SCKE[2]  | C17 | PORTC[1]   |

| B10 | nSWE     | C18 | PORTC[2]   |

| B11 | SD[7]    | C19 | PORTC[3]   |

| B12 | SD[6]    | C20 | UVM        |

| B13 | SD[5]    | C21 | GND        |

| B14 | SD[3]    | C22 | nPCACE[0]  |

| B15 | SD[1]    | C23 | nPCACE[1]  |

| B16 | PORTA[4] | D1  | TMS        |

| B17 | PORTA[5] | D2  | ТСК        |

| B18 | PORTA[6] | D3  | TDO        |

| B19 | PORTA[7] | D4  | GND        |

| B20 | URCVIN   | D5  | nRESET     |

| B21 | UVP      | D6  | SA[8]      |

| B22 | GND      | D7  | SA[11]     |

Table 2-2: Pin Reference Numbers and Signal Names (continued)

| Pin | Signal    | Pin | Signal    |

|-----|-----------|-----|-----------|

| D8  | nSCS[0]   | E16 | PORTB[7]  |

| D9  | SCKE[0]   | E17 | VDD       |

| D10 | nSCAS     | E18 | PORTB[6]  |

| D11 | VDDcore   | E19 | GND       |

| D12 | VSScore   | E20 | nPCAIORD  |

| D13 | SD[4]     | E21 | nPCAIOWR  |

| D14 | SD[2]     | E22 | PCARESET  |

| D15 | SD[0]     | E23 | nPCAWAIT  |

| D16 | PORTC[4]  | F1  | LFP       |

| D17 | PORTC[5]  | F2  | LAC       |

| D18 | PORTC[6]  | F3  | LCP       |

| D19 | PORTC[7]  | F4  | LD[11]    |

| D20 | GND       | F5  | IRDIN     |

| D21 | nPCREG    | F19 | PCBIPORTE |

| D22 | nPCBCE[0] | F20 | nPCBIORD  |

| D23 | nPCBCE[1] | F21 | nPCBIOWR  |

| E1  | LLP       | F22 | PCBRESET  |

| E2  | nTRST     | F23 | nPCBWAIT  |

| E3  | LCDEN     | G1  | LD[10]    |

| E4  | LBLEN     | G2  | LD[9]     |

| E5  | GND       | G3  | LD[8]     |

| E6  | IRDOUT    | G4  | LD[7]     |

| E7  | VDD       | G5  | VDD       |

| E8  | nSRAS     | G19 | VDD       |

| E9  | VDD       | G20 | PCABVD[0] |

| E10 | SCLK      | G21 | PCABVD[1] |

| E11 | nPMWAKEUP | G22 | PCCADRV   |

| E12 | GND       | G23 | PCAREADY  |

| E13 | VDD       | H1  | LD[6]     |

| E14 | PORTD[6]  | Н2  | LD[5]     |

| E15 | VDD       | Н3  | LD[4]     |

Table 2-2: Pin Reference Numbers and Signal Names (continued)

GMS30C7201 Data Sheet Mynix

| Pin | Signal     | Pin | Signal      |

|-----|------------|-----|-------------|

| H4  | LD[3]      | L5  | VDD         |

| Н5  | LD[2]      | L19 | PORTD[7]    |

| H19 | nPCAWE     | L20 | VDDcore     |

| H20 | PCBBVD[0]  | L21 | PCAVPPEN[0] |

| H21 | PCBBVD[1]  | L22 | PCAVS[0]    |

| H22 | PCCBDRV    | L23 | PCAVS[1]    |

| Н23 | PCBREADY   | M1  | VT[1]       |

| J1  | LD[1]      | M2  | VGAREF      |

| J2  | LD[0]      | М3  | VT[0]       |

| J3  | VGAAVDD[0] | M4  | VSScore     |

| J4  | VGAHS      | M5  | GND         |

| J5  | VDD        | M19 | GND         |

| J19 | VDD        | M20 | VSScore     |

| J20 | nPCAOE     | M21 | PCAVPPEN[1] |

| J21 | PCAWP      | M22 | PCBVS[0]    |

| J22 | nPCACD[0]  | M23 | PCBVS[1]    |

| J23 | nPCACD[1]  | N1  | AVDDDAC     |

| K1  | VGAROUTP   | N2  | VBIAS       |

| К2  | VGAROUTM   | N3  | ADAC[0] (R) |

| К3  | VGAGOUTM   | N4  | VDDcore     |

| K4  | VGAVS      | N5  | PLLVSS[0]   |

| K5  | VGAAVSS    | N19 | VDD         |

| K19 | nPCBWE     | N20 | PCBVPPEN[0] |

| K20 | nPCBOE     | N21 | PCBVPPEN[1] |

| K21 | PCBWP      | N22 | PCAVCCEN[0] |

| K22 | nPCBCD[0]  | N23 | PCAVCCEN[1] |

| K23 | nPCBCD[1]  | P1  | PLLVDD[0]   |

| L1  | VGABOUTM   | P2  | ADAC[1] (L) |

| L2  | VGABOUTP   | Р3  | PLLFILT[0]  |

| L3  | VGAAVDD[1] | P4  | AVSSDAC     |

| L4  | VGAGOUTP   | Р5  | AVDDADC     |

Table 2-2: Pin Reference Numbers and Signal Names (continued)

| Pin | Signal      | Pin | Signal    |

|-----|-------------|-----|-----------|

| P19 | RD[23]      | U20 | RD[13]    |

| P20 | RD[27]      | U21 | RD[17]    |

| P21 | RD[30]      | U22 | RD[20]    |

| P22 | PCBVCCEN[0] | U23 | RD[24]    |

| P23 | PCBVCCEN[1] | V1  | nSSCS     |

| R1  | PLLFILT[2]  | V2  | SSDIN     |

| R2  | PLLFILT[1]  | V3  | ATSYM     |

| R3  | ADIN[0]     | V4  | SSCLK     |

| R4  | PLLVDD[1]   | V5  | MCLK      |

| R5  | VDD         | V19 | RD[5]     |

| R19 | VDD         | V20 | RD[9]     |

| R20 | RD[22]      | V21 | RD[12]    |

| R21 | RD[26]      | V22 | RD[16]    |

| R22 | RD[29]      | V23 | RD[19]    |

| R23 | RD[31]      | W1  | ATSXP     |

| T1  | ADIN[1]     | W2  | ATSYP     |

| T2  | PLLVSS[1]   | W3  | ATSXM     |

| Т3  | ADIN[4]     | W4  | MDOUT     |

| T4  | ADIN[2]     | W5  | GND       |

| Т5  | PORTD[5]    | W6  | nURTS[1]  |

| T19 | RD[14]      | W7  | VDD       |

| T20 | RD[18]      | W8  | KSCANO[6] |

| T21 | RD[21]      | W9  | VDD       |

| T22 | RD[25]      | W10 | KSCANI[5] |

| T23 | RD[28]      | W11 | VDD       |

| U1  | AVREFADC    | W12 | GND       |

| U2  | ADIN[3]     | W13 | PORTD[4]  |

| U3  | SSOUT       | W14 | RA[13]    |

| U4  | AVSSADC     | W15 | VDD       |

| U5  | VDD         | W16 | RA[4]     |

| U19 | VDD         | W17 | VDD       |

Table 2-2: Pin Reference Numbers and Signal Names (continued)

GMS30C7201 Data Sheet Mynix

| Pin | Signal     | Pin  | Signal    |

|-----|------------|------|-----------|

| W18 | nRWE[3]    | AA3  | GND       |

| W19 | GND        | AA4  | USIN[1]   |

| W20 | RD[4]      | AA5  | nUDCD[1]  |

| W21 | RD[8]      | AA6  | nUDSR[1]  |

| W22 | RD[11]     | AA7  | KSCANO[9] |

| W23 | RD[15]     | AA8  | KSCANO[4] |

| Y1  | MDFR       | AA9  | KSCANO[0] |

| Y2  | MRLY       | AA10 | KSCANI[3] |

| ¥3  | MDIN       | AA11 | nRCS[5]   |

| ¥4  | GND        | AA12 | EXBCLK    |

| ¥5  | nUDTR[1]   | AA13 | RA[23]    |

| ¥6  | USOUT[1]   | AA14 | RA[20]    |

| ¥7  | KSCANO[10] | AA15 | RA[16]    |

| ¥8  | KSCANO[5]  | AA16 | RA[11]    |

| ¥9  | KSCANO[1]  | AA17 | RA[7]     |

| Y10 | KSCANI[4]  | AA18 | RA[2]     |

| Y11 | KSCANI[0]  | AA19 | nRCS[2]   |

| Y12 | VSScore    | AA20 | nRWE[1]   |

| Y13 | VDDcore    | AA21 | GND       |

| Y14 | RA[17]     | AA22 | RD[2]     |

| Y15 | RA[12]     | AA23 | RD[6]     |

| Y16 | RA[8]      | AB1  | RTCOSCIN  |

| Y17 | RA[3]      | AB2  | GND       |

| Y18 | nROE       | AB3  | nMCON     |

| ¥19 | nRWE[2]    | AB4  | nUCTS[1]  |

| Y20 | GND        | AB5  | nURTS[0]  |

| Y21 | RD[3]      | AB6  | nUDTR[0]  |

| Y22 | RD[7]      | AB7  | KSCANO[8] |

| ¥23 | RD[10]     | AB8  | KSCANO[3] |

| AA1 | RTCOSCOUT  | AB9  | KSCANI[7] |

| AA2 | MRING      | AB10 | KSCANI[2] |

Table 2-2: Pin Reference Numbers and Signal Names (continued)

| Pin  | Signal     | Pin  | Signal  |

|------|------------|------|---------|

| AB11 | nRCS[4]    | AC19 | RA[5]   |

| AB12 | EXPRDY     | AC20 | RA[0]   |

| AB13 | RA[25]     | AC21 | nRCS[0] |

| AB14 | RA[22]     | AC22 | RD[0]   |

| AB15 | RA[19]     | AC23 | GND     |

| AB16 | RA[15]     |      |         |

| AB17 | RA[10]     |      |         |

| AB18 | RA[6]      |      |         |

| AB19 | RA[1]      |      |         |

| AB20 | nRCS[1]    |      |         |

| AB21 | nRWE[0]    |      |         |

| AB22 | GND        |      |         |

| AB23 | RD[1]      |      |         |

| AC1  | GND        |      |         |

| AC2  | USOUT[0]   |      |         |

| AC3  | USIN[0]    |      |         |

| AC4  | nUCTS[0]   |      |         |

| AC5  | nUDSR[0]   |      |         |

| AC6  | nUDCD[0]   |      |         |

| AC7  | KSCANO[7]  |      |         |

| AC8  | KSCANO[2]  |      |         |

| AC9  | KSCANI[6]  |      |         |

| AC10 | KSCANI[1]  |      |         |

| AC11 | nRCS[3]    |      |         |

| AC12 | BOOTBIT[0] |      |         |

| AC13 | BOOTBIT[1] |      |         |

| AC14 | RA[24]     |      |         |

| AC15 | RA[21]     |      |         |

| AC16 | RA[18]     |      |         |

| AC17 | RA[14]     |      |         |

| AC18 | RA[9]      |      |         |

Table 2-2: Pin Reference Numbers and Signal Names (continued)

GMS30C7201 Data Sheet Mynix

3

# **Architecture Overview**

| 3.1 | Internal bus structure | 3-2 |

|-----|------------------------|-----|

| 3.2 | SDRAM controller       | 3-4 |

| 3.3 | Peripheral DMA         | 3-5 |

| 3.4 | Power management       | 3-7 |

| 3.5 | Performance            | 3-8 |

|     |                        |     |

### **Architecture Overview**

### 3.1 Internal bus structure

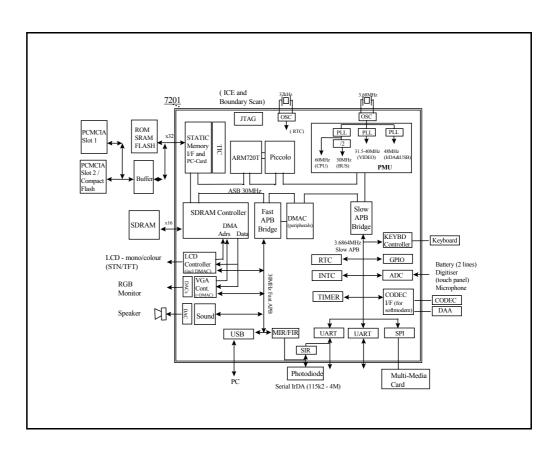

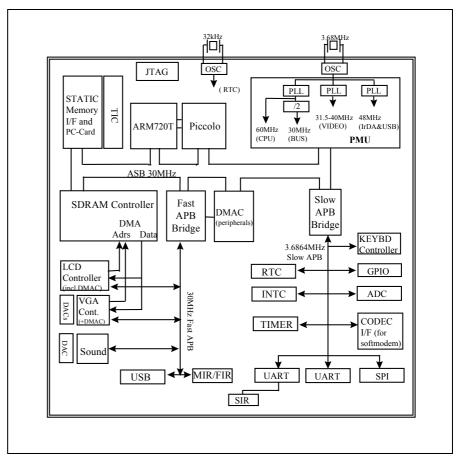

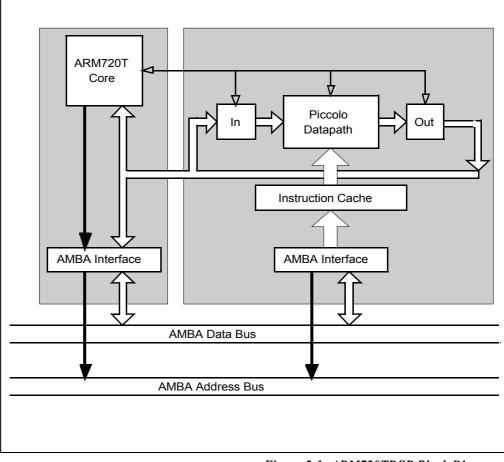

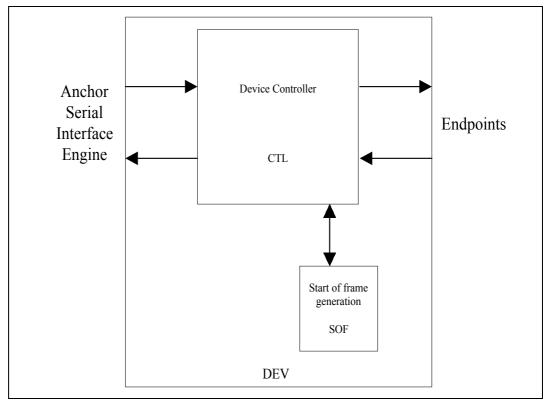

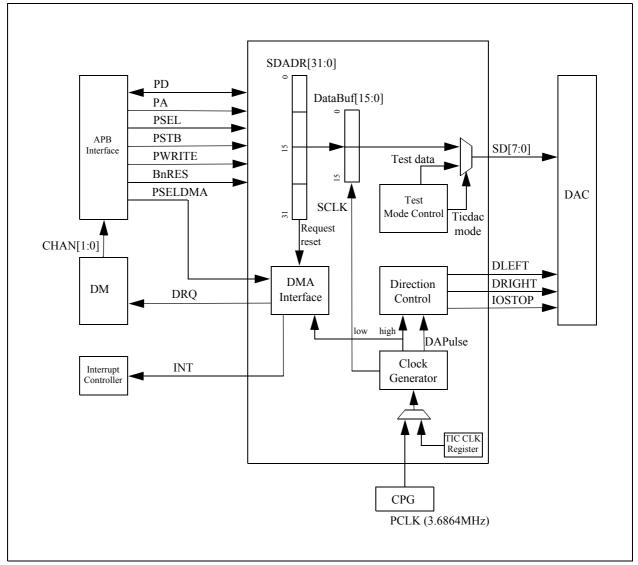

*Figure 3-1: GMS30C7201* shows a block diagram of GMS30C7201. GMS30C7201 consists of the ARM720T processor core, a Piccolo SP7 DSP coprocessor and a set of peripherals.

*Figure 3-1: GMS30C7201*

### 3.1.1 GMS30C7201 bus structure

The GMS30C7201 internal bus organization is based upon the AMBA standard, but with some minor modifications to the peripheral buses (the APBs). There are three main buses in the GMS30C7201:

- 1 the main system bus (the ASB) to which the CPU and memory controllers are connected

- 2 the fast APB to which high-bandwidth peripherals are connected

- 3 the slow APB (to which timers, the UART and other low-bandwidth peripherals are connected)

There is also a separate video DMA bus.

#### 3.1.2 ASB

The ASB is designed to allow the ARM to have continuous access to both the ROM/PCMCIA interface and the SDRAM. The SDRAM controller straddles both the ASB and the video DMA bus so the LCD and VGA can access the SDRAM controller simultaneously with activity on the ASB. This means that the ARM or Piccolo can read code from ROM, or access a peripheral, without being interrupted by video DMA.

The GMS30C7201 uses a modified arbiter to control mastership on the main ASB bus. The arbiter only arbitrates on quad-word boundaries, or when the bus is idle. This is to get the best performance with the ARM720T, which uses a quad-word cache line, and also to get the best performance from the SDRAM, which uses a burst size of eight halfwords per access. By arbitrating only when the bus is idle or on quad-word boundaries (A[3:2] = 11), it ensures that cache line fills are not broken up, hence SDRAM bursts are not broken up.

Video ASB arbitration is controlled by the SDRAM controller. This is explained in *3.2.2 Arbitration* on page 3-4.

#### 3.1.3 Video bus

The video bus hosts the LCD controller and the VGA controller DMA. The video bus consists of separate address inputs, a request / acknowledge to / from the SDRAM controller, for each of the LCD and VGA blocks, and a shared data bus. The LCD and VGA registers are programmed from the fast APB. The SDRAM controller arbitrates between ASB, VGA and LCD access requests. Video always has higher priority than ASB access requests. The split ASB/video bus architecture of the SDRAM controller allows slow device accesses—such as access to a PC-Card that asserts a **WAIT** signal for several microseconds—without blocking video DMA.

#### 3.1.4 APBs

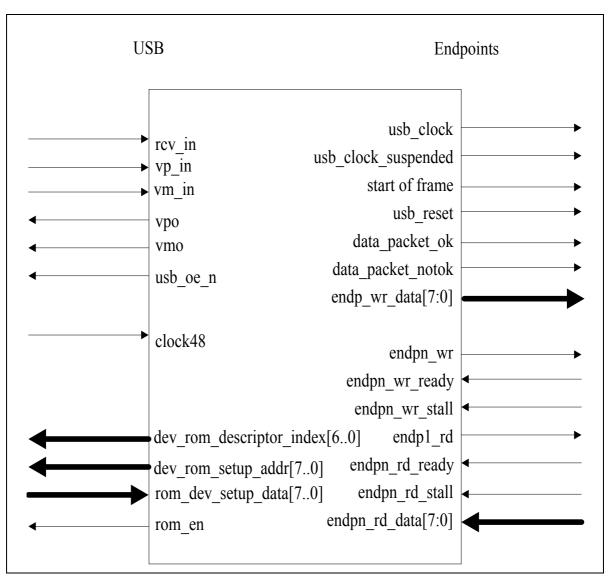

There are two APB buses. These are the *fast* and *slow* APB buses. The fast APB bus operates at the speed of the ASB (30 MHz), and hosts the Fast and Medium speed infra-red interface, the USB interface, the sound output interface, and the LCD and VGA registers. These are the high performance peripherals, which are generally DMA targets.

The slow APB peripherals generally operate at the UART crystal clock frequency of 3.6864MHz, though register access via the APB is at ASB speed. The slow APB peripherals do not support DMA transfers. This arrangement of operating most of the peripherals from a slower clock, and reducing the load on the faster bus, results in significantly reduced power consumption. Both APB buses connect to the main ASB bus via specially modified bridges. The slow APB bridge takes care of all re-synchronization, handing over data and control signals between the ASB and UART clock domains in a safe and reliable manner.

The fast APB bridge is modified from the normal AMBA bridge, to allow DMA access to fast APB peripherals. Additional signals from the DMA controller to the APB bridge request, select and acknowledge DMA transfers to and from DMA-aware peripherals.

### **Architecture Overview**

### 3.2 SDRAM controller

### 3.2.1 Overview

The SDRAM controller is a key part of the GMS30C7201 architecture. The SDRAM controller has two data ports—one for video DMA and one for the main ASB—and interfaces to a single 16-bit wide SDRAM. One to four 16, 64 or 128Mbit x16-bit devices are supported, giving a memory size ranging from 2 to 64Mbytes.

### 3.2.2 Arbitration

The main ASB and video DMA buses are independent, and operate concurrently. The SDRAM controller contains the arbitration logic, for selecting between the two buses, and between the LCD and VGA on the video bus. The video bus is always higher priority than the main bus. The SDRAM controller uses a modified round-robin arbitration between the LCD and the VGA, but allows the highest priority device on the video bus to be programmed as either the LCD or the VGA.

The video interface consists of separate address and request inputs to the SDRAM controller, and shared data but individual acknowledge outputs to the VGA and the LCD. The video access burst size is fixed to 16 words. The address is non-incrementing for words within a burst (as the SDRAM controller only makes use of the first address for each burst request).

The arbitration scheme is modified round-robin. When the bus is idle, prioritization is fixed, with whichever LCD or VGA is programmed as highest priority getting data next, if they request data at the same time. When the bus is busy, the prioritization becomes round-robin, so if the higher priority device wants two bursts one immediately after the other, but the other device also requested a burst at the same time as the higher priority device, (or after, but before the first burst to the other device completed), then the lower priority device would get the second burst, and the higher priority device the third burst.

In use, the highest bandwidth video device (VGA or LCD) should be programmed as highest priority in the SDRAM controller. If both devices are equal priority, and use the same bandwidth, an arbitrary decision can be made. If only one video device is being used (for example, only LCD is being used, as will most often be the case), then that device should have the highest priority.

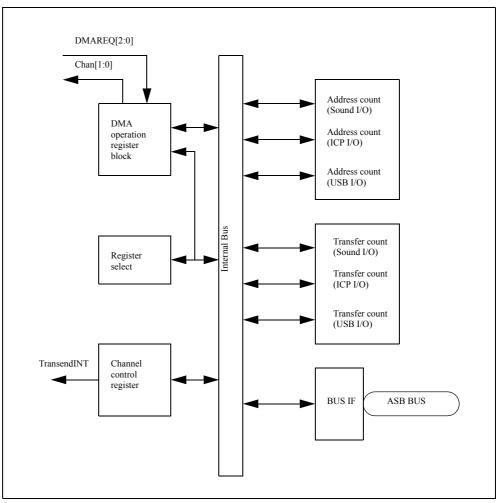

### 3.3 Peripheral DMA

#### 3.3.1 Overview

GMS30C7201 incorporates a three-channel, general-purpose DMA controller which operates on the ASB. The DMA controller is an AMBA compliant ASB bus master with a higher arbitration priority than either the ARM or Piccolo DSP coprocessor, to ensure low DMA latency. Since, however, the main ASB bus always has lower priority access to the SDRAM controller than the video bus, it will always get lower priority access to SDRAM than the LCD and VGA.

#### 3.3.2 Transfer sizes

The devices that make use of the peripheral DMA are:

- 1 USB

- 2 Fast/Medium IR

- 3 Sound output

The USB and FIR are bidirectional but half-duplex, so only one DMA channel is required at a time. The data rate for the USB is 12Mbit/sec, which translates to 1.5Mbyte/sec. The data rate for the FIR is a maximum of 4Mbit/sec, which translates to 0.5Mbyte/sec. The sound output data rate is 88.2KB/sec. To ensure reasonable usage of SDRAM, APB and ASB bandwidth, the transfer sizes to these device are:

| Quad-word |

|-----------|

| Word      |

| Word      |

|           |

The SDRAM controller will do a complete quad-word access for every SDRAM access. With the transfer sizes above, the approximate SDRAM bandwidth taken by the devices is:

| USB   | 3%    |

|-------|-------|

| FIR   | 4%    |

| Sound | 0.75% |

The maximum total of SDRAM bandwidth taken by all three devices running concurrently is 7.75%.

DMA accesses to FIR and Sound blocks are fully AMBA compliant, meaning that a word transfer takes a minimum of two bus cycles to complete. The APB protocol however, for USB DMA accesses, has been slightly modified to allow burst accesses.

### 3.3.3 Fly-by

The DMA controller is tightly coupled to the fast APB bridge. In order for the DMA Controller to start a transfer, it must first receive a DMA data request from one of the peripherals; it will then request mastership of the ASB.

Once granted, the DMA Controller will retain mastership of the ASB until the requested DMA transaction is completed, which ensures correct data in the DMA peripherals (that is data in the DMA peripherals cannot be modified by the ARM processor while a DMA transfer is in progress).

The DMA transfer request is monitored by the Fast APB bridge, who will perform the correspondent APB transfer by inverting the read/write line with respect to the ASB, to generate a **PWRITE** signal on the APB. The DMA transfer is acknowledged on the APB by asserting a **PSELDMA** signal for the given peripheral. The data is timed by **PSTB** as on a normal APB transfer. The APB address **PA** is not used for DMA transfers.

### MUNIX GMS30C7201 Data Sheet

### **Architecture Overview**

The APB bridge receives two signals from the DMA controller called **CHAN[1:0]**, which tells it which DMA channel (peripheral) the DMA access is for. All other information comes from monitoring the ASB bus signals. For example, the direction of transfer comes from **BWRITE** (the sense is inverted to get the APB signal), and when the SDRAM transfer completes, comes from the bridge monitoring the **BWAIT** ASB signal.

### 3.3.4 Timing

This is detailed in Chapter 12, Fast AMBA Peripherals.

### 3.3.5 Slow APB peripherals

Since the DMA controller is not coupled with the slow APB bridge, it is not possible to use DMA with devices on the slow APB bus. However, since devices on the slow APB bus are inherently low performance, this is not a serious restriction. Devices on the slow APB bus must use the ARM acting under interrupt control to simulate DMA. The highest data rate peripheral on the slow APB bus is the modem CODEC interface, at a maximum of 48KB/sec. The ARM FIQ is used to transfer data to the CODEC.

### 3.3.6 Sound output

In the GMS30C7201, the sound peripheral is located on the fast APB bus, and is supported by the DMA controller. (Note that this is compatible with some operating systems, which require DMA-support sound hardware.)

#### **3.4** Power management

The GMS30C7201 is designed for battery-powered portable applications and incorporates innovative design features in the bus structure and the PMU to reduce power consumption. The slow APB bus allows peripherals to be clocked slowly hence reducing power consumption. The use of three buses reduces the number of nodes that are toggled during a data access, thereby further reducing power consumption. In addition, clocks to peripherals which are not active can also be gated.

#### 3.4.1 Clock gating

The high performance peripherals, such as the SDRAM controller and the LCD controller, run most of the time at high frequencies and careful design, including the use of clock gating, has minimized their power consumption. The VGA controller can be powered down completely when not in use (that is, when not connected to an external monitor).

### 3.4.2 PMU

The Power Management Unit (PMU) is used to control the overall state the system is in. The system can be in one of five states:

#### Run

The system is running normally. All clocks are running (except where gated locally), and the SDRAM controller is performing normal refresh.

#### Slow

The system operates normally, except the ARM is placed into Fast Bus mode, and hence is clocked at half its normal rate.

#### Idle

In this mode, the PMU becomes the bus master until there is an interrupt for the CPU, or the peripheral DMA controller requests mastership of the bus.

#### Sleep

The SDRAM is placed into self-refresh mode, and internal clocks are gated off. This mode can only be entered from Idle mode (that is, the PMU must be ASB master before this mode can be entered). The PMU must get bus mastership to ensure that the system is stopped in a safe state and not, for example, half-way through an SDRAM write.

Usually this state is only to be entered briefly, on the way to entering deep sleep mode.

#### **Deep Sleep**

In deep sleep mode, the 3.6864MHz oscillator and the PLLs are disabled. This is the lowest power state available. Only the 32kHz oscillator runs. The real time clock and wakeup sections of the PMU are operated from this clock. Everything else is powered down, and SDRAM is in self-refresh mode. This is the normal system "off" mode.

Sleep and Deep Sleep modes are exited either by a user wake-up event (generally pressing the "On" key), an RTC wake-up alarm, a device reset request, or by a modem ring indicate event. These interrupt sources go directly to the PMU. In addition, the modem ring indicate signal also goes to the normal interrupt controller to signal an interrupt if there is a ring indicate event in a non-sleep mode.

## 3.5 Performance

#### **ARM720T** operation

The actual performance of the device will be highly application specific as well as dependent on the speed of memory attached and the rate at which data is being transferred to the DMA peripherals, in particular the LCD and VGA.

If a particular application or part of application is executing entirely from within the 720T cache then the memory speed and peripheral DMA bandwidth may not have any affect at all. However most applications will require access to either the static memory interface or the SDRAM interface for its data structures and for instructions whenever there are cache misses. The cache miss rate will have a large impact on the achievable performance, however it is impossible to predict this for any general application.

It is possible though to give some indication of the potential performance of the device when operating out of cache.

Run Mode operation (Cache on and operating at 60MHz, ASB clock at 30MHz): Approximately 75K Dhrystones/s (~42.6 DMIPS)

Slow Mode operation (Cache on and operating at the ASB clock frequency of 30MHz): Approximately 44K Dhrystones/s (~25 DMIPS)

\* Both sets of figures assume two wait state memory external memory is available and no peripheral DMA is active.

#### SP7 (Piccolo) operation

Once again it is not possible to generalize about the performance achievable on ARM720T when the SP7 co-processor (Piccolo) is being used, it will depend entirely on the frequency with which the ARM720T must transfer data to or from the SP7 co-processor which in turn is entirely application dependent.

The performance of the ARM7TDSP processing element is best illustrated by its performance for particular applications - it not possible to specify its performance in generalized MIPS terms.

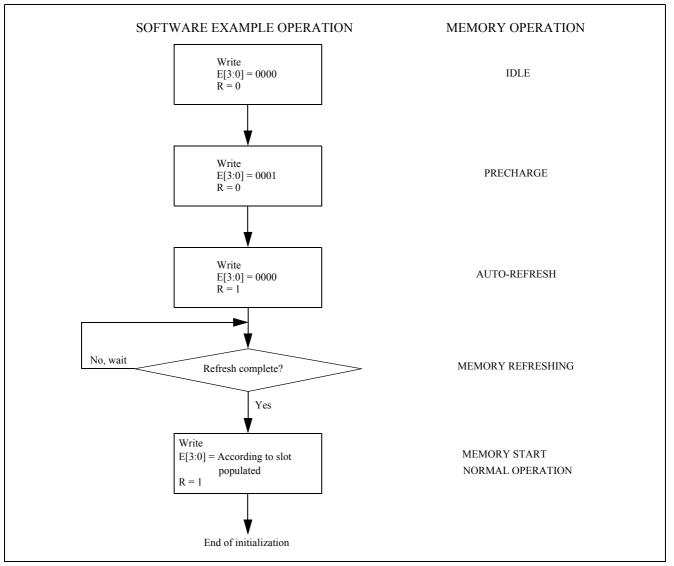

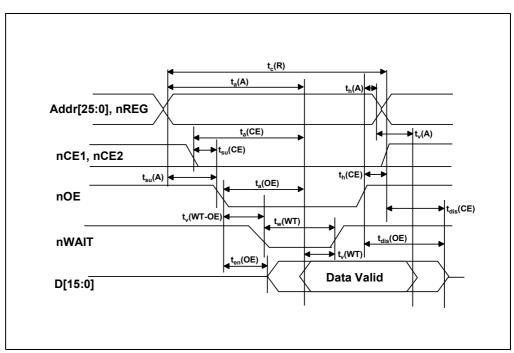

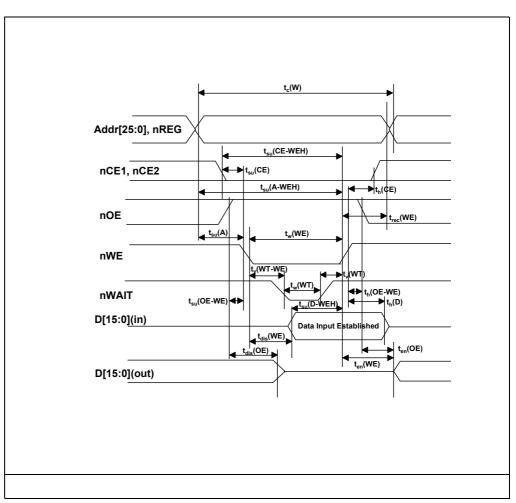

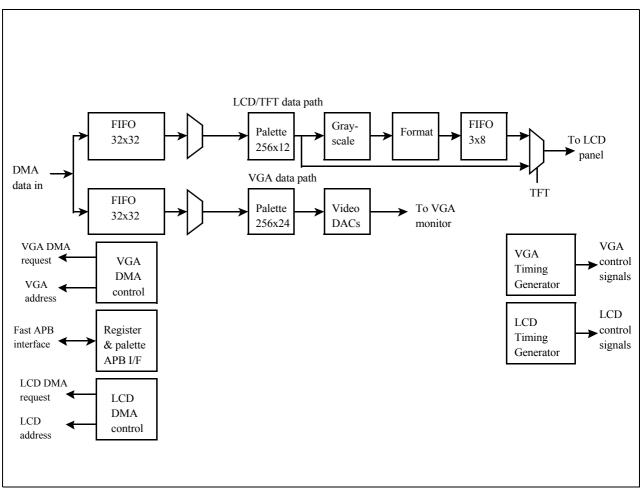

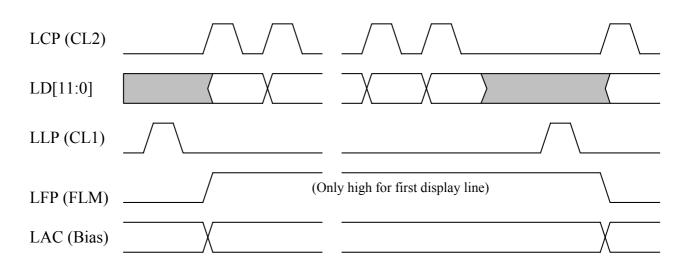

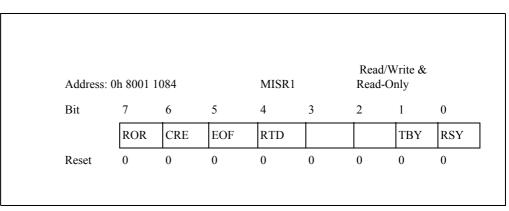

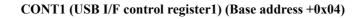

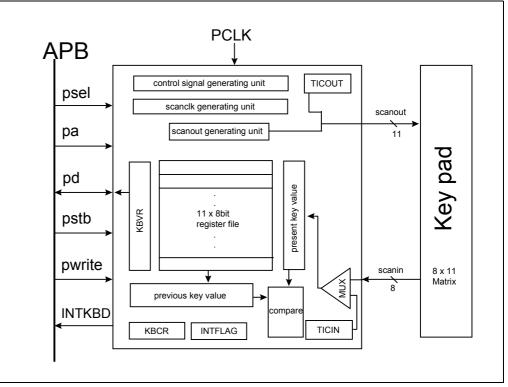

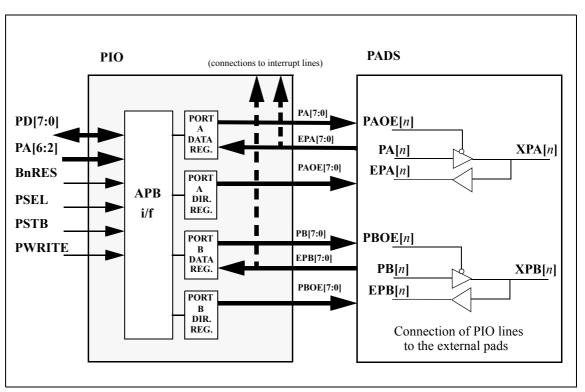

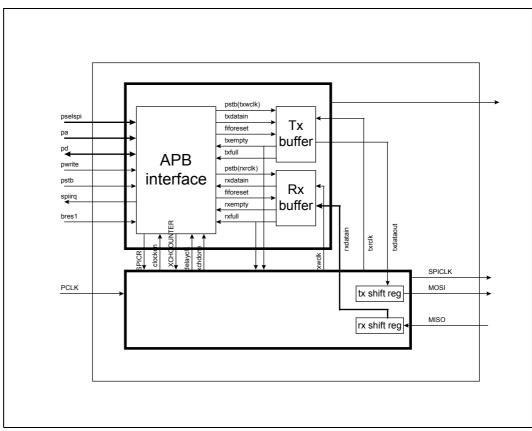

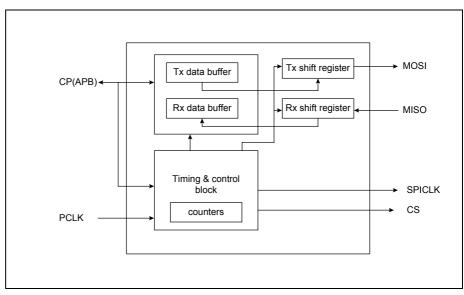

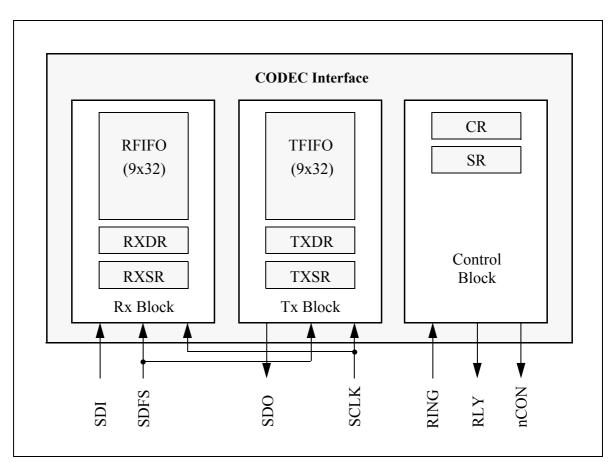

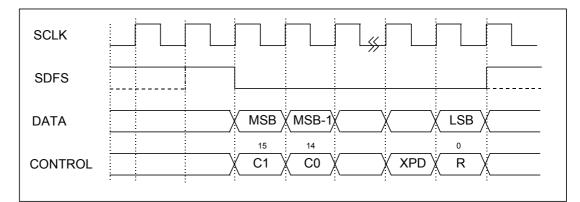

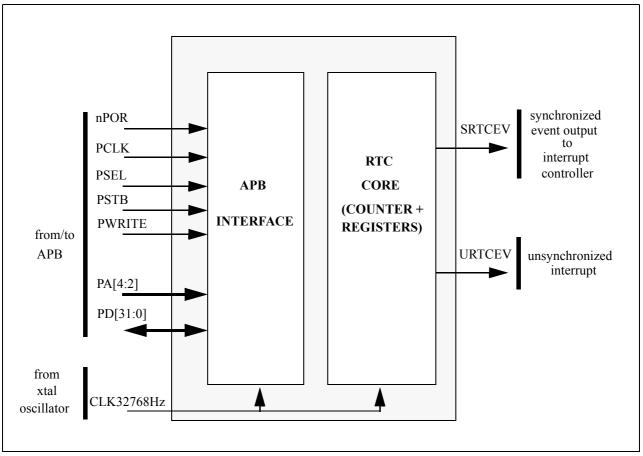

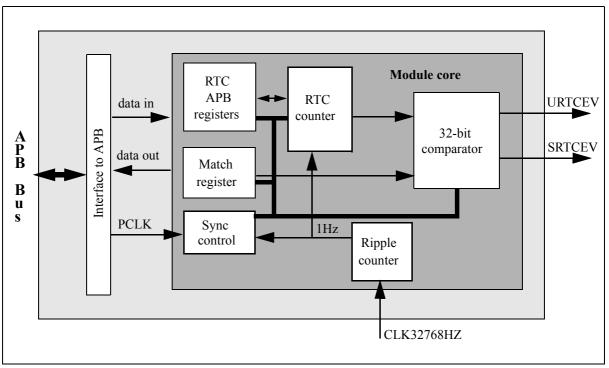

#### SoftModem Performance