# VM6101

## I<sup>2</sup>C color light sensor

## Features

- 4-channel Y+RGB photosensor, with integrated infrared filter

- Wide dynamic range light to frequency converters

- 2-wire serial interface, I<sup>2</sup>C and SMBus compatible

- PWM output for direct LCD backlight control

- Comparator logic with two programmable thresholds and hysteresis function

- Power down input

- 3.0 V to 3.6 V supply range

- Built-in clock generator, precision voltage and current references

- Low profile Pb-free package (RoHS compliant)

## Applications

- General purpose color measurement

- Automatic backlighting control

- Panel lighting

- White goods

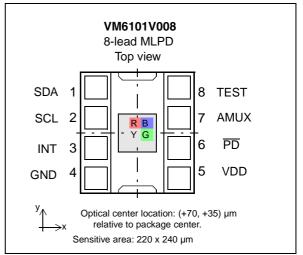

### Pinout

## Description

The VM6101 is a high dynamic range 4-channel CMOS photosensor suitable for ambient light sensing as well as color light sensing. Light intensity is converted linearly to a variable frequency signal. The signal period is readable through the two-wire serial interface.

A direct PWM output is provided for power saving LCD backlighting applications, where backlighting intensity adapts to the ambient light level. Alternatively, this output can be used as an ambient light level detector output, with two user programmable thresholds.

A power down input puts the VM6101 in ultra low power mode.

The VM6101 is housed in an compact 8-lead surface mount clear plastic package, compliant to RoHS directive.

# Contents

| 1 | Pin des  | Pin description                        |  |  |  |

|---|----------|----------------------------------------|--|--|--|

| 2 | Functio  | onal description                       |  |  |  |

|   | 2.1 L    | ight measurement channels 4            |  |  |  |

|   | 2.2 C    | Comparator logic                       |  |  |  |

|   | 2.3 F    | WM generator                           |  |  |  |

|   | 2.4 T    | wo-wire serial interface               |  |  |  |

|   | 2        | .4.1 Message types                     |  |  |  |

|   | 2        | .4.2 Alternate slave address selection |  |  |  |

| 3 | Applica  | tion information                       |  |  |  |

| 4 | Registe  | er description                         |  |  |  |

| 5 | Optical  | characteristics                        |  |  |  |

| 6 | Electric | al characteristics                     |  |  |  |

| 7 | Mechar   | nical information                      |  |  |  |

| 8 | Orderin  | g information                          |  |  |  |

| 9 | Revisio  | n history                              |  |  |  |

# 1 Pin description

| Table |      |      |                                                                                                                                                                                                                                                                  |  |  |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin   | Name | Туре | Description                                                                                                                                                                                                                                                      |  |  |

| 1     | SDA  | I/O  | Serial interface data. Requires external pull-up to VDD.                                                                                                                                                                                                         |  |  |

| 2     | SCL  | I/O  | Serial interface clock. Requires external pull-up to VDD.                                                                                                                                                                                                        |  |  |

| 3     | INT  | 1/0  | Dual function output:<br>- Comparator logic output<br>- PWM generator output<br>Input for serial interface 7-bit address select:<br>- low = address 0x10 (default)<br>- high = address 0x11<br>Requires external pull-up or pull-down resistor (1 MΩ typically). |  |  |

| 4     | GND  | PWR  | Ground                                                                                                                                                                                                                                                           |  |  |

| 5     | VDD  | PWR  | Positive power supply                                                                                                                                                                                                                                            |  |  |

| 6     | PD   | AIN  | Power down control:<br>- low = force low power standby<br>- high = normal operation                                                                                                                                                                              |  |  |

| 7     | AMUX | AIO  | Reserved. Do not connect.                                                                                                                                                                                                                                        |  |  |

| 8     | TEST | AIN  | Reserved. Connect to GND.                                                                                                                                                                                                                                        |  |  |

### Table 1.Pin description

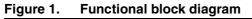

# 2 Functional description

57

57

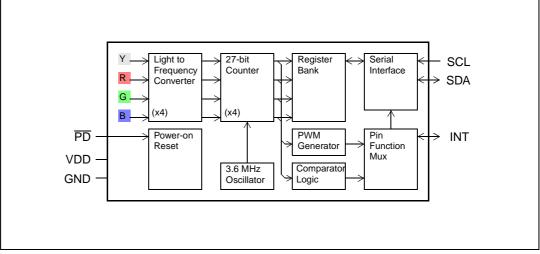

## 2.1 Light measurement channels

The VM6101 has four independent wide dynamic range photosensors and current-tofrequency converters. Each channel produces a digital output with a frequency proportional to the incoming light level on the photosensor. By construction, the device ensures automatic exposure control.

Figure 2. Light-to-Frequency converter (L2F)

The output period is measured using a 27-bit free-running counter and the internal 3.6 MHz oscillator clock; counter values are then read through the serial interface.

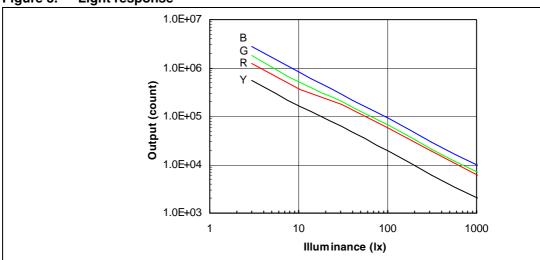

The typical light response is shown in *Figure 3*. below, obtained using a CIE D65 white point light source (~ daylight illumination) and no light diffuser.

Figure 3. Light response

The light response can be approximated by:

- Y channel:  $E_{vY} = 1.58e6 \text{ x count}^{-0.960}$

- R channel:  $E_{vR} = 3.34e6 \text{ x count}^{-0.902}$

- G channel:  $E_{vG} = 4.92e6 \text{ x count}^{-0.944}$

- B channel:  $E_{vB} = 8.03e6 \text{ x count}^{-0.973}$

The response time is:  $t = count / f_{OSC}$  + serial interface read time (about 200 µs) Example: t = 9.3 ms for 300 lx.

Each channel provides three status flags and a counter value:

- **RESET**: This flag is set upon reset or power-down resume. The counter value is invalid and should be discarded. This flag is cleared after a status read operation.

- **OVERFLOW**: at least one counter overflow occurred: the counter value is invalid and should be discarded. This flag is cleared when a new valid counter value is available.

- READY: a new counter value is available. This flag is cleared immediately after the status register read.

- CNT: a 27-bit counter value, mapped in 4 consecutive bytes, MSB first and right justified.

Channel readout must always start by reading the corresponding status register. The suggested read operation is a 5-byte read operation starting at the status register address.

Refer to Chapter 4: Register description for details.

## 2.2 Comparator logic

This function compares the light level (i.e. channel counter CNT) with two programmable thresholds (TH\_LO and TH\_HI) and drives the INT pin accordingly. The following table shows available configurations using TH\_CFG register setup:

| INT output                                                                | INT versus CNT                                                                                                                    |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                                                                           | (assumes INT_POL = 0)                                                                                                             |

| 0                                                                         | 0                                                                                                                                 |

| POL_LO xor (CNT < TH_LO)                                                  | 1 +                                                                                                                               |

|                                                                           | (POL_LO = 0)                                                                                                                      |

| POL_HI xor (CNT < TH_HI)                                                  | 1 +                                                                                                                               |

|                                                                           | (POL_HI = 0)                                                                                                                      |

| HYST = 0:<br>(POL_LO xor (CNT < TH_LO)) and<br>(POL_HI xor (CNT < TH_HI)) | $(POL_LO = 1, POL_HI = 0)$                                                                                                        |

| HYST = 1: see diagram                                                     | $(POL_LO = 1, POL_HI = 0)$                                                                                                        |

|                                                                           | POL_LO xor (CNT < TH_LO)<br>POL_HI xor (CNT < TH_HI)<br>HYST = 0:<br>(POL_LO xor (CNT < TH_LO)) and<br>(POL_HI xor (CNT < TH_HI)) |

Table 2. Threshold module configurations (TH\_CFG register usage)

#### Notes

- 1. Upon reset, the comparator logic is enabled (EN\_HI:EN\_LO = 01) with POL\_LO = 1 and TH\_LO = 0x0008. The INT pin is high when Y channel count > 8.

- 2. Assuming CONTROL= 0x04, i.e. comparator mode using Y channel count (default value for CONTROL register).

- 3. Ensure TH\_LO < TH\_HI otherwise unpredictable results may occur.

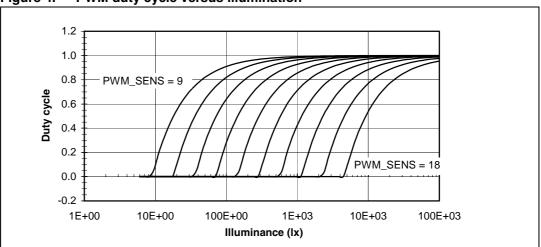

### 2.3 **PWM** generator

The pulse width modulator (PWM) generates a signal which may be used to directly control LCD backlight driver ICs according to ambient light level.

There are three registers to control the PWM generator operation:

- PWM\_FREQ register bits [4:0] sets the period of the PWM signal. This is adjustable from 12Hz to 400kHz.

- PWM\_SENS register bits [4:0] sets the sensitivity of the PWM signal to light level.

- CONTROL register bit 2 = 0 to select PWM output at INT pin.

- CONTROL register bit 3 controls the polarity of the PWM output (default = 0).

For more details please refer to Chapter 4: Register description.

The curve below shows typical PWM output duty cycle (default polarity) as a function of illumination, with sensitivity setting ranging from 9 to 18, corresponding to typical use cases (10 to 10000 lx illumination).

Figure 4. PWM duty cycle versus illumination

### 2.4 Two-wire serial interface

The VM6101 two-wire serial interface supports the following features:

- Standard-mode (100 kHz) I<sup>2</sup>C slave controller supporting 8-bit addressing (7-bit address = 0x10 or 0010 000). SMBus compliant.

- Data and clock deglitching filters (double sampling)

- 8-bit index, i.e. 256 on-chip register address space

- Multiple read or write with index auto-increment

- Alternate address (0x11) selectable

### 2.4.1 Message types

The VM6101 registers are accessed by serial bus byte-oriented transactions. The following message types are supported:

- Master write:

<S> <addr><w><A> <index><A> <data><A>[<data><A>...<data><A>]<P>

- Master read:

<S> <addr><r><A> [<data><A>...<data><A>]<data><nA><P>

- Combined format:

<S> <addr><w><A> <index><A>

<Sr> <addr><r><A> [<data><A>...<data><A>]<data><r><P>

where:

```

S = start, Sr = repeated start, P = stop, A = acknowledge, nA = negative acknowledge

addr = 7-bit slave address, w = write bit (0), r = read bit (1),

index = 8-bit register address,

data = 8-bit register data, [] = optional.

```

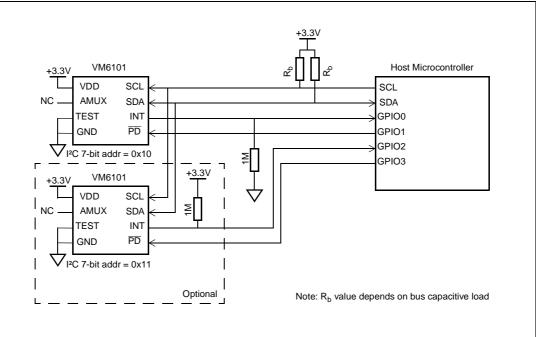

### 2.4.2 Alternate slave address selection

After power-on or after resuming from power-down, the 7-bit slave address is 0x10. If another slave device shares the same address, it is possible to remap the VM6101 to address 0x11 by performing the following operations:

- 1. Connect the INT pin to a pull-up resistor to  $V_{DD}$  (1 M $\Omega$  typ.).

- 2. After power-on or power-down resume, issue a write command to set the ADDR\_SEL bit of CONTROL register (i.e. write 0x10 at register address 0x02, slave address 0x10).

- At this time, the VM6101 samples the INT pin and sets its slave address accordingly: INT sampled low: 7-bit address = 0x10, INT sampled high: 7-bit address = 0x11.

Two VM6101 can thus coexist on the same bus; one should have its INT pin pulled low, the other one should have its INT pin pulled high (see *Figure 5*.).

## **3** Application information

#### Figure 5. Application diagram

# 4 Register description

Note: RO = Read Only; RW = Read/Write.

Reserved bits must be written with 0s and return 0 upon read; Reserved bytes must not be accessed otherwise unpredictable results my occur.

| Addr. | Bits  | Def. | Name      | Description                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-------|-------|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0x00  | [3:0] | 1    | REVISION  | Chip revision (RO).                                                                                                                                                                                                                                                                            |  |  |  |  |

| 0x00  | [7:4] | 0    | MASK      | Mask code (RO).                                                                                                                                                                                                                                                                                |  |  |  |  |

| 0x01  | [7:0] | 0x04 | N_PIXEL   | (RO)                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 0x02  | [6:0] | 0x04 | CONTROL   | Control register (RW)                                                                                                                                                                                                                                                                          |  |  |  |  |

|       | [1:0] | 0    | CHSEL     | Channel select for comparator and PWM logic:<br>0: Y<br>1: R<br>2: G<br>3: B                                                                                                                                                                                                                   |  |  |  |  |

|       | 2     | 1    | INT_FSEL  | INT pin function select:<br>0: PWM generator output<br>1: Comparator logic output                                                                                                                                                                                                              |  |  |  |  |

|       | 3     | 0    | PWM_POL   | PWM polarity:<br>0: Normal (Thin pulse for low values, Wide pulses for high values)<br>1: Inverted.                                                                                                                                                                                            |  |  |  |  |

|       | 4     | 0    | ADDR_SEL  | Address Select: when written with '1', the INT pin goes high impedance;<br>after a duration T (defined below), the INT pin is sampled and returns to<br>low impedance.<br>The device slave address is set accordingly:<br>INT sampled low: address = 0x20<br>INT sampled high: address = 0x22. |  |  |  |  |

|       | [6:5] | 0    | ADDR_SELW | Address select sampling window duration:<br>0: $T = 160 \ \mu s$ (default)<br>1: $T = 80 \ \mu s$<br>2: $T = 40 \ \mu s$<br>3: $T = 20 \ u s$<br>This duration allows for INT pin pull-up rise time.                                                                                           |  |  |  |  |

|       | 7     | 0    |           | Reserved                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 0x03  | [7:0] | 0    |           | Reserved (RO).                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 0x04  | [2:0] | 0x01 | Y_STATUS  | Y-channel status register (RO).<br>Reading this register will cause Y_CNT to be transferred to serial<br>interface buffer. 5 MSBs are read as zeros.                                                                                                                                           |  |  |  |  |

|       | 0     | 1    | RESET     | This bit is set after reset. Cleared after first read of STATUS register.                                                                                                                                                                                                                      |  |  |  |  |

|       | 1     | 0    | OVERFLOW  | This bit is set upon counter overflow: current counter values are invalid.                                                                                                                                                                                                                     |  |  |  |  |

|       | 2     | 0    | READY     | When set, indicates that a new count value is available in the 4 registers here below.                                                                                                                                                                                                         |  |  |  |  |

Table 3.Register description

| Table 3. | e 3. Register description (continued) |      |          |                                                                                                                                     |  |  |  |  |

|----------|---------------------------------------|------|----------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Addr.    | Bits                                  | Def. | Name     | Description                                                                                                                         |  |  |  |  |

| 0x05     | [2:0]                                 | 0    | Y_CNT3   | Y channel count bits [26:24] (RO). 5 MSBs are read as zeros.                                                                        |  |  |  |  |

| 0x06     | [7:0]                                 | 0    | Y_CNT2   | Y channel count bits [23:16] (RO)                                                                                                   |  |  |  |  |

| 0x07     | [7:0]                                 | 0    | Y_CNT1   | Y channel count bits [15:8] (RO)                                                                                                    |  |  |  |  |

| 0x08     | [7:0]                                 | 0    | Y_CNT0   | Y channel count bits [7:0] (RO)                                                                                                     |  |  |  |  |

| 0x09     | [7:0]                                 | 0x01 | R_STATUS | R channel status register (RO). Refer to Y Channel for description.                                                                 |  |  |  |  |

| 0x0a     | [2:0]                                 | 0x00 | R_CNT3   | R channel count bits [26:24] (RO). 5 MSBs are read as zeros.                                                                        |  |  |  |  |

| 0x0b     | [7:0]                                 | 0x00 | R_CNT2   | R channel count bits [23:16] (RO)                                                                                                   |  |  |  |  |

| 0x0c     | [7:0]                                 | 0x00 | R_CNT1   | R channel count bits [15:8] (RO)                                                                                                    |  |  |  |  |

| 0x0d     | [7:0]                                 | 0x00 | R_CNT0   | R channel count bits [7:0] (RO)                                                                                                     |  |  |  |  |

| 0x0e     | [7:0]                                 | 0x01 | G_STATUS | Channel status register (RO). Refer to Y Channel for description.                                                                   |  |  |  |  |

| 0x0f     | [2:0]                                 | 0x00 | G_CNT3   | channel count bits [26:24] (RO). 5 MSBs are read as zeros.                                                                          |  |  |  |  |

| 0x10     | [7:0]                                 | 0x00 | G_CNT2   | channel count bits [23:16] (RO)                                                                                                     |  |  |  |  |

| 0x11     | [7:0]                                 | 0x00 | G_CNT1   | G channel count bits [15:8] (RO)                                                                                                    |  |  |  |  |

| 0x12     | [7:0]                                 | 0x00 | G_CNT0   | G channel count bits [7:0] (RO)                                                                                                     |  |  |  |  |

| 0x13     | [7:0]                                 | 0x01 | B_STATUS | B channel status register (RO). Refer to Y Channel for description.                                                                 |  |  |  |  |

| 0x14     | [2:0]                                 | 0x00 | B_CNT3   | B channel count bits [26:24] (RO). 5 MSBs are read as zeros.                                                                        |  |  |  |  |

| 0x15     | [7:0]                                 | 0x00 | B_CNT2   | B channel count bits [23:16] (RO)                                                                                                   |  |  |  |  |

| 0x16     | [7:0]                                 | 0x00 | B_CNT1   | B channel count bits [15:8] (RO)                                                                                                    |  |  |  |  |

| 0x17     | [7:0]                                 | 0x00 | B_CNT0   | B channel count bits [7:0] (RO)                                                                                                     |  |  |  |  |

|          | [5:0]                                 | 0x03 | TH_CFG   | Comparator logic configuration (RW). 2 MSBs are reserved.<br>Refer to <i>Section 2.2: Comparator logic</i> for programming details. |  |  |  |  |

|          | 0                                     | 1    | EN_LO    | Enable low threshold comparator $(1 = enable, 0 = disable)$                                                                         |  |  |  |  |

| -        | 1                                     | 1    | POL_LO   | Low threshold comparator output polarity                                                                                            |  |  |  |  |

| 0x18     | 2                                     | 0    | EN_HI    | Enable high threshold comparator (1 = enable, 0 = disable)                                                                          |  |  |  |  |

|          | 3                                     | 0    | POL_HI   | High threshold comparator output polarity                                                                                           |  |  |  |  |

|          | 4                                     | 0    | INT_POL  | INT pin output polarity                                                                                                             |  |  |  |  |

|          | 5                                     | 0    | HYST     | Enable hysteresis function                                                                                                          |  |  |  |  |

| 0x19     | [2:0]                                 | 0x00 | TH_LO3   | Low threshold bits [26:24] (RW). 5 MSBs are read as zeros.                                                                          |  |  |  |  |

| 0x1a     | [7:0]                                 | 0x00 | TH_LO2   | Low threshold bits [23:16] (RW)                                                                                                     |  |  |  |  |

| 0x1b     | [7:0]                                 | 0x00 | TH_LO1   | Low threshold bits [15:8] (RW)                                                                                                      |  |  |  |  |

| 0x1c     | [7:0]                                 | 0x08 | TH_LO0   | Low threshold bits [7:0] (RW)                                                                                                       |  |  |  |  |

| 0x1d     | [2:0]                                 | 0x00 | TH_HI3   | High threshold bits [26:24] (RW). 5 MSBs are read as zeros.                                                                         |  |  |  |  |

| 0x1e     | [7:0]                                 | 0x00 | TH_HI2   | High threshold bits [23:16] (RW)                                                                                                    |  |  |  |  |

| 0x1f     | [7:0]                                 | 0x00 | TH_HI1   | High threshold bits [15:8] (RW)                                                                                                     |  |  |  |  |

| 0x20     | [7:0]                                 | 0    | TH_HI0   | High threshold bits [7:0] (RW)                                                                                                      |  |  |  |  |

Table 3.

Register description (continued)

| Addr.    | Bits  | Def. | Name     | Description                                                                  |  |  |  |  |

|----------|-------|------|----------|------------------------------------------------------------------------------|--|--|--|--|

| 0x21     | [3:0] | 0x00 | PWM_FREQ | PWM output frequency (RW)(4 MSBs are reserved):                              |  |  |  |  |

|          |       |      |          | n = 0 to 15                                                                  |  |  |  |  |

|          |       |      |          | $f_{PWM} = f_{OSC} * 2^{n-18}$ , where $f_{OSC} = 3.6$ MHz.                  |  |  |  |  |

| 0x22     | [4:0] | 0x00 | PWM_SENS | PWM sensitivity (RW)(3 MSBs are reserved):                                   |  |  |  |  |

|          |       |      |          | n = 0 to 26                                                                  |  |  |  |  |

|          |       |      |          | 0 = high sensitivity, $26 =$ low sensitivity. Practical values lie between 9 |  |  |  |  |

|          |       |      |          | and 18. Refer to Figure 4: PWM duty cycle versus illumination for            |  |  |  |  |

|          |       |      |          | typical behavior.                                                            |  |  |  |  |

| 0x22     | [7:0] |      |          | Reserved.                                                                    |  |  |  |  |

|          |       |      |          |                                                                              |  |  |  |  |

| 0x27     |       |      |          |                                                                              |  |  |  |  |

| 0x28     | [7:0] | 0x04 | TEST_MOD | Reserved (RW).                                                               |  |  |  |  |

| 0x29     | [7:0] | 0x00 | TEST_SEL | Reserved (RW).                                                               |  |  |  |  |

| 0x2A     | [7:0] |      |          | Reserved.                                                                    |  |  |  |  |

| <br>0xFF |       |      |          |                                                                              |  |  |  |  |

| 0xFF     |       |      |          |                                                                              |  |  |  |  |

Table 3.

Register description (continued)

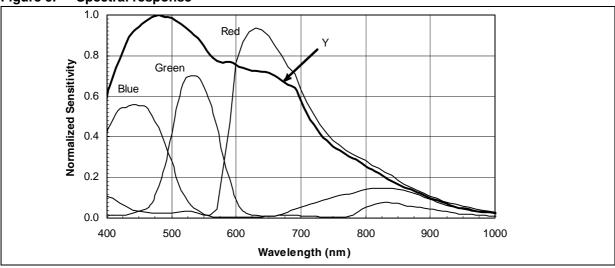

# 5 Optical characteristics

| Table 4. | Optical characteristics <sup>(1)</sup> |

|----------|----------------------------------------|

|----------|----------------------------------------|

| Symbol | Parameter         | Conditions | Min    | Тур | Max  | Unit |

|--------|-------------------|------------|--------|-----|------|------|

| E      | Irradiance range  |            | 0.0001 |     | 800  | Wm⁻² |

| Ev     | Illuminance range |            | 0.03   |     | 170k | lx   |

1. Using typical operating conditions:  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V

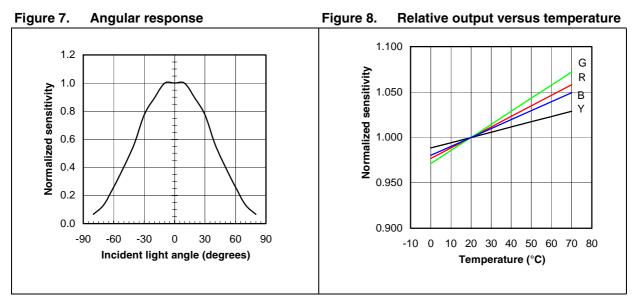

### Figure 6. Spectral response

# 6 Electrical characteristics

### Table 5. Absolute maximum ratings (Note 1, Note 2)

| Symbol             | Parameter                                                | Min  | Max                   | Unit |

|--------------------|----------------------------------------------------------|------|-----------------------|------|

| V <sub>DD</sub>    | Supply voltage                                           | -0.5 | 3.7                   | V    |

| V <sub>IN</sub>    | DC input voltage, all I/O pins                           | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| T <sub>STG</sub>   | Storage temperature                                      | -40  | 85                    | °C   |

| TL                 | Solder reflow peak temperature, JEDEC J STD-020          |      | 245                   | °C   |

| ESD <sub>HBM</sub> | Human body model ESD rating, all pins, JESD22-A114-B     |      | 2                     | kV   |

| ESD <sub>MM</sub>  | Machine model ESD rating, all pins, JESD22-A115-B        |      | 200                   | V    |

| ESD <sub>CDM</sub> | Charged device model ESD rating, all pins, JESD22-C101-C |      | 500                   | V    |

### Table 6. Recommended operating conditions

| Symbol          | Parameter                     | Min                 | Max                 | Unit |

|-----------------|-------------------------------|---------------------|---------------------|------|

| T <sub>A</sub>  | Operating temperature         | 0                   | 70                  | °C   |

| V <sub>DD</sub> | Supply voltage                | 3.0                 | 3.6                 | V    |

| V <sub>IL</sub> | Input low voltage (SCL, SDA)  | 0                   | 0.3 V <sub>DD</sub> | V    |

|                 | Input low voltage (PD)        | 0                   | 0.8                 | V    |

| V <sub>IH</sub> | Input high voltage (SCL, SDA) | 0.7 V <sub>DD</sub> | V <sub>DD</sub>     | V    |

|                 | Input high voltage (PD)       | 2.0                 |                     | V    |

| I <sub>OL</sub> | Output low current            |                     | 4                   | mA   |

| I <sub>OH</sub> | Output high current           |                     | 4                   | mA   |

### Table 7. DC electrical characteristics (*Note 3*)

| Symbol            | Parameter                     | Conditions                                   | Min | Max | Unit |

|-------------------|-------------------------------|----------------------------------------------|-----|-----|------|

| V <sub>OL</sub>   | Output low voltage (SDA, INT) | I <sub>OL</sub> = max, V <sub>DD</sub> = min |     | 0.4 | V    |

| V <sub>OH</sub>   | Output high voltage (INT)     | I <sub>OH</sub> = max, V <sub>DD</sub> = min | 2.4 |     | V    |

| IIL               | Input leakage current         | All I/O pins                                 | -1  | +1  | μA   |

| I <sub>DDPD</sub> | Supply current, power-down    | PD low (Note 4)                              |     | 1.0 | μA   |

| I <sub>DD</sub>   | Supply current, active        | PD high (Note 4)                             |     | 1.1 | mA   |

### Table 8. AC electrical characteristics (*Note 3*)

| Symbol           | Parameter                     | Conditions | Min | Тур | Max | Unit |

|------------------|-------------------------------|------------|-----|-----|-----|------|

| f <sub>OSC</sub> | Internal oscillator frequency |            |     | 3.6 |     | MHz  |

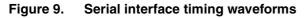

| Symbol              | Parameter                                            | Min | Max | Unit |

|---------------------|------------------------------------------------------|-----|-----|------|

| f <sub>SCL</sub>    | SCL clock frequency                                  | 0   | 100 | kHz  |

| t <sub>LOW</sub>    | SCL clock low period                                 | 4.7 |     | μs   |

| t <sub>HIGH</sub>   | SCL clock high period                                | 4.0 |     | μs   |

| t <sub>SU;STA</sub> | (Repeated) START condition setup time                | 4.7 |     | μs   |

| t <sub>HD;STA</sub> | (Repeated) START condition hold time                 | 4.0 |     | μs   |

| t <sub>SU;DAT</sub> | Data setup time                                      | 250 |     | ns   |

| t <sub>HD;DAT</sub> | Data hold time                                       | 300 |     | ns   |

| t <sub>SU;STO</sub> | STOP condition setup time                            | 4.0 |     | ns   |

| t <sub>BUF</sub>    | Bus free condition between START and STOP conditions | 4.7 |     | μs   |

| t <sub>R</sub>      | Rise time of both SDA and SCL signals                |     | 300 | ns   |

| t <sub>F</sub>      | Fall time of both SDA and SCL signals                |     | 300 | ns   |

| Cb                  | Capacitive load for each bus line                    |     | 400 | pF   |

Table 9.

Serial interface timing (Note 3)

- Note: 1 Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2 Unless otherwise specified, all voltages are referenced to ground.

- 3 Over recommended operating conditions, unless otherwise specified.

- 4 Using typical operating conditions:  $T_A = 25 \text{ °C}$ ,  $V_{DD} = 3.3 \text{ V}$

57

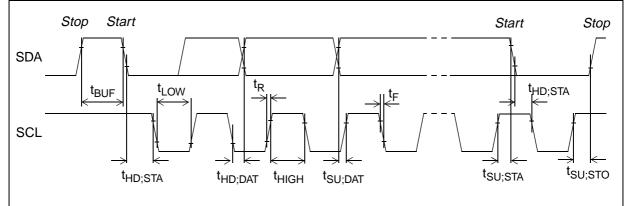

# 7 Mechanical information

| Symbol                        | Min  | Тур  | Max  |  |

|-------------------------------|------|------|------|--|

| А                             | 0.65 | 0.7  | 0.75 |  |

| A3                            |      | 0.20 |      |  |

| b                             | 0.25 | 0.30 | 0.35 |  |

| D                             | 2.90 | 3.00 | 3.10 |  |

| D2                            | 2.20 | 2.35 | 2.45 |  |

| Е                             | 2.90 | 3.00 | 3.10 |  |

| E2                            | 1.00 | 1.15 | 1.25 |  |

| е                             |      | 0.65 |      |  |

| L                             | 0.55 | 0.60 | 0.65 |  |

| All dimensions in millimeters |      |      |      |  |

Figure 11. Recommended PCB layout

57

# 8 Ordering information

### Table 10. Order codes

| Part number   | Description                                                                     |

|---------------|---------------------------------------------------------------------------------|

| VM6101V008    | 8-lead MLPD 3 x 3 x 0.7 mm, RoHS compliant, tray packing.                       |

| VM6101V008/TR | 8-lead MLPD 3 x 3 x 0.7 mm, RoHS compliant, 13" tape and reel, 5000 parts/reel. |

| STV-6101-R01  | VM6101 evaluation board                                                         |

# 9 Revision history

| Table 11. | Document revision history |

|-----------|---------------------------|

|-----------|---------------------------|

| Date          | Revision | Changes                                                                              |

|---------------|----------|--------------------------------------------------------------------------------------|

| 05-Jun-2006   | 1        | Initial release                                                                      |

| 14-Dec-2006   | 2        | Global update                                                                        |

| 27-Apr-2007 3 |          | Updated Chapter 6: Electrical characteristics and Chapter 4:<br>Register description |

#### **Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com