## **Advance Information**

#### 4-BIT DATA BUS INPUT PLL FREQUENCY SYNTHESIZER

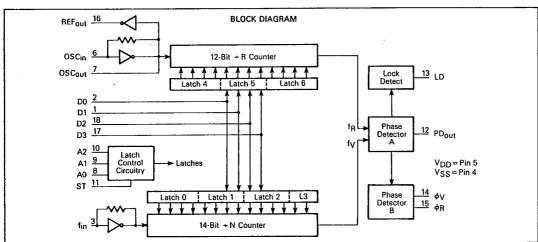

The MC145145-1 is programmed by a 4-bit input, with strobe and address lines. The device features consist of a reference oscillator, 12-bit programmable reference divider, digital-phase detector, 14-bit programmable divide-by-N counter and the necessary latch circuitry for accepting the 4-bit input data. When combined with a loop filter and VCO, the MC145145-1 can provide all the remaining functions for a PLL frequency synthesizer operating up to the device's frequency limit. For higher VCO frequency operation, a down mixer or a fixed divide prescaler can be used between the VCO and MC145145-1.

The MC145145-1 offers improved performance over the MC145145. The ac characteristics have been improved and the input current requirements have been modified.

- General Purpose Applications: CATV TV Tuning AM/FM Radios Scanning Receivers Two Way Radios Amateur Radio

- Low Power Consumption

- 3.0 to 9.0 V Supply Range

- On- or Off-Chip Reference Oscillator Operation

- Single Modulus 4-Bit Data Bus Programming

- ÷ R Range = 3 to 4095

- ÷ N Range = 3 to 16383

- "Linearized" Digital Phase Detector Enhances Transfer Function Linearity

- Two Error Signal Options: Single Ended (Three State) Double Ended

## **HIGH-PERFORMANCE CMOS**

LOW-POWER COMPLEMENTARY MOS SILICON-GATE

4-BIT DATA BUS INPUT PLL FREQUENCY SYNTHESIZER

This document contains information on a new product. Specifications and information herein are subject to change without notice.

MAXIMUM RATINGS\* (Voltages Referenced to VSS)

| Parameter                                          | Value                                                          | Unit                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC Supply Voltage                                  | -0.5 to +10                                                    | ٧                                                                                                                                                                                                                                                                                                                                                                                               |

| Input or Output Voltage (DC or Transient)          | -0.5 to V <sub>DD</sub> +0.5                                   | ٧                                                                                                                                                                                                                                                                                                                                                                                               |

| Input or Output Current (DC or Transient), per Pin | ± 10                                                           | mΑ                                                                                                                                                                                                                                                                                                                                                                                              |

| Supply Current, VDD or VSS Pins                    | ±30                                                            | mΑ                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                    | 500                                                            | mW                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                    | -65 to +150                                                    | °C                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                    | 260                                                            | °C.                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                    | DC Supply Voltage<br>Input or Output Voltage (DC or Transient) | DC Supply Voltage         −0.5 to +10           Input or Output Voltage (DC or Transient)         −0.5 to V <sub>DD</sub> +0.5           Input or Output Current (DC or Transient), per Pin         ± 10           Supply Current, V <sub>DD</sub> or V <sub>SS</sub> Pins         ± 30           Power Dissipation, per Package†         500           Storage Temperature         −65 to +150 |

Maximum Ratings are those values beyond which damage to the device may occur.

tPower Dissipation Temperature Derating:

Ceramic "L" Package: No derating

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation it is recommended that Vin and Vout be constrained to the range V<sub>SS</sub>≤(V<sub>in</sub> or V<sub>out</sub>)≤V<sub>DD</sub>. Unused inputs must always be tied to

an appropriate logic voltage level (e.g., either VSS or VDD).

# ELECTRICAL CHARACTERISTICS (Voltages Referenced to VSS)

|                                                                                       |                 |             | 40                      | )°C                  |                         | 25°C                    |                      | 85                      | <u>`C</u>            |       |

|---------------------------------------------------------------------------------------|-----------------|-------------|-------------------------|----------------------|-------------------------|-------------------------|----------------------|-------------------------|----------------------|-------|

| Characteristic                                                                        | Symbol          | VDD         | Min                     | Max                  | Min                     | Тур                     | Max                  | Min                     | Max                  | Units |

| Power Supply Voltage Range                                                            | VDD             | _           | 3                       | 9                    | 3                       |                         | 9                    | 3                       | . 9                  | ٧     |

| Output Voltage 0 Level  Vin=0 V or VDD  Iout=0 µA                                     | VOL             | 3<br>5<br>9 | 1 1 1                   | 0.05<br>0.05<br>0.05 | 1 1 1                   | 0.001<br>0.001<br>0.001 | 0.05<br>0.05<br>0.05 | -                       | 0.05<br>0.05<br>0.05 | ٧     |

| 1 Level                                                                               | VOH             | 3<br>5<br>9 | 2.95<br>4.95<br>8.95    |                      | 2.95<br>4.95<br>8.95    | 2.999<br>4.999<br>8.999 | -                    | 2.95<br>4.95<br>8.95    | 1 1 1                |       |

| Input Voltage 0 Level  Vout = 0.5 V or VDD - 0.5 V  (All Outputs Except OSCout)       | V <sub>IL</sub> | 3<br>5<br>9 | -                       | 0.9<br>1.5<br>2.7    | -<br>-<br>-             | 1.35<br>2.25<br>4.05    | 0.9<br>1.5<br>2.7    | -<br>-<br>-<br>2.1      | 0.9<br>1.5<br>2.7    | v     |

| 1 Level                                                                               | ViH             | 3<br>5<br>9 | 2.1<br>3.5<br>6.3       | -                    | 2.1<br>3.5<br>6.3       | 2.75<br>4.95            | <u>-</u>             | 3.5<br>6.3              | <u>-</u>             |       |

| Output Current  Vout = 2.7 V Source  Vout = 4.6 V  Vout = 8.5 V                       | Іон             | 3<br>5<br>9 | -0.44<br>-0.64<br>-1.30 | -                    | -0.35<br>-0.51<br>-1.00 | - 1.0<br>- 1.2<br>- 2.0 | -<br>-<br>-          | -0.22<br>-0.36<br>-0.70 |                      | mA    |

| V <sub>Out</sub> = 0.3 V Sink<br>V <sub>Out</sub> = 0.4 V<br>V <sub>Out</sub> = 0.5 V | 10L             | 3<br>5<br>9 | 0.44<br>0.64<br>1.30    | -<br>-<br>-          | 0.35<br>0.51<br>1.00    | 1.0<br>1.2<br>2.0       | -<br>-<br>-          | 0.22<br>0.36<br>0.70    | -                    |       |

| Input Current — Other Inputs                                                          | Iin             | 9           |                         | ±0.3                 |                         | ± 0.00001               | ± 0.1                |                         | ± 1.0                | μA    |

| Input Current - fin, OSCin                                                            | lin             | 9           | _                       | ±50                  |                         | ± 10                    | ± 25                 |                         | ± 22                 | μΑ    |

| Input Capacitance                                                                     | Cin             | _           | _                       | 10                   | _                       | 6                       | 10                   |                         | 10                   | pF    |

| 3-State Output Capacitance — PDout                                                    | Cout            | _           |                         | 10                   | _                       | 6                       | 10                   | . –                     | 10                   | pF    |

| Quiescent Current Vin=0 V or VDD Iout=0 µA                                            | IDD             | 3<br>5<br>9 | -<br>-                  | 800<br>1200<br>1600  | -                       | 200<br>300<br>400       | 800<br>1200<br>1600  | -<br>-<br>-             | 1600<br>2400<br>3200 | μΑ    |

| 3-State Leakage Current — PD <sub>out</sub> V <sub>out</sub> =0 V or 9 V              | loz             | 9           |                         | ±0.3                 |                         | ± 0.0001                | ± 0.1                | _                       | ± 3.0                | μА    |

Plastic "P" Package: - 12 mW/ °C from 65°C to 85°C

MOTOROLA SC LOGIC T-50-17 14E D 6367252 0082562 2

# MC145145-1

#### SWITCHING CHARACTERISTICS (TA = 25°C, CL = 50 pF)

| Characteristic                                         | Symbol                          | V <sub>DD</sub> | Min  | Тур | Max | Units |

|--------------------------------------------------------|---------------------------------|-----------------|------|-----|-----|-------|

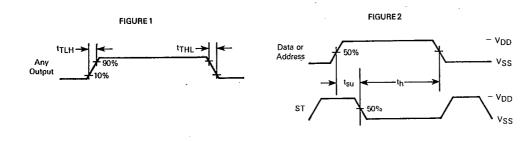

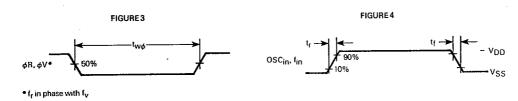

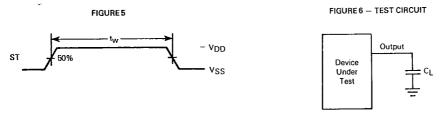

| Output Rise and Fall Time (Figures 1 and 6)            | t <sub>TLH</sub> ,              | 3               |      | 60  | 140 | ns    |

|                                                        | t <sub>THL</sub>                | .5              | _    | 40  | 80  |       |

|                                                        | "                               | 9               | - '  | 30  | 60  |       |

| Setup Times                                            | t <sub>su</sub>                 | 3               | 10   | 0   | _   | ns    |

| Data to ST (Figure 2)                                  |                                 | 5               | 10   | 0   | -   | ١.    |

|                                                        |                                 | 9               | 10   | 0   | -   | l     |

| Address to ST (Figure 2)                               |                                 | 3               | 80   | 60  | -   | i     |

|                                                        |                                 | 5               | 50   | 30  | -   |       |

|                                                        |                                 | 9               | 30   | 18  | -   |       |

| Hold Times                                             | th                              | 3               | 25   | 10  | -   | ns    |

| Data to Strobe (Figure 2)                              | I "                             | 5               | 20   | 10  | -   | 1     |

|                                                        |                                 | 9               | 15   | 10  | _   |       |

| Address to Strobe (Figure 2)                           |                                 | 3               | 35   | 15  | _   |       |

|                                                        |                                 | 5               | 25 . | 10  |     | İ     |

|                                                        |                                 | 9               | 20   | 10  | -   |       |

| Output Pulse Width                                     | twø                             | 3               | 25   | 100 | 175 | ns    |

| φ <sub>R</sub> , φ <sub>V</sub> with f <sub>R</sub> in | 1 "                             | 5               | 20   | 60  | 100 | 1     |

| Phase with fy (Figures 3 and 6)                        |                                 | 9               | 10   | 40  | 70  | 1     |

| Input Rise and Fall Times                              | t <sub>r</sub> , t <sub>f</sub> | 3               | -    | 20  | 5   | μs    |

| OSC <sub>in</sub> , f <sub>in</sub> (Figure 4)         |                                 | 5               | -    | 5   | 2   |       |

|                                                        |                                 | 9               | -    | 2   | 0.5 |       |

| Input Pulse Width                                      | tw                              | 3               | 40   | 30  | _   | ns    |

| ST (Figure 5)                                          | I                               | 5               | 35   | 20  | -   |       |

| -                                                      |                                 | 9               | 25   | 15  | _   | 1     |

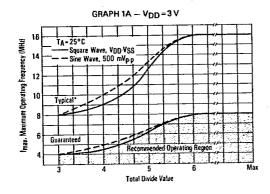

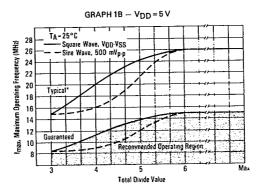

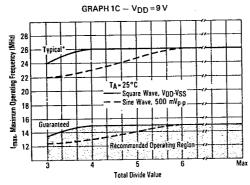

GRAPH 1 —  $OSC_{in}$  AND  $f_{in}$  MAXIMUM FREQUENCY VERSUS TOTAL DIVIDE VALUE

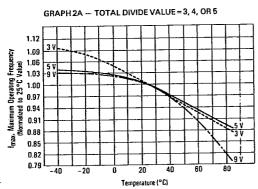

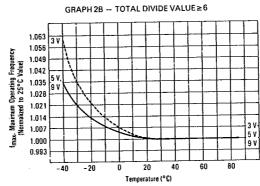

GRAPH 2 -  ${\rm OSC_{in}}$  and  ${\rm f_{in}}$  maximum frequency versus temperature for sine and square wave inputs

<sup>\*</sup>Data labelled "Typical" is not to be used for design purposes, but is intended as an indication of the IC's potential performance

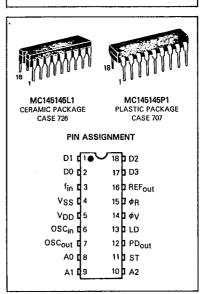

#### PIN DESCRIPTIONS

DATA INPUTS (Pins 2, 1, 18, 17) — Information at these inputs is transferred to the internal latches when the ST input is in the high state. Pin 17 (D3) is most significant.

fin (Pin 3) — Input to +N portion of synthesizer, fin is typically derived from loop VCO and is AC coupled into Pin 3. For larger amplitude signals (standard CMOS-logic levels) DC coupling may be used.

VSS (Pin 4) - Circuit Ground.

Vpp (Pin 5) - Positive power supply.

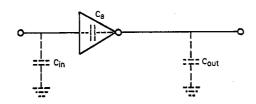

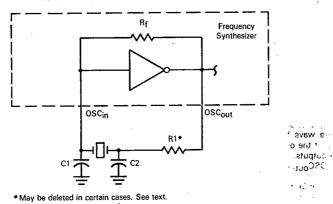

OSC<sub>in</sub>, OSC<sub>out</sub> (Pins 6 and 7) — These pins form an onchip reference oscillator when connected to terminals of an external parallel resonant crystal. Frequency setting capacitors of appropriate value must be connected from OSC<sub>in</sub> to ground and OSC<sub>out</sub> to ground. OSC<sub>in</sub> may also serve as input for an externally-generated reference signal. This signal will typically be AC coupled to OSC<sub>in</sub>, but for larger amplitude signals (standard CMOS-logic levels) DC coupling may also be used. In the external reference mode, no connection is required to OSC<sub>out</sub>.

ADDRESS INPUTS (Pins 8, 9, 10) - A0, A1 and A2 are used to define which latch receives the information on the data input lines. The addresses refer to the following latches:

| <b>A2</b> | A1 | Á0  | Selected | Function       | D0 | D1 | D2 | D3 |

|-----------|----|-----|----------|----------------|----|----|----|----|

| 0         | 0  | 0   | Latch 0  | -N Bits        | 0  | 1  | 2  | 3  |

| 0         | 0  | 1   | Latch 1  | +N Bits        |    | 5  | 6  | 7  |

| 0         | 1  | 0   | Latch 2  | + N Bits       | 8  | 9  | 10 | 11 |

| Ð         | 1  | 1   | Latch 3  | +N Bits        | 12 | 13 | -  | _  |

| 1         | 0  | 0   | Latch 4  | Reference Bits | 0  | 1  | 2  | 3  |

| 1         | 0  | 1   | Latch 5  | Reference Bits | 4  | 5  | 6  | 7  |

| 1         | 1  | 0   | Latch 6  | Reference Bits | 8  | 9  | 10 | 11 |

| 1         | 1  | 1 1 | · –      | -              | _  | _  | _  | _  |

ST (Pin 11) — When high, this input will enter the data that appears at the D0, D1, D2 and D3 inputs, and when low, will latch that information. When high, any changes in the data information will be transferred into the latches.

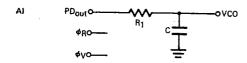

PD<sub>out</sub> (Pin 12) — Three-state output of phase detector for use as loop error signal.

Frequency fy>fg or fy Leading: Negative Pulses.

Frequency fy<fg or fy Lagging: Positive Pulses.

Frequency fy=fg and Phase Coincidence: HighImpedance State.

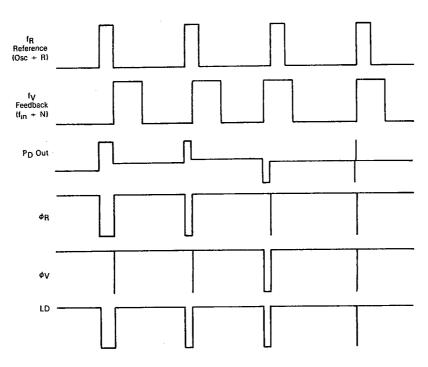

LD (Pin 13) — Lock detector signal. High level when loop is locked (f $_{\rm R}$ , fy of same phase and frequency). Pulses low when loop is out of lock.

$\phi_V,\,\phi_R$  (Pins 14 and 15) — These phase detector outputs can be combined externally for a loop error signal. A single-ended output is also available for this purpose (see PDout).

If frequency fy is greater than  $f_R$  or if the phase of fy is leading, then error information is provided by  $\phi_V$  pulsing low.  $\phi_R$  remains essentially high.

If the frquency fy is less than f $\eta$  or if the phase of fy is lagging, then error information is provided by  $\phi \eta$  pulsing low.  $\phi \gamma$  remains essentially high.

If the frequency of  $f_V = f_R$  and both are in phase, then both  $\phi_V$  and  $\phi_R$  remain high except for a small minimum time period when both pulse low in phase.

REF<sub>out</sub> (Pin 16) — Buffered output of on-chip reference oscillator or externally provided reference-input signal.

## SWITCHING WAVEFORMS

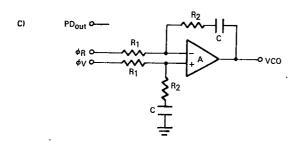

#### PHASE LOCKED LOOP - LOW PASS FILTER DESIGN

$$\omega_{\rm n} = \sqrt{\frac{K_{\phi}K_{\rm VC}}{NR_{1}C}}$$

$$\xi = \frac{N\omega_{\rm n}}{2K_{\phi}K_{\rm VCO}}$$

$$\omega_{n} = \sqrt{\frac{K_{\phi}K_{VCO}}{NC(R_{1} + R_{2})}}$$

$$f = 0.5\omega_{n} \left(R_{2}C + \frac{N}{K_{\phi}K_{VCO}}\right)$$

$$F(s) = \frac{R_{2}CS + 1}{S(R_{1}C + R_{2}CJ + 1)}$$

$$\omega_{\rm n} = \sqrt{\frac{\kappa_{\phi} \kappa_{\rm VCO}}{NCR_1}}$$

$$\xi = \frac{\omega_{\rm n} R_2 C}{2}$$

Assuming gain A is very large, then:

$$F(s) = \frac{R_2CS + 1}{R_1CS}$$

NOTE: Sometimes  $R_1$  is split into two series resistors each  $R_1 + 2$ . A capacitor  $C_C$  is then placed from the midpoint to ground to further filter  $\phi_V$  and  $\phi_R$ . The value of  $C_C$  should be such that the corner frequency of this network does not significantly affect  $\omega_R$ .

DEFINITIONS: N = Total Division Ratio in feedback loop  $K_{\phi} = V_{DD}/4\pi$  for  $PD_{out}$   $K_{\phi} = V_{DD}/2\pi$  for  $\phi_{V}$  and  $\phi_{R}$  $K_{VCO} = \frac{2\pi\Delta f_{VCO}}{2\pi}$ ΔV<sub>V</sub>CO

for a typical design  $\omega_{\Omega} \cong \frac{2\pi fr}{10}$  (at phase detector input),

#### RECOMMENDED FOR READING:

Gardner, Floyd M., Phaselock Techniques Isecond edition). New York, Wiley-Interscience, 1979.

Manassewitsch, Vadim, Frequency Synthesizers: Theory and Design Isecond edition). New York, Wiley-Interscience, 1980.

Blanchard, Alain, Phase-Locked Loops: Application to Coherent Receiver Design. New York, Wiley-Interscience, 1976.

Egan, William F., Frequency Synthesis by Phase Lock. New York, Wiley-Interscience, 1981.

Rohde, Ulrich L., Digital PLL Frequency Synthesizers Theory and Design. Englewood Cliffs, NJ, Prentice-Hall, 1983.

Berlin, Howard M., Design of Phase-Locked Loop Circuits, with Experiments. Indianapolis, Howard W. Sams and Co., 1978.

Kinley, Harold, The PLL Synthesizer Cookbook. Blue Ridge Summit, PA, Tab Books, 1980.

MOTORCLA SC LOGIC T-50-17 14E D 6367252 0082567 1

# MC145145-1

FIGURE 7 — PHASE DETECTOR OUTPUT WAVEFORMS

NOTE: The PD output state is equal to either VDD or VSS when active. When not active, the output is high impedance and the voltage at that pin is determined by the low pass filter capacitor.

#### **APPLICATIONS**

The features of the MC145145-1 permit bus operation with a dedicated wire needed only for the strobe input. In a microprocessor-controlled system this strobe input is accessed when the phase lock loop is addressed. The remaining data and address inputs will directly interface to the microprocessor's data and address buses.

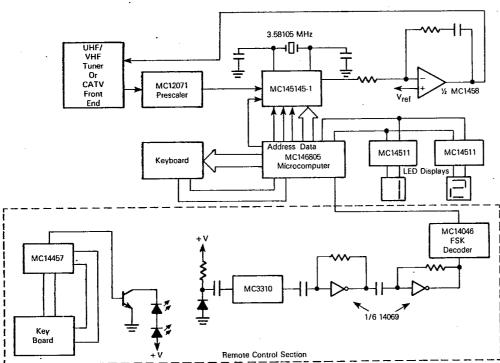

The ÷ R programmability is used to advantage in Figure

8. Here, the nominal ÷ R value is 3667; but by programming

small changes in this value, fine tuning is accomplished. Better tuning resolution is achievable with this method than by changing the + N, due to the use of the large fixed prescaling value of +256 provided by the MC12071.

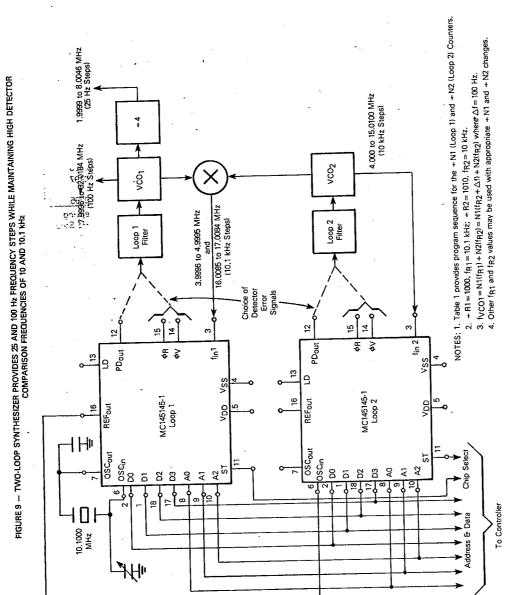

The two loop synthesizer, in Figure 9, takes advantage of these features to control the phase locked loop with a minimum of dedicated lines while preserving optimal loop performance. Both 25 Hz and 100 Hz steps are provided while the relatively large reference frequencies of 10 kHz or 10.1 kHz are maintained.

FIGURE 6 - TV/CATV TUNING SYSTEM

TABLE 1 - PROGRAMMING SEQUENCE FOR TWO-LOOP SYNTHESIZER OF FIGURE 9

| + N1                  | f <sub>in1</sub> (MHz)         | + N2                              | f <sub>VCO2</sub> (MHz)        | fvco1 (MHz)                              |

|-----------------------|--------------------------------|-----------------------------------|--------------------------------|------------------------------------------|

| 396<br>"A" 397<br>495 | 3.9996<br>"B" 4.0097<br>4.9995 | 400<br>399<br>↓<br>301            | 4.0000<br>3.9900<br>3.0100     | 7.9996<br>7.9997<br>8.0095               |

| "A"                   | "В"                            | 401<br>400<br>\$302               | 4.0100<br>4.0000<br>3.0200     | 8.0096<br>8.0097<br>\$.0195              |

| "A"                   | "B"                            | 402<br><sub>C</sub> ., 401<br>303 | 4.0200<br>"D" 4.0100<br>3.0300 | 8.0196<br>8.0197<br>• #<br>8.0295        |

|                       |                                | 1500                              | 15.0000                        | Increasing<br>In 100 Hz Steps<br>19.9995 |

|                       | #B"<br>                        | 1600<br>1599<br>1501              | 16.0000<br>15.9900<br>15.0100  | 19.9996<br>19.9997<br>20.0095            |

| 1585<br>"E" 1586      | 16.0085<br>                    |                                   |                                | 20.0085<br>20.0086<br>20.0184            |

| "E"                   | " <del>F</del> "               | "ç"                               | "ņ"                            | 20.0185<br>20.0186<br>20.0284            |

|                       |                                |                                   |                                | Increasing<br>In 100 Hz Steps<br>32.0084 |

| "E"                   | "F"<br>                        |                                   |                                | 32.0085<br>32.0086<br>32.0184            |

#### CRYSTAL OSCILLATOR CONSIDERATIONS

The following options may be considered to provide a reference frequency to Motorola's CMOS frequency synthesizers. The most desirable is discussed first.

#### USE OF A HYBRID CRYSTAL OSCILLATOR

Commercially available temperature-compensated crystal oscillators (TXCOs) or crystal-controlled data clock oscillators provide very stable reference frequencies. An oscillator capable of sinking and sourcing 50  $\mu A$  at CMOS logic levels may be direct or dc coupled to OSCin. In general, the highest frequency capability is obtained utilizing a direct-coupled square wave having a rail-to-rail (VDD to VSS) voltage swing. If the oscillator does not have CMOS logic levels on the outputs, capacitive or ac coupling to OSCin may be used. OSCout, an unbuffered output, should be left floating.

For additional information about TXCOs and data clock oscillators, please contact: Motorola Inc., Component Products, 2553 N. Edgington St., Franklin Park, IL 60131, phone (312) 451-1000.

#### **DESIGN AN OFF-CHIP REFERENCE**

The user may design an off-chip crystal oscillator using ICs specifically developed for crystal oscillator applications, such as the MC12060, MC12061, MC12560, or MC12561 MECL devices. The reference signal from the MECL device is ac coupled to OSC<sub>in</sub>. For large amplitude signals (standard CMOS logic levels), dc coupling is used. OSC<sub>out</sub>, an unbuffered output, should be left floating. In general, the highest frequency capability is obtained with a direct-coupled square wave having rail-to-rail voltage swing.

#### USE OF THE ON-CHIP OSCILLATOR CIRCUITRY

The on-chip amplifier (a digital inverter) along with an appropriate crystal may be used to provide a reference source frequency. A fundamental mode crystal, parallel resonant at the desired operating frequency, should be connected as shown in Figure A.

For V<sub>DD</sub>=5 V, the crystal should be specified for a loading capacitance, C<sub>L</sub>, which does not exceed 32 pF for frequencies to approximately 8 MHz, 20 pF for frequencies in

the area of 8 to 15 MHz, and 10 pF for higher frequencies. These are guidelines that provide a reasonable compromise between IC capacitance, drive capability, swamping variations in stray and IC input/output capacitance, and realistic C<sub>L</sub> values. The shunt load capacitance, C<sub>L</sub>, presented across the crystal can be estimated to be:

$$C_L = \frac{C_{in}C_{out}}{C_{in}+C_{out}} + C_a + C_O + \frac{C1 \cdot C2}{C1+C2}$$

where C<sub>in</sub> = 5 pF (see Figure C)

C<sub>out</sub> = 6 pF (see Figure C)

C<sub>a</sub> = 5 pF (see Figure C)

CO = The crystal's holder capacitance (see Figure B)

C1 and C2 = External capacitors (see Figure A)

The oscillator can be "trimmed" on-frequency by making a portion or all of C1 variable. The crystal and associated components must be located as close as possible to the OSCin and OSCout pins to minimize distortion, stray capacitance, stray inductance, and startup stabilization time. In some cases, stray capacitance should be added to the values for Cin and Cout.

Power is dissipated in the effective series resistance of the crystal, Re, in Figure B. The drive level specified by the crystal manufacturer is the maximum stress that a crystal can withstand without damage or excessive shift in frequency. R1 in Figure A limits the drive level. The use of R1 may not be necessary in some cases; i.e. R1=0 ohms.

To verify that the maximum dc supply voltage does not overdrive the crystal, monitor the output frequency as a function of voltage at OSC<sub>out</sub>. (Care should be taken to minimize loading.) The frequency should increase very slightly as the dc supply voltage is increased. An overdriven crystal will decrease in frequency or become unstable with an increase in supply voltage. The operating supply voltage must be reduced or R1 must be increased in value if the overdriven condition exists. The user should note that the oscillator start-up time is proportional to the value of R1.

Through the process of supplying crystals for use with CMOS inverters, many crystal manufacturers have developed expertise in CMOS oscillator design with crystals. Discussions with such manufacturers can prove very helpful. See Table A.

TABLE A - PARTIAL LIST OF CRYSTAL MANUFACTURERS

| NAME                        | ADDRESS                               | PHONE          |

|-----------------------------|---------------------------------------|----------------|

| United States Crystal Corp. | 3605 McCart St., Ft. Worth, TX 76110  | (817) 921-3013 |

| Crystek Crystal             | 1000 Crystal Dr., Ft. Myers, FL 33906 | (813) 936-2109 |

| Statek Corp.                | 512 N. Main St., Orange, CA 92668     | (714) 639-7810 |

#### RECOMMENDED FOR READING

Technical Note TN-24, Statek Corp.

Technical Note TN-7, Statek Corp.

E. Hafner, "The Piezoelectric Crystal Unit - Definitions and Method of Measurement", *Proc. IEEE*, Vol. 57, No. 2, Feb., 1969.

D. Kemper, L. Rosine, "Quartz Crystals for Frequency Control", *Electro-Technology*, June, 1969.

P. J. Ottowitz, "A Guide to Crystal Selection", *Electronic Design*, May, 1966.

## FIGURE A - PIERCE CRYSTAL OSCILLATOR CIRCUIT

#### FIGURE B - EQUIVALENT CRYSTAL NETWORKS

Values are supplied by crystal manufacturer (parallel resonant crystal).

# FIGURE C — PARASITIC CAPACITANCES OF THE AMPLIFIER