# LH1692

#### **DESCRIPTION**

The LH1692 is a 300-output TFT-LCD gate driver IC.

### **FEATURES**

- Number of LCD drive outputs : 300

- LCD drive output sequence :

Output shift direction can be selected

OG1→OG300 or OG300→OG1

- Cascade connection :

Max. 4 cascades (internal counting system)

- Usable with both positive/negative power supplies

- Output mode selection

- Normal mode (1-pulse scanning)

- Continuous 2-pulse mode (2-pulse scanning)

- Jumping 2-pulse mode (2-pulse scanning)

- LCD drive voltage: +16.0 to +42.0 V

Operating temperature: -30 to + 85 °C

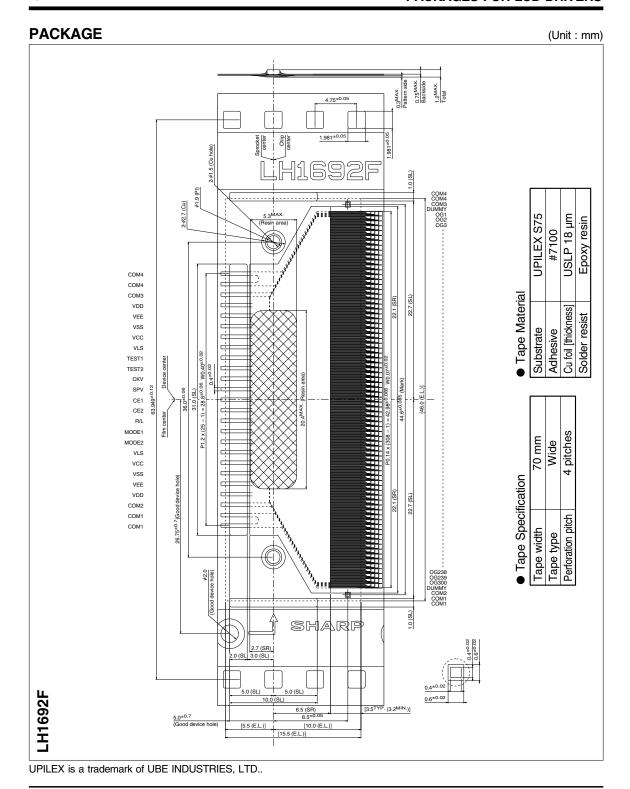

- Package: 319-pin TCP (Tape Carrier Package)

# 300-output TFT-LCD Gate Driver IC

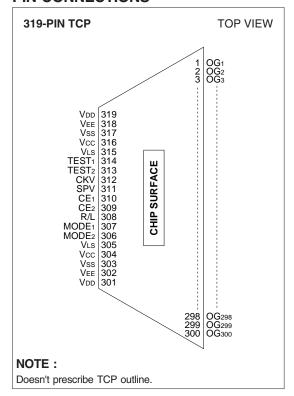

#### PIN CONNECTIONS

# **PIN DESCRIPTION**

| PIN NO.  | SYMBOL       | I/O | DESCRIPTION                                                         |

|----------|--------------|-----|---------------------------------------------------------------------|

| 1 to 300 | OG1-OG300    | 0   | LCD drive output pins                                               |

| 301, 309 | VDD          | -   | Power supply pins for LCD drive                                     |

| 302, 318 | VEE          | -   | Power supply pins for LCD drive                                     |

| 303, 317 | Vss          | -   | Power supply pins for logic system                                  |

| 304, 316 | Vcc          | -   | Power supply pins for logic system                                  |

| 305, 315 | VLS          | -   | Power supply pins for input level shifter                           |

| 306, 307 | MODE2, MODE1 | I   | Output mode selection pins                                          |

| 308      | B/L          | ı   | Pin for selecting bi-directional shift register and setting cascade |

| 306      | n/L          | I   | sequence                                                            |

| 309, 310 | CE2, CE1     | I   | Cascade sequence setting pins                                       |

| 311      | SPV          | I   | Vertical scanning start pulse input pin                             |

| 312      | CKV          | I   | Vertical shift clock input pin                                      |

| 313, 314 | TEST2, TEST1 | I   | IC test pins                                                        |

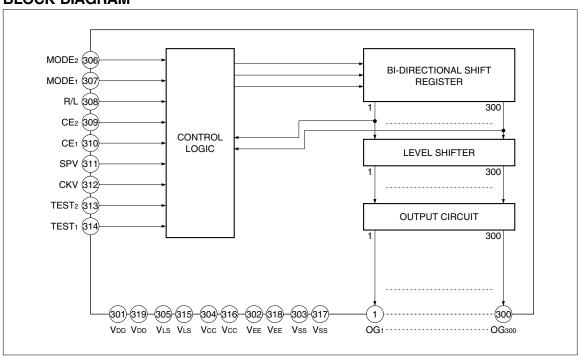

# **BLOCK DIAGRAM**

# **FUNCTIONAL OPERATIONS OF EACH BLOCK**

| BLOCK                | FUNCTION                                                                                   |  |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| Control Logic        | sed to create signals necessary for mode selecting signal, cascade sequence setting        |  |  |  |  |  |

| Control Logic        | signal and for operation of bi-directional shift register.                                 |  |  |  |  |  |

| Bi-directional Shift | Used as transfer circuit of LCD drive output start signal. It is possible to set LCD drive |  |  |  |  |  |

| Register             | output sequence of OG1→OG300 direction or OG300→OG1 direction.                             |  |  |  |  |  |

| Level Shifter        | Used as circuit which shifts LCD drive output signals transferred by bi-directional shift  |  |  |  |  |  |

| Level Shiller        | register to VDD-VEE level.                                                                 |  |  |  |  |  |

| Output Circuit       | Configured with output buffers to output VDD-VEE level.                                    |  |  |  |  |  |

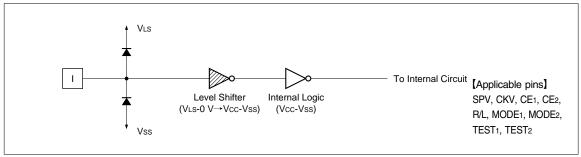

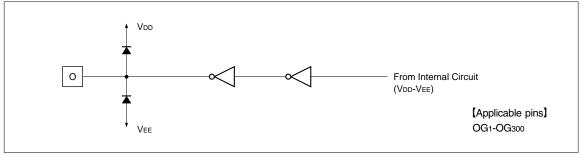

# INPUT/OUTPUT CIRCUITS

Fig. 1 Input Circuit

Fig. 2 Output Circuit

# **FUNCTIONAL DESCRIPTION**

# **Pin Functions**

| SYMBOL            |                                   |                                                                                                                                          |            |           | FUNCTIO            | ON              |                             |  |  |  |

|-------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|--------------------|-----------------|-----------------------------|--|--|--|

| VDD               | Used as po                        | wer su                                                                                                                                   | pply pin   | for high  | level LCD driv     | re.             |                             |  |  |  |

| VLS               | Used as po                        | wer su                                                                                                                                   | pply pin   | for inpu  | it level shifters. |                 |                             |  |  |  |

| Vcc               | Used as po                        | wer su                                                                                                                                   | pply pin   | for logic | c system, norm     | ally connecte   | d to Vss + 5.0 V.           |  |  |  |

| VEE               | Used as po                        | d as power supply pin for low level LCD drive.                                                                                           |            |           |                    |                 |                             |  |  |  |

| Vss               | Used as lo                        | d as logic system power supply pin.                                                                                                      |            |           |                    |                 |                             |  |  |  |

| CKV               | Used as ve                        | d as vertical shift clock pulse input pin.                                                                                               |            |           |                    |                 |                             |  |  |  |

| SPV               | Used as ve                        | Ised as vertical scanning start pulse input pin. (At least, input one cycle of CKV during "L"                                            |            |           |                    |                 |                             |  |  |  |

| 3FV               | period of S                       | eriod of SPV.)                                                                                                                           |            |           |                    |                 |                             |  |  |  |

|                   | Used as in                        | out pins                                                                                                                                 | for sele   | ecting o  | utput mode.        |                 |                             |  |  |  |

|                   | Output mod                        | de is se                                                                                                                                 | t as sho   | wn in th  | ne table below I   | by setting MC   | DE1 pin and MODE2 pin.      |  |  |  |

|                   | MODE                              | E1 M                                                                                                                                     | IODE2      |           | Output mod         | de              |                             |  |  |  |

| MODE1             | Н                                 |                                                                                                                                          | Н          | Norma     | l mode (1-pulse    | scanning)       |                             |  |  |  |

| MODE2             | L                                 |                                                                                                                                          | Н          | Continu   | uous 2-pulse m     | ode             |                             |  |  |  |

|                   | Н                                 |                                                                                                                                          | L          | Jumpin    | ig 2-pulse mode    | е               |                             |  |  |  |

|                   | L L Set all outputs to VEE level. |                                                                                                                                          |            |           |                    |                 |                             |  |  |  |

|                   | Used as in                        | out pin                                                                                                                                  | for selec  | tina the  | shift direction    | of bi-direction | al shift register and for   |  |  |  |

|                   | 1                                 | Used as input pin for selecting the shift direction of bi-directional shift register and for setting the sequence of cascade connection. |            |           |                    |                 |                             |  |  |  |

| R/L               |                                   |                                                                                                                                          |            |           |                    | set to "H". L   | CD drive outputs shift from |  |  |  |

|                   |                                   | •                                                                                                                                        |            |           |                    |                 | quence is set as shown in   |  |  |  |

|                   | the table be                      |                                                                                                                                          |            |           |                    |                 | '                           |  |  |  |

|                   | Used as in                        | out pins                                                                                                                                 | for sett   | ing of c  | hip cascade se     | quence. (Max    | x. 4 cascades)              |  |  |  |

|                   | 05.                               | 05-                                                                                                                                      | Ca         | ascade    | sequence           | ]               |                             |  |  |  |

|                   | CE <sub>1</sub>                   | CE2                                                                                                                                      | R/L =      | = "H"     | R/L = "L"          | 1               |                             |  |  |  |

| CE <sub>1</sub>   | Н                                 | Н                                                                                                                                        | 1:         | st        | 4th                | 1               |                             |  |  |  |

| CE2               | L                                 | Н                                                                                                                                        | 2r         | nd        | 3rd                |                 |                             |  |  |  |

|                   | Н                                 | L                                                                                                                                        | 3r         | ď         | 2nd                |                 |                             |  |  |  |

|                   | L                                 | L                                                                                                                                        | 4t         | h         | 1st                |                 |                             |  |  |  |

|                   | With above                        | setting                                                                                                                                  | , sets th  | e casca   | ide sequence s     | ignal inside th | ne IC.                      |  |  |  |

| TEST <sub>1</sub> | Used as in                        | out pins                                                                                                                                 | for IC t   | esting.   |                    |                 |                             |  |  |  |

| TEST2             | Must be se                        |                                                                                                                                          |            |           |                    |                 |                             |  |  |  |

|                   | Used as ou                        | ıtput pir                                                                                                                                | ns for LC  | D drive   | output, and wh     | hich output da  | ata at 2 levels.            |  |  |  |

| OG1-OG300         | Selecting                         |                                                                                                                                          | •          |           |                    |                 |                             |  |  |  |

|                   | Non-sele                          | cting da                                                                                                                                 | ata is out | put at \  | /EE level .        |                 |                             |  |  |  |

# **Functional Operations**

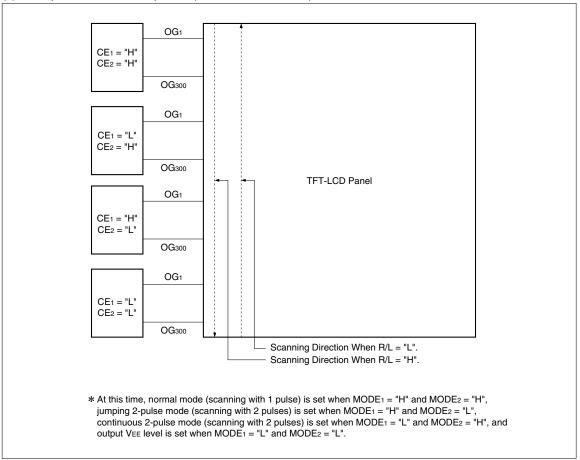

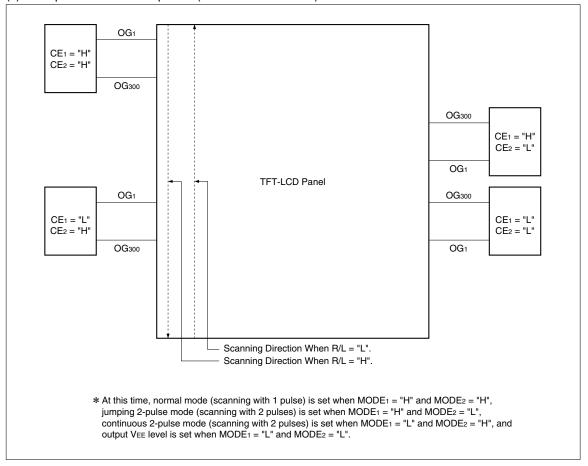

(1) Example of Cascade Sequence (One Side Assembled)

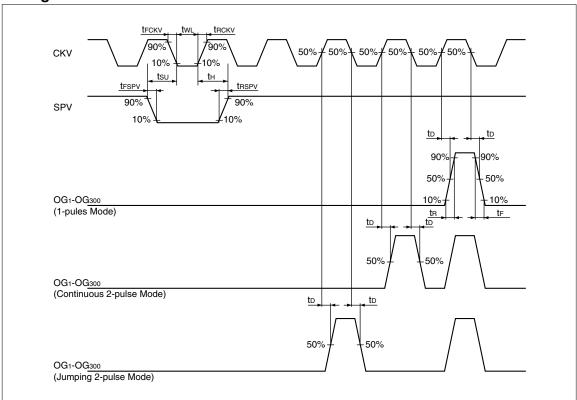

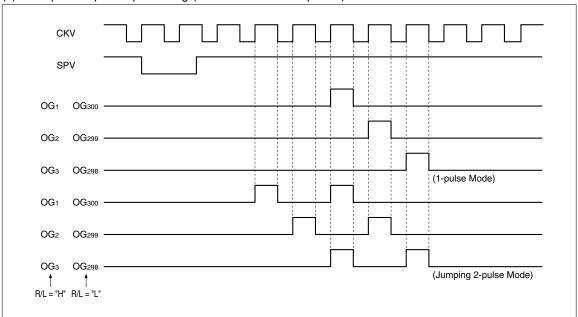

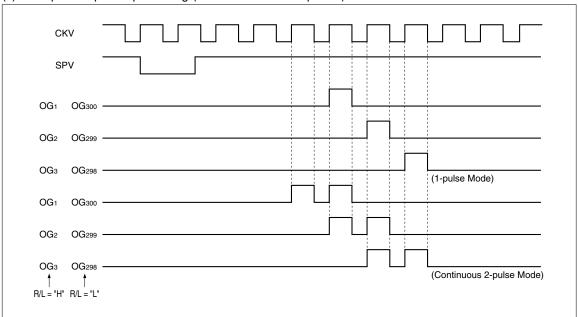

(2) Example of Input/Output Timing (For 1st Cascade Sequence)

## (3) Example of Cascade Sequence (Both Side Assembled)

(4) Example of Input/Output Timing (For 1st Cascade Sequence)

#### **PRECAUTIONS**

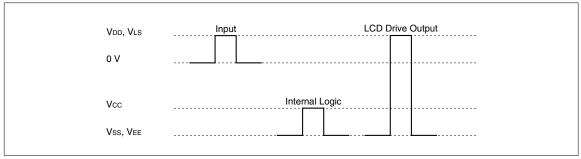

# Precautions when connecting or disconnecting the power supply

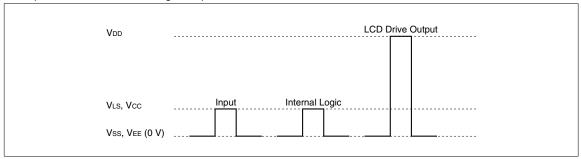

This IC has a high-voltage LCD driver, so it may be permanently damaged by a high current which may flow if voltage is supplied to the LCD drive power supply while the logic system power supply is floating. Therefore, when connecting the power supply, observe the following sequence.

Logic system power supply (VLs) or internal logic system power supply (Vss, Vcc; Vcc > Vss) → logic input → LCD drive power supply (VEE, VDD)

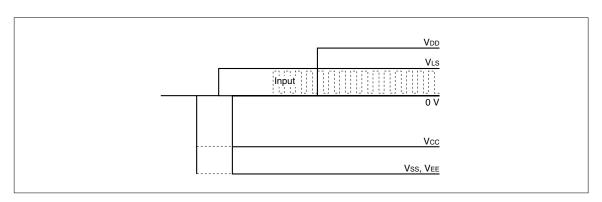

It is possible to set voltage VEE to the same as Vss. When connecting the power supply when VEE = Vss, observe the following sequence and the recommended sequence figure shown below.

Logic system power supply (VLS), internal logic system power supply (VSS, VCC; VCC > VSS) and low-level LCD drive power supply (VEE) → logic input → high-level LCD drive power supply (VDD)

When disconnecting the power supply, follow the reverse sequence.

Since the logic state of the internal circuit is unstable immediately after the logic system power is supplied, input CKV and SPV while initializing the internal circuit (minimum input clock number is 300 CKV).

MODE1 and MODE2 should be set to "L" during the initializing period for setting the LCD drive output to VEE level.

#### Input pin setting

Input pins other than CKV and SPV must be set to "H" or "L" level.

#### **Maximum ratings**

When connecting or disconnecting the power, this IC must be used within the range of the absolute maximum ratings.

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER           | SYMBOL    | APPLICABLE PINS            | RATING            | UNIT | NOTE  |

|---------------------|-----------|----------------------------|-------------------|------|-------|

|                     | VDD       | VDD                        | -0.3 to +45.0     | V    |       |

|                     | VLS       | VLS                        | -0.3 to +7.0      | V    |       |

| Supply voltage      | Vcc – Vss | Vcc, Vss                   | -0.3 to +7.0      | V    |       |

| Supply voltage      | VEE - VSS | VEE, VSS                   | -0.3 to +45.0     | V    | ] , , |

|                     | Vdd – Vee | VDD, VEE, VSS              | -0.3 to +45.0     | V    | 1, 2  |

|                     | (Vss)     | VDD, VEE, VSS              | -0.3 to +45.0     |      |       |

| lenut voltage       | Vin       | CKV, SPV, CE1, CE2, R/L,   | -0.3 to VLS + 0.3 | V    |       |

| Input voltage       | VIN       | MODE1, MODE2, TEST1, TEST2 | -0.3 to VLS + 0.3 | \ \  |       |

| Storage temperature | Tstg      |                            | -45 to +125       | °C   |       |

## NOTES:

- 1.  $TA = +25 \,^{\circ}C$

- 2. The maximum applicable voltage on any pin with respect to 0 V.

# RECOMMENDED OPERATING CONDITIONS

| PARAMETER             | SYMBOL    | MIN.  | TYP.  | MAX.  | UNIT | NOTE |

|-----------------------|-----------|-------|-------|-------|------|------|

|                       | VDD       | +5.5  | +9.0  | +42.0 | >    |      |

|                       | VLS       | +3.0  | +5.0  | +5.5  | >    |      |

| Supply voltage        | Vcc - Vss | +3.0  | +5.0  | +5.5  | ٧    |      |

| Supply voltage        | VEE - VSS | 0     |       | +11.0 | ٧    | 1, 2 |

|                       | VDD - VEE | +16.0 | +25.0 | +42.0 | ٧    |      |

|                       | (Vss)     |       |       |       |      |      |

| Input voltage         | VIN       | 0     |       | VLS   | V    |      |

| Operating temperature | Topr      | -30   |       | +85   | Ç    |      |

#### NOTES:

- 1. The applicable voltage on any pin with respect to 0 V.

- 2. Ensure that voltages are set as follows.

Vss, Vee  $\leq$  0 V

Vcc - Vss = VLs±0.1 V (For 3.3 V specifications)

Vcc - Vss = VLs±0.2 V (For 5.0 V specifications)

$Vcc \le Vls$

When power supply pins are set as shown below, the LH1692 can output positive voltage and negative voltage to LCD drive output.

Example 1 : For Positive Voltage Output

Example 2 : For Negative Voltage Output

# **ELECTRICAL CHARACTERISTICS**

## **DC Characteristics**

(VLS =  $+3.3\pm0.3$  V (= VCC - VSS), VEE = VSS, TOPR = -30 to +85 °C)

| PARAMETER             | SYMBOL | CONDITIONS     | APPLICABLE PINS      | MIN.      | TYP. | MAX.      | UNIT | NOTE |

|-----------------------|--------|----------------|----------------------|-----------|------|-----------|------|------|

| Input "Low" voltage   | VIL    |                | CKV, SPV, MODE1,     |           |      | 0.2VLS    | V    |      |

| Input "High" voltage  | VIH    |                | MODE2, CE1, CE2, R/L | 0.8VLS    |      |           | V    |      |

| Output "Low" voltage  | Vol    | IOL = 0.4  mA  | OG1-OG300            |           |      | VEE + 0.4 | V    |      |

| Output "High" voltage | Vон    | IOH = -0.4  mA | OG1-OG300            | VDD - 0.4 |      |           | V    |      |

| Input "Low" current   | lı∟    | $V_I = 0 V$    | CKV, SPV, MODE1,     |           |      | 5.0       | μΑ   |      |

| Input "High" current  | lін    | $V_I = V_{LS}$ | MODE2, CE1, CE2, R/L |           |      | 5.0       | μΑ   | 1    |

| Supply current (1)    | IDD    |                |                      |           |      | 60        | μΑ   |      |

|                       | ILS    | For            |                      |           |      | 130       | μΑ   | 2    |

|                       | Icc    | 1-pulse mode   |                      |           |      | 80        | μΑ   |      |

|                       | IEE    |                |                      |           |      | 50        | μΑ   |      |

|                       | IDD    |                |                      |           |      | 130       | μΑ   |      |

| Supply ourrent (2)    | ILS    | For jumping    |                      |           |      | 200       | μΑ   | 3    |

| Supply current (2)    | Icc    | 2-pulse mode   |                      |           |      | 90        | μΑ   | 3    |

|                       | IEE    |                |                      |           |      | 50        | μΑ   |      |

| Cumple of many (2)    | IDD    |                |                      |           |      | 130       | μΑ   |      |

|                       | ILS    | For continuous |                      |           |      | 200       | μΑ   | 4    |

| Supply current (3)    | Icc    | 2-pulse mode   |                      |           |      | 90        | μΑ   | 4    |

|                       | IEE    |                |                      |           |      | 90        | μΑ   |      |

#### NOTES:

- 1. All input pins: 3.3 V

- 2. CKV : Frequency = 31 kHz, "L" period width  $twL = 16.2 \mu s$

SPV: Frequency = 60 Hz Other input pins: 3.3 V All output pins are opened.

3. CKV : Frequency = 31 kHz, "L" period width twL = 16.2  $\mu$ s

SPV : Frequency = 60 Hz

MODE2: 0 V

Other input pins: 3.3 V All output pins are opened. 4. CKV : Frequency = 31 kHz, "L" period width  $twL = 16.2 \mu s$

SPV : Frequency = 60 Hz

MODE1:0 V

Other input pins: 3.3 V All output pins are opened. (VLS =  $+5.0\pm0.5$  V (= VCC - VSS), VEE = VSS, TOPR = -30 to +85 °C)

| PARAMETER             | SYMBOL | CONDITIONS     | APPLICABLE PINS      | MIN.      | TYP. | MAX.      | UNIT | NOTE |

|-----------------------|--------|----------------|----------------------|-----------|------|-----------|------|------|

| Input "Low" voltage   | VIL    |                | CKV, SPV, MODE1,     |           |      | 0.2VLS    | V    |      |

| Input "High" voltage  | ViH    |                | MODE2, CE1, CE2, R/L | 0.8VLS    |      |           | V    |      |

| Output "Low" voltage  | Vol    | IOL = 0.4  mA  | OG1-OG300            |           |      | VEE + 0.4 | V    |      |

| Output "High" voltage | Vон    | IOH = -0.4  mA | OG1-OG300            | VDD - 0.4 |      |           | V    |      |

| Input "Low" current   | lı∟    | $V_I = 0 V$    | CKV, SPV, MODE1,     |           |      | 5.0       | μΑ   |      |

| Input "High" current  | lін    | $V_I = V_{LS}$ | MODE2, CE1, CE2, R/L |           |      | 5.0       | μΑ   | 1    |

|                       | IDD    |                |                      |           |      | 60        | μΑ   |      |

| Supply current (1)    | ILS    | For            |                      |           |      | 180       | μΑ   | 2    |

|                       | Icc    | 1-pulse mode   |                      |           |      | 100       | μΑ   |      |

|                       | IEE    |                |                      |           |      | 50        | μΑ   |      |

|                       | IDD    |                |                      |           |      | 130       | μΑ   |      |

| Supply current (2)    | ILS    | For jumping    |                      |           |      | 300       | μΑ   | 3    |

| Supply current (2)    | Icc    | 2-pulse mode   |                      |           |      | 150       | μΑ   | 3    |

|                       | IEE    |                |                      |           |      | 50        | μΑ   |      |

| Cumply ourset (2)     | IDD    |                |                      |           |      | 130       | μΑ   |      |

|                       | ILS    | For continuous |                      |           |      | 300       | μΑ   | 4    |

| Supply current (3)    | Icc    | 2-pulse mode   |                      |           |      | 150       | μΑ   | 4    |

|                       | IEE    |                |                      |           |      | 50        | μΑ   |      |

#### NOTES:

- 1. All input pins: 5 V

- 2. CKV : Frequency = 31 kHz, "L" period width  $twL = 16.2 \mu s$

SPV : Frequency = 60 Hz Other input pins : 5 V All output pins are opened.

3. CKV : Frequency = 31 kHz, "L" period width twL = 16.2  $\mu s$

SPV : Frequency = 60 Hz

MODE2: 0 V

Other input pins: 5 V

All output pins are opened.

4. CKV : Frequency = 31 kHz, "L" period width twL = 16.2  $\mu$ s

SPV : Frequency = 60 Hz

MODE1: 0 V

Other input pins: 5 V

All output pins are opened.

# **AC Characteristics** (VLS = $+3.3\pm0.3$ V (= VCC - VSS), VEE = VSS, TOPR = -30 to +85 °C)

|                       |        | •           |                 |          |      |      |      |

|-----------------------|--------|-------------|-----------------|----------|------|------|------|

| PARAMETER             | SYMBOL | CONDITIONS  | APPLICABLE PINS | MIN.     | TYP. | MAX. | UNIT |

| Clock frequency       | fckv   |             |                 |          |      | 100  | kHz  |

| "L" clock pulse width | twL    |             | CKV             | 0.5      |      |      | μs   |

| Clock rise time       | trckv  |             | CKV             |          |      | 100  | ns   |

| Clock fall time       | tFCKV  | -           |                 |          |      | 100  | ns   |

| Data setup time       | tsu    |             | CKV, SPV        | 100      |      |      | ns   |

| Data hold time        | tH     |             | CRV, 5PV        | 300      |      |      | ns   |

| Pulse rise time       | trspv  |             | SPV             |          |      | 100  | ns   |

| Pulse fall time       | trspv  |             | 327             |          |      | 100  | ns   |

| Output transfer delay | to.    |             |                 |          |      | 3.0  |      |

| time                  | tD     | C: 500 pE   | OG1-OG300       |          |      | 3.0  | μs   |

| Output rise time      | tR     | CL = 500 pF | OG1-OG300       |          |      | 1.0  | μs   |

| Output fall time      | tF     |             |                 | <u> </u> |      | 1.0  | μs   |

# (VLS = $+5.0\pm0.5$ V (= VCC - VSS), VEE = VSS, TOPR = -30 to +85 °C)

|                       |        | `           | , , , , , , , , , , , , , , , , , , , , |      |      |      |      |

|-----------------------|--------|-------------|-----------------------------------------|------|------|------|------|

| PARAMETER             | SYMBOL | CONDITIONS  | APPLICABLE PINS                         | MIN. | TYP. | MAX. | UNIT |

| Clock frequency       | fckv   |             |                                         |      |      | 100  | kHz  |

| "L" clock pulse width | twL    |             | CKV                                     | 0.5  |      |      | μs   |

| Clock rise time       | trckv  |             | CKV                                     |      |      | 100  | ns   |

| Clock fall time       | tFCKV  |             |                                         |      |      | 100  | ns   |

| Data setup time       | tsu    |             | CKV CDV                                 | 100  |      |      | ns   |

| Data hold time        | tн     |             | CKV, SPV                                | 300  |      |      | ns   |

| Pulse rise time       | trspv  |             | SPV                                     |      |      | 100  | ns   |

| Pulse fall time       | trspv  |             | 5PV                                     |      |      | 100  | ns   |

| Output transfer delay | to.    |             |                                         |      |      | 2.0  |      |

| time                  | tD     | C: F00 =F   | OG1-OG300                               |      |      | 2.0  | μs   |

| Output rise time      | tR     | CL = 500 pF | OG1-OG300                               |      |      | 1.0  | μs   |

| Output fall time      | tF     |             |                                         |      |      | 1.0  | μs   |

# **Timing Chart**