# **MOTOROLA SEMICONDUCTOR TECHNICAL DATA**

# BINARY TO PHONE PULSE CONVERTER SUBSYSTEM

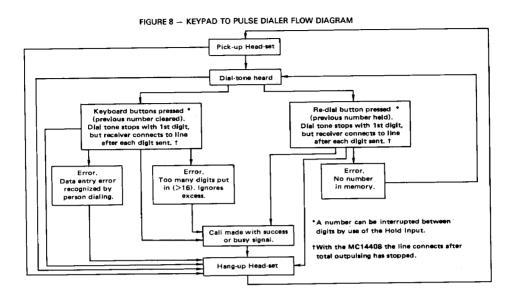

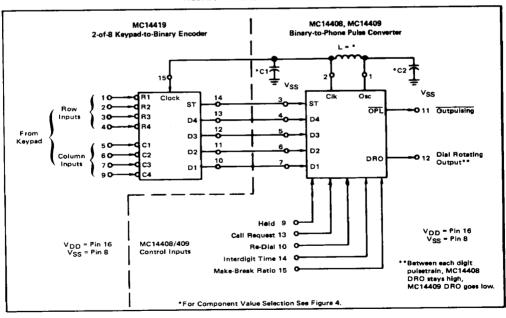

The MC14408 and the MC14409 are devices designed to convert a four bit binary input code to a number of serial output pulses corresponding to the value of the input code.

The devices can be used in telephone pulse dialing applications when combined with their companion device, the MC14419 (2-of-8 keypad-to-binary code converter). The devices have been partitioned to allow convenient addition of RAM memory and controls for repertoire dialing applications.

The MC14408 and MC14409 perform identical functions with the exception of the signal output at the DRO (Dial Rotating Output). In the MC14408, DRO remains high during continuous outpulsing of all digits and in the MC14409 DRO is low between each digit pulse burst.

- On-Chip Oscillator

- Diode Protection on All Inputs

- Dialing of Numbers Up to 16 Digits Long

- Memory Storage (FIFO) and Re-Dialing (single pin) of Last Telephone Number

- Hold Interrupt Control for Additional Interdigit Delays Isual a Wait for Intermediate Dial Tones)

- Selectable Dialing Rate (10 pps or 20 pps)

- Selectable Dialing Nate (10 pps of 20 pps)

Selectable Interdigit Time (300 or 800 ms & 10 pps 150 or 400 ms @ 20 pps)

- Selectable Make Break Ratio (61% or 67%)

- Buffered Outputs Compatible with Discrete Transistor Driver Interface, One Low-power Schottky TTL Load or Two Lowpower TTL Loads Over the Rated Temperature Range.

- Low Power Dissipation IDD (operating with oscillator) = 470 µA typ @ VDD = 5.0 Vdc, fOsc = 16 kHz, CL = 50 pF

# MC14408 MC14409

## **CMOS LSI**

(LOW-POWER COMPLEMENTARY MOS)

RINARY TO PHONE PULSE CONVERTER SUBSYSTEM

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \leq (V_{in})$  or  $V_{out}$ )  $\leq V_{DD}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either VSS or VDD).

$\textbf{MAXIMUM RATINGS} \ \, (\text{Voltages referenced to V}_{SS}, \text{Pin 8.})$

| Symbol           | Value                               | Unit               |  |  |  |  |

|------------------|-------------------------------------|--------------------|--|--|--|--|

| V <sub>DD</sub>  | -0.5 to +6.0                        | Vdc                |  |  |  |  |

| V <sub>in</sub>  | -0.5<br>to<br>V <sub>DD</sub> + 0.5 | Vdc                |  |  |  |  |

|                  | 10                                  | mAdc               |  |  |  |  |

| TA               | -40 to +85                          | °C                 |  |  |  |  |

| T <sub>stg</sub> | -65 to +150                         | σС                 |  |  |  |  |

|                  | V <sub>DD</sub> V <sub>in</sub>     | Symbol Value   VDD |  |  |  |  |

## **ELECTRICAL CHARACTERISTICS**

|                                                                   |                                    | V <sub>DD</sub><br>Vdc | -40°C                                            |              | 25°C          |               |             | +85°C         |             | T          |

|-------------------------------------------------------------------|------------------------------------|------------------------|--------------------------------------------------|--------------|---------------|---------------|-------------|---------------|-------------|------------|

| Characteristic                                                    | Symbol                             |                        | Min<br>3.0                                       | Max<br>6.0   | Min<br>3,0    | Тур<br>5.0    | Max         | Min           | Max<br>6.0  | Unit       |

| Supply Voltage                                                    | V <sub>DD</sub>                    | -                      |                                                  |              |               |               | 6.0         | 3,0           |             | Vdc        |

| Output Voltage "0" Level "1" Level                                | Vont                               | 5.0<br>5.0             | 4.95                                             | 0.05         | 4.95          | 0<br>5.0      | 0.05        | 4.95          | 0.05        | Vdc        |

| Noise Immunity                                                    |                                    |                        | <del>                                     </del> |              | 1.00          |               |             | 7.50          |             | VOL        |

| (△V <sub>out</sub> ≤ 0.5 Vdc)<br>(△V <sub>out</sub> ≤ 0.5 Vdc)    | V <sub>NL</sub><br>V <sub>NH</sub> | 5.0<br>5.0             | 1.5<br>1.4                                       | -            | 1.5<br>1.5    | 2,25<br>2,25  | _           | 1.4<br>1.5    | _           | Vdc<br>Vdc |

| Output Drive Current                                              | IOH                                | -                      | <del>                                     </del> | <del> </del> | <del> </del>  |               | <del></del> | <del></del> - | <u> </u>    | mAd        |

| (V <sub>OH</sub> = 2.5 Vdc) Source<br>(V <sub>OH</sub> = 4.6 Vdc) |                                    | 5.0<br>5.0             | -1.0<br>-0.20                                    | _            | -0,80         | -1.7          | -           | -0.60         | _           | l "IIAG    |

| (V <sub>OL</sub> = 0.4 Vdc) Sink                                  | loL                                | 5.0                    | 0.52                                             | _            | -0.16<br>0.44 | -0.36<br>0.88 | _           | -0.12<br>0.36 | _           | mAd        |

| Input Current                                                     | lin                                | 6.0                    |                                                  | 0.3          |               | ±0.00001:4    | ±0.30       |               | 1,0         | μAd        |

| Input Capacitance<br>(V <sub>in</sub> = 0)                        | C <sub>in</sub>                    | -                      |                                                  | 12           | =             | 5.0           | 12          |               | 12          | ρF         |

| Operating Supply Current                                          | I <sub>DD</sub><br>(operating      | 3 5                    |                                                  | 250          | -             | 160           | 200         | -             | 200         | μAdo       |

| er comme                                                          | with<br>Osc)                       | 6                      | -                                                | 700<br>1250  | -             | 470<br>740    | 550<br>1000 | -             | 550<br>1000 |            |

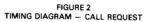

FIGURE 1

TIMING DIAGRAM — DATA AND STROBE INPUTS

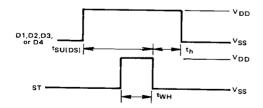

If power is turned off after each call, CRQ must stay high after power is applied (for a duration of  $tp_{\mathbb{C}}$ ) to ensure no spurious outpulsing. For this use the redial function is invalid.

SWITCHING CHARACTERISTICS (CL = 50 pF, TA = 25°C)

| Characteristic                                       | Symbol           | VDD    | Min                  | Тур      | Max | Unit |

|------------------------------------------------------|------------------|--------|----------------------|----------|-----|------|

| Dutput Rise Time**                                   | <sup>t</sup> TLH | 5.0    | -                    | 180      | 400 | ns   |

| tTLH = (3.0 ns/pF) CL + 30 ns                        |                  |        |                      |          |     |      |

| Output Fall Time**                                   | tTHL.            | 5.0    | _                    | 100      | 200 | ns   |

| tTHL = (1.5 ns/pF) C <sub>L</sub> + 25 ns            |                  |        |                      | L        |     |      |

| Power Up to Call Request Pause                       | tPC              | 3 to 6 | 48/f <sub>cl</sub> * |          |     | ms   |

| Call Request to First Strobe Pulse                   | tcs              | 3 to 6 | 48/f <sub>cl</sub> * |          |     | ms   |

| Strobe to Strobe Separation Time                     | tss              | 3 to 6 | 48/f <sub>cl</sub> * |          |     | ms   |

| Strobe Pulse Width                                   | twH              | 3 to 6 | 1.0                  |          |     | μς   |

| Strobe to Data Hold Time                             | th               | 3 to 5 |                      | 150      | 400 | ns   |

| Clock Frequency***                                   | fcl              | 3 to 6 | 12.5                 | 16       | 100 | kHz  |

| Percent Break to Make Ratio                          | %MB              | 3 to 6 |                      | 1 ]      |     | %    |

| (MBR = 0)                                            | i l              |        | -                    | 61       | _   |      |

| (MBR = 1)                                            |                  |        | _                    | 67       |     |      |

| Outpulsing Rate (fOPL = *fci/1.6)                    | fOPL             | 3 to 6 |                      |          |     | pps  |

| f <sub>Cl</sub> = 16 kHz                             | Į l              |        | _                    | 10<br>20 | _   | 1    |

| f <sub>cl</sub> = 32 kHz                             |                  |        |                      | 20       |     |      |

| Interdigit Time                                      | t1D              | 3 to 6 |                      | 1        |     | ms   |

| $t_{ID} = (5 \times IDT + 3)/f_{OPL}$                |                  |        |                      |          |     |      |

| IDT = 0                                              |                  |        | _                    | 300      | _   | ì    |

| fOPL = 10 pps                                        |                  |        | _                    | 150      | _   |      |

| fOPL = 20 pps                                        |                  |        | ĺ                    | 1        |     |      |

| IDT = 1                                              |                  |        | _                    | 800      | _   |      |

| f <sub>OPL</sub> = 10 pps                            | ŧ.               | ,      | Ì _                  | 400      | _   | ł    |

| fOPL = 20 pps                                        |                  | 3 to 6 | <del></del>          |          |     | ms   |

| Strobe to Output Time                                | tsoı             | 3.00   | 1                    | 1        |     | l    |

| Initial Outpulsing Stream                            |                  |        |                      |          | 1   | l    |

| IDT = 0                                              |                  | \<br>\ | 300                  | 1 -      | 400 | 1    |

| fOPL = 10 pps<br>fOPL = 20 pps                       |                  |        | 150                  | -        | 200 |      |

| IDT = 1                                              |                  |        |                      | 1        |     | 1    |

| fOpt = 10 pps                                        |                  |        | 800                  | _        | 900 |      |

| fOPL = 20 pps                                        |                  |        | 400                  | -        | 450 | 1    |

| Continued Outpulsing Stream                          | tsoc             | 3 to 6 | Ļ                    |          |     | ms   |

| IDT = 0 or 1                                         | 300              |        |                      | 1        | ļ   | 1    |

| fOPL = 10 pps                                        |                  |        | 100                  | -        | 200 |      |

| fOPL = 20 pps                                        | Ì                |        | 50                   |          | 100 |      |

| Hold to Outpulse Time                                | tHOL             | 3 to 6 |                      |          | 1   | ms   |

| IDT = 0 or 1                                         | ""               | ļ      | İ                    | 1        |     |      |

| fopt = 10 pps                                        |                  |        | 100                  | _        | 200 |      |

| fOPL = 20 pps                                        |                  | ŀ      | 50                   | <u> </u> | 100 | 1    |

| Dial Rotating Overlap Time .                         | *DRO             | 3 to 6 |                      |          | 1   | ms   |

| fopL = 10 pps                                        |                  |        | -                    | 100      | -   |      |

| fOPL = 20 pps                                        |                  | l      | <u> </u>             | 50       |     | 1    |

| Data to Strobe Setup Time (f <sub>cl</sub> = 16 kHz) | tsu(DS)          | 3 to 6 | 1.5                  | -        |     | μs   |

| Re-dial Pulse Width (fcl = 16 kHz)                   |                  | 3 to 6 | 1                    | 200      | _   | ns   |

<sup>\*</sup>f<sub>cl</sub> in kHz

<sup>\*\*</sup>The formula given is for the typical characteristics only.

<sup>\*\*\*</sup> Minimum clack pulse width = 1.0 \(mus.

## Notes:

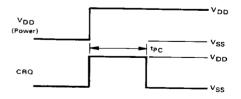

- (\*)1st, 2nd, 3rd, etc., denotes Strobe pulse sequence i.e., which digit in the phone number is being dialed. The number in parentheses denotes the numerical value of the digit being dialed. The examples define the various voltage — level and timing requirements, not a complete phone number.

- (\*\*) For the MC14408 the DRO signal will remain high provided digits remain in the memory, or a digit for continuing outpulsing is strobed in before the anticipated falling edge of the most significant digit in the memory. (i.e., [200 % MB] ms after the most significant outpulsing edge). The time from Strobe to DRO can be 0 to 100 ms.

- (\*\*\*)For the HOL signal to hold a next digit (e.g. the 4th, etc.,) the HOL falling edge must not appear after  $\{t_{|D}$ -%MB + 100 $\}$  ms the last outpulsing edge of the previous digit.

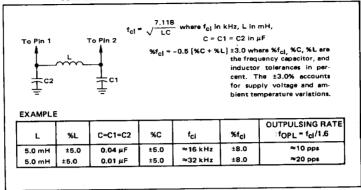

FIGURE 4

COMPONENT SELECTION FOR OSCILLATOR/CLOCK FREQUENCY

FIGURE 5 TRUTH TABLE

|          | INPUTS |          |           |    |    |     |     |     | OUTPUTS |                                                                                  |        |                                              |

|----------|--------|----------|-----------|----|----|-----|-----|-----|---------|----------------------------------------------------------------------------------|--------|----------------------------------------------|

| CRO      | D4     | D3       | D2        | Dı | ST | RED | HOL | IDT | MBR     | OPL                                                                              |        | DRO †                                        |

| 1        | ×      | ×        | ж         | ×  | ×  | - x | ×   | ×   | х       | 0                                                                                |        | 0                                            |

| <u> </u> | ×      | <u>×</u> |           |    | 0  |     | 1   | x   | ×       | 1 (Steady State)                                                                 |        | 0 (Steady State)                             |

| 0        |        |          | X<br>Digi |    | 九  | ,   | 1   | х   | ×       | Number of pulses (Lr) of nth<br>digit = binary combination of<br>D4, D3, D2, D1. | 0      | During outpulsing<br>Otherwise               |

| 0        | ×      | ×        | x         | ×  | •  | ݖ   | 1   | х   | ×       | Digits of number in memory re-sent.                                              | 1 0    | During outpulsing<br>Otherwise               |

| 0        | ×      | ×        | ×         | ×  | ×  | 1   | 0   | х   | ×       | 1 After conclusion of digit being outpulsed.                                     | 0      | After conclusion of digit<br>being outpulsed |

| ×        | ×      | ×        | ×         | ×  | ×  | х   | ×   | 0   | ×       | 300 ms Interdigit time<br>800 ms Interdigit time<br>fcl = 1                      | 16 kHz |                                              |

| ×        | ×      | х        | ×         | ×  | ×  | ×   | х   | ×   | 0       | 61% (≈1.6:1) Make-Break Ratio<br>67% (≈2:1) Make-Break Ratio                     |        | _                                            |

- X = Don't Care

- With the exception of 0000 which will give 10 pulses.

- † Refer to timing diagram Figure 3.

## DEVICE OPERATION

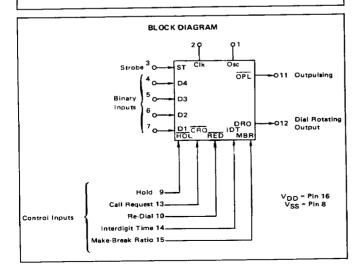

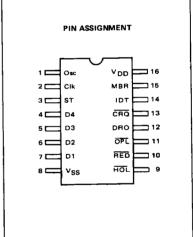

#### OSCILLATOR (Osc. Pin 1)

This pin is an input to the internal oscillator and feed-back connection for the L-C  $\pi$ -network. An external clock signal, if desired can be applied to Osc.

#### CLOCK (Clk. Pin 2)

This pin is an output from the internal oscillator and feedback connection for the L-C  $\pi$ -network and provides the system clock for the MC14419 bounce eliminator circuitry.

## STROBE INPUT (ST. Pin 3)

This Strobe input, when high (ST = V<sub>DD</sub>), signifies that the data at the D1, D2, D3, and D4 inputs is valid, and enters the 4-bit number into the internal FIFO (First-In, First-Out) memory for subsequent outpulsing. The first strobe pulse after a call is requested (CRO = low) clears the memory of any previous number and enters the first digit of the new number. Successive strobe pulses will store up to a maximum of 16 digits in the internal FIFO memory, which ignores all digits entered in excess of that amount until a new call is requested.

## DATA INPUTS (D4, D3, D2, D1, Pins 4, 5, 6, 7)

These pins are the Data inputs to the internal memory. A binary coded digit number entered will result in an equivalent number of pulses at the OPL (outpulsing) output, except for the code 0000, which will outpulse 10 pulses.

# NEGATIVE POWER SUPPLY (VSS, Pin 8)

This pin is the negative power supply connection. Normally this pin is system ground.

## HOLD (HOL, Pin 9)

When taken low (HOL = VSS), the Hold input disables the outpulsing at the completion of the digit being outpulsed. When taken high, outpulsing resumes. This feature can be used in multi-dial-tone phone systems to provide longer interdigit pauses when necessary.

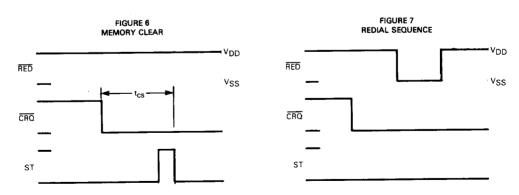

## RE-DIAL (RED, Pin 10)

The Re-Dial input, when taken low  $(\overline{RED} = V_{SS})$  automatically outpulses the digits entered into memory after the last time a call was requested. (See Redial Sequence Diagram Figure 6.)

#### OUTPULSING (OPL. Pin 11)

The Outpulsing output sends out bursts of pulses equivalent to the digits of the telephone number stored in the memory. The duty cycle and interdigit time of the digit pulse bursts are controlled, respectively by the MBR (Pin 15) and IDT (Pin 14).

## DIAL ROTATING OUTPUT (DRO, Pin 12)

The Dial Rotating (also known as "Off Normal") Output provides a signal which indicates that digit pulse bursts are being sent. In the MC14409, DRO goes high (VDD) at the beginning of the first digit pulse burst and goes low (VSS) between succeeding consecutive digit pulse bursts. In the MC14408, however, DRO goes high at the beginning of the first digit pulse burst and remains high until the last digit pulse burst of the telephone number has been sent (see Timing Diagram, Figure 3).

# CALL REQUEST (CRQ, Pin 13)

The Call Request input when taken low (CRQ = VSS) resets internal counters and prepares the internal logic to either accept new digit inputs to be dialed, or to re-dial (see RED, Pin 10) the digits stored in the memory. The Relationship Between Memory Clear and Redial is shown in Figure 7.

## INTERDIGIT TIME (IDT, Pin 14)

The Interdigit Timing input determines the length of time between consecutive digit pulse bursts. See the Interdigit Time ( $t_{\parallel}D$ ) in the switching characteristics for the length of time.

## MAKE-BREAK RATIO (MBR. Pin 15)

The Make-to-Break Ratio input controls the duty cycle of the digit pulse bursts at the  $\overline{OPL}$  output. For MBR = VDD, duty cycle = 67% low, 33% high, and for MBR = VSS, duty cycle = 61% low, 39% high.

# POSITIVE POWER SUPPLY (VDD, Pin 16)

This pin is the package positive power supply pin.

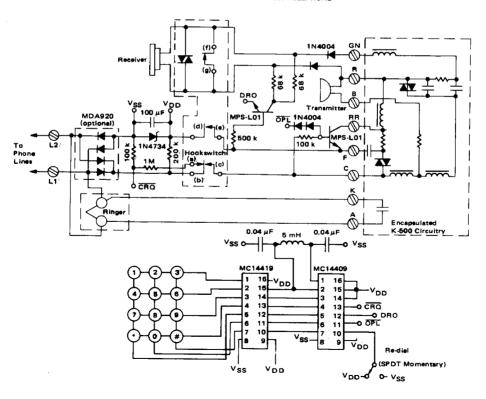

FIGURE 9 - PHONE DIALER SYSTEM

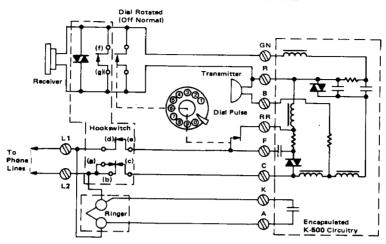

FIGURE 10 - STANDARD K-500 TELEPHONE

FIGURE 11 - MODIFIED K-500 TELEPHONE