### **Features**

- Programmable System Clock with Prescaler and Five Different Clock Sources

- Up to 8-MHz Crystal Oscillator (System Clock)

- 32-kHz Crystal Oscillator

- RC-oscillator Fully Integrated

- RC-oscillator with External Resistor Adjustment

- External Clock Input

- Wide Supply-voltage Range (2.4 V to 6.2 V)

- Very Low Halt Current

- 4-Kbyte EEPROM, 256 × 4-bit RAM

- 8 Hard and Software Interrupt Priority Levels

- Up to 10 External and 4 Internal Interrupts, Bit Wise Maskable with Programmable Priority Level

- Up to 34 I/O Lines

- I/O Ports Bit Wise Configurable with Combined Interrupt Handling (for Serial I/O Applications)

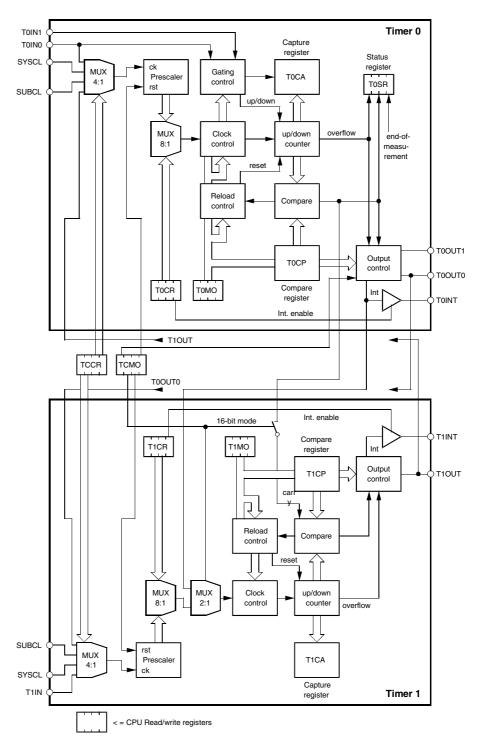

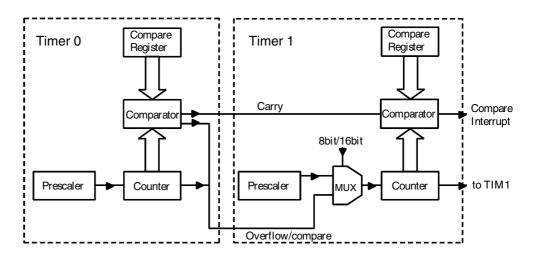

- 2 × 8-bit Multifunction Timer/Counters

- Coded Reset and Watchdog Timer

- Power-on Reset and "Brown Out" Functions

- Various Power-down Modes

- Efficient, Hardware-controlled Interrupt Handling

- High Level Programming Language qFORTH

- Comprehensive Library of Useful Routines

- Windows<sup>®</sup> 95/Windows NT<sup>®</sup> Based Development and Programmer Tools

# **Description**

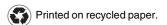

The ATAM510 is a Multi-time Programmable (MTP) microcontroller which is pin and functionally compatible to Atmel's ATAR510 mask programmable microcontroller. It contains an EEPROM, RAM, up to 34 digital I/O pins, up to 10 maskable external interrupt sources, 4 maskable internal interrupts, a watchdog timer, an interval timer,  $2 \times 8$ -bit multifunction timer/counter modules and a versatile software configurable on-chip system clock module.

# MARC4 4-bit MTP Universal Microcontroller

# **ATAM510**

Figure 0-1. Block Diagram

# 1. Pin Configuration

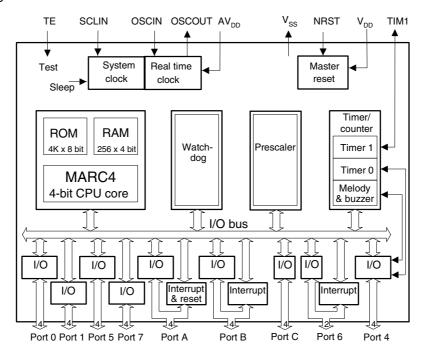

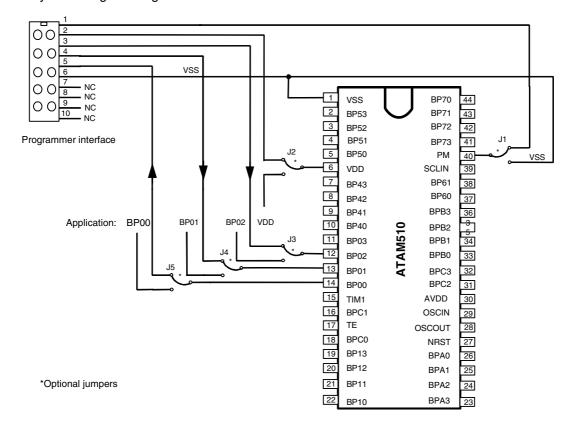

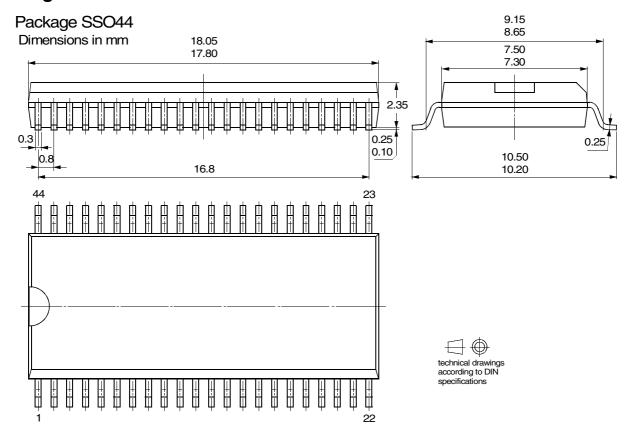

Figure 1-1. Pinning SSO44

Table 1-1.Pin Description

| Pin | Symbol           | Function                                                                    |

|-----|------------------|-----------------------------------------------------------------------------|

| 1   | VSS              | Circuit ground                                                              |

| 2   | BP53             | I/O line of high current Port 5 – bit wise configurable                     |

| 3   | BP52             | I/O line of high current Port 5 – bit wise configurable                     |

| 4   | BP51             | I/O line of high current Port 5 – bit wise configurable                     |

| 5   | BP50             | I/O line of high current Port 5 – bit wise configurable                     |

| 6   | VDD              | Power supply voltage +2.2 V to +6.2 V                                       |

| 7   | BP43<br>(NBUZ)   | High current I/O line BP43 of Port 4 – configurable or buzzer output NBUZ   |

| 8   | BP42<br>(BUZ)    | High current I/O line BP42 of Port 4 – configurable or buzzer output BUZ    |

| 9   | BP41<br>(T0OUT1) | I/O line BP41 of Port 4 – configurable or timer/counter I/O T0OUT1          |

| 10  | BP40<br>(T0OUT0) | I/O line BP40 of Port 4 – configurable or timer/counter I/O T0OUT0          |

| 11  | BP03             | I/O line of Port 0 – automatic nibble wise configurable                     |

| 12  | BP02             | I/O line of Port 0 – automatic nibble wise configurable                     |

| 13  | BP01             | I/O line of Port 0 – automatic nibble wise configurable                     |

| 14  | BP00             | I/O line of Port 0 – automatic nibble wise configurable                     |

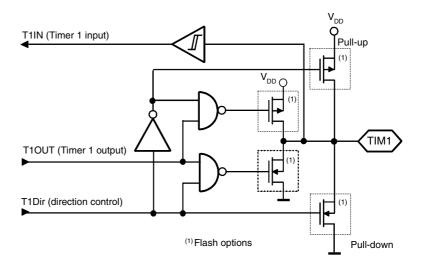

| 15  | TIM1             | Dedicated I/O for Timer 1                                                   |

| 16  | BPC1             | I/O line of Port C – bit wise configurable I/O                              |

| 17  | TE               | Test mode input, used to control production test modes (internal pull-down) |

| 18  | BPC0             | I/O line of Port C – bit wise configurable I/O                              |

| 19  | BP13             | I/O line of Port 1 – automatic nibble wise configurable                     |

Table 1-1.Pin Description

| Pin | Symbol | Function                                                                                                                                   |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 20  | BP12   | I/O line of Port 1 – automatic nibble wise configurable                                                                                    |

| 21  | BP11   | I/O line of Port 1 – automatic nibble wise configurable                                                                                    |

| 22  | BP10   | I/O line of Port 1 – automatic nibble wise configurable                                                                                    |

| 23  | BPA3   | I/O line of Port A – bit wise configurable, as inputs for port monitor module and optional coded reset inputs                              |

| 24  | BPA2   | I/O line of Port A – bit wise configurable, as inputs for port monitor module and optional coded reset inputs                              |

| 25  | BPA1   | I/O line of Port A – bit wise configurable, as inputs for port monitor module and optional coded reset inputs                              |

| 26  | BPA0   | I/O line of Port A – bit wise configurable, as inputs for port monitor module and optional coded reset inputs                              |

| 27  | NRST   | Reset input (/output), a logic low on this pin resets the device. An internal watchdog or coded reset can generate a low pulse on this pin |

| 28  | OSCOUT | 32-kHz or 4-MHz quartz crystal output pin                                                                                                  |

| 29  | OSCIN  | 32-kHz or 4-MHz quartz crystal input pin                                                                                                   |

| 30  | AVDD   | Analog power supply voltage +2.2 V to +6.2 V                                                                                               |

| 31  | BPC2   | I/O line of Port C – bit wise configurable I/O                                                                                             |

| 32  | BPC3   | I/O line of Port C – bit wise configurable I/O                                                                                             |

| 33  | BPB0   | I/O line of Port B – bit wise configurable I/O and as inputs for port monitor module                                                       |

| 34  | BPB1   | I/O line of Port B – bit wise configurable I/O and as inputs for port monitor module                                                       |

| 35  | BPB2   | I/O line of Port B – bit wise configurable I/O and as inputs for port monitor module                                                       |

| 36  | BPB3   | I/O line of Port B – bit wise configurable I/O and as inputs for port monitor module                                                       |

| 37  | BP60   | I/O line of Port 6 – bit wise configurable I/O or as external programmable interrupts                                                      |

| 38  | BP61   | I/O line of Port 6 – bit wise configurable I/O or as external programmable interrupts                                                      |

| 39  | SCLIN  | External trimming resistor or external clock input                                                                                         |

| 40  | PM     | MTP program mode enable pin (internal pull-down)                                                                                           |

| 41  | BP73   | I/O line of high current Port 7 – bit wise configurable                                                                                    |

| 42  | BP72   | I/O line of high current Port 7 – bit wise configurable                                                                                    |

| 43  | BP71   | I/O line of high current Port 7 – bit wise configurable                                                                                    |

| 44  | BP70   | I/O line of high current Port 7 – bit wise configurable                                                                                    |

# 2. MARC4 Architecture

# 2.1 General Description

The functionality, programming and pinning of the ATAM510 is compatible with the ATAR510 mask programmable microcontroller from Atmel. All on-chip modules are addressed and controlled with exactly the same programming code, so that a program targeted for the ATAR510 can be read directly into the ATAM510 and will operate in the same fashion.

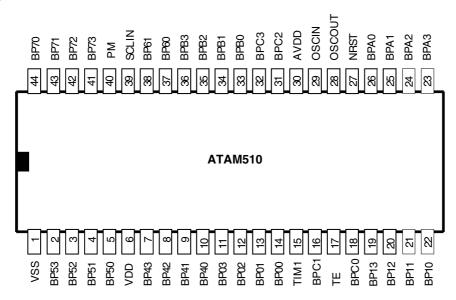

The MARC4 microcontroller consists of an advanced stack-based 4-bit CPU core and on-chip peripherals. The CPU is based on the Harvard architecture with physically separate program memory (ROM) and data memory (RAM). Three independent buses, the instruction bus, the memory bus and the I/O bus, are used for parallel communication between ROM, RAM and peripherals. This enhances program execution speed by allowing both instruction prefetching, and a simultaneous communication to the on-chip peripheral circuitry. The extremely powerful integrated interrupt controller with associated eight prioritized interrupt levels supports fast and efficient processing of hardware events. The MARC4 is designed for the high-level programming language qFORTH. The core includes both an expression and a return stack. This architecture enables high-level language programming without any loss of efficiency or code density.

Figure 2-1. MARC4 Core

# 2.2 Components of MARC4 Core

The core contains ROM, RAM, ALU, a program counter, RAM address registers, an instruction decoder and an interrupt controller. The following sections describe each functional block in more detail.

#### 2.2.1 **EEPROM**

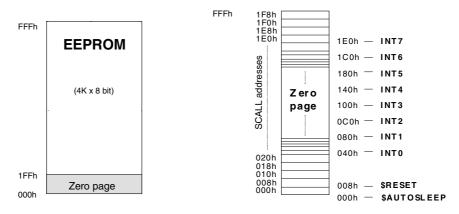

The program memory (EEPROM) is programmed with the customer application program. The EEPROM is addressed by a 12-bit wide program counter, thus predefining a maximum program bank size of 4 Kbytes. The lowest user ROM address segment is taken up by a 512-byte zero page which contains predefined start addresses for interrupt service routines and special subroutines accessible with single byte instructions (SCALL). The corresponding memory map is shown in Figure 2-2. Look-up tables of constants can also be held in EEPROM and are accessed via the MARC4's built-in table instruction.

Figure 2-2. EEPROM Map of the ATAM510

#### 2.2.2 RAM

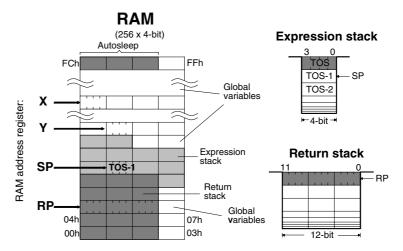

The MARC4 contains 256 x 4-bit wide static random access memory (RAM). It is used for the expression stack, the return stack and data memory for variables and arrays. The RAM is addressed by any of the four 8-bit wide RAM address registers SP, RP, X and Y.

Figure 2-3. RAM Map

#### 2.2.3 Expression Stack

The 4-bit wide expression stack is addressed with the expression stack pointer (SP). All arithmetic, I/O and memory reference operations take their operands from, and return their results to the expression stack. The MARC4 performs the operations with the top of stack items (TOS and TOS-1). The TOS register contains the top element of the expression stack and works in the same way as an accumulator. This stack is also used for passing parameters between subroutines and as a scratch pad area for temporary storage of data.

#### 2.2.4 Return Stack

The 12-bit wide return stack is addressed by the return stack pointer (RP). It is used for storing return addresses of subroutines, interrupt routines and for keeping loop index counts. The return stack can also be used as a temporary storage area.

The MARC4 instruction set supports the exchange of data between the top elements of the expression stack and the return stack. The two stacks, within the RAM, have a user definable location and maximum depth.

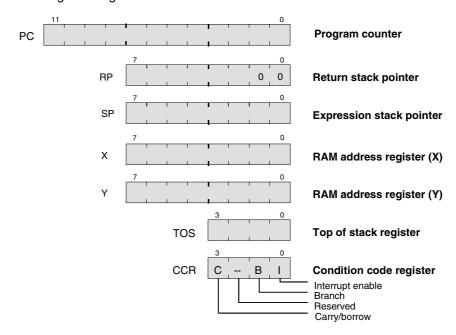

# 2.3 Registers

The MARC4 controller has seven programmable registers and one condition code register. They are shown in the following programming model.

#### 2.3.1 Program Counter (PC)

The program counter is a 12-bit register which contains the address of the next instruction to be fetched from the ROM. Instructions currently being executed are decoded in the instruction decoder to determine the internal micro-operations. For linear code (no calls or branches) the program counter is incremented with every instruction cycle. If a branch, call, return instruction or an interrupt is executed, the program counter is loaded with a new address. The program counter is also used with the table instruction to fetch 8-bit wide constants.

Figure 2-4. Programming Model

#### 2.3.2 RAM Address Registers

The RAM is addressed with the four 8-bit wide RAM address registers: SP, RP, X and Y. These registers allow access to any of the 256 RAM nibbles.

#### 2.3.3 Expression Stack Pointer (SP)

The stack pointer contains the address of the next-to-top 4-bit item (TOS-1) of the expression stack. The pointer is automatically pre-incremented if a nibble is moved onto the stack or post-decremented if a nibble is removed from the stack. Every post-decrement operation moves the item (TOS-1) to the TOS register before the SP is decremented. After a reset the stack pointer has to be initialized with >SP S0 to allocate the start address of the expression stack area.

#### 2.3.4 Return Stack Pointer (RP)

The return stack pointer points to the top element of the 12-bit wide return stack. The pointer automatically pre-increments if an element is moved onto the stack, or it post-decrements if an element is removed from the stack. The return stack pointer increments and decrements in steps of 4. This means that every time a 12-bit element is stacked, a 4-bit RAM location is left unwritten. This location is used by the qFORTH compiler to allocate 4-bit variables. After a reset the return stack pointer has to be initialized via >RP FCh.

# 2.3.5 RAM Address Registers (X and Y)

The X and Y registers are used to address any 4-bit item in the RAM. A fetch operation moves the addressed nibble onto the TOS. A store operation moves the TOS to the addressed RAM location. By using either the pre-increment or post-decrement addressing mode arrays in the RAM can be compared, filled or moved.

#### 2.3.6 Top of Stack (TOS)

The top of stack register is the accumulator of the MARC4. All arithmetic/logic, memory reference and I/O operations use this register. The TOS register receives data from the ALU, ROM, RAM or I/O bus.

# 2.3.7 Condition Code Register (CCR)

The 4-bit wide condition code register contains the branch, the carry and the interrupt enable flag. These bits indicate the current state of the CPU. The CCR flags are set or reset by ALU operations. The instructions SET\_BCF, TOG\_BF, CCR! and DI allow direct manipulation of the condition code register.

#### 2.3.8 Carry/Borrow (C)

The carry/borrow flag indicates that the borrow or carry out of the Arithmetic Logic Unit (ALU) occurred during the last arithmetic operation. During shift and rotate operations, this bit is used as a fifth bit. Boolean operations have no affect on the C-flag.

#### 2.3.9 Branch (B)

The branch flag controls the conditional program branching. Should the branch flag have been set by a previous instruction, a conditional branch will cause a jump. This flag is affected by arithmetic, logic, shift, and rotate operations.

#### 2.3.10 Interrupt Enable (I)

The interrupt enable flag globally enables or disables the triggering of all interrupt routines with the exception of the non-maskable reset. After a reset or while executing the DI instruction, the interrupt enable flag is reset, thus disabling all interrupts. The core will not accept any further interrupt requests until the interrupt enable flag has been set again by either executing an EI or SLEEP instruction.

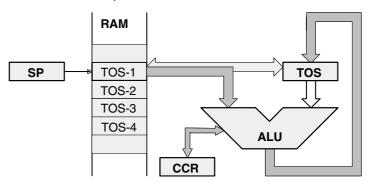

#### 2.4 ALU

The 4-bit ALU performs all the arithmetic, logical, shift and rotate operations with the top two elements of the expression stack (TOS and TOS-1) and returns the result to the TOS. The ALU operations affect the carry/borrow and branch flag in the condition code register (CCR).

Figure 2-5. ALU Zero-address Operations

#### 2.4.1 Instruction Set

The MARC4 instruction set is optimized for the high level programming language qFORTH. Many MARC4 instructions are qFORTH words. This enables the compiler to generate a fast and compact program code. The CPU has an instruction pipeline which allows the controller to prefetch an instruction from EEPROM at the same time as the present instruction is being executed. The MARC4 is a zero-address machine, the instructions contain only the operation to be performed and no source or destination address fields. The operations are implicitly performed on the data placed on the stack. There are one and two byte instructions which are executed within 1 to 4 machine cycles. A MARC4 machine cycle is made up of two system clock cycles (SYSCL). Most of the instructions are only one byte long and are executed in a single machine cycle.

#### 2.4.2 I/O Bus

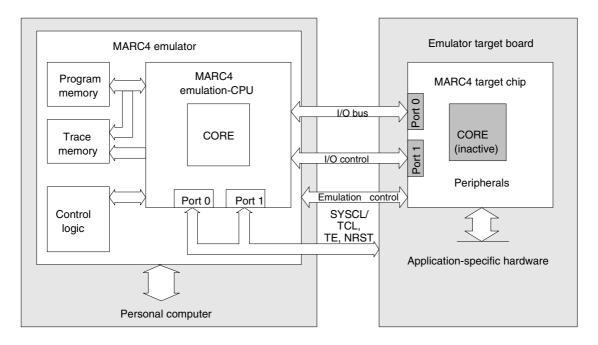

The I/O ports and the registers of the peripheral modules are I/O mapped. All communication between the core and the on-chip peripherals takes place via the I/O bus and the associated I/O control. With the MARC4 IN and OUT instructions the I/O bus allows a direct read or write access to one of the 16 primary I/O addresses. More about the I/O access to the on-chip peripherals is described in the section "Peripheral Modules". The I/O bus is internal and is not accessible by the customer on the final microcontroller device, but it is used as the interface for the MARC4 emulation.

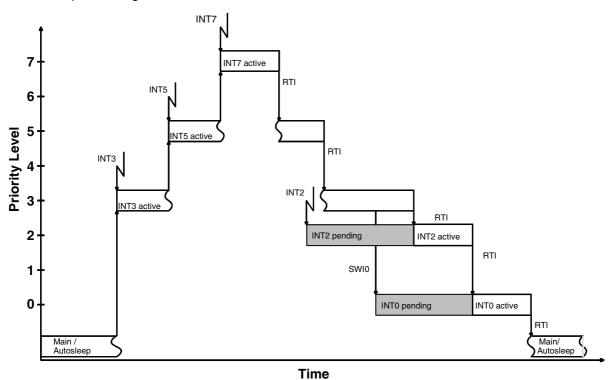

### 2.5 Interrupt Structure

The MARC4 can handle interrupts with eight different priority levels. They can be generated from the internal and external interrupt sources or by a software interrupt from the CPU itself. Each interrupt level has a hard-wired priority and an associated vector for the service routine in the ROM (see Table 2-1 on page 11). The programmer can postpone the processing of interrupts by resetting the interrupt enable flag (I) in the CCR. An interrupt occurrence will still be registered, but the interrupt routine only started after the I flag is set. All interrupts can be masked, and the priority individually software configured by programming the appropriate control register of the interrupting module (see section "Peripheral Modules").

#### 2.5.1 Interrupt Processing

For processing the eight interrupt levels, the MARC4 includes an interrupt controller with two 8-bit wide interrupt pending and interrupt active registers. The interrupt controller samples all interrupt requests during every non-I/O instruction cycle and latches these in the interrupt pending register. Whenever an interrupt request is detected, the CPU interrupts the program currently being executed, on condition that no higher priority interrupt is present in the interrupt active register. If the interrupt enable bit is set, the processor enters an interrupt acknowledge cycle. During this cycle a short call (SCALL) instruction to the service routine is executed and the current PC is saved on the return stack.

An interrupt service routine is completed with the RTI instruction. This instruction resets the corresponding bits in the interrupt pending/active register and fetches the return address from the return stack to the program counter. When the interrupt-enable flag is reset (triggering of interrupt routines are disabled), the execution of new interrupt service routines is inhibited but not the logging of the interrupt requests in the interrupt pending register. The execution of the interrupt is delayed until the interrupt-enable flag is set again. Note that interrupts are only lost if an interrupt request occurs while the corresponding bit in the pending register is still set (i.e., the interrupt service routine is not yet finished).

After a master reset (power-on, brown-out or watchdog reset), the interrupt-enable flag and the interrupt pending and interrupt active registers are all reset.

#### 2.5.2 Interrupt Latency

The interrupt latency is the time from the occurrence of the interrupt to the interrupt service routine being activated. In MARC4 this is extremely short (taking between 3 to 5 machine cycles depending on the state of the core).

Figure 2-6. Interrupt Handling

Table 2-1.

Interrupt Priority Table

| Interrupt | Priority | ROM Address | Maskable | Interrupt Opcode |

|-----------|----------|-------------|----------|------------------|

| INT0      | Lowest   | 040h        | Yes      | C8h (SCALL 040h) |

| INT1      | I        | 080h        | Yes      | D0h (SCALL 080h) |

| INT2      | I        | 0C0h        | Yes      | D8h (SCALL 0C0h) |

| INT3      | I        | 100h        | Yes      | E8h (SCALL 100h) |

| INT4      | I        | 140h        | Yes      | E8h (SCALL 140h) |

| INT5      | I        | 180h        | Yes      | F0h (SCALL 180h) |

| INT6      | <b>\</b> | 1C0h        | Yes      | F8h (SCALL 1C0h) |

| INT7      | Highest  | 1E0h        | Yes      | FCh (SCALL 1E0h) |

Table 2-2. Hardware Interrupts

|                     |   | Possible Interrupt Priorities |   |   |   |   |   |   |     | Interrup | ot Mask |                                      |  |

|---------------------|---|-------------------------------|---|---|---|---|---|---|-----|----------|---------|--------------------------------------|--|

| Interrupt Source    | 0 | 1                             | 2 | 3 | 4 | 5 | 6 | 7 | RST | Register | Bit     | Function                             |  |

| NRST external       |   |                               |   |   |   |   |   |   | Х   | _        | _       | Low level active                     |  |

| Watchdog            |   |                               |   |   |   |   |   |   | #   | _        | _       | 1/2 to 2 s time out                  |  |

| Port A coded reset  |   |                               |   |   |   |   |   |   | #   | _        | _       | Level any inputs                     |  |

| Port A monitor      |   | *                             |   | * |   | * |   | * |     | PAIPR    | 3       | Any edge, any input                  |  |

| Port B monitor      |   | *                             |   | * |   | * |   | * |     | PBIPR    | 3       | Any edge, any input                  |  |

| Port 60 external    |   | *                             |   | * |   | * |   | * |     | P6CR     | 1.0     | Any edge                             |  |

| Port 61 external    | * |                               | * |   | * |   | * |   |     | P6CR     | 3.2     | Any edge                             |  |

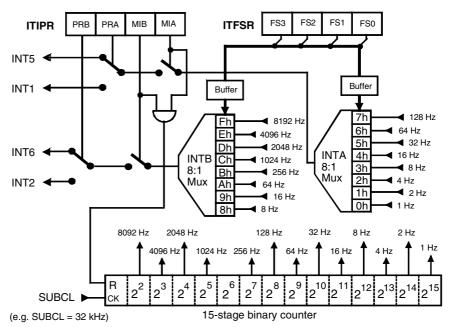

| Interval timer INTA |   | *                             |   |   |   | * |   |   |     | ITIPR    | 0       | 1 of 8 frequencies<br>(8 to 128 Hz)  |  |

| Interval timer INTB |   |                               | * |   |   |   | * |   |     | ITIPR    | 1       | 1 of 8 frequencies<br>(8 to 8192 Hz) |  |

| Timer 0             |   | *                             |   | * |   | * |   | * |     | T0CR     | 0       | Overflow/compare/<br>end measurement |  |

| Timer 1             | * |                               | * |   | * |   | * |   |     | T1CR     | 0       | Compare                              |  |

X = Hardwired (neither optional or software configurable)

In the ATAM510, there are eleven hardware interrupt sources which can be programmed to occupy a variety of priority levels. With the exception of the reset sources (RST), each source can be individually masked by mask bits in the corresponding control registers. An overview of the possible hardware configurations is shown in Table 2-2.

#### 2.5.3 Software Interrupts

The programmer can generate interrupts by using the software interrupt instruction (SWI) which is supported in qFORTH by predefined macros named SWI0 to SWI7. The software triggered interrupt operates exactly like any hardware triggered interrupt. The SWI instruction takes the top two elements from the expression stack and writes the corresponding bits via the I/O bus to the interrupt pending register. Therefore, by using the SWI instruction, interrupts can be re-prioritized or lower priority processes scheduled for later execution.

<sup># =</sup> Customer mask option (see "Hardware Options")

<sup>\* =</sup> Software configurable (see "Peripheral Modules" section for further details)

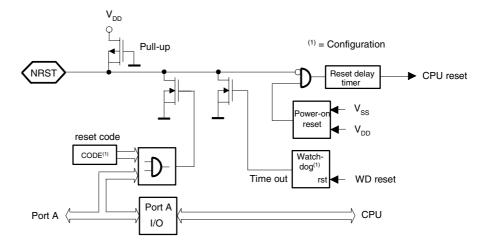

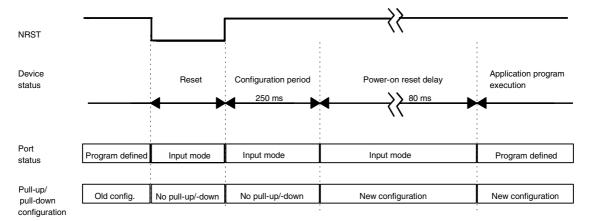

#### 2.6 Hardware Reset

The master reset forces the CPU into a well-defined condition. It is unmaskable and is activated independent of the current program state. It can be triggered by either initial supply power-up, a short collapse of the power supply, a watchdog time-out, activation of the NRST input, or the occurrence of a coded reset on Port A (see Figure 2-7).

A master reset activation will reset the interrupt enable flag, the interrupt pending registers the interrupt active registers and initializes all on-chip peripherals. In this state all ports take on a high resistance input status with deactivated pull-up and pull-down transistors (see Figure 2-9 on page 16)

When the reset condition disappears, the hardware configuration previously programmed in the configuration EEPROM (see section "MTP Programming") is loaded into the peripherals so that all port characteristics and pull-up/downs reflect the programmed configuration. This configuration period is immediately followed by a further reset delay time (approximately 80 ms), after which a short call instruction (opcode C1h) to the EEPROM address 008h is performed. This activates the initialization routine \$RESET which in turn initializes all necessary RAM variables, stack pointers and peripheral configuration registers.

Figure 2-7. Reset Configuration/Start-up Sequence

#### 2.6.1 Power-on Reset

The fully integrated power-on reset circuit ensures that the core is held in a reset state until the minimum operating supply voltage has been reached. A reset condition is also generated should the supply voltage drop momentarily below the minimum operating supply.

#### 2.6.2 External Reset (NRST)

An external reset can be triggered with the NRST pin. To activate an external reset, the pin should be low for a minimum of  $4 \mu s$ .

#### 2.6.3 Coded Reset (Port A)

The coded reset circuit is connected directly to Port A terminals. By using a mask option, the user can define a hardwired code combination (e.g., all pins low) which, if occurring on Port A, will generate a reset in the same way as the NRST pin.

Table 2-3. Multiple Key Reset Options

| NO_RST | Not used (default)                     |

|--------|----------------------------------------|

| RST2   | BPA0 and BPA1 = low                    |

| RST3   | BPA0 and BPA1 and BPA2 = low           |

| RST4   | BPA0 and BPA1 and BPA2 and BPA3 = low  |

| RST5   | BPA0 and BPA1 = high                   |

| RST6   | BPA0 and BPA1 and BPA2 = high          |

| RST7   | BPA0 and BPA1 and BPA2 and BPA3 = high |

Note:

If this option is used, the reset is not maskable and will also trigger if the predefined code is written on to Port A by the CPU itself. Care should also be taken not to generate an unwanted reset by inadvertently passing through the reset code on input transitions. This applies especially if the pins have a high capacitive load.

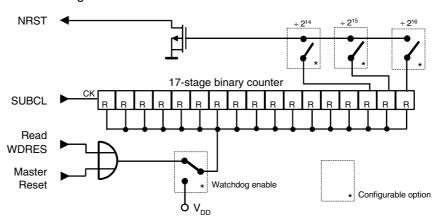

## 2.6.4 Watchdog Reset

The watchdog's function can be enabled via a mask option and triggers a reset with every watchdog counter overflow. To suppress the watchdog reset, the counter must be regularly reset by reading the watchdog register address (CWD). The CPU reacts in exactly the same manner as a reset stimulus from any of the above sources.

Figure 2-8. Normal Mode Start-up

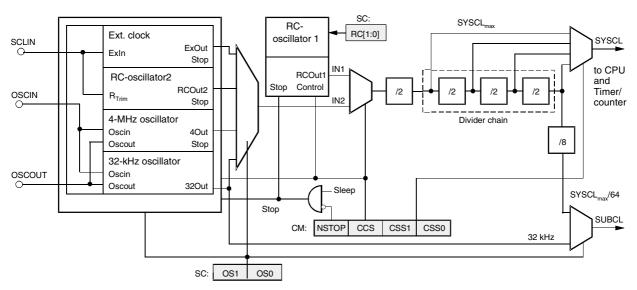

#### 2.7 Clock Generation

#### 2.7.1 Clock Module

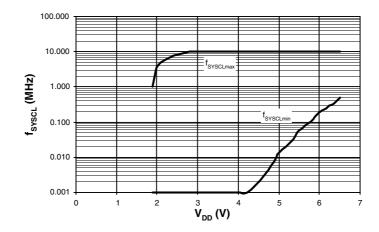

The clock module generates two clocks. The system clock (SYSCL) supplies the CPU and the peripherals while the lower frequency periphery sub-clock (SUBCL) supplies only the peripherals. The modes for clock sources are programmable with the OS1-bit and OS0-bit in the SC-register and the CCS-bit in the CM-register.

The clock module includes 4 different internal oscillator types: two RC-oscillators, one 4-MHz crystal oscillator and one 32-kHz crystal oscillator. The pins OSC1 and OSC2 provide the interface to connect a crystal either to the 4-MHz, or to the 32-kHz crystal oscillator. SCLIN can be used as an input for an external clock or to connect an external trimming resistor for the RC-oscillator 2. All necessary components with the exception of the crystal and the trimming resistor is integrated on-chip. Any one of these clock sources can be selected to generate the system clock (SYSCL).

In applications that do not require exact timing, it is possible to use the fully integrated RC-oscillator 1 without any external components. The RC-oscillator 2 is more stable but the oscillator frequency must be trimmed with an external resistor attached between SCLIN and  $V_{DD}$ . In this configuration, for system clock frequencies below 2 MHz, the RC-oscillator 2 frequency can be maintained stable with a tolerance of  $\pm 10\%$  over the full operating temperature and voltage range.

The clock module is software programmable using the clock management register (CM) and the system configuration register (SC). The required oscillator configuration can be selected with the OS(1:0)-bits in the SC-register. A programmable 4-bit divider stage allows the adjustment of the system clock speed. A synchronization stage avoids any clock glitches which could be caused by clock source switching.

The CPU always requires SYSCL clocks to execute instructions, process interrupts and enter or leave the SLEEP state. Internal oscillators are, depending on the condition of the NSTOP-bit automatically stopped and started where necessary. Special care must however be taken when using an external clock source which is gated by one of the microcontroller port signals. This configuration can hang up if the external oscillator is switched off while the external clock source is still selected. It is therefore advisable in such a case to switch first to the internal RC-oscillator 1 source using the CSS-bit. The external source can then be reselected later when the external oscillator has again been restarted.

Figure 2-9. Clock Module

Table 2-4. Clock Modes

|      |     |     | Clock Source                  | e for SYSCL                                     | Clock Sourc             | e for SUBCL             |

|------|-----|-----|-------------------------------|-------------------------------------------------|-------------------------|-------------------------|

| Mode | OS1 | OS0 | CCS = 1                       | CCS = 0                                         | CCS = 1                 | CCS = 0                 |

| 1    | 1   | 1   | RC-oscillator 1 (internal)    | External input clock                            | SYCL <sub>max</sub> /64 | SCLIN/128               |

| 2    | 0   | 1   | RC-oscillator 1<br>(internal) | RC-oscillator 2 with external trimming resistor | SYCL <sub>max</sub> /64 | SYCL <sub>max</sub> /64 |

| 3    | 1   | 0   | RC-oscillator 1 (internal)    | 4-MHz oscillator                                | SYCL <sub>max</sub> /64 | f <sub>XTAL</sub> /128  |

| 4    | 0   | 0   | RC-oscillator 1 (internal)    | 32-kHz oscillator                               | 32 kHz                  |                         |

#### 2.7.2 Oscillator Circuits and External Clock Input Stage

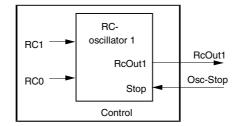

### 2.7.2.1 RC-oscillator 1 Fully Integrated

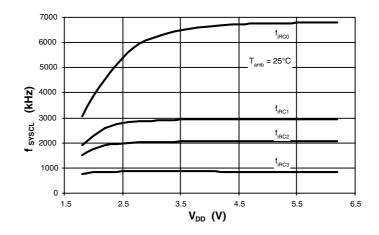

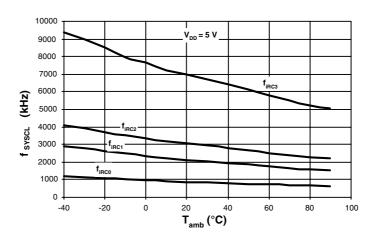

For timing insensitive applications, it is possible to use the fully integrated RC-oscillator 1. It operates without any external components and saves additional costs. The RC-oscillator 1 center frequency tolerance is better than  $\pm 50\%$  over the full temperature and voltage range. A reduction in the application operating supply voltage and temperature ranges will result in improved frequency tolerance. For more detailed information see Figure 7-8 to Figure 7-9 on page 66. The basic center frequency of the RC-oscillator 1 is programmable with the RC1 and the RC0-bits in the SC-register.

Figure 2-10. RC-oscillator 1

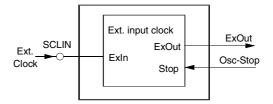

#### 2.7.2.2 External Input Clock

The SCLIN pin can be driven by an external clock source provided it meets the specified duty cycle, rise and fall times and input levels. The maximum system clock frequency f<sub>SYSCLmax</sub> that the core can operate is f<sub>SCLIN</sub>/2 (see Figure 2-11).

Figure 2-11. External Input Clock

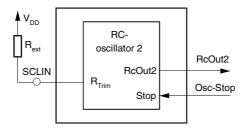

#### 2.7.2.3 RC-oscillator 2 with External Trimming Resistor

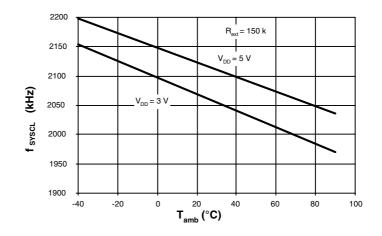

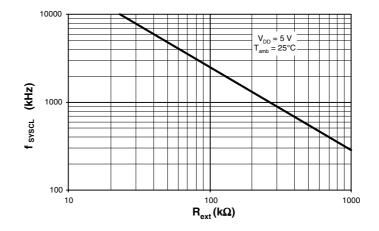

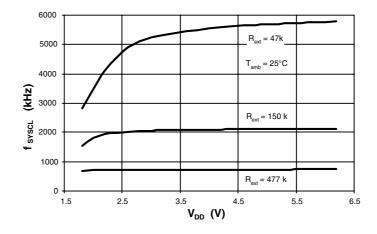

The RC-oscillator 2 is a high stability oscillator whereby the oscillator frequency can be trimmed with an external resistor between SCLIN and V<sub>DD</sub>. In this configuration, as long as the system clock frequency does not exceed 2 MHz, the RC-oscillator 2 frequency can be maintained stable with a tolerance of ±10% over the full operating temperature and voltage range.

For example: A SYSCL<sub>max</sub> frequency of 2 MHz, can be obtained by connecting a resistor R<sub>ext</sub> = 150 k $\Omega$  (see Figure 2-12, Figure 7-6 on page 65 to Figure 7-7 on page 65).

Figure 2-12. RC-oscillator 2

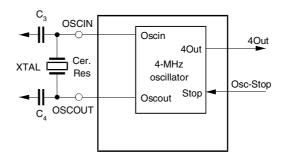

#### 2.7.2.4 4-MHz Oscillator

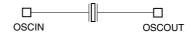

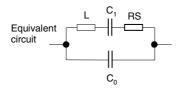

The integrated system clock oscillator requires an external crystal or ceramic resonator connected between the OSCIN and OSCOUT pins to establish oscillation. All the necessary oscillator circuitry, with the exception of the actual crystal, resonator and the optional C3 and C4 are integrated on-chip.

Figure 2-13. System Clock Oscillator

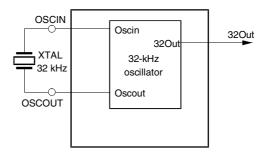

#### 2.7.2.5 32-kHz Oscillator

Some applications require accurate long-term time keeping without putting excessive demands on the CPU or alternatively low resolution computing power. In this case, the on-chip ultra low power 32-kHz crystal oscillator can be used to generate both the SUBCL and/or the SYSCL. In this mode, power consumption can be significantly reduced. The 32-kHz crystal oscillator will key operating (not stopped) during any CPU power-down/SLEEP mode.

Figure 2-14. 32-kHz Crystal Oscillator

Note: Both, the 4-MHz and the 32-kHz crystal oscillator, use an integrated 14 stage divider circuit to stabilize oscillation before the oscillator output is used as system clock. This results in an additional delay of about 4 ms for the 4-MHz crystal and about 500 ms for the 32-kHz crystal.

#### 2.7.2.6 Quartz Oscillator Configuration

If the customer's application necessitates the use of a quartz crystal clock source and this requires capacitive trimming, the trimming capacitors are not integrated into the MTP unlike the ATAR510 and should therefore be connected externally as discrete components between the respective Quartz Crystal terminals (OSCIN, OSCOUT) and VSS.

### 2.7.3 Clock Management Register (CM)

The clock management register controls the system clock divider chain, as well as the peripheral clock in power-down modes.

Auxiliary register address: 'E'hex

Bit 3

Bit 2

Bit 1

Bit 0

CM

NSTOP

CCS

CSS1

CSS0

Reset value: 1111b

Not STOP peripheral clock

NSTOP = 0, stops the peripheral clock while the core is in SLEEP mode

The 32-kHz crystal oscillator SUBCL clock cannot be stopped

NSTOP = 1, enables the peripheral clock while the core is in SLEEP mode

Core Clock Select

CCS = 1, the internal RC-oscillator 1 generates SYSCL

CCS = 0, the 4-MHz crystal oscillator, the 32-kHz crystal oscillator, an external

clock source or the RC-oscillator 2 (with the external resistor) will generate SYSCL dependent on the setting of OS0 and OS1 in the  $\,$

system configuration register

CSS1 (1:0) Core Speed Select

These two bits control the system clock divider chain

Table 2-5. Core Speed Select

| CSS1 | CSS0 | Divider | Note                               |

|------|------|---------|------------------------------------|

| 0    | 0    | 16      | SYSCL <sub>max</sub> /8            |

| 0    | 1    | 8       | SYSCL <sub>max</sub> /4            |

| 1    | 0    | 4       | SYSCL <sub>max</sub> /2            |

| 1    | 1    | 2       | Reset value = SYSCL <sub>max</sub> |

#### 2.7.4 System Configuration Register (SC)

Primary register address: 'E'hex

Bit 3

Bit 2

Bit 1

Bit 0

SC: write

RC1

RC0

OS1

OS0

Reset value: 1111b

**Table 2-6.** Internal RC Oscillator 1 Frequency Selection (SYSCL<sub>max</sub>)

| RC1 | RC0 | SYSCL <sub>max</sub> at 25°C, V <sub>DD</sub> = 5 V | Note        |

|-----|-----|-----------------------------------------------------|-------------|

| 0   | 0   | 7.0 MHz (f <sub>iRC0</sub> )                        | -           |

| 0   | 1   | 3.0 MHz (f <sub>iRC1</sub> )                        | -           |

| 1   | 0   | 2.0 MHz (f <sub>iRC2</sub> )                        | _           |

| 1   | 1   | 0.8 MHz (f <sub>iRC3</sub> )                        | Reset value |

OS1, OS0 Oscillator selection bits (in conjunction with the CCS-bit)

Table 2-7. Oscillator Select

| ccs | OS1 | OS0 | SUBCL                              | System Oscillator Selection           |

|-----|-----|-----|------------------------------------|---------------------------------------|

| 0   | 1   | 1   |                                    | External input clock at SCLIN         |

| 0   | 0   | 1   | SYSCL <sub>max</sub> /64           | RC-oscillator 2 with R <sub>ext</sub> |

| 0   | 1   | 0   |                                    | 4-MHz crystal oscillator              |

| 0   | 0   | 0   | 32 kHz                             | 32-kHz crystal oscillator             |

| 1   | х   | х   | SYSCL <sub>max</sub> /64 or 32 kHz | RC-oscillator 1                       |

Note: If the bit CCS = 0 in the CM-register, the RC-oscillator 1 is stopped.

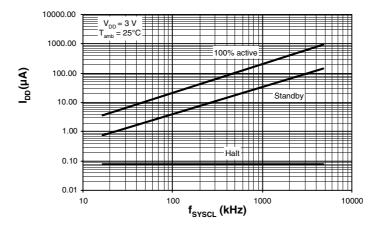

#### 2.7.5 Power-down Modes

The ATAM510 incorporates several modes which enable the power consumption to be tailored to a minimum without sacrificing computational power. When the controller exits the lowest priority interrupt task, it reverts to a SLEEP state. This is a CPU shutdown condition which is used to reduce average system power consumption where the CPU itself is only partially utilized. In SLEEP, the CPU clocking system is deactivated whereby the peripherals and associated clock sources may remain active (Standby Mode) or they can also be halted (Halt Mode). In Standby Mode, the peripherals are able to continue operation and if required also generate interrupts which can, along with a reset, reactivate the CPU to bring it out of the sleep state.

SLEEP can only be maintained when none of the interrupt pending or active register bits are set. The application of the \$AUTOSLEEP routine ensures the correct function of the sleep mode.

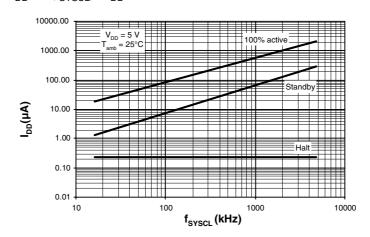

In both Standby and Active modes the current consumption is largely dependent on the frequency of the CPU system clock (SYSCL) and the supply voltage (VDD) (see Figure 7-3 and Figure 7-4 on page 64) while the Halt Mode current is merely controller static leakage current.

Selection of Standby or Halt mode is performed by the NSTOP bit in the clock management register (CM). It should be noted that the low power 32-kHz crystal oscillator, if enabled will always remain active in both Standby and Halt modes.

Table 2-8. Power-down Modes

| Mode    | CPU Core<br>State | NSTOP | RC-Oscillator 1<br>RC-Oscillator 2<br>4-MHz Oscillator | 32-kHz<br>Oscillator | External Input<br>Clock at SCLIN |

|---------|-------------------|-------|--------------------------------------------------------|----------------------|----------------------------------|

| Active  | RUN               | 1     | RUN                                                    | RUN                  | Enabled                          |

| Standby | SLEEP             | 1     | RUN                                                    | RUN                  | Enabled                          |

| Halt    | SLEEP             | 0     | STOP                                                   | RUN                  | Disabled                         |

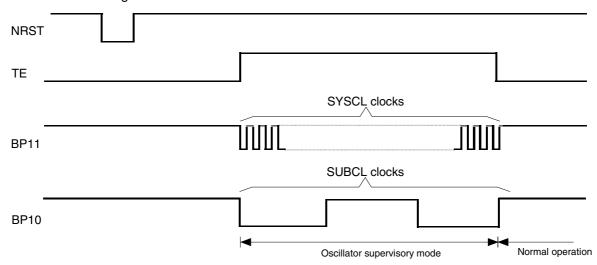

#### 2.7.6 Clock Monitor Mode

Figure 2-15. Clock Monitoring

For trimming purposes, the ATAM510 can be put into a clock monitor mode. By forcing the test input (TE) high, the SYSCL clock will appear on BP11 (Port 1, bit 1) and SUBCL clock on Port BP10 (Port 1, bit 0). On releasing the TE pin, the BP10 and BP11 will resume their normal function (see Figure 2-15).

# 3. Peripheral Modules

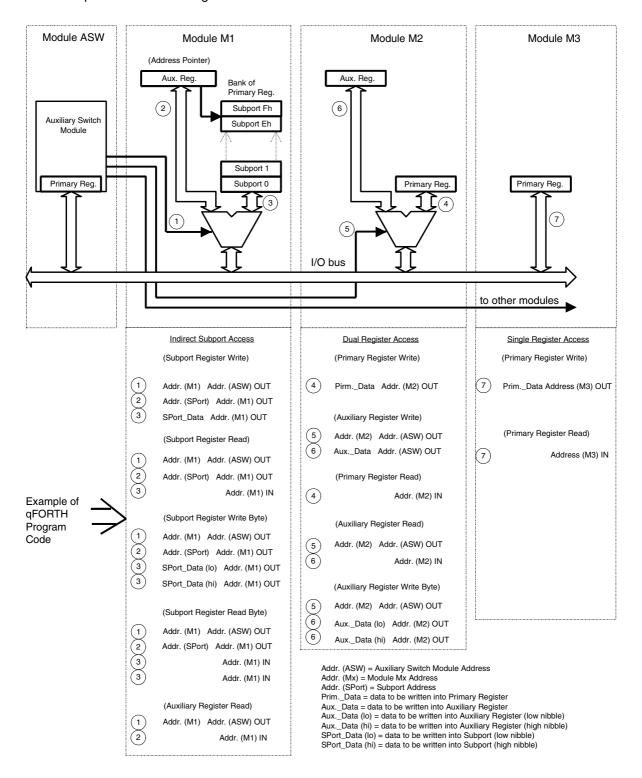

# 3.1 Addressing Peripherals

Accessing the peripheral modules takes place via the I/O bus (see Figure 3-1 on page 22). The IN or OUT instructions allow direct addressing of up to 16 I/O modules. A dual register addressing scheme has been adopted which addresses the "primary register" directly. To address the "auxiliary register", the access must be switched with an "auxiliary switching module". Thus, a single IN (or OUT) to the module address will read (or write) into the module primary register. Accessing the auxiliary register is performed with the same instruction preceded by writing the module address into the auxiliary switching module. Byte-wide registers are accessed by multiple IN (or OUT) instructions. Extended addressing is used for more complex peripheral modules, with a larger number of registers. In this case, a bank of up to 16 subport registers are indirectly addressed with the subport address being initially written into the auxiliary register. Please refer to the "HARDC510.SCR" hardware interface file as a programming guideline.

Figure 3-1. Example of I/O Addressing

Table 3-1.

Peripheral Addresses

|   | Port Addres | s         | Name   | Write/Read | Reset Value | Register Function                        | Module<br>Type                                                                                                                                                                                                                                                                                                                                                                                                                                                 | See<br>Pag |

|---|-------------|-----------|--------|------------|-------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 0 |             |           | P0DAT  | W/R        | 1111b       | Port 0 - data register/input data        | M3                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25         |

| 1 |             |           | P1DAT  | W/R        | 1111b       | Port 1- data register/input data         | МЗ                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25         |

| 2 |             |           | PAIPR  | W          | 1111b       | Port A - interrupt priority register     | MO                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2          |

|   | Auxiliary   |           | PAICR  | W          | 1111b       | Port A - interrupt control register      | IVIZ                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2          |

| 3 |             |           | CWD    | R          | _           | Watchdog timer reset                     | МЗ                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.         |

|   |             |           | PBIBR  | W          | 1111b       | Port B- interrupt priority register      | MO                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2          |

|   | Auxiliary   |           | PBICR  | W          | 1111b       | Port B- interrupt control register       | M3<br>M3<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2          |

| 4 |             |           | P4DAT  | W/R        | 1111b       | Port 4 - data register/pin data          | Type           M3           M3           M2           M2           M2           M2           M2           M2           M2           ASW           M1           M2                                                                              | 2          |

|   | Auxiliary   |           | P4DDR  | W          | 1111b       | Port 4 - data direction register         | IVIZ                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2          |

| 5 | ,           |           | P5DAT  | W/R        | 1111b       | Port 5 - data register/pin data          | Type           M3           M3           M2           M3           M2           M2           M2           M2           M2           M2           M1           M2                                                                               | 2          |

|   | Auxiliary   |           | P5DDR  | W          | 1111b       | Port 5 - data direction register         | Type           M3           M3           M2           M3           M2           M2           M2           M2           M2           M2           M3           M2           M2           M3           M4           M1           M2 | 2          |

| 6 |             |           | P6DAT  | W/R        | 0011b       | Port 6 - data register/pin data          | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3          |

|   | Auxiliary   |           | P6CR   | W          | 1111 1111b  | Port 6 - control register (byte)         | - M2                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3          |

| 7 |             |           | P7DAT  | W/R        | 1111b       | Port 7- data register/pin data           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2          |

|   | Auxiliary   |           | P7DDR  | W          | 1111b       | Port 7- data direction register          | - M2                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2          |

| 8 |             |           | ASW    | W          | 1111b       | Auxiliary switch register                | ASW                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2          |

| 9 |             |           | TCM    | W/R        | 1111b       | Data to/from subport addressed by TCSUB  | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2          |

|   | Auxiliary   |           | T0SR   | R          | 0000b       | Timer 0 interrupt status register        | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4          |

|   |             |           | TCSUB  | W          | 1111b       | Timer/counter subport address pointer    | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3          |

|   |             | Subport a | ddress |            |             |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|   |             | 0         | TOMO   | W          | 1111b       | Timer 0 mode register                    | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4          |

|   |             | 1         | T0CR   | W          | 1111b       | Timer 0 control register                 | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4          |

|   |             | 2         | T1M0   | W          | 1111b       | Timer 1 mode register                    | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5          |

|   |             | 3         | T1CR   | W          | 1111b       | Timer 1 control register                 | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5          |

|   |             | 4         | ТСМО   | W          | 1111b       | Timer/counter mode register              | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4          |

|   |             | 5         | TCIOR  | W          | 1111b       | Timer/counter I/O control register       | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3          |

|   |             | 6         | TCCR   | W          | 1111b       | Timer/counter control register           | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3          |

|   |             | 7         | TCIP   | W          | 1111b       | Timer/counter interrupt priority         | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3          |

|   |             | 8         | T1CP   | W          | xxxx xxxxb  | Timer 1 compare register (byte)          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5          |

|   |             |           | T1CA   | R          | xxxx xxxxb  | Timer 1 capture register (byte)          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5          |

|   |             | 9         | T0CP   | W          | xxxx xxxxb  | Timer 0 compare register (byte)          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4          |

|   |             |           | TOCA   | R          | xxxx xxxxb  | Timer 0 capture register (byte)          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4          |

|   |             | Α         | BZCR   | W          | 1111b       | Buzzer control register                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5          |

|   |             | B-F       |        |            |             | Reserved                                 | ••••                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

| Α |             |           | PADAT  | W/R        | 1111b       | Port A - data register/pin data          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2          |

|   | Auxiliary   |           | PADDR  | W          | 1111b       | Port A - data direction register         | M2                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2          |

| В | / turinal y |           | PBDAT  | W/R        | 1111b       | Port B - data register/pin data          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2          |

| _ | Auxiliary   |           | PBDDR  | W          | 1111b       | Port B - data direction register         | M2                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2          |

| С | raxilary    |           | PCDAT  | W/R        | 1111b       | Port C - data register/pin data          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2          |

| • | Auxiliary   |           | PCDDR  | W          | 1111b       | Port C - data direction register         | M2                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2          |

| D | / wallary   |           | _      | _          | -           | Reserved                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _          |

| E |             |           | SC     | W          | 1111b       | System configuration register            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1          |

| _ | Auxiliary   |           | CM     | W/R        | 1111b       | Clock management register                | M2                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1          |

| F | Auxillaly   |           | ITFSR  | W W        | 1111b       | Interval timer frequency select register |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3          |

|   |             |           | IIIFOR | VV         | HILLD       | interval timer frequency select register | M2                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3          |

### 3.2 Bi-directional Ports

**Table 3-2.** Overview of Port Features

| Port Address                                    | 0                 | 1    | 4       | 5    | 6                  | 7    | Α                                  | В               | С    |

|-------------------------------------------------|-------------------|------|---------|------|--------------------|------|------------------------------------|-----------------|------|

| Number of bits                                  | 4                 | 4    | 4       | 4    | 2                  | 4    | 4                                  | 4               | 4    |

| Bit wise programmable direction                 | no                | no   | yes     | yes  | yes                | yes  | yes                                | yes             | yes  |

| Output drivers mask configurable <sup>(1)</sup> | no <sup>(2)</sup> | yes  | yes     | yes  | yes                | yes  | yes                                | yes             | yes  |

| Dynamic pull-up/-down typ. (Ohm) <sup>(3)</sup> | 500k              | 500k | 500k    | 500k | 500k               | 500k | 500k                               | 500k            | 500k |

| Static pull-up/-down typ. (Ohm) <sup>(4)</sup>  | none              | none | 30k     | 30k  | 4k                 | 30k  | 30k                                | 30k             | 30k  |

| Schmitt trigger inputs                          | yes               | yes  | yes     | no   | yes                | no   | yes                                | yes             | no   |

| Additional functions                            |                   |      | Timer 0 |      | External interrupt |      | Port<br>monitor/<br>coded<br>reset | Port<br>monitor |      |

Notes:

- 1. Either "open drain down", "open drain up" or CMOS output configuration

- 2. This output must always be CMOS

- 3. The Dynamic pull-up/-down transistors are mask programmable and if programmed, are only activated when the associated complementary driver transistor is off. i.e.. A dynamic pull up transistor is only active when the port is either in input mode (both drivers off) or when a logical 1 is written to the port pad (low driver off) in output mode (Figure 3-3 on page 26)

- 4. The static pull-up/-down transistors are mask programmed and if programmed are always active independent of the port direction or driven state (Figure 3-3 on page 26)

For further data see section "DC Operating Characteristics".

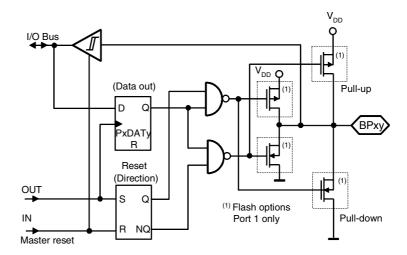

All Ports (0, 1, 4, 5, 7, A, B and C with the exception of Port 6) are 4 bits wide. Port 6 has a data width of only 2 bits (bit 0 and bit 1). The ports may be used for data input or output. All ports that can either directly or indirectly generate an interrupt are equipped with Schmitt trigger inputs. A variety of mask options are available such as open drain, open source and full complementary outputs as well as different types of pull-up and pull-down transistors. All Port Data Registers (PxDAT) are I/O mapped to the primary address register of the respective port address, and the Port Data Direction Register (PxDDR) to the corresponding auxiliary register.

All bi-directional ports except Port 0 and Port 1, include a bit wise programmable Data Direction Register (PxDDR) which allows the individual programming of each port bit as input or output. It is also possible to read the pin condition when in output mode. This is a useful feature for self-testing and for collision detection on wired-OR bus systems.

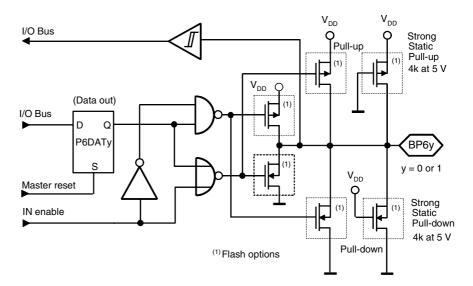

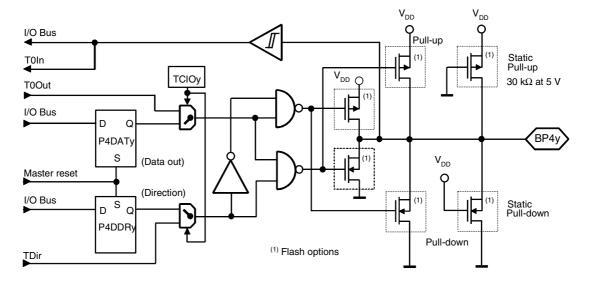

There are five different types of bi-directional ports:

- Ports 0 and 1: 4-bit wide, bi-directional ports with automatic full bus width direction switching

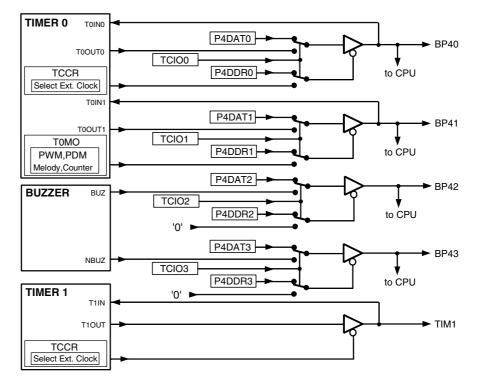

- Port 4: 4-bit wide, bit wise programmable bi-directional port also provides the I/O interface to Timer 0 and the Buzzer

- Ports 5, 7 and C: 4-bit wide, bit wise programmable high drive I/O ports

- Port 6: 2-bit wide, bit wise programmable bi-directional port with optional static (4 kΩ) pull-up/-down and programmable interrupt logic

- Ports A and B: 4-bit wide, bit wise programmable bi-directional ports with optional port monitor function

#### 3.2.1 Port Data Register (PxDAT)

Primary register address: 'Port address' hex

Bit 3

Bit 2

Bit 1

Bit 0

PxDAT

PxDAT3

PxDAT2

PxDAT1

PxDAT0

Reset value: 1111b

Bit 3 = MSB, Bit 0 = LSB, x = Port address

#### 3.2.2 Port Data Direction Register (PxDDR)

Auxiliary register address: 'Port address' hex

Bit 3

Bit 2

Bit 1

Bit 0

PxDDR

PxDDR3

PxDDR2

PxDDR1

PxDDR0

Reset value: 1111b

**Table 3-3.** Port Data Direction Register (PxDDR)

| Code: 3 2 1 0 | Function            |

|---------------|---------------------|

| x x x 1       | BPx0 in input mode  |

| x x x 0       | BPx0 in output mode |

| x x 1 x       | BPx1 in input mode  |

| x x 0 x       | BPx1 in output mode |

| x 1 x x       | BPx2 in input mode  |

| x 0 x x       | BPx2 in output mode |

| 1 x x x       | BPx3 in input mode  |

| 0 x x x       | BPx3 in output mode |

#### 3.2.3 Bi-directional Port 0 and Port 1

In this port type, the data direction register is not independently software programmable because the direction of the complete port is switched automatically when an I/O instruction occurs (see Figure 3-2 on page 26). The port can be switched to output mode with an OUT instruction and to input with an IN instruction. The data written to a port will be stored in the output data latches and appears immediately at the port pin following the OUT instruction. After RESET, all output latches are set to 1 and the ports are switched to input mode. An IN instruction reads the condition of the associated pins.

Note: Care must be taken when switching these bi-directional ports from output to input. The capacitive pin loading at this port, in conjunction with the high resistance pull-ups, may cause the CPU to read the contents of the output data register rather than the external input state. This can be avoided by using either of the following programming techniques:

Use two IN instructions and DROP the first data nibble. The first IN switches the port from output to input and the DROP removes the first invalid nibble. The second IN reads the valid pin state.

Use an OUT instruction followed by an IN instruction. With the OUT instruction, the capacitive load is charged or discharged depending on the optional pull-up /pull-down configuration. Write a 1 for pins with pull-up resistors, and a 0 for pins with pull-down resistors.

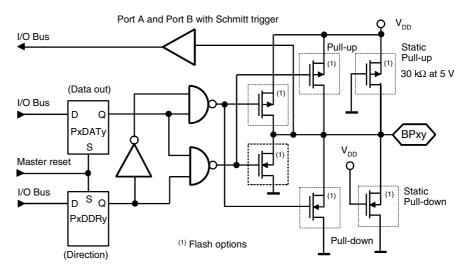

Figure 3-2. Bi-directional Port 0 and 1

#### 3.2.4 Bi-directional Port 5, Port 7 and Port C

All bi-directional ports except Port 0 and Port 1, include a bit wise programmable Data Direction Register (PxDDR) which allows the individual programming of each port bit as input or output. It also enables the reading of the pin condition in output mode.

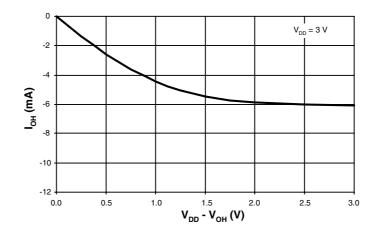

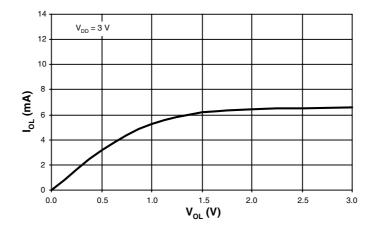

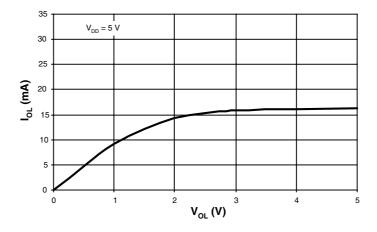

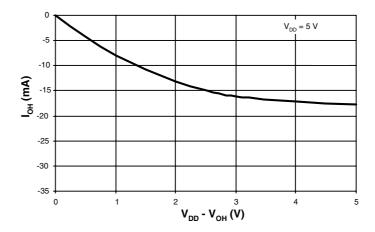

The bi-directional Ports 5, 7 and C as well as Port A and Port B are equipped with the same standard I/O logic. However, Port 5, Port 7 and Port C include standard CMOS input stages, whereas Port A, Port B and all other digital signal pins have Schmitt trigger inputs. Port 5 and Port 7 have high current output drive capability for up to 20 mA at 5 V. Whereby the instantaneous sum of the output currents should not exceed 100 mA.

Figure 3-3. Bi-directional Ports 5, 7, A, B and C

#### 3.2.5 Bi-directional Port A and Port B with Port Monitor Function

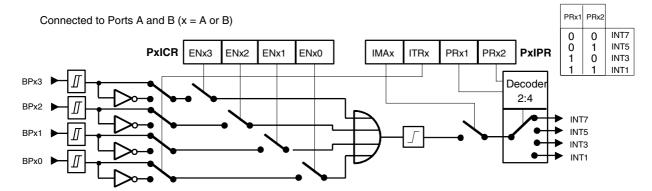

Figure 3-4. Port Monitor Module of Port A and Port B

In addition to the standard I/O functions described in section "Bi-directional Port 5, Port 7 and Port C", both Port A (BPA3 - BPA0) and Port B (BPB3 - BPB0) are equipped with Schmitt trigger inputs and a port monitor module. This module is connected across all four port pins (see Figure 3-4) and is intended for monitoring those pins selected by control bits Enx3 - Enx0 and generating an interrupt when the first pin leaves a preselected logical default idle state. This state is defined by control bit ITRx. Transitions on other pins will only cause an interrupt if the other pins have first returned to the idle state. This, for example is useful for interrupt initiated port scanning without the power consuming task of continuously polling for port activity.

Using the Port Interrupt Control Register (PxICR), pins can be individually selected. A non-selected pin cannot generate an interrupt. The Port Interrupt Priority Register (PxIPR) allows masking of each interrupt, definition of the interrupt edge and programming of the interrupt priority levels. When programming or reprogramming either of the port monitor control registers, any previously generated interrupt on that port which has not yet been acknowledged by the CPU or an interrupt generated by the reprogramming itself is automatically cleared. Port A can also be used for a mask programmable coded reset. For more information see section "Hardware Reset".

The Port Interrupt Priority Registers PAIPR and PBIPR are I/O mapped to the primary address registers of the Port Monitor Module addresses '2'h and '3'h respectively. The Port Interrupt Control Registers PAICR and PBICR are mapped to the corresponding auxiliary registers.

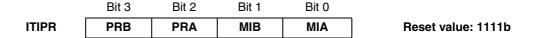

#### 3.2.5.1 Port Monitor Interrupt Priority Register (PxIPR)

x = 'A' (Port A) or 'B' (Port B) (Port A) Primary register address: '2'hex (Port B) Primary register address: '3'hex

|       | Bit 3 | Bit 2 | Bit 1 | Bit 0 |                    |

|-------|-------|-------|-------|-------|--------------------|

| PxIPR | IMx   | ITRx  | PRx2  | PRx1  | Reset value: 1111b |

IMx Interrupt Mask

ITRx Interrupt Transition

PRx2..1 Interrupt Priority code

**Table 3-4.** Port Monitor Interrupt Priority Register (PxIPR)

| Code<br>3 2 1 0 | Function                               |  |  |

|-----------------|----------------------------------------|--|--|

| x x 0 0         | Port monitor interrupt priority 7      |  |  |

| x x 0 1         | Port monitor interrupt priority 5      |  |  |

| x x 1 0         | Port monitor interrupt priority 3      |  |  |

| x x 1 1         | Port monitor interrupt priority 1      |  |  |

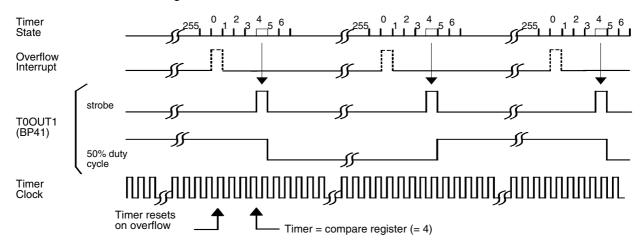

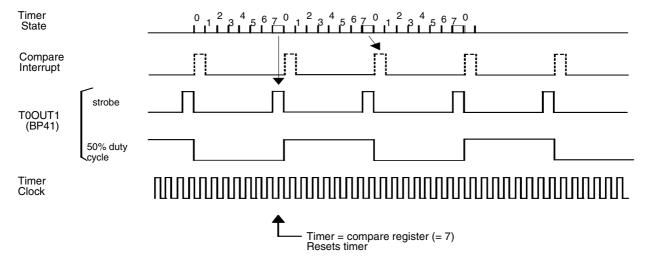

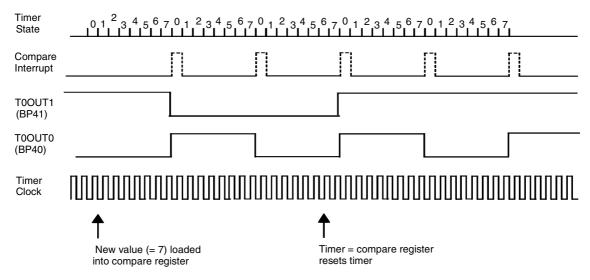

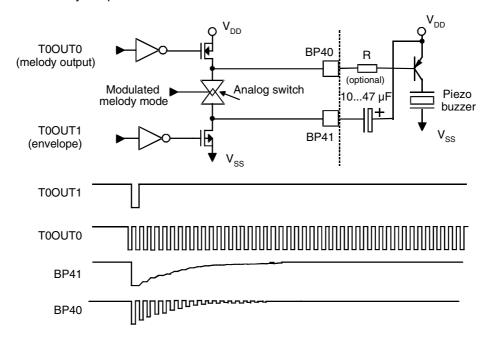

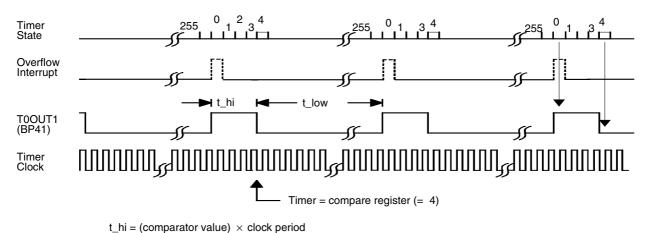

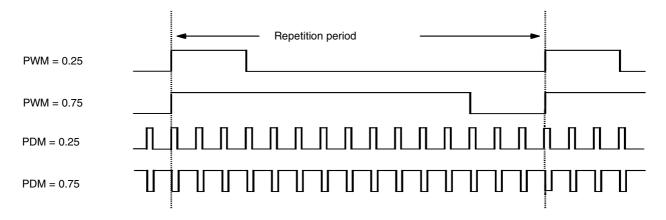

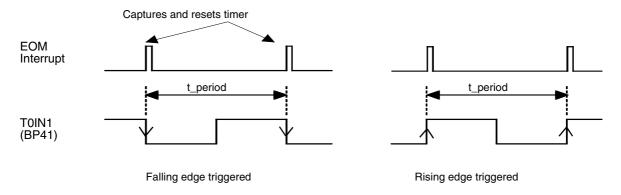

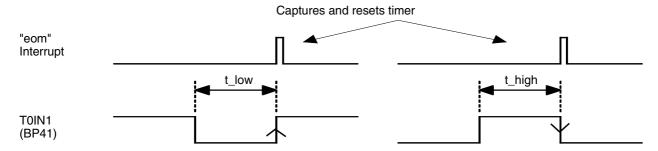

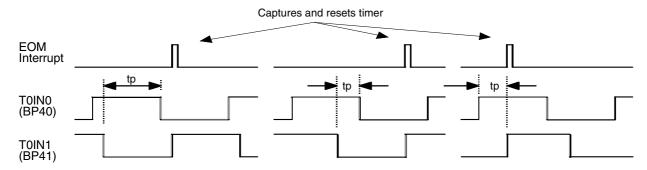

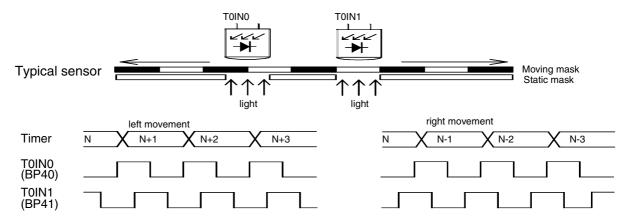

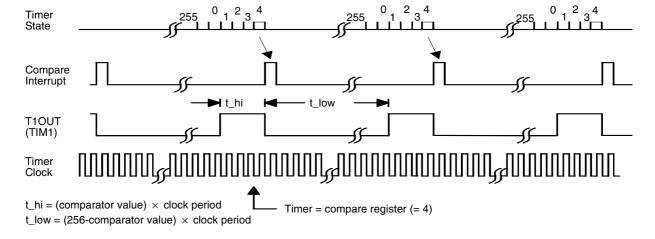

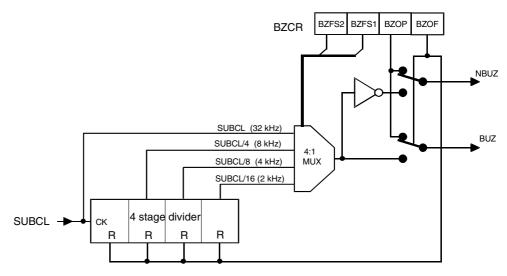

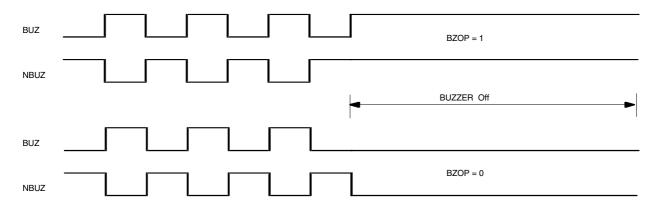

| x 0 x x         | Port monitor interrupt on falling edge |  |  |