### POCSAG MICROCONTROLLER

#### **GENERAL DESCRIPTION**

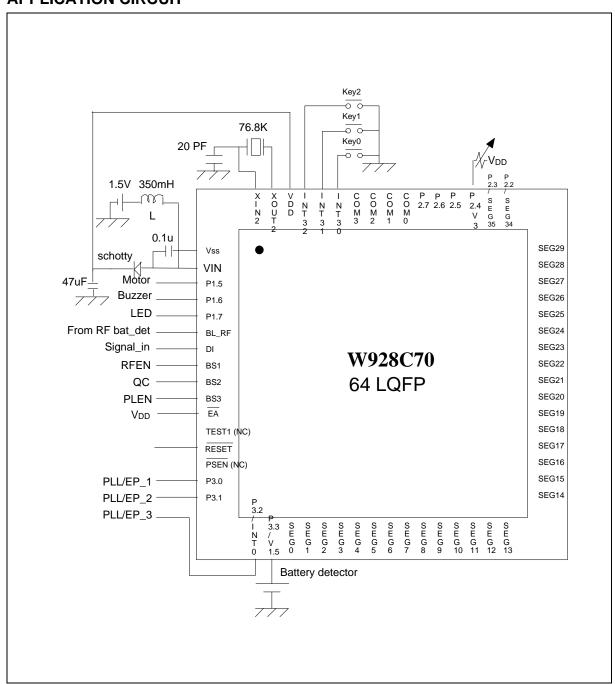

The W928C70 is a high performance 8 bits microcontroller with build-in POCSAG decoder and LCD driver. It is possible to switch the normal mode, idle mode and power down mode for power saving purpose. The W928C70 is an extended  $\mu$ C from standard 8031 (excluding UART) that it can be easily applied to pager system or other telecommunication system.

#### **FEATURES**

- 512, 1200 and 2400 bps POCSAG decoder

- 6 independent user addresses

- Instruction set compatible with MCS51

- System clock

- OSC2: 76.8 KHz

- 238 bytes on-chip fast RAM

- 384 bytes on-chip MOVX RAM

- 16K bytes on-chip program ROM

- Timer

- Two 16-bit timer

- One RTC timer

- One Watch-dog timer

- One Buzzer timer

- Four 8-bit bit-addressable I/O ports

- Three external interrupt source, INTO, INT1 (BAT DET INT), INT3 (KEY INT)

- · Battery low detector

- · Battery detector

- Power fail detector

- Build in dc/dc converter

- · Power down wake-up via external interrupts

- Two 16-bit Data Pointers (Selected by DPS.0)

- 10 source, 10 vector interrupts structure with two priority-level interrupts

- Built-in programmable power-saving modes Idle mode & Power-down mode

- Operating voltage range: 2.4V to 3.3V

- 32 segment × 4 common, 1/3 bias, 1/4 duty LCD driver output

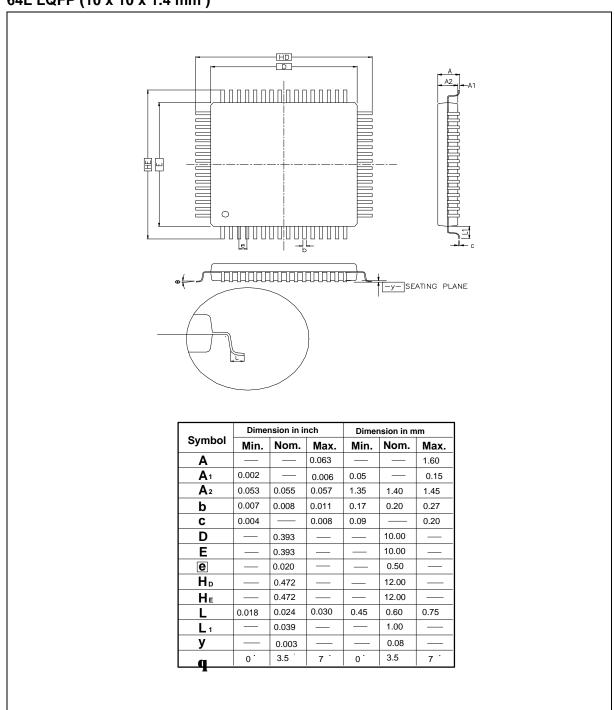

- Packaged in 64-pin LQFP

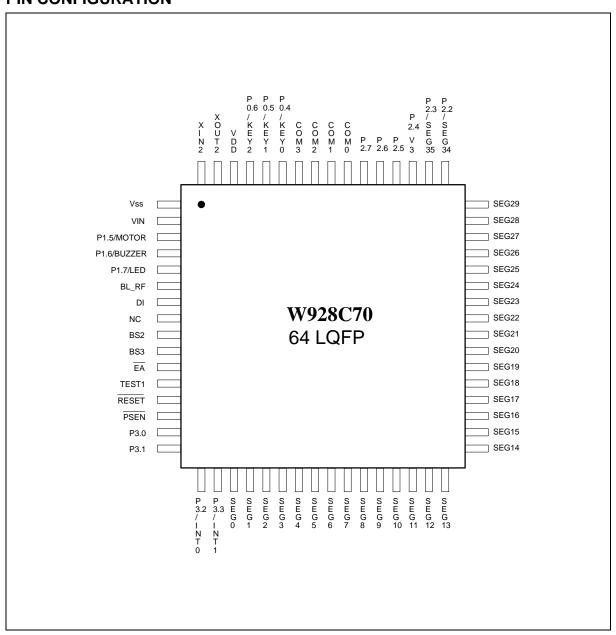

#### **PIN CONFIGURATION**

### **PIN DESCRIPTIONS**

| SYMBOL    | TYPE | DESCRIPTIONS                                                                                                                               |  |  |  |  |  |  |  |

|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Vss       | I    | GROUND: ground potential                                                                                                                   |  |  |  |  |  |  |  |

| RST       | ΙΗ   | RESET: A low on this pin for two machine cycles while the oscillator is running resets the device.                                         |  |  |  |  |  |  |  |

| P1.5      | 0    | Motor output, hi-drive                                                                                                                     |  |  |  |  |  |  |  |

| P1.6      | 0    | Buzzer clock output, hi-drive                                                                                                              |  |  |  |  |  |  |  |

| P1.7      | 0    | LED output, hi-drive                                                                                                                       |  |  |  |  |  |  |  |

| BL_RF     | I    | Connect to LVS of IF chip                                                                                                                  |  |  |  |  |  |  |  |

| DI        | I    | POCSAG signal input                                                                                                                        |  |  |  |  |  |  |  |

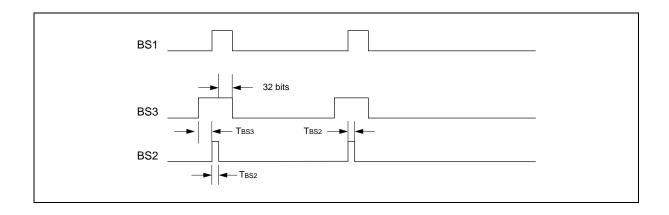

| BS1       | 0    | RF control 1                                                                                                                               |  |  |  |  |  |  |  |

| BS2       | 0    | RF control 2                                                                                                                               |  |  |  |  |  |  |  |

| BS3       | 0    | RF control 3                                                                                                                               |  |  |  |  |  |  |  |

| ĒĀ        | I    | External access enable pin. Should connect to VDD.                                                                                         |  |  |  |  |  |  |  |

| TEST1     |      | No connection. Test pin. Internal pull low                                                                                                 |  |  |  |  |  |  |  |

| VIN       | I    | DC converter battery input pin                                                                                                             |  |  |  |  |  |  |  |

| PSEN      | 0    | No connection. Test pin.                                                                                                                   |  |  |  |  |  |  |  |

| P3.0      | I/O  | Bit addressable general I/O port 3.0                                                                                                       |  |  |  |  |  |  |  |

| P3.1      | I/O  | Bit addressable general I/O port 3.1                                                                                                       |  |  |  |  |  |  |  |

| P3.2/INT0 | I/O  | Bit addressable general I/O port 3.2 or INT0 defined by SFR                                                                                |  |  |  |  |  |  |  |

| P3.3/INT1 | I    | Battery fail interrupt input. Connect to V1.5. If voltage potential of battery is less than the 0.8V, the INT1 interrupt flag will be set. |  |  |  |  |  |  |  |

| SEG0      | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

| SEG1      | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

| SEG2      | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

| SEG3      | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

| SEG4      | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

| SEG5      | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

| SEG6      | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

| SEG7      | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

| SEG8      | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

| SEG9      | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

| SEG10     | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

| SEG11     | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

| SEG12     | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

| SEG13     | 0    | LCD segment signal out                                                                                                                     |  |  |  |  |  |  |  |

Pin Descriptions, continued

| SYMBOL     | TYPE | DESCRIPTIONS                                             |  |  |  |  |  |  |  |

|------------|------|----------------------------------------------------------|--|--|--|--|--|--|--|

| SEG14      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG15      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG16      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG17      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG18      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG19      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG20      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG21      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG22      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG23      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG24      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG25      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG26      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG27      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG28      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| SEG29      | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| P2.2/SEG34 | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| P2.3/SEG35 | 0    | LCD segment signal out                                   |  |  |  |  |  |  |  |

| P2.4/VDD   | I    | LCD voltage input (VDD)                                  |  |  |  |  |  |  |  |

| P2.5       | I/O  | I/O pin                                                  |  |  |  |  |  |  |  |

| P2.6       | I/O  | I/O pin                                                  |  |  |  |  |  |  |  |

| P2.7       | I/O  | I/O pin                                                  |  |  |  |  |  |  |  |

| COM0       | 0    | LCD common signal output pins.                           |  |  |  |  |  |  |  |

| COM1       | 0    | LCD common signal output pins.                           |  |  |  |  |  |  |  |

| COM2       | 0    | LCD common signal output pins.                           |  |  |  |  |  |  |  |

| COM3       | 0    | LCD common signal output pins.                           |  |  |  |  |  |  |  |

| P0.4       | I    | Bit addressable general I/O port 0.4 and Key_0 interrupt |  |  |  |  |  |  |  |

| P0.5       | I    | Bit addressable general I/O port 0.5 and Key_1 interrupt |  |  |  |  |  |  |  |

| P0.6       | I    | Bit addressable general I/O port 0.6 and Key_2 interrupt |  |  |  |  |  |  |  |

| VDD        | I    | POWER SUPPLY: Supply voltage for operation.              |  |  |  |  |  |  |  |

| XOUT2      | 0    | Output pin for clock_2. It is the inversion of XIN2.     |  |  |  |  |  |  |  |

| XIN2       | I    | Input pin for clock_2                                    |  |  |  |  |  |  |  |

Note 1: I/O TYPE I: input, O: output, I/O: bi-directional, H: pull-high, L: pull-low, D: open drain

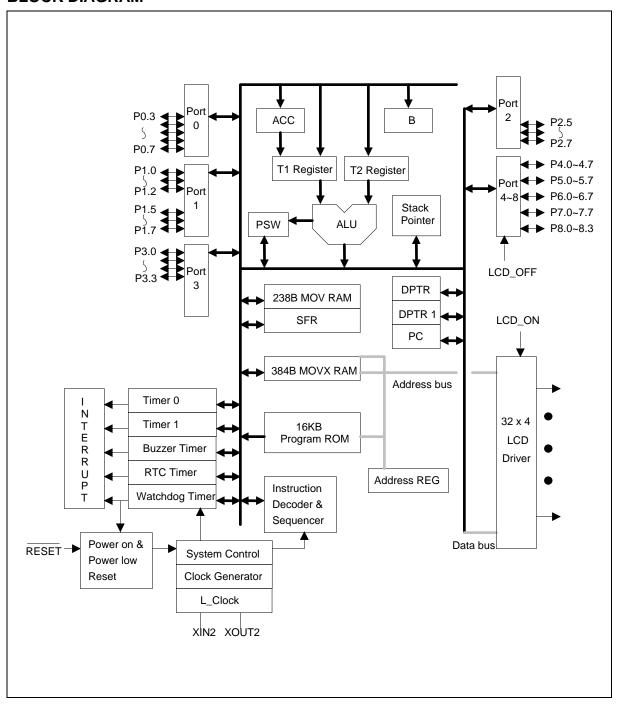

#### **BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

The W928C70 is a high performance 8 bits POCSAG microcontroller with build-in LCD driver and POCSAG decoder. The  $\mu$ C is 8031 instruction set compatible with one addition: DEC DPTR (op-code A5H, the DPTR is decreased by 1). The W928C70 has all the standard features of the 8031 except the UART, and has a few extra peripherals and features like watchdog, RTC, buzzer timers, LCD driver, and build-in POCSAG decoder.

The W928C70 features a faster running and better performance 8-bit CPU by reducing the machine cycle duration from the standard 8031 period of twelve clocks to four clock cycles for the majority of instructions. The W928C70 also provides dual Data Pointers (DPTRs) to speed up block data memory transfers. In addition, the W928C70 contains on-chip 384B MOVX SRAM. It only can be accessed by MOVX instruction; this on-chip data memory can be enabled by software commend.

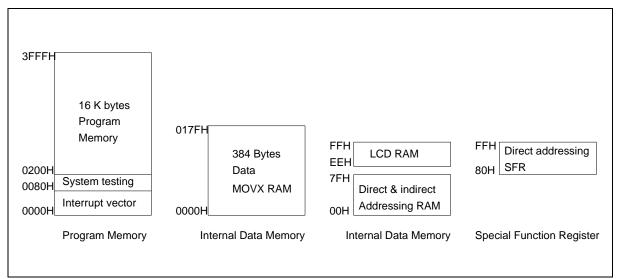

#### **Memory Organization**

The W928C70 separates the memory into two sections, the Program Memory and Data Memory. The Program Memory is used to store the instruction op-codes, while the Data Memory is used for storing data or memory mapped devices. The  $\overline{\mathsf{EA}}$  pin must connect to high to access on-chip program ROM.

On-chip memory space of W928C70

#### Stack

The scratch-pad RAM can be used for the stack. This area is selected by the Stack Pointer (SP), which stores the address of the top of the stack. Whenever a jump, call or interrupt is invoked the return address is placed on the stack. There is no restriction as to where the stack can begin in the RAM. By default however, the Stack Pointer contains 07H at reset. The user can then change this to any value desired. The SP will point to the last used value. Therefore, the SP will be incremented and then address saved onto the stack. Conversely, while popping from the stack the contents will be read first, then the SP is decreased.

#### **LCD Data Area**

When LCD ON, the indirect RAM area EEH-FFH work as the LCD data RAM (LCD00-LCD35). Instruction such as "MOV @R0, #I" (Where R0 = EEH-FFH) are used to control the LCD data RAM. The data in the LCD data RAM (bit7-bit0) are transferred to the segment output pins automatically without program control. When the bit value of the LCD data RAM is "1", the LCD is turned on. When the bit value of the LCD data RAM is "0", LCD is turned off. The relation between the LCD data RAM and segment/common pins is shows below.

| LCD      | СОМЗ  | COM2  | COM1       | COM0  | СОМЗ  | COM2  | COM1       | COM0  |  |

|----------|-------|-------|------------|-------|-------|-------|------------|-------|--|

| Data RAM | BIT 7 | BIT 6 | BIT 5      | BIT 4 | BIT 3 | BIT 2 | BIT 1      | BIT 0 |  |

| EEH      |       | SEC   | 31         |       |       | SEC   | <b>3</b> 0 |       |  |

| EFH      |       | SEC   | 33         |       |       | SEC   | <b>3</b> 2 |       |  |

| F0H      |       | SEC   | <b>3</b> 5 |       |       | SEC   | <b>3</b> 4 |       |  |

| F1H      |       | SEC   | 37         |       |       | SEC   | <b>3</b> 6 |       |  |

| F2H      |       | SEC   | 39         |       |       | SE    | <b>3</b> 8 |       |  |

| F3H      |       | SEG   | 611        |       | SEG10 |       |            |       |  |

| F4H      |       | SEG   | 13         |       | SEG12 |       |            |       |  |

| F5H      |       | SEG   | 15         |       | SEG14 |       |            |       |  |

| F6H      |       | SEG   | 617        |       | SEG16 |       |            |       |  |

| F7H      |       | SEG   | 19         |       | SEG18 |       |            |       |  |

| F8H      |       | SEG   | 21         |       | SEG20 |       |            |       |  |

| F9H      |       | SEG   | 23         |       | SEG22 |       |            |       |  |

| FAH      |       | SEG   | 25         |       | SEG24 |       |            |       |  |

| FBH      |       | SEG   | 627        |       | SEG26 |       |            |       |  |

| FCH      |       | SEG   | 29         |       | SEG28 |       |            |       |  |

| FFH      |       | SEG   | 35         |       | SEG34 |       |            |       |  |

### **Descriptions Of Special Function Registers (SFRS)**

| ADDRESS<br>/NAME | BIT  | BIT NAME          | R/W | 1         | 0         | INITIAL  | FUNCTION                                                                                                                                                               |

|------------------|------|-------------------|-----|-----------|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80H/P0           | В7   |                   | R   |           |           | 1        | No use                                                                                                                                                                 |

|                  | В6   | Key_2             | R   |           |           | 1        | Key_2 input. A corresponding key_INT (INT3_3) can be enabled.                                                                                                          |

|                  | B5   | Key_1             | R   |           |           | 1        | Key_1 input. A corresponding key_INT (INT3_3) can be enabled.                                                                                                          |

|                  | B4   | Key_0             | R   |           |           | 1        | Key_0 input. A corresponding key_ INT (INT3_3) can be enabled.                                                                                                         |

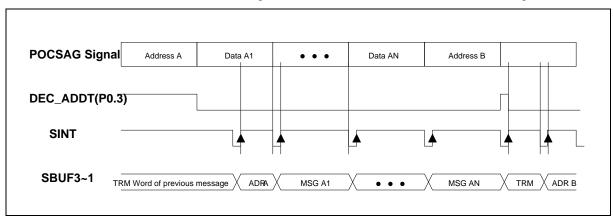

|                  | В3   | DEC_ADDT          | R   | Matched   | Unmatched | 1        | POCSAG address matched flag. A corresponding INT (INT2) could be setup.                                                                                                |

|                  | B2   |                   | W   |           |           | 1        | No use                                                                                                                                                                 |

|                  | B1   | DEC_<br>SYNVAL    | R   | SYNC      | Lost SYNC | 1        | Decoder synchronization condition                                                                                                                                      |

|                  | В0   |                   | R/W |           |           | 1        | No use                                                                                                                                                                 |

| 81H/SP           | B7~0 | SP                | R/W |           |           | 00000111 | Stack pointer address. Always points to top of the stack.                                                                                                              |

| 82H/DPL          | B7~0 | DPL               | R/W |           |           | 00000000 | Low byte of 16 bit data pointer                                                                                                                                        |

| 83H/DPH          | B7~0 | DPH               | R/W |           |           | 00000000 | High byte of 16 bit data pointer                                                                                                                                       |

| 84H/DPL1         | B7~0 | DPL1              | R/W |           |           | 00000000 | Low byte of 16 bit data pointer 1                                                                                                                                      |

| 85H/DPH1         | B7~0 | DPH1              | R/W |           |           | 00000000 | High byte of 16 bit data pointer 1                                                                                                                                     |

| 86H/DPS          | В0   | DPS.0             | R/W | Pointer 1 | Pointer 0 | 0        | Selection of data pointer, B7~1 are not used                                                                                                                           |

| 87H/PCON         | В7   | SMOD              |     |           |           | 0        | No use. Clear to "o" after power_on reset                                                                                                                              |

|                  | B6   | SMOD0             |     |           |           | 0        | No use. Clear to "o" after power_on reset                                                                                                                              |

|                  | B5   | -                 |     |           |           | 0        | No use. Clear to "o" after power_on reset                                                                                                                              |

|                  | B4   | -                 |     |           |           | 0        | No use. Clear to "o" after power_on reset                                                                                                                              |

|                  | В3   | GF1               |     |           |           | 0        | General purpose user defined flag                                                                                                                                      |

|                  | B2   | GF0               |     | Enable    | Disable   | 0        | GF0=0 disable DC converter.                                                                                                                                            |

|                  |      |                   |     |           |           |          | GF0=1 enable DC converter.                                                                                                                                             |

|                  | B1   | PD                | W   | Enable    | Disable   | 0        | Power down mode enable bit. Set this bit to "1" will stop the CPU and oscillation.                                                                                     |

|                  | В0   | IDL               | W   | Enable    | Disable   | 0        | Idle mode enable bit. Set this bit to "1" will stop the CPU clock, but the oscillator keep running.                                                                    |

| 88H/TCON         | В7   | TF1               | R/W | Overflow  |           | 0        | Timer 1 overflow flag,. TF1 will automatically clear after INT service routine.                                                                                        |

|                  | В6   | TR1               | W   | Enable    | Disable   | 0        | Timer 1 enable                                                                                                                                                         |

|                  | B5   | TF0               | R/W | Overflow  |           | 0        | Timer 0 overflow flag, TF0 will automatically clear after INT service routine                                                                                          |

|                  | B4   | TR0               | R/W | Enable    | Disable   | 0        | Timer 0 enable                                                                                                                                                         |

|                  | В3   | IE1<br>(Bat_fail) | R/W | INT       | No INT    | 0        | Interrupt 1(battery fail INT) flag. Set by hardware when a pre-selected INT level (high or low) is detected on INT1. The INT flag will keep only if the level is held. |

| ADDRESS<br>/NAME | BIT  | BIT NAME | R/W    | 1               | 0         | INITIAL  | FUNCTION                                                                                                                                                                                                                         |  |

|------------------|------|----------|--------|-----------------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                  | B2   | IT1      | R/W    | High level      | Low level | 0        | Interrupt 1 level selection. Set by software to specify high (>0.8V) / low (<0.8V) level external INT 1 triggered.                                                                                                               |  |

|                  | B1   | IEO      | R/W    | INT             | No INT    | 0        | Interrupt 0 edge detect: Set by hardware when an edge/level is detected on INT0. This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise it follows the pin. |  |

|                  | В0   | IT0      | R/W    | Falling<br>edge | Low level | 0        | Interrupt 0 type selection. Set/cleared by software to specify falling edge/ low level triggered external inputs                                                                                                                 |  |

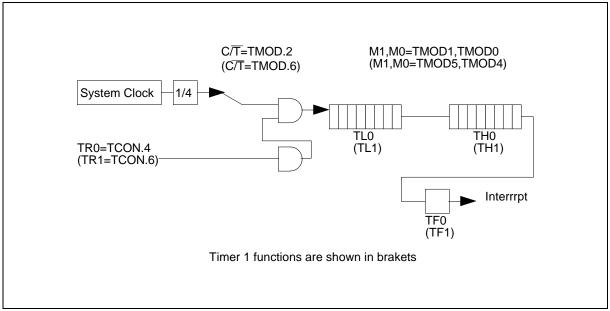

| 89H/TMOD         | B7   | T1_GATE  | R/W    |                 |           | 0        | Timer 1 & timer 0 control:                                                                                                                                                                                                       |  |

|                  |      |          |        |                 |           |          | Tx_GATE (gating control):                                                                                                                                                                                                        |  |

|                  | В6   | T1_T     | R/W    |                 | Timer     | 0        | When this bit is set, Timer/counter x will be enabled if both INTx pin is high and TRx control bit is set.                                                                                                                       |  |

|                  | B5   | T1_M1    | R/W    |                 |           | 0        | When this bit is cleared, Timerx is enabled whenever TRx control bit is set.                                                                                                                                                     |  |

|                  | B4   | T1_M0    | R/W    |                 |           | 0        | Tx_C/T (timer or counter select):                                                                                                                                                                                                |  |

|                  |      | _        |        |                 |           |          | When cleared, the timer is incremented by internal clocks.                                                                                                                                                                       |  |

|                  | В3   | T0_GATE  | R/W    |                 |           | 0        | When set, the timer counts high-to-low edges of the Tx pin.                                                                                                                                                                      |  |

|                  | B2   | T0_T     | R/W    |                 | Timer     | 0        |                                                                                                                                                                                                                                  |  |

|                  |      |          |        |                 |           |          | M1 M0 Mode                                                                                                                                                                                                                       |  |

|                  | B1   | T0_M1    | R/W    |                 |           | 0        | 0 0 8-bits with 5-bit pre-scalar.                                                                                                                                                                                                |  |

|                  | ы    | 10_1011  | 17,44  |                 |           |          | <ul><li>1 16-bits, no pre-scalar.</li><li>0 8-bits with auto-reload from THx</li></ul>                                                                                                                                           |  |

|                  | В0   | T0_M0    | R/W    |                 |           | 0        | 1 1 (Timer 0) TL0 is an 8-bit timer/counter controlled by the standard                                                                                                                                                           |  |

|                  |      |          |        |                 |           |          | Timer 0 control bits. TH0 is an 8-bit timer only controlled by Timer 1 control bits. (Timer 1) Timer/counter is stopped.                                                                                                         |  |

| 8AH/TL0          | B7~0 | TL0      | R/W    |                 |           | 00000000 | Low byte of timer 0                                                                                                                                                                                                              |  |

| 8BH/TL1          | B7~0 | TL1      | R/W    |                 |           | 00000000 | Low byte of timer 1                                                                                                                                                                                                              |  |

| 8CH/TH0          | B7~0 | TH0      | R/W    |                 |           | 00000000 | High byte of timer 0                                                                                                                                                                                                             |  |

| 8DH/TH1          | B7~0 | TH1      | R/W    |                 |           | 00000000 | High byte of timer 1                                                                                                                                                                                                             |  |

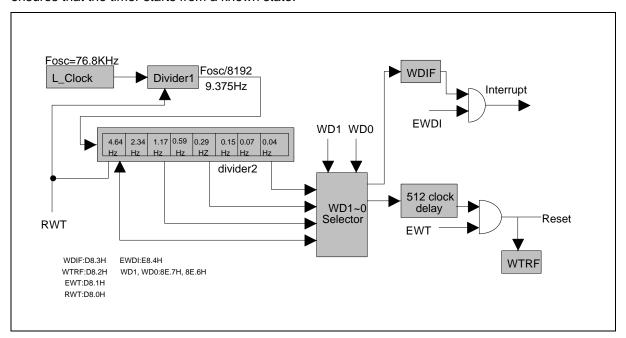

| 8EH/CKCON        | В7   | WD1      | R/W    |                 |           | 0        | WD1 WD0 (watchdog timeout period)                                                                                                                                                                                                |  |

|                  |      |          |        |                 |           |          | 0 0 Fs/2 <sup>14</sup> +512 clock                                                                                                                                                                                                |  |

|                  | В6   | WD0      | R/W    |                 |           | 0        | 0 1 Fs/2 <sup>16</sup> +512 clock<br>1 0 Fs/2 <sup>18</sup> +512 clock                                                                                                                                                           |  |

|                  |      |          |        |                 |           |          | 1 1 Fs/2 <sup>21</sup> +512 clock                                                                                                                                                                                                |  |

|                  | B5   | RTC1     | R/W    |                 |           | 0        | RTC1 RTC0 (RTC timeout period)                                                                                                                                                                                                   |  |

|                  | -    |          |        |                 |           |          | 0 0 32 Hz for RTLCD = 74                                                                                                                                                                                                         |  |

|                  | D.1  | 5700     | D // / |                 |           |          | 0 1 8 Hz                                                                                                                                                                                                                         |  |

|                  | B4   | RTC0     | R/W    |                 |           | 0        | 1 0 2 Hz                                                                                                                                                                                                                         |  |

|                  |      |          |        | 1               |           |          | 1 1 Hz                                                                                                                                                                                                                           |  |

| ADDRESS<br>/NAME | BIT  | BIT NAME     | R/W | 1      | 0       | INITIAL  | FUNCTION                                                                                                         |

|------------------|------|--------------|-----|--------|---------|----------|------------------------------------------------------------------------------------------------------------------|

|                  | В3   | -            | R/W |        |         | 1        | Set B3 and B2 to 1 after power on reset.                                                                         |

|                  | B2   | -            | R/W |        |         | 1        | ]                                                                                                                |

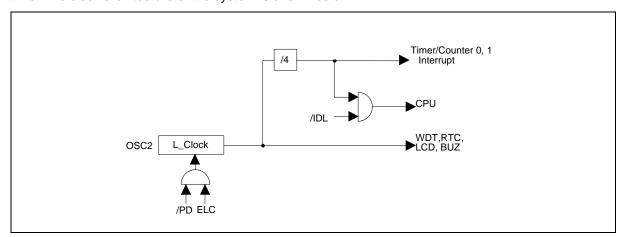

|                  | B1   | ELC          | R/W | Enable | Disable | 1        | ELC: enable L_clock.                                                                                             |

|                  |      |              |     |        |         |          | Keep this bit high for whole operation.                                                                          |

|                  | В0   | EHC          | R/W |        |         | 0        | Clear to "0" after reset.                                                                                        |

| 90H/P1           | В7   | LED          | W   | High   | Low     | 1        | LED output port P1.7 (HI-drive)                                                                                  |

|                  | В6   | Buz_out      | W   | High   | Low     | 1        | Initial value of buzzer output pin                                                                               |

|                  | B5   | Motor        | W   | High   | Low     | 1        | Motor output pin(Hi-drive)                                                                                       |

|                  | B4   |              | W   |        |         | 1        | No use                                                                                                           |

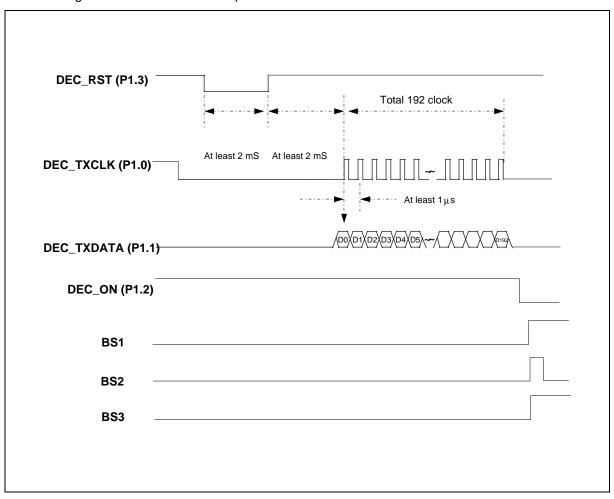

|                  | В3   | DEC_RST      | W   | High   | Low     | 1        | Decoder reset control bit                                                                                        |

|                  | B2   | DEC_ON       | W   | High   | Low     | 1        | Decoder enable control bit                                                                                       |

|                  | B1   | DEC_<br>DATA | W   | High   | Low     | 1        | Decoder option setup data output control bit                                                                     |

|                  | В0   | DEC_CLK      | W   | High   | Low     | 1        | Decoder option setup clock output control bit                                                                    |

| 91H/PBCON        | В7   | -            | W   |        |         | 0        | Clear B7~B2 to 0 after power on reset.                                                                           |

|                  | В6   | -            | W   |        |         | 0        | ]                                                                                                                |

|                  | B5   | -            | W   |        |         | 0        | ]                                                                                                                |

|                  | В4   | -            | W   |        |         | 0        | ]                                                                                                                |

|                  | В3   | -            | W   |        |         | 0        | ]                                                                                                                |

|                  | B2   | -            | W   |        |         | 0        |                                                                                                                  |

|                  | B1   | ENBT         | W   | Enable | Disable | 0        | Buzzer timer enable (used as a general timer)                                                                    |

|                  | В0   | ENBUZ        | W   | Enable | Disable | 0        | Buzzer output enable                                                                                             |

| 92H/TONE0        | B7~0 | TONE0        | W   |        |         | 00000000 | Auto reload value of buzzer timer                                                                                |

| 96H/PLC          | B7~0 | PLC          | R   |        |         | 00000000 | Low byte of program counter                                                                                      |

| 97H/PLH          | B7~0 | PLH          | R   |        |         | 00000000 | High byte of program counter                                                                                     |

| A0H/P2           | В7   | P2.7         | W/R | High   | Low     | 1        | I/O P2.7                                                                                                         |

|                  | В6   | P2.6         | W/R |        |         | 1        | B6~B4 no use when LCD is on.                                                                                     |

|                  | B5   | P2.5         | W/R |        |         | 1        |                                                                                                                  |

|                  | B4   | P2.4         | W/R |        |         | 1        |                                                                                                                  |

|                  | В3   | P2.3         | W/R | High   | Low     | 1        | No use if SEG35~32 work as LCD segment.                                                                          |

|                  |      |              |     |        |         |          | I/O P2.3 value if SEG35~32 work as<br>P2.3~P2.0 function (P2M (A1.1H) = 0)                                       |

|                  | B2   | P2.2         | W/R | High   | Low     | 1        | I/O P2.2 value if SEG35~32 work as<br>P2.3~P2.0 function (P2M (A1.1H) = 0)                                       |

|                  | B1   | P2.1         | W/R | High   | Low     | 1        | No use if SEG35~32 work as LCD segment.  I/O P2.1 value if SEG35~32 work as P2.3~P2.0 function (P2M (A1.1H) = 0) |

| ADDRESS<br>/NAME | BIT  | BIT NAME | R/W | 1       | 0       | INITIAL  | FUNCTION                                                                                                                                                                                    |  |  |

|------------------|------|----------|-----|---------|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                  | В0   | P2.0     | W/R | High    | Low     | 1        | No use if SEG35~32 work as LCD segment.                                                                                                                                                     |  |  |

|                  |      |          |     |         |         |          | I/O P2.0 value if SEG35~32 work as<br>P2.3~P2.0 function (P2M (A1.1H) = 0)                                                                                                                  |  |  |

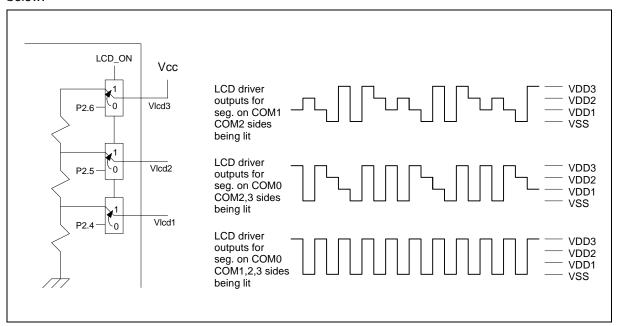

| A1H/LCDR         | В7   | LCDWAVE  | W   | A Type  | В Туре  | 0        | Clear B7~B4 to "0" after reset.                                                                                                                                                             |  |  |

|                  | В6   | -        | W   |         |         | 0        | Default LCDWAVE = 0 (B type)                                                                                                                                                                |  |  |

|                  | B5   | -        | W   |         |         | 0        |                                                                                                                                                                                             |  |  |

|                  | В4   | -        | W   |         |         | 0        |                                                                                                                                                                                             |  |  |

|                  | В3   | FLCD1    | W   |         |         | 0        | FLCD1 FLCD0 LCD frequency 0 0 512 Hz, set RTLCD = 74                                                                                                                                        |  |  |

|                  | B2   | FLCD0    | W   |         |         | 0        | 0 1 256 Hz<br>1 0 128 Hz<br>1 1 64 Hz<br>LCD scan rate = LCD frequency/ 4                                                                                                                   |  |  |

|                  | B1   | P2M      | W   | SEG out | P2      | 0        | P2.0~2.3/SEG32~35 pin function selection This bit can only be set while LCD is on.  While set to 1, these 4 pins work as SEG32~35 output. If clear to 0, these 4 pin will work as P2.0~2.3. |  |  |

|                  | В0   | LCDON    | W   | LCD ON  | LCD OFF | 0        | LCD driver enable control                                                                                                                                                                   |  |  |

| A2H/RTLCD        | B7~0 | RTLCD    | W   |         |         | 11111111 | RTC timer value. Set RTLCD = 74 for 76.8 KHz crystal                                                                                                                                        |  |  |

| A8H/IE           | В7   | EA       | W   | Enable  | Disable | 0        | Global interrupt enable control                                                                                                                                                             |  |  |

|                  | В6   | ES1      | W   | Enable  | Disable | 0        | POCSAG receiving buffer interrupt enable control                                                                                                                                            |  |  |

|                  | B5   | -        | W   |         |         | 0        | Clear this bit to 0 after power on reset                                                                                                                                                    |  |  |

|                  | B4   | -        | W   |         |         | 0        | Clear this bit to 0 after power on reset                                                                                                                                                    |  |  |

|                  | В3   | ET1      | W   | Enable  | Disable | 0        | Timer 1 interrupt enable control                                                                                                                                                            |  |  |

|                  | B2   | EX1      | W   | Enable  | Disable | 0        | External interrupt 1 (battery fail INT) enable control                                                                                                                                      |  |  |

|                  | B1   | ET0      | W   | Enable  | Disable | 0        | Timer 0 interrupt enable control                                                                                                                                                            |  |  |

|                  | B0   | EX0      | W   | Enable  | Disable | 0        | External interrupt 0 enable control                                                                                                                                                         |  |  |

| AAH/SDTMF        | B7   | INT33    | W   | Enable  | Disable | 0        | Clear this bit to 0 after reset                                                                                                                                                             |  |  |

|                  | B6   | INT32    | W   | Enable  | Disable | 0        | Enable INT32 (key2)                                                                                                                                                                         |  |  |

|                  | B5   | INT31    | W   | Enable  | Disable | 0        | Enable INT31 (key1)                                                                                                                                                                         |  |  |

|                  | B4   | INT30    | W   | Enable  | Disable | 0        | Enable INT30 (key0)                                                                                                                                                                         |  |  |

|                  | В3   | -        | W   |         |         | 0        | Clear B3~B0 after reset                                                                                                                                                                     |  |  |

|                  | B2   | -        | W   |         |         | 0        |                                                                                                                                                                                             |  |  |

|                  | B1   | -        | W   |         |         | 0        |                                                                                                                                                                                             |  |  |

|                  | В0   | -        | W   |         |         | 0        |                                                                                                                                                                                             |  |  |

| ADDRESS<br>/NAME | BIT  | BIT NAME          | R/W | 1              | 0                                | INITIAL  | FUNCTION                                                                                                                                                                                |

|------------------|------|-------------------|-----|----------------|----------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B0H/P3           | В7   | DEC_BL            | R   | Battery<br>low | Battery<br>OK                    | 1        | Battery condition.  If battery voltage is lower than 1 volt, this bit will change to 1, otherwise this bit will be 0.  This bit works only if BL_RF pin is connect to IF IC LVS output. |

|                  | B6   |                   | W   | High           | Low                              | 1        | No use                                                                                                                                                                                  |

|                  | B5   |                   | W   | High           | Low                              | 1        | No use                                                                                                                                                                                  |

|                  | B4   |                   | W   | High           | Low                              | 1        | No use                                                                                                                                                                                  |

|                  | B3   | Bat_fail/<br>INT1 | R   | Battery<br>OK  | Battery<br>fail or no<br>battery | 1        | Battery fail condition.  If battery voltage is lower than 0.8 volt, this bit will change to 0, otherwise this bit will be 1.  An additional level interrupt(INT1) can be                |

|                  |      |                   |     |                |                                  |          | enabled to monitor this bit.                                                                                                                                                            |

|                  | B2   | P3.2/INT0         | R/W |                |                                  | 1        | I/O P3.2 & external interrupt 0 input                                                                                                                                                   |

|                  | B1   | P3.1              | R/W |                |                                  | 1        | I/O P3.1                                                                                                                                                                                |

|                  | В0   | P3.0              | R/W |                |                                  | 1        | I/O P3.0                                                                                                                                                                                |

| B2/HB            | B7~0 | НВ                | R/W |                |                                  | 00000000 | High byte address of "MOVX @Ri"                                                                                                                                                         |

| B8H/IP           | B7   | BTF               | W   | High           | Low                              | 0        | Buzzer timer interrupt priority level                                                                                                                                                   |

|                  | B6   | PS1               | W   | High           | Low                              | 0        | POCSAG receiving buffer interrupt priority level                                                                                                                                        |

|                  | B5   | -                 | W   |                |                                  | 0        | Clear this bit to 0 after reset                                                                                                                                                         |

|                  | B4   | -                 | W   |                |                                  | 0        | Clear this bit to 0 after reset                                                                                                                                                         |

|                  | В3   | PT1               | W   | High           | Low                              | 0        | Timer 1 interrupt priority level                                                                                                                                                        |

|                  | B2   | PX1               | W   | High           | Low                              | 0        | Interrupt 1 (INT1) interrupt priority level                                                                                                                                             |

|                  | B1   | PT0               | W   | High           | Low                              | 0        | Timer 0 interrupt priority level                                                                                                                                                        |

|                  | В0   | PX0               | W   | High           | Low                              | 0        | Interrupt 0 (INT0) interrupt priority level                                                                                                                                             |

| C0H/CSCON        | B7   | 1                 | W   |                |                                  | 0        | Clear B7~B4 to 0 after reset                                                                                                                                                            |

|                  | B6   | 1                 | W   |                |                                  | 0        |                                                                                                                                                                                         |

|                  | B5   | -                 | W   |                |                                  | 0        |                                                                                                                                                                                         |

|                  | B4   | -                 | W   |                |                                  | 0        |                                                                                                                                                                                         |

|                  | В3   | OVFH              | R   |                |                                  | 0        | No use                                                                                                                                                                                  |

|                  | B2   | OVFL              | R   |                |                                  | 0        | OSC2 clock stable flag                                                                                                                                                                  |

|                  | B1   | SIF               | R   |                |                                  | 0        | POCSAG receiving buffer interrupt request flag                                                                                                                                          |

|                  | В0   | REN1              | W   | Enable         | Disable                          | 0        | POCSAG receiving buffer enable control                                                                                                                                                  |

| C1H/SMODE        | B7~0 | SMODE             | W   |                |                                  | 00000000 | POCSAG mode control, Set SMODE = 11101101 after reset                                                                                                                                   |

| C2H/SB1          | B7~0 | SB1               | R   |                |                                  | 00000000 | POCSAG receiving buffer 1                                                                                                                                                               |

| C3H/SB2          | B7~0 | SB2               | R   |                |                                  | 00000000 | POCSAG receiving buffer 2                                                                                                                                                               |

| ADDRESS<br>/NAME | BIT  | BIT NAME | R/W | 1       | 0         | INITIAL  | FUNCTION                                                                                                                                                                 |

|------------------|------|----------|-----|---------|-----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C4H/SB3          | B7~0 | SB3      | R   |         |           | 00000000 | POCSAG receiving buffer 3                                                                                                                                                |

| C9H/T2MOD        | В7   | DME0     | W   | On-chip | External  | 1        | MOVX RAM selection (384 bytes), set to 1 after reset                                                                                                                     |

|                  | В6   | -        | W   |         |           | 0        | Clear this bit to "0" after reset                                                                                                                                        |

|                  | B5   | -        | W   |         |           | 0        | Clear this bit to "0" after reset                                                                                                                                        |

|                  | B4   | -        | W   |         |           | 0        | Clear this bit to "0" after reset                                                                                                                                        |

|                  | В3   | -        | W   |         |           | 0        | Clear this bit to "0" after reset                                                                                                                                        |

|                  | B2   | TONESEL  | W   | PWM     | 50-50duty | 0        | Buzzer tone duty control                                                                                                                                                 |

|                  | B1   | -        | W   |         |           | 0        | Clear this bit to "0" after reset                                                                                                                                        |

|                  | В0   | -        | W   |         |           | 0        | Clear this bit to "0" after reset                                                                                                                                        |

| D0H/PSW          | В7   | CY       | R   |         |           | 0        | Carry flag:                                                                                                                                                              |

|                  |      |          |     |         |           |          | Set for an arithmetic operation which results in a carry being generated from the ALU. It is also used as the accumulator for the bit operations.                        |

|                  | B6   | AC       | R   |         |           | 0        | Auxiliary carry: Set when the previous operation resulted in a carry (during addition) or a borrowing (during subtraction) from the high order nibble.                   |

|                  | B5   | F0       | R/W |         |           | 0        | User define flag                                                                                                                                                         |

|                  | B4   | RS1      | R/W |         |           | 0        | RS1 RS0 Register bank selection 0 0 Bank 0 00-07(B0-B7)                                                                                                                  |

|                  | В3   | RS0      | R/W |         |           | 0        | 0 1 Bank 1 08-0F(B0-B7)<br>1 0 Bank 2 10-17(B0-B7)<br>1 1 Bank 3 18-1F(B0-B7)                                                                                            |

|                  | B2   | OV       | R   |         |           | 0        | Overflow flag:  Set when a carry was generated from the seventh bit but not from the 8th bit as a result of the previous operation or viceversa.                         |

|                  | B1   | F1       | R/W |         |           | 0        | User defined flag                                                                                                                                                        |

|                  | В0   | Р        | R   |         |           | 0        | Parity flag:                                                                                                                                                             |

|                  |      |          |     |         |           |          | Set/cleared by hardware to indicate odd/even number of 1's in the accumulator.                                                                                           |

| D8H/WDCON        | В7   | RTIF     | R   |         |           | 0        | RTC interrupt request flag                                                                                                                                               |

|                  | В6   | POR      | R/W |         |           | Х        | Power-on reset flag:                                                                                                                                                     |

|                  |      |          |     |         |           |          | Hardware will set this flag on a power up condition. This flag can be read or written by software. A write by software is the only way to clear this bit once it is set. |

|                  | B5   | -        | R/W |         |           | 0        | Clear this be after reset                                                                                                                                                |

|                  | B4   | -        | R/W |         |           | 0        | Clear this be after reset                                                                                                                                                |

| ADDRESS<br>/NAME | BIT | BIT NAME | R/W | 1 | 0 | INITIAL | FUNCTION                                                                                                                                                                                                                                                                                                                                                           |

|------------------|-----|----------|-----|---|---|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D8H/WDCON        | В3  | WDIF     | R   |   |   | 0       | Watchdog Timer Interrupt Flag: If the watchdog interrupt is enabled, hardware will set this bit to indicate that the watchdog interrupt has occurred. If the interrupt is not enabled, then this bit indicates that the time-out period has elapsed.                                                                                                               |

|                  | B2  | WTRF     |     |   |   | Х       | Watchdog Timer Reset Flag:                                                                                                                                                                                                                                                                                                                                         |

|                  |     |          |     |   |   | , ,     | Hardware will set this bit when the watchdog timer causes a reset. Software can read it but must clear it manually. A power-fail reset will also clear the bit. This bit helps software in determining the cause of a reset. If EWT = 0, the watchdog timer will have no affect on this bit.                                                                       |

|                  | B1  | EWT      |     |   |   | Х       | Enable Watchdog timer Reset: Setting this bit will enable the Watchdog timer Reset function.                                                                                                                                                                                                                                                                       |

|                  | В0  | RWT      |     |   |   | 0       | Reset Watchdog Timer: This bit helps in putting the watchdog timer into a know state. It also helps in resetting the watchdog timer before a time-out occurs. Failing to set the EWT before time-out will cause an interrupt, if EWDI (EIE.4) is set, and 512 clocks after that a watchdog timer reset will be generated if EWT is set. This bit is self-clearing. |

| D9H/P0IO         | В7  | P0IO.7   | W   |   |   | 0       | R/W control for P0.7 (key3):                                                                                                                                                                                                                                                                                                                                       |

|                  |     |          |     |   |   |         | No use, clear this bit to 0 after.                                                                                                                                                                                                                                                                                                                                 |

|                  | В6  | P0IO.6   | W   |   |   | 0       | R/W control for P0.6 (key2):                                                                                                                                                                                                                                                                                                                                       |

|                  |     |          |     |   |   |         | 1: input mode without pull high R                                                                                                                                                                                                                                                                                                                                  |

|                  |     |          |     |   |   |         | 0: output mode or input with pull high R                                                                                                                                                                                                                                                                                                                           |

|                  |     |          |     |   |   |         | Clear this bit after reset for key2 input with pull high R function.                                                                                                                                                                                                                                                                                               |

|                  | B5  | P0IO.5   | W   |   |   | 0       | R/W control for P0.5 (key1):                                                                                                                                                                                                                                                                                                                                       |

|                  |     |          |     |   |   |         | 1: input mode without pull high R                                                                                                                                                                                                                                                                                                                                  |

|                  |     |          |     |   |   |         | 0: output mode or input with pull high R                                                                                                                                                                                                                                                                                                                           |

|                  |     |          |     |   |   |         | Clear this bit after reset for key1 input with pull high R function.                                                                                                                                                                                                                                                                                               |

|                  | B4  | P0IO.4   | W   |   |   | 0       | R/W control for P0.4 (key0):                                                                                                                                                                                                                                                                                                                                       |

|                  |     |          |     |   |   |         | 1: input mode without pull high R                                                                                                                                                                                                                                                                                                                                  |

|                  |     |          |     |   |   |         | 0: output mode or input with pull high R                                                                                                                                                                                                                                                                                                                           |

|                  |     |          |     |   |   |         | Clear this bit after reset for key0 input with pull high R function.                                                                                                                                                                                                                                                                                               |

|                  | В3  | P0IO.3   | W   |   |   | 0       | R/W control for P0.3:                                                                                                                                                                                                                                                                                                                                              |

|                  |     |          |     |   |   |         | Set this bit to "1" after reset for DEC_ADDT input                                                                                                                                                                                                                                                                                                                 |

|                  | B2  | P0IO.2   | W   |   |   | 0       | R/W control for P0.2:                                                                                                                                                                                                                                                                                                                                              |

|                  |     |          |     |   |   |         | Clear this bit to "0" after reset for F_ADR output function                                                                                                                                                                                                                                                                                                        |

|                  | B1  | P0IO.1   | W   |   |   | 0       | R/W control for P0.1:                                                                                                                                                                                                                                                                                                                                              |

|                  |     |          |     |   |   |         | Set this bit to "1" after reset for DEC_SYNVAL input                                                                                                                                                                                                                                                                                                               |

|                  | В0  | P0IO.0   | W   |   |   | 0       | R/W control for P0.0:                                                                                                                                                                                                                                                                                                                                              |

|                  |     |          |     |   |   |         | Set this bit to "1" after reset.                                                                                                                                                                                                                                                                                                                                   |

|                  |     |          |     |   |   |         | For read-in F_data, set this bit to "1".                                                                                                                                                                                                                                                                                                                           |

|                  |     |          |     |   |   |         | For write-out F_data, clear this bit to "0".                                                                                                                                                                                                                                                                                                                       |

Descriptions Of Special Function Registers (SFRS), continued

| ADDRESS<br>/NAME | BIT  | BIT NAME | R/W | 1       | 0                                                                      | INITIAL  | FUNCTION                                                                                                                                                                                                                              |  |

|------------------|------|----------|-----|---------|------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DAH/P1IO         | B7~0 | P1IO     | W   |         |                                                                        | 00000000 | Bit addressable R/W control for P1:  1: input mode without pull high R  0: output mode or input with pull high R  Set DA to "00000000" after reset, since P' are all output mode.                                                     |  |

| DBH/P2IO         | B7~0 | P2IO     | W   |         | Set DB to "X0000000 " after reset.  The value of P2IO.7 depends on the |          | 1: input mode without pull high R<br>0: output mode or input with pull high R                                                                                                                                                         |  |