S/UNI-PDH REFERENCE DESIGN

# PM7545 S/UNI-PDH-EVBD

# REFERENCE DESIGN FOR S/UNI-PDH

**Preliminary Information**

Issue 2, January, 1995

PRELIMINARY INFORMATION, Issue 2, January 11, 1995

S/UNI-PDH REFERENCE DESIGN

# **CONTENTS**

| OVERVIEW                                     | 1  |

|----------------------------------------------|----|

| FUNCTIONAL DESCRIPTION                       | 2  |

| SCI-PHY Interface                            | 3  |

| Microprocessor interface                     | 3  |

| Indicators                                   | 3  |

| PM7345 S/UNI-PDH                             | 3  |

| On Board Oscillators                         | 4  |

| PLCP Stuff Control                           | 4  |

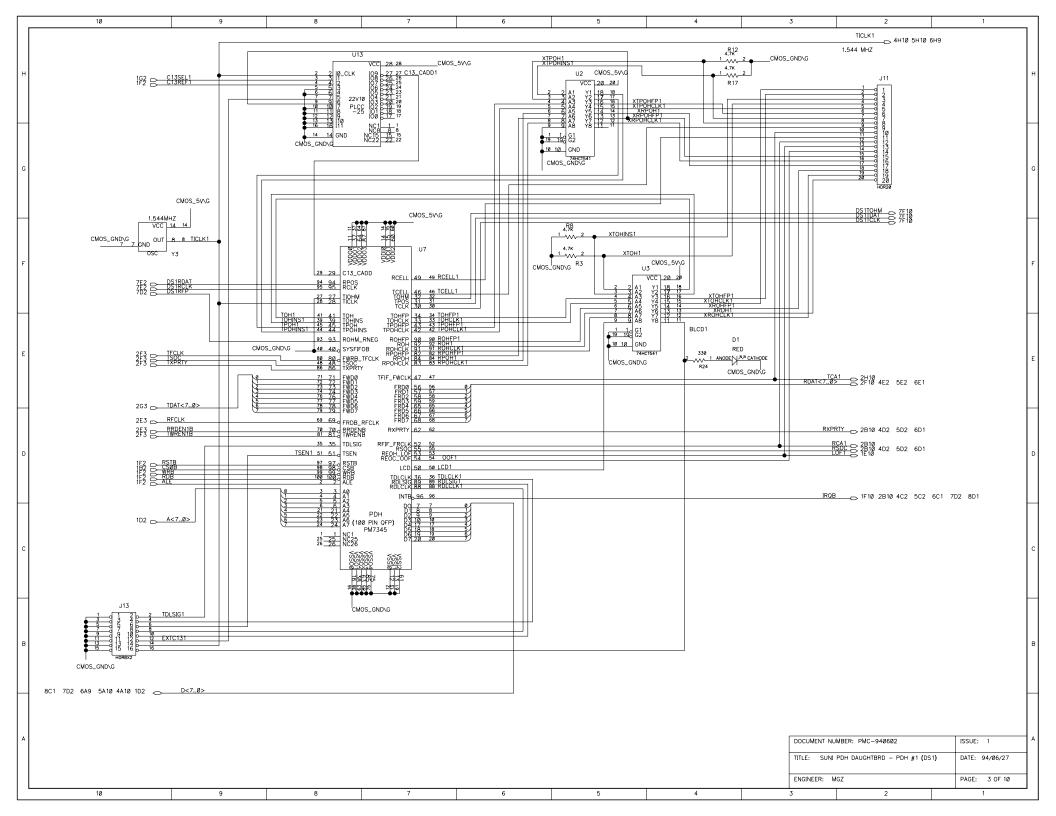

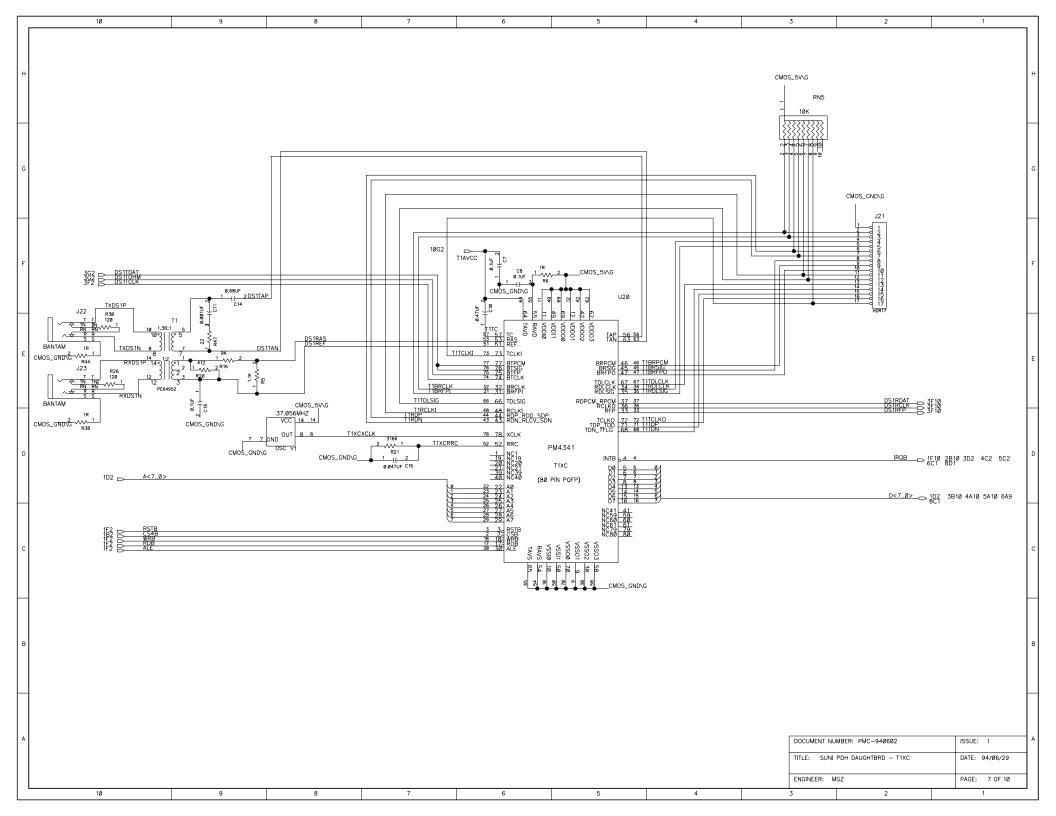

| T1XC                                         | 4  |

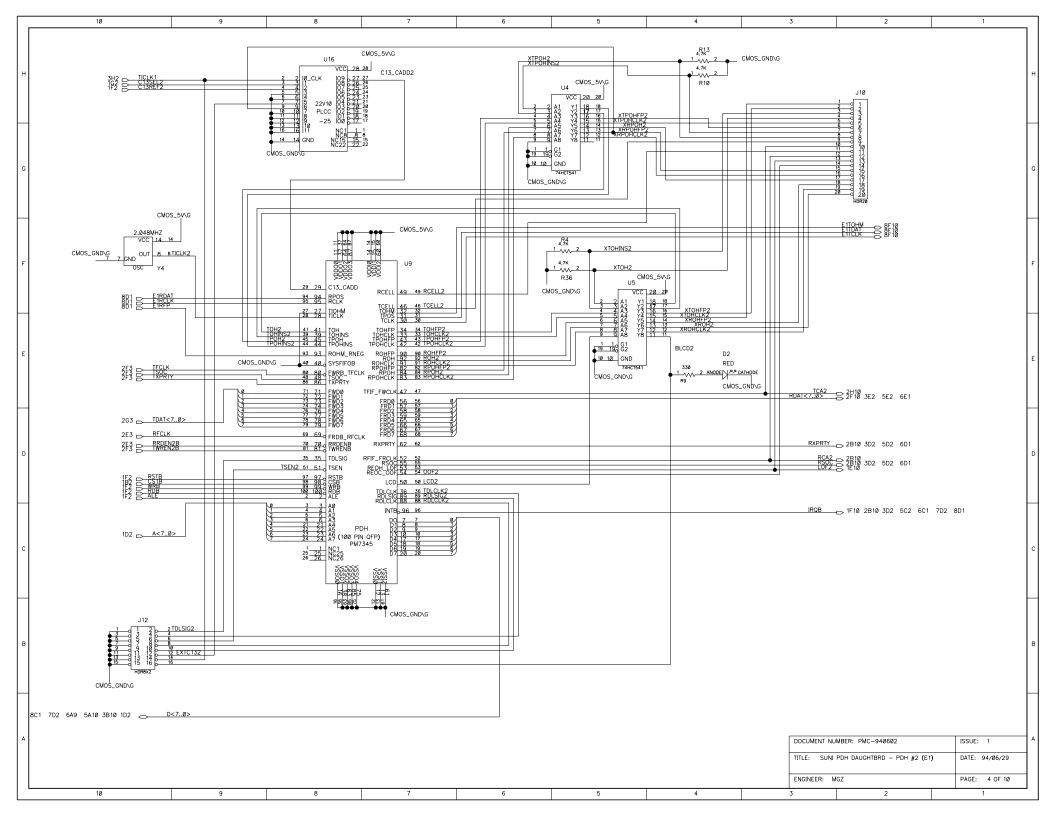

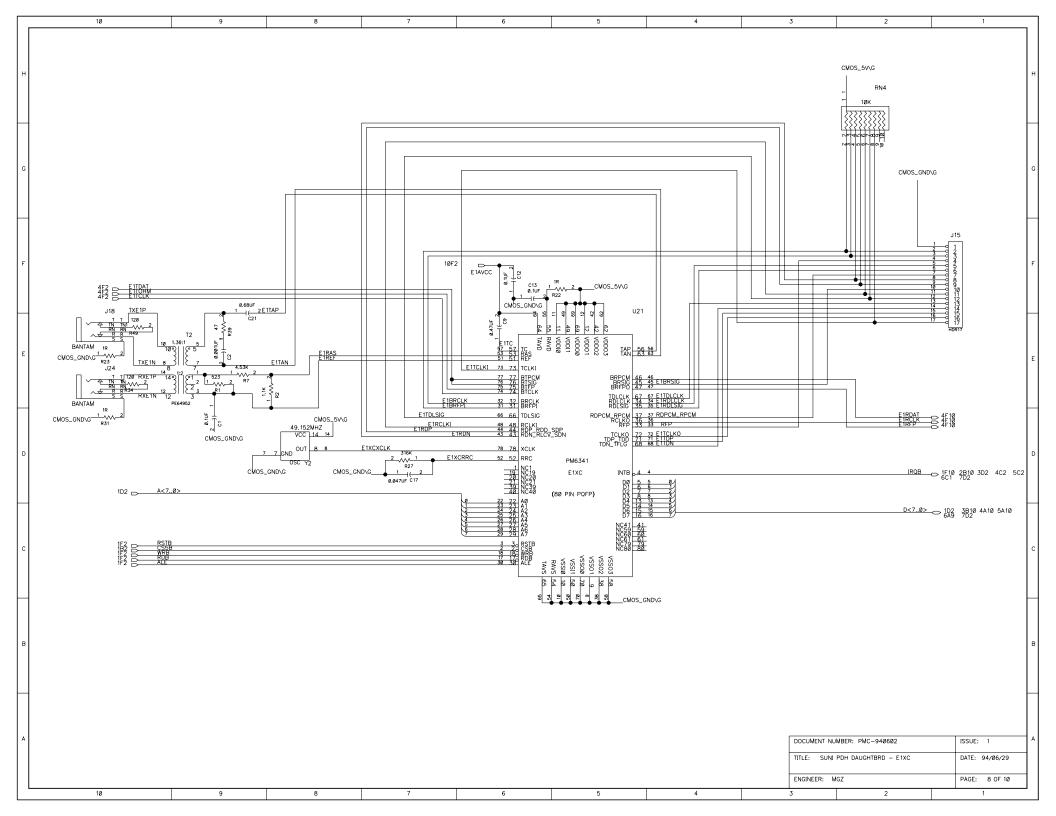

| E1XC                                         | 5  |

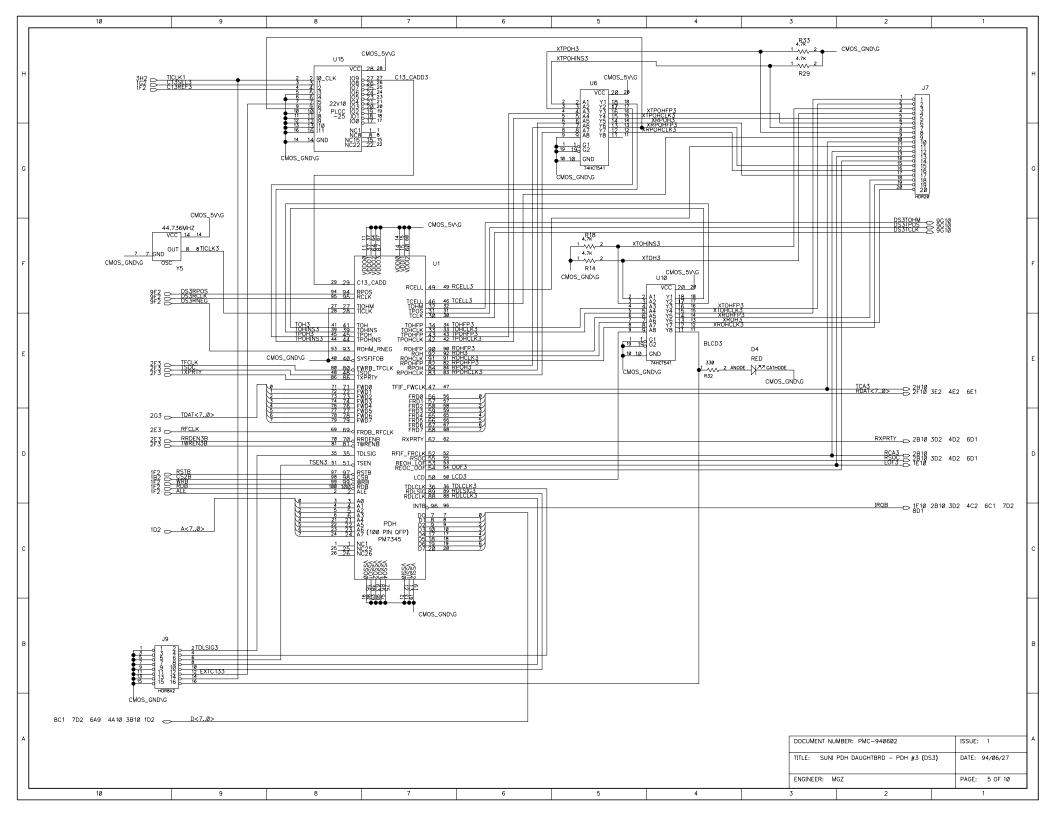

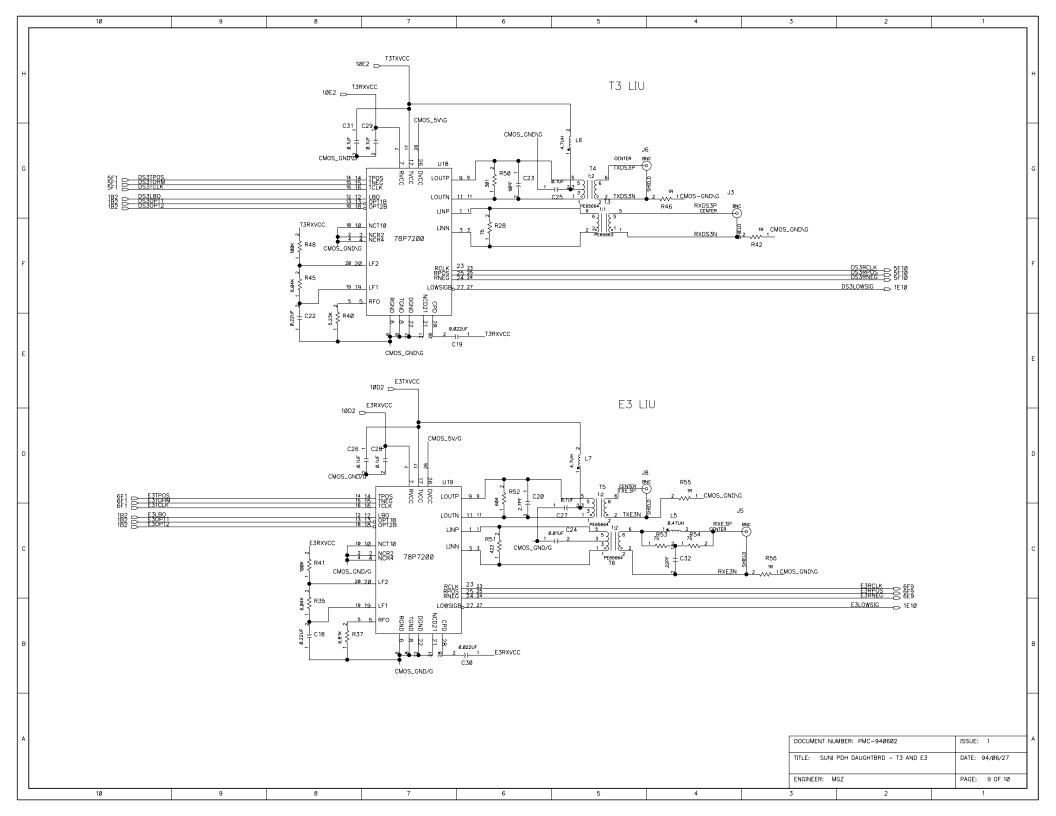

| DS3 LIU                                      | 5  |

| E3 LIU                                       | 5  |

| DS1 Line Interface                           | 6  |

| E1 Line Interface                            | 6  |

| DS3 Line Interface                           |    |

| E3 Line Interface                            | 6  |

| S/UNI-PDH EVBD CONNECTOR SIGNAL DESCRIPTIONS | 7  |

| Daughterboard Microprocessor Connector       | 7  |

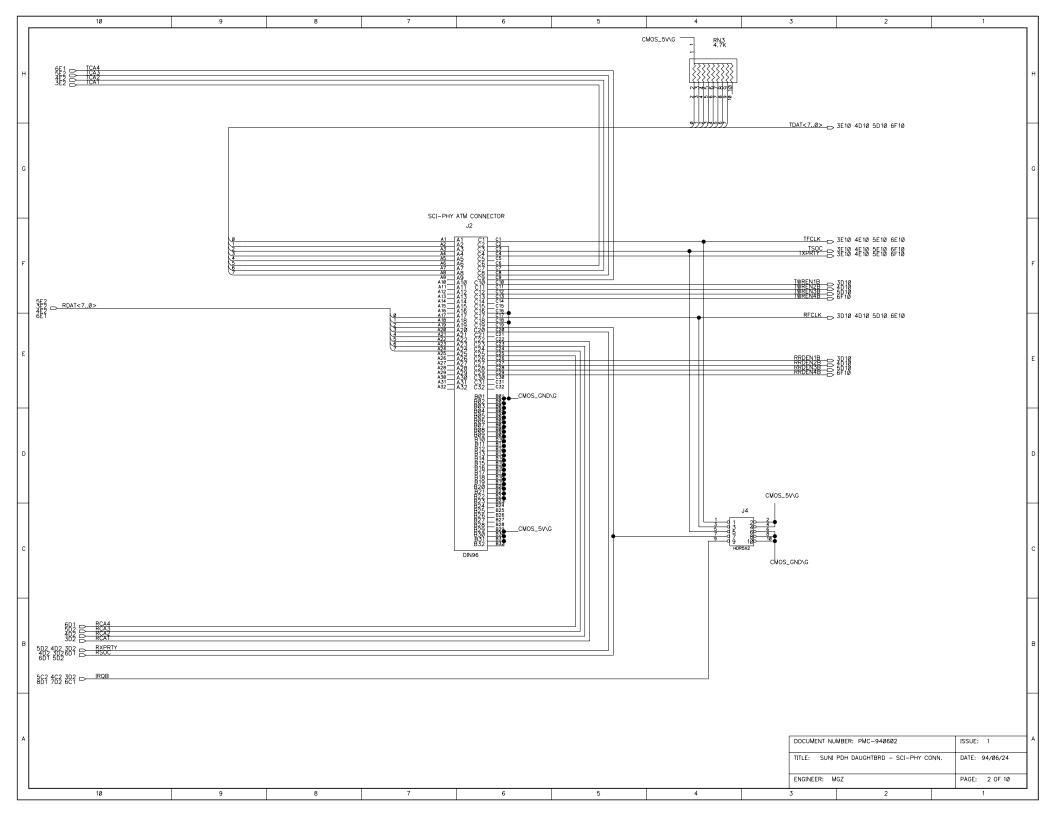

| Daughterboard SCI-PHY Connector Interface    | 10 |

| Line Interface Signals                       | 13 |

| Header Descriptions                          | 13 |

| Power Connector                              | 23 |

| OPERATION                                    | 24 |

| Operation with SCI-PHY Motherboard           |    |

| Operation in Loopback Mode                   |    |

| ELECTRICAL SPECIFICATIONS                    |    |

| SCI-PHY ATM and Microprocessor Interface     |    |

| Line Interface Signals                       |    |

| S/UNI-PDH EVBD Power                         |    |

|                                              |    |

| STOCK LIST                                   | 26 |

| REFERENCES                              | 30 |

|-----------------------------------------|----|

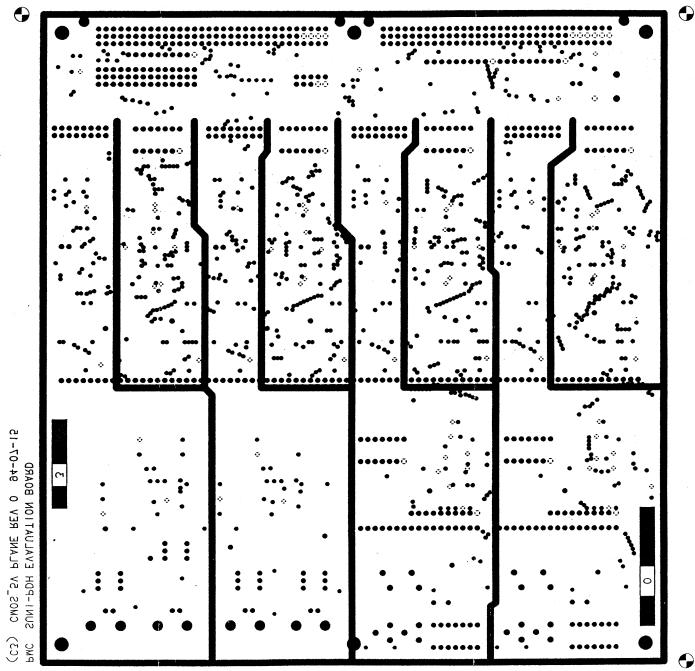

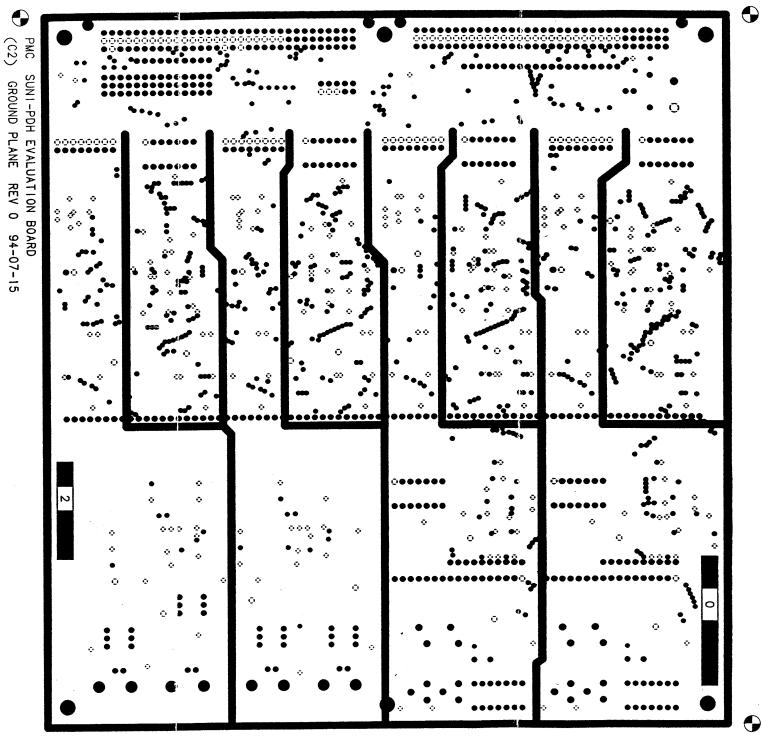

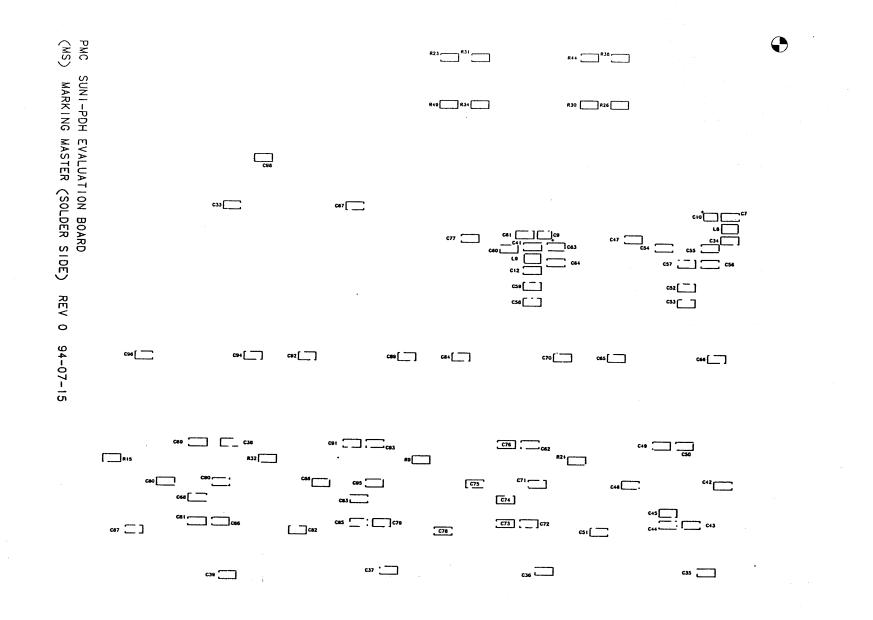

| APPENDIX 1: COMPONENT PLACEMENT DIAGRAM | 31 |

| APPENDIX 2: SUGGESTED REVISIONS         | 32 |

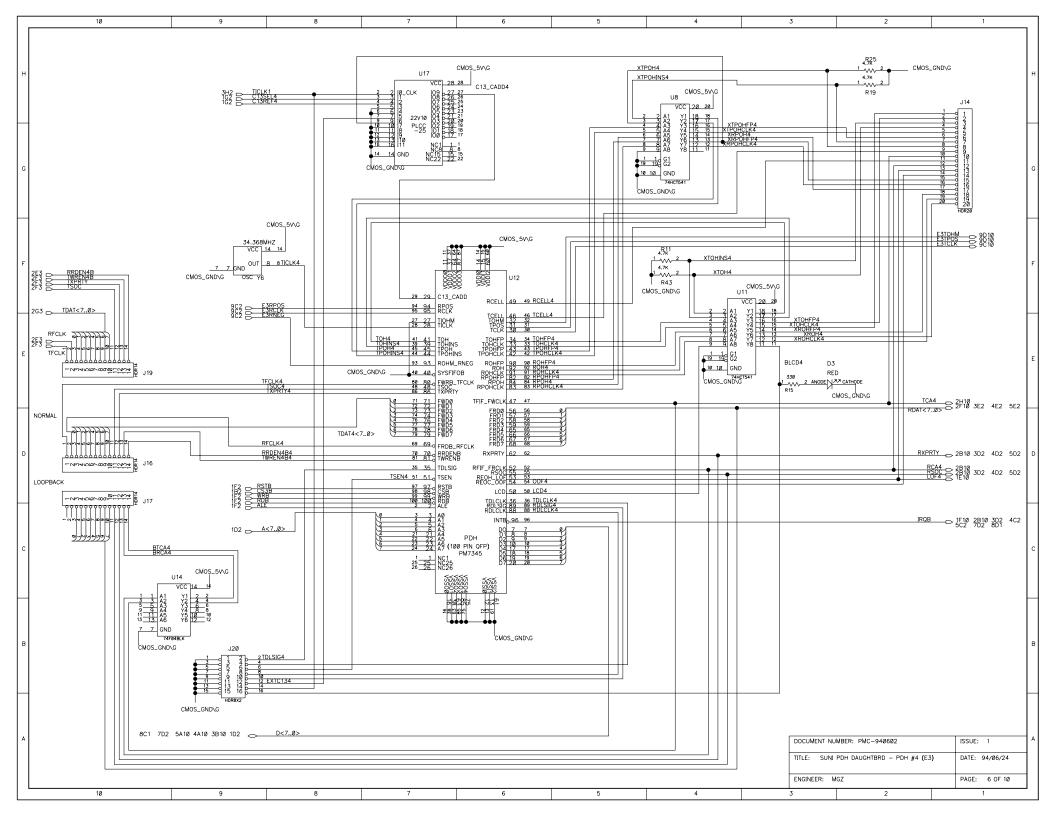

| APPENDIX 3: SCHEMATICS                  | 33 |

| APPENDIX 4: EXAMPLE FORTH WORDS         | 34 |

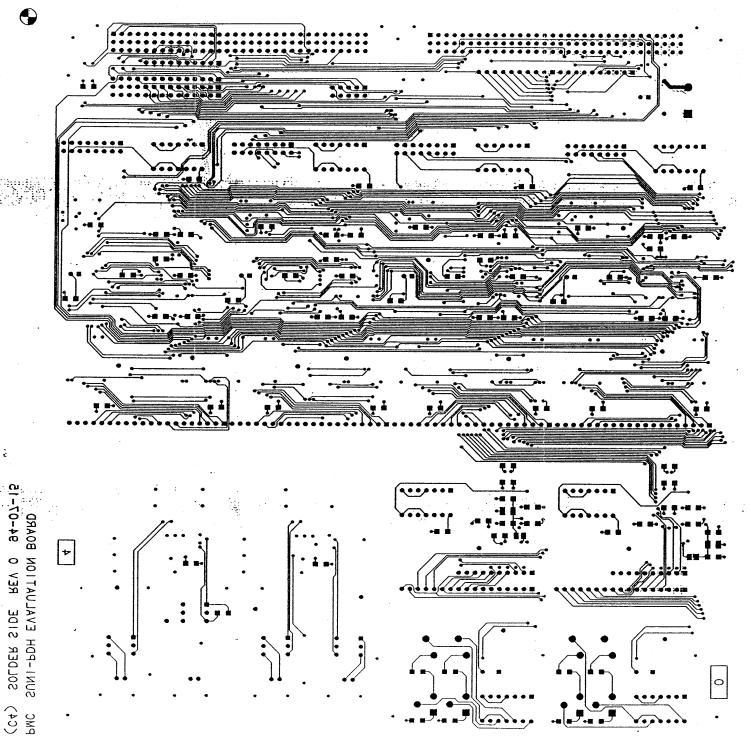

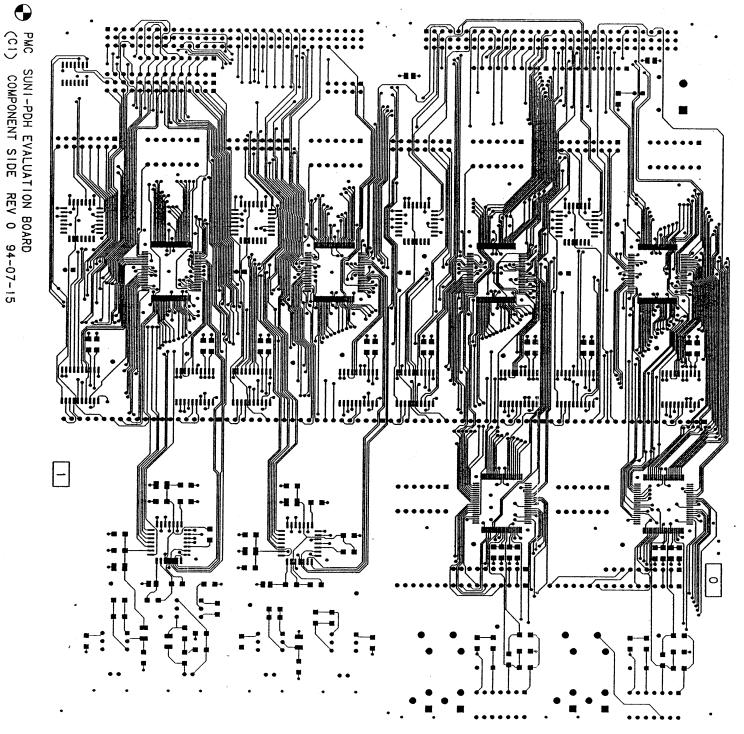

| APPENDIX 5: EXAMPLE BOARD LAYOUT        | 35 |

<sup>™</sup> PM7545 S/UNI-PDH-EVBD

PRELIMINARY INFORMATION, Issue 2, January 11, 1995

S/UNI-PDH REFERENCE DESIGN

#### **OVERVIEW**

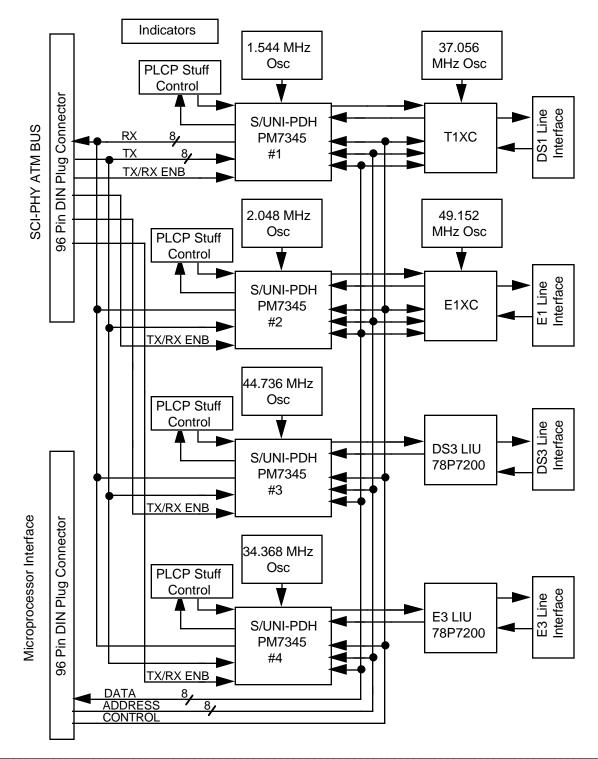

The PM7545 S/UNI-PDH EVBD is a versatile board used to perform functional testing of the S/UNI-PDH PM7345 chip (PDH). The board allows for complete functional testing of the S/UNI-PDH device at DS3 and E3 rates of 44.736 Mbit/s and 34.368 Mbit/s, as well as at DS1 and E1 rates of 1.544 Mbit/s and 2.048 Mbit/s. The board can be used with the SATURN COMPLIANT INTERFACE FOR ATM PHYSICAL LAYER INTERCONNECT EVALUATION MOTHER BOARD (SCI-PHY EVMB), or it can be used stand alone with reduced functionality. The S/UNI-PDH EVBD is normally configured, monitored, and powered through two 96 pin DIN connectors that mate directly to the SCI-PHY EVMB. There is a power connector and fuse for the application of +5V and ground directly to the S/UNI-PDH EVBD.

There are four PM7345 S/UNI-PDH devices on the S/UNI-PDH EVBD. One PM7345 is configured for operation at DS1, another one at E1, one at DS3, and the last one at E3. The rate that each S/UNI-PDH works at is fixed by the board design. The DS1 format S/UNI-PDH utilizes the PMC PM4341 T1XC T1 framer and transceiver. The DS3/E3 format S/UNI-PDHs utilize the internal PDH T3/E3 framer and the external Silicon Systems SSI78P7200 DS3/E3 LIU. The E1 format S/UNI-PDH utilizes the PMC PM6341 E1XC E1 framer and transceiver. The E3 format S/UNI-PDH can also be put into a special Loopback mode whereby parallel ATM bus receive signals are looped back into the transmit side. The rest of the S/UNI-PDH devices will not function in this mode. Line side connections use BNC and Bantam connectors. One of the 96 pin DIN connectors is a generic microcontroller port. The second 96 pin DIN connector contains signals necessary to implement ATM cell transfer.

All four S/UNI-PDH PM7345 devices have microprocessor interfaces that are accessible through the DIN connector. Control of the T1XC, E1XC, and 78P7200 devices is accomplished via the same connector. Twenty four general purpose parallel input/output (PIO) lines are also accessible through the same connector. PIO lines are used to control and monitor various signals on the S/UNI-PDH EVBD. Headers are provided for PLCP and DS3/E3 overhead insertion and extraction. Headers are also provided for HDLC signals and other pertinent control/status signals.

Each S/UNI-PDH PM7345 is independently configurable and has its own LIU. All four PM7345 share data signals on the ATM bus side and are individually selectable under microprocessor control.

S/UNI-PDH REFERENCE DESIGN

# FUNCTIONAL DESCRIPTION

# Fig 1. Block Diagram

<sup>™</sup> PM7545 S/UNI-PDH-EVBD

PRELIMINARY INFORMATION, Issue 2, January 11, 1995

S/UNI-PDH REFERENCE DESIGN

#### SCI-PHY Interface

The SCI-PHY interface provides a standard connection to the S/UNI-PDH ATM drop side according the SCI-PHY specification. The 96 pin DIN SCI-PHY connector contains parallel ATM receive and transmit signals along with the required FIFO control signals and clocks. The PDH devices on the S/UNI-PDH EVBD utilize 8 bit parallel transmit and receive ATM transfers. The SCI-PHY interface contains signals that support multiple physical layer devices. Since there are four S/UNI-PDH PM7345 on the EVBD, the SCI-PHY interface will be supporting its maximum number of physical layer devices. Also included in the SCI-PHY connector is a +5V supply. The SCI-PHY interface was designed to be electrically compatible with the SCI-PHY EVMB.

#### Microprocessor interface

The Microprocessor interface is a generic microprocessor interface. The interface contains data, address, and control lines compatible with the SCI-PHY EVMB microprocessor interface and is available on a 96 pin DIN connector. These signals are directly connected to the microprocessor ports on the four S/UNI-PDH PM7345 devices, the T1XC, and the E1XC. Six chip select lines are use to control the programmable devices on the board. In addition, this interface contains 24 parallel input/output (PIO) lines, 16 of which are used by the S/UNI-PDH EVBD. The mother board's PIO lines come from an undedicated 8255 PIO on that board. PIO lines are used to provide control over each PM7345's 8 kHz reference for PLCP stuff control (C13/CADD). PIO lines are used to control the two 78P7200 devices. PIO input lines are used to monitor low received line signal level on the 78P7200 LIUs. PIO inputs also monitor Loss of Frame signals from the PM7345s.

#### **Indicators**

There are five LEDs provided for visual status. One LED lights when a source of five volts is provided to the S/UNI-PDH EVBD. The other four LEDs light up when Loss of Cell Delineation (LCD) occurs for the individual S/UNI-PDH PM7345 chips.

#### PM7345 S/UNI-PDH

The PM7345 devices are the heart of the S/UNI-PDH EVBD. They are ATM physical layer processors with integrated DS3 and E3 framing. PLCP sublayer DS1, DS3, E1, and E3 processing is supported as is ATM cell delineation. All traffic goes through the PM7345s. Each PM7345 is setup through the microprocessor interface. All the internal registers are accessed through this interface.

When a PM7345 is configured for DS3 transmission, the overhead bits are inserted and extracted on an external serial interface. The DS3 overhead interface signals are brought out to a header. When PLCP framing is enabled, the PLCP overhead octets are inserted and extracted on an external serial interface that is also brought out to headers. All ATM data is passed through the parallel SCI-PHY data bus.

PRELIMINARY INFORMATION, Issue 2, January 11, 1995

S/UNI-PDH REFERENCE DESIGN

Because there are four physical layer devices sharing the ATM parallel data buses, device select signals on the SCI-PHY DIN connector are utilized to select a particular PM7345 in the transmit and receive directions. S/UNI-PDH device 4 can be put into a special Loopback mode using jumpers on the board. This will allow Loopback testing on the ATM parallel bus side. All other S/UNI-PDH devices do not function in this mode.

When a PM7345 is configured for DS1 or E1 transmission sublayer processing, a unipolar signal with the appropriate clock and framing is provided and expected.

For a complete description of the PM7345, refer to the PM7345 data sheet.

### On Board Oscillators

Each S/UNI-PDH PM7345 device requires an oscillator feeding its TICLK pin . This clock source is used to generate the transmit clock for line side transmissions. S/UNI-PDH device 1 uses a 1.544 MHz oscillator for DS1 transmissions. S/UNI-PDH device 2 uses a 2.048 MHz oscillator for E1 transmissions. S/UNI-PDH device 3 uses a 44.736 MHz oscillator for DS3 transmissions. S/UNI-PDH device 4 uses a 34.368 MHz oscillator for E3 transmissions. The T1XC device uses a 37.056 MHz oscillator on pin XCLK for internal timing generation. The E1XC device uses a 49.152 MHz oscillator on pin XCLK for internal timing generation.

# PLCP Stuff Control

The PM7345 S/UNI-PDH devices provide stuffing control for T3 PLCP (nibble stuffing) and E3 PLCP (byte stuffing) frame formats via the C13/CADD pin. The PLCP Stuff Control block allows this pin to be controlled by one of two reference sources to produce a nominal 125 microsecond PLCP frame rate. The source is either the result of a phase comparison between the transmit PLCP frame rate and receive PLCP frame rate (loop time operation) or the result of a phase comparison between the transmit PLCP frame rate and receive PLCP frame rate (loop time operation) or the result of a phase comparison between the transmit PLCP frame rate and a generated 8 KHz clock. The 8 KHz clock is generated using the onboard 1.544 MHz crystal oscillator and 22V10 PALs.

# <u>T1XC</u>

The PM4341 T1XC is a full featured T1 transceiver with an integrated framer and line analog circuitry. A 37.056 MHz oscillator is used by its internal digital PLL for clock and data recovery. All internal registers for configuration, control, and status monitoring are accessible through its microprocessor interface. The analog line interface is brought out to Bantam connectors. Headers are provided for the digital transmit and receive interface as well as the facility data link (FDL) interface. Also note that the T1XC is connected on the digital signal side to PM7345 S/UNI-PDH device 1.

For a complete description of the T1XC, refer to the PM4341 datasheet.

<sup>™</sup> PM7545 S/UNI-PDH-EVBD

PRELIMINARY INFORMATION, Issue 2, January 11, 1995

S/UNI-PDH REFERENCE DESIGN

# <u>E1XC</u>

The PM6341 E1XC is a full featured E1 transceiver with an integrated framer and line analog circuitry. A 49.152 MHz oscillator is used by its internal digital PLL for clock and data recovery. All internal registers for configuration, control, and status monitoring are accessible through its microprocessor interface. The analog line interface is brought out to Bantam connectors. Headers are provided for the digital transmit and receive interface as well as the facility data link (FDL) interface. Also note that the E1XC is connected on the digital signal side to PM7345 S/UNI-PDH device 2.

For a complete description of the E1XC, refer to the PM6341 datasheet

#### DS3 LIU

A Silicon Systems 78P7200 DS3 line interface unit (LIU) is used to convert the digital B3ZS-encoded AMI encoded data to its analog equivalent and to convert analog B3ZS-encoded AMI to its digital equivalent. The LIU has 3 main control inputs for controlling the transmitter. If the received signal falls below the required threshold, a status signal, LOWSIGB, is asserted. The transmitter control and LOWSIGB signals are accessible via PIO lines. These lines would be under microprocessor control if the SCI-PHY EVMB was connected to the S/UNI-PDH EVBD. Also note that the 78P7200 DS3 LIU is connected on the digital signal side to PM7345 S/UNI-PDH device 3.

For a complete description of the 78P7200, refer to the datasheets in Silicon Systems Communication Products databook.

#### <u>E3 LIU</u>

A Silicon Systems 78P7200 E3 line interface unit (LIU) is used to convert the digital HDB3-encoded AMI encoded data to its analog equivalent and to convert analog HDB3-encoded AMI to its digital equivalent. The LIU has 3 main control inputs for controlling the transmitter. If the received signal falls below the required threshold, a status signal, LOWSIGB, is asserted. The transmitter control and LOWSIGB signals are accessible via PIO lines. These lines would be under microprocessor control if the SCI-PHY EVMB were connected to the S/UNI-PDH EVBD. Also note that the 78P7200 E3 LIU is connected on the digital signal side to PM7345 S/UNI-PDH device 4.

For a complete description of the 78P7200, refer to the datasheets in Silicon Systems Communication Products databook.

PM7545 S/UNI-PDH-EVBD

PRELIMINARY INFORMATION, Issue 2, January 11, 1995

S/UNI-PDH REFERENCE DESIGN

#### DS1 Line Interface

The S/UNI-PDH EVBD provides for the standard DS1 100 ohm analog interface. Two Bantam connectors are provided.

#### E1 Line Interface

The S/UNI-PDH EVBD provides for the standard E1 120 ohm analog interface. Two Bantam connectors are provided.

#### DS3 Line Interface

The S/UNI-PDH EVBD provides for the standard DS3 75 ohm analog interface. Two BNC connectors are provided.

#### E3 Line Interface

The S/UNI-PDH EVBD provides for the standard E3 75 ohm analog interface. Two BNC connectors are provided.

S/UNI-PDH REFERENCE DESIGN

# S/UNI-PDH EVBD CONNECTOR SIGNAL DESCRIPTIONS

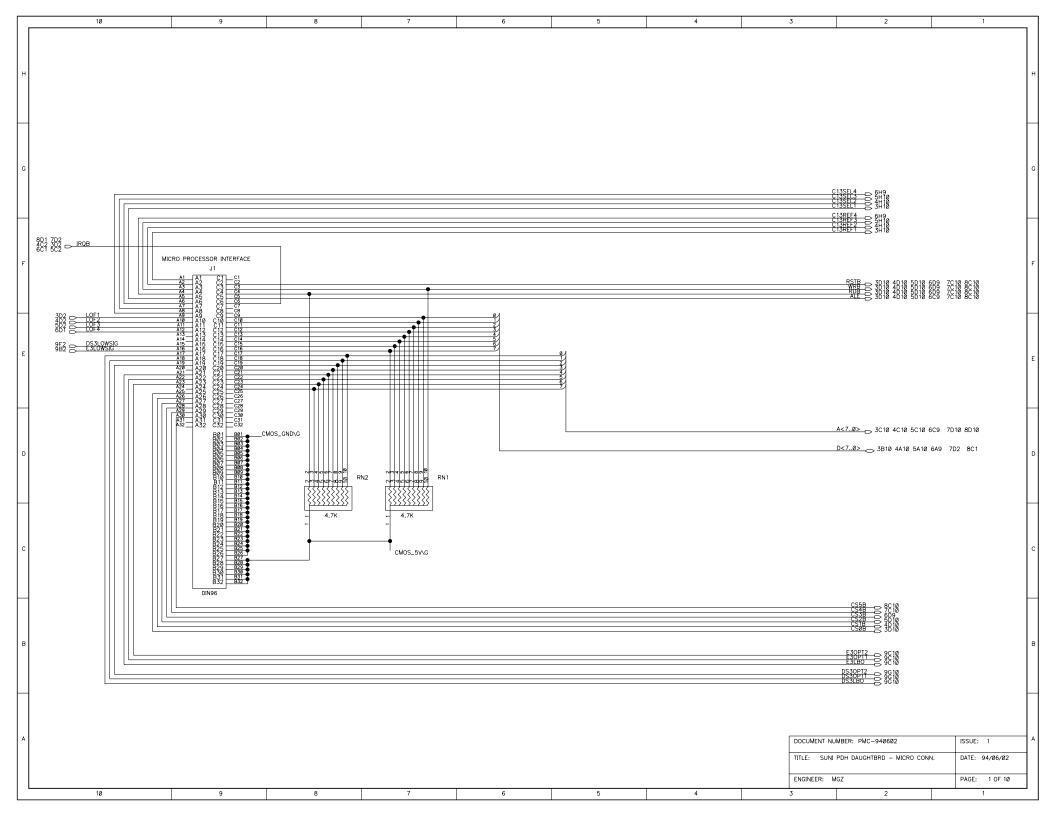

#### Daughterboard Microprocessor Connector

The Daughterboard Microprocessor Connector Interface is made up of a 96 pin DIN plug connector designed to mate with a corresponding connector on the SCI-PHY mother board. The connector consists of signals appropriate to read and write the registers of the S/UNI-PDH EVBD. It also provides the necessary power and ground. CMOS signal levels are used on this interface.

| Signal   |      |     |                                                                                                                                                                               |

|----------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name     | Туре | Pin | Function                                                                                                                                                                      |

| PIO1A[0] | I    | A1  | Connected to C13REF1. This signal selects between<br>the 1.544 MHz crystal (divided by 193) or RPOHFP1<br>as the onboard source of the C13/CADD pin on<br>S/UNI-PDH device 1. |

| PIO1A[1] | I    | A2  | Connected to C13REF2. This signal selects between<br>the 1.544 MHz crystal (divided by 193) or RPOHFP2<br>as the onboard source of the C13/CADD pin on<br>S/UNI-PDH device 2. |

| PIO1A[2] | I    | A3  | Connected to C13REF3. This signal selects between<br>the 1.544 MHz crystal (divided by 193) or RPOHFP3<br>as the onboard source of the C13/CADD pin on<br>S/UNI-PDH device 3. |

| PIO1A[3] | I    | A4  | Connected to C13REF4. This signal selects between<br>the 1.544 MHz crystal (divided by 193) or RPOHFP4<br>as the onboard source of the C13/CADD pin on<br>S/UNI-PDH device 4. |

| PIO1A[4] | I    | A5  | Connected to C13SEL1. This signals controls which<br>8 kHz reference signal goes to the C13/CADD pin on<br>S/UNI-PDH device 1                                                 |

| PIO1A[5] | I    | A6  | Connected to C13SEL2. This signals controls which<br>8 kHz reference signal goes to the C13/CADD pin on<br>S/UNI-PDH device 2.                                                |

| PIO1A[6] | I    | A7  | Connected to C13SEL3. This signals controls which<br>8 kHz reference signal goes to the C13/CADD pin on<br>S/UNI-PDH device 3.                                                |

| PIO1A[7] | I    | A8  | Connected to C13SEL4. This signals controls which<br>8 kHz reference signal goes to the C13/CADD pin on<br>S/UNI-PDH device 4.                                                |

| PIO1B[0] | 0    | A9  | Connected to LOF1. Loss of frame for S/UNI-PDH device 1.                                                                                                                      |

| PIO1B[1] | 0    | A10 | Connected to LOF2. Loss of frame for S/UNI-PDH device 2.                                                                                                                      |

| PIO1B[2] | 0  | A11              | Connected to LOF3. Loss of frame for S/UNI-PDH device 3                            |

|----------|----|------------------|------------------------------------------------------------------------------------|

| PIO1B[3] | 0  | A12              | Connected to LOF4. Loss of frame for S/UNI-PDH device 4.                           |

| PIO1B[4] | 0  | A13              | Not used                                                                           |

| PIO1B[5] | 0  | A14              | Not used                                                                           |

| PIO1B[6] | 0  | A15              | Connected to DS3LOWSIG. Low receive line level for<br>DS3 78P7200 LIU.             |

| PIO1B[7] | 0  | A16              | Connected to E3LOWSIG. Low receive line level for E3 78P7200 LIU.                  |

| PIO1C[0] | I  | A17              | Connected to DS3LBO. Controls line buildout<br>function on DS3 78P7200 LIU.        |

| PIO1C[1] | I  | A18              | Connected to DS3OPT1. Controls transmitter output power on DS3 78P7200 LIU.        |

| PIO1C[2] | I  | A19              | Connected to DS3OPT2. Controls transmitter enable on DS3 78P7200 LIU.              |

| PIO1C[3] |    | A20              | Not used                                                                           |

| PIO1C[4] | I  | A21              | Connected to E3LBO. Controls line build out function<br>on E3 78P7200 LIU.         |

| PIO1C[5] | I  | A22              | Connected to E3OPT1. Controls transmitter output power on E3 78P7200 LIU.          |

| PIO1C[6] | I  | A23              | Connected to E3OPT2. Controls transmitter enable<br>on E3 78P7200 LIU.             |

| PIO1C[7] | 1  | A24              | Not used                                                                           |

| CSB0     | I  | A25              | Active low chip select for S/UNI-PDH device 1. Active address range C000H - C0FFH. |

| CSB1     | I  | A26              | Active low chip select for S/UNI-PDH device 2. Active address range C100H - C1FFH. |

| CSB2     | I  | A27              | Active low chip select for S/UNI-PDH device 3. Active address range C200H - C2FFH. |

| CSB3     | I  | A28              | Active low chip select for S/UNI-PDH device 4. Active address range C300H - C3FFH. |

| CSB4     | I  | A29              | Active low chip select for T1XC. Active address range C400H - C4FFH.               |

| CSB5     | I  | A30              | Active low chip select for E1XC. Active address range C500H - C5FFH.               |

| CSB6     | NC | A31              | Not used                                                                           |

| CSB7     | NC | A32              | Not used.                                                                          |

| GND      | Р  | B1<br>to<br>B26  | Ground.                                                                            |

| PWR+5V   | Ρ  | B27<br>to<br>B32 | +5V power.                                                                         |

| RST                                                                                                                                                 | NC                                                                     | C1                                                                                                                  | Not Connected                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSTB                                                                                                                                                | I                                                                      | C2                                                                                                                  | Active low hardware reset connected to RSTB line of S/UNI-PDH devices, T1XC, and E1XC.                                                                                        |

| WRB                                                                                                                                                 | I                                                                      | C3                                                                                                                  | Active low write strobe to S/UNI-PDH devices, T1XC, and E1XC.                                                                                                                 |

| RDB                                                                                                                                                 | I                                                                      | C4                                                                                                                  | Active low read strobe to S/UNI-PDH devices, T1XC, and E1XC.                                                                                                                  |

| ALE                                                                                                                                                 | I                                                                      | C5                                                                                                                  | Address latch enable. When high, identifies that address is valid on D[7:0]. Connected to the four S/UNI-PDH devices, T1XC, and E1XC.                                         |

| HC11_IRQB                                                                                                                                           | 0                                                                      | C6                                                                                                                  | Maskable 68HC11 interrupt. Connected to the four S/UNI-PDH devices, the T1XC, and the E1XC interrupt pins (INTB).                                                             |

| HC11_<br>XIRQB                                                                                                                                      | NC                                                                     | C7                                                                                                                  | Not used                                                                                                                                                                      |

| PIO_RSTB                                                                                                                                            | NC                                                                     | C8                                                                                                                  | Not used                                                                                                                                                                      |

| D[0]                                                                                                                                                | I/O                                                                    | C9                                                                                                                  | Eight bit microprocessor data bus. Connected to the                                                                                                                           |

| D[1]                                                                                                                                                | I/O                                                                    | C10                                                                                                                 | four S/UNI-PDH devices, T1XC, and the E1XC data                                                                                                                               |

| D[2]                                                                                                                                                | I/O                                                                    | C11                                                                                                                 | lines.                                                                                                                                                                        |

| D[3]                                                                                                                                                | I/O                                                                    | C12                                                                                                                 |                                                                                                                                                                               |

| D[4]                                                                                                                                                | I/O                                                                    | C13                                                                                                                 |                                                                                                                                                                               |

| D[5]                                                                                                                                                | I/O                                                                    | C14                                                                                                                 |                                                                                                                                                                               |

| D[6]                                                                                                                                                | I/O                                                                    | C15                                                                                                                 |                                                                                                                                                                               |

| D[7]                                                                                                                                                | I/O                                                                    | C16                                                                                                                 |                                                                                                                                                                               |

| D[7]<br>A[0]<br>A[1]<br>A[2]<br>A[3]<br>A[4]<br>A[5]<br>A[6]<br>A[7]<br>A[6]<br>A[7]<br>A[10]<br>A[10]<br>A[11]<br>A[12]<br>A[13]<br>A[14]<br>A[15] | I<br>I<br>I<br>I<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC<br>NC | C16<br>C17<br>C18<br>C19<br>C20<br>C21<br>C22<br>C23<br>C24<br>C25<br>C26<br>C27<br>C28<br>C29<br>C30<br>C31<br>C32 | Sixteen bit microprocessor address bus. Lower eight<br>bits are connected to the S/UNI-PDH devices, T1XC,<br>and E1XC address lines. Higher address lines are<br>unconnected. |

S/UNI-PDH REFERENCE DESIGN

#### Daughterboard SCI-PHY Connector Interface

The Daughterboard SCI-PHY connector is the parallel ATM drop side interface made up of a 96 pin DIN plug connector and is designed to mate with a corresponding connector on the SCI-PHY mother board. It consists of signals required by the SCI-PHY interface. Please refer to the PMC-940212, SATURN COMPLIANT INTERFACE FOR ATM DEVICES document for interface timing details. CMOS signal levels are used on this interface.

| Signal   |                  |     |                                                        |

|----------|------------------|-----|--------------------------------------------------------|

| Name     | Туре             | Pin | Function                                               |

| TDAT[0]  | I                | A1  | Transmit Data. TDAT[7:0] is used to transfer ATM cells |

| TDAT[1]  | I                | A2  | to an ATM PHY daughterboard. TDAT[15:8] are not        |

| TDAT[2]  | I                | A3  | connected.                                             |

| TDAT[3]  | I                | A4  |                                                        |

| TDAT[4]  | I                | A5  |                                                        |

| TDAT[5]  | I                | A6  |                                                        |

| TDAT[6]  | I                | A7  |                                                        |

| TDAT[7]  | I                | A8  |                                                        |

| TDAT[8]  | NC               | A9  |                                                        |

| TDAT[9]  | NC               | A10 |                                                        |

| TDAT[10] | NC               | A11 |                                                        |

| TDAT[11] | NC               | A12 |                                                        |

| TDAT[12] | NC               | A13 |                                                        |

| TDAT[13] | NC               | A14 |                                                        |

| TDAT[14] | NC               | A15 |                                                        |

| TDAT[15] | NC               | A16 |                                                        |

| RDAT[0]  | 0                | A17 | Receive Data. RDAT[8:0] is used to transfer ATM cells  |

| RDAT[1]  | 0                | A18 | from an ATM PHY daughterboard. RDAT[15:8] are not      |

| RDAT[2]  | 0                | A19 | connected.                                             |

| RDAT[3]  | 0                | A20 |                                                        |

| RDAT[4]  | 0                | A21 |                                                        |

| RDAT[5]  | 0<br>0<br>0<br>0 | A22 |                                                        |

| RDAT[6]  |                  | A23 |                                                        |

| RDAT[7]  | 0                | A24 |                                                        |

| RDAT[8]  | NC               | A25 |                                                        |

| RDAT[9]  | NC               | A26 |                                                        |

| RDAT[10] | NC               | A27 |                                                        |

| RDAT[11] | NC               | A28 |                                                        |

| RDAT[12] | NC               | A29 |                                                        |

| RDAT[13] | NC               | A30 |                                                        |

| RDAT[14] | NC               | A31 |                                                        |

| RDAT[15] | NC               | A32 |                                                        |

| GND       | Р        | B1               | Ground.                                                                                              |

|-----------|----------|------------------|------------------------------------------------------------------------------------------------------|

|           |          | to               |                                                                                                      |

|           |          | B23              |                                                                                                      |

| PWR-2V    | NC       | B24              | Not Connected.                                                                                       |

| PWR-4.5V  | NC       | B25              | Not Connected.                                                                                       |

|           |          | to               |                                                                                                      |

|           |          | B28              |                                                                                                      |

| PWR+5V    | Р        | B29              | +5V power.                                                                                           |

|           |          | to<br>B32        |                                                                                                      |

| TFCLK     | -        | <u>Б32</u><br>С1 | Supplies S/UNI-PDH devices with a TFCLK signal up                                                    |

| IFULK     | 1        |                  | to 25 MHz.                                                                                           |

| GND       | P        | C2               | Ground.                                                                                              |

| TSOC      |          | C2<br>C3         | Transmit Start Of Cell. TSOC marks the start of cell on                                              |

| 1300      | 1        | 03               | the TDAT bus. TSOC drives all S/UNI-PDH devices'                                                     |

|           |          |                  | TSOC input.                                                                                          |

| TXPRTY[0] | -        | C4               | Transmit Parity. TXPRTY[0] drives all S/UNI-PDH                                                      |

|           | ľ        | 04               | devices' TXPRTY input.                                                                               |

| TXPRTY[1] | NC       | C5               | Not connected                                                                                        |

| TCA1      | 0        | C6               | Transmit cell available. Connected to S/UNI-PDH                                                      |

| -         | -        |                  | device 1 TCA output.                                                                                 |

| TCA2      | 0        | C7               | Transmit cell available. Connected to S/UNI-PDH                                                      |

|           |          |                  | device 2 TCA output.                                                                                 |

| TCA3      | 0        | C8               | Transmit cell available. Connected to S/UNI-PDH                                                      |

|           |          |                  | device 3 TCA output.                                                                                 |

| TCA4      | 0        | C9               | Transmit cell available. Connected S/UNI-PDH                                                         |

|           |          |                  | device 4 TCA output.                                                                                 |

| TWREN1B   | 1        | C10              | The Transmit Write Enable. TWREN1B drives the                                                        |

|           |          |                  | TWRENB signal of S/UNI-PDH device 1.                                                                 |

| TWREN2B   |          | C11              | The Transmit Write Enable. TWREN2B drives the                                                        |

|           |          |                  | TWRENB signal of S/UNI-PDH device 2.                                                                 |

| TWREN3B   |          | C12              | The Transmit Write Enable. TWREN3B drives the                                                        |

|           |          |                  | TWRENB signal of S/UNI-PDH device 3.                                                                 |

| TWREN4B   |          | C13              | The Transmit Write Enable. TWREN4B drives the                                                        |

|           |          | 011              | TWRENB signal of S/UNI-PDH device 4.                                                                 |

| PD2_MISO  | NC       | C14              | Not connected                                                                                        |

| PD3_MOSI  | NC<br>P  | C15              | Not connected                                                                                        |

| GND       | <u>۲</u> | C16              | Ground.                                                                                              |

| RFCLK     | μ        | C17              | Receive FIFO clock. RFCLK is used to synchronize                                                     |

|           |          |                  | data transfer transactions from the ATM PHY                                                          |

|           |          |                  | daughterboard. RFCLK supplies a 25 MHz clock and is connected to all S/UNI-PDH devices' RFCLK input. |

| GND       | P        | C18              | Ground.                                                                                              |

| טאפ       | Г        |                  | Ground.                                                                                              |

| RSOC      | 0  | C19 | Receive Start Of Cell. RSOC marks the start of cell on<br>the RDAT bus. When RSOC is high, the first word of<br>the cell structure should be present on the RDAT bus.<br>RSOC is sampled on the rising edge of RFCLK and is<br>considered valid only when RRDENB is<br>simultaneously asserted. RSOC is connected to each<br>S/UNI-PDH devices' RSOC output. |

|-----------|----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXPRTY[0] | 0  | C20 | Receive parity. RXPRTY[0] should indicate the parity<br>of the RDAT[7:0] bus. RXPRTY[0] is connected to all<br>S/UNI-PDH devices' RXPRTY output.                                                                                                                                                                                                             |

| RXPRTY[1] | NC | C21 | Not Connected                                                                                                                                                                                                                                                                                                                                                |

| RCA1      | 0  | C22 | Receive Cell Available. RCA1 is used by an ATM<br>physical layer device to indicate when it can provide<br>a full cell. RCA1 is connected to the S/UNI-PDH<br>device 1 RCA output.                                                                                                                                                                           |

| RCA2      | 0  | C23 | Receive Cell Available. RCA2 is used by an ATM<br>physical layer device to indicate when it can provide<br>a full cell. RCA2 is connected to the S/UNI-PDH<br>device 2 RCA output.                                                                                                                                                                           |

| RCA3      | 0  | C24 | Receive Cell Available. RCA3 is used by an ATM<br>physical layer device to indicate when it can provide<br>a full cell. RCA3 is connected to the S/UNI-PDH<br>device 3 RCA output.                                                                                                                                                                           |

| RCA4      | 0  | C25 | Receive Cell Available. RCA4 is used by an ATM<br>physical layer device to indicate when it can provide<br>a full cell. RCA4 is connected to the S/UNI-PDH<br>device 4 RCA output.                                                                                                                                                                           |

| RRDEN1B   | I  | C26 | The Receive Read Enable. RRDEN1B is connected to<br>S/UNI-PDH device 1 RRDENB input.                                                                                                                                                                                                                                                                         |

| RRDEN2B   | I  | C27 | The Receive Read Enable. RRDEN2B is connected to<br>S/UNI-PDH device 2 RRDENB input.                                                                                                                                                                                                                                                                         |

| RRDEN3B   | I  | C28 | The Receive Read Enable. RRDEN3B is connected to<br>S/UNI-PDH device 3 RRDENB input.                                                                                                                                                                                                                                                                         |

| RRDEN4B   | I  | C29 | The Receive Read Enable. RRDEN4B is connected to<br>S/UNI-PDH device 4 RRDENB input.                                                                                                                                                                                                                                                                         |

| PD4_SCLK  |    | C30 | Not connected                                                                                                                                                                                                                                                                                                                                                |

| PD5_SS    | NC | C31 | Not connected                                                                                                                                                                                                                                                                                                                                                |

| BUS8      | NC | C32 | Not connected                                                                                                                                                                                                                                                                                                                                                |

S/UNI-PDH REFERENCE DESIGN

#### Line Interface Signals

The S/UNI-PDH EVBD contains four S/UNI-PDH devices that operate with four different line interface formats. These input and output signals are transformer isolated.

| Signal+ | Signal- | Description                |

|---------|---------|----------------------------|

| TXDS1P  | TXDS1N  | DS1 balanced TX outputs.   |

| RXDS1P  | RXDS1N  | DS1 balanced RX inputs.    |

| TXE1P   | TXE1N   | E1 balanced TX outputs.    |

| RXE1P   | RXE1N   | E1 balanced RX inputs.     |

| TXDS3P  | TXDS3N  | DS3 unbalanced TX outputs. |

| RXDS3N  | RXDS3N  | DS3 unbalanced RX inputs.  |

| TXE3P   | TXE3N   | E3 unbalanced TX outputs.  |

| RXE3P   | RXE3N   | E3 unbalanced RX inputs.   |

#### Header Descriptions

Several jumper terminals are used as test headers to test and monitor certain S/UNI-PDH EVBD signal lines. CMOS signal levels are used for all inputs and outputs.

#### Header J4 (page 2 of schematics)

Header J4 is a 5 row by 2 column header whose function is to monitor signals common to the four S/UNI-PDH devices. The selection of operating modes is given in the OPERATION section. The signals on the header are described in the next table.

| Signal | PIN # | Description                                                                                    |

|--------|-------|------------------------------------------------------------------------------------------------|

| TFCLK  | 1     | ATM Transmit FIFO clock. Clock for transferring ATM                                            |

|        |       | parallel data into the S/UNI-PDH devices.                                                      |

| +5V    | 2     | Power                                                                                          |

| RFCLK  | 3     | ATM Receive FIFO clock. Clock for transferring ATM parallel data out of the S/UNI-PDH devices. |

| +5V    | 4     | Power                                                                                          |

| TSOC   | 5     | Transmit start of Cell. TSOC marks the start of cell on                                        |

|        |       | the TDAT data bus.                                                                             |

| GND    | 6     | Ground                                                                                         |

| RSOC   | 7     | Receive start of cell. RSOC marks the start of cell on                                         |

|        |       | the RDAT data bus.                                                                             |

| GND    | 8     | Ground                                                                                         |

| IRQB   | 9     | Maskable interrupt to the controlling microprocessor                                           |

|        |       | via the microprocessor interface.                                                              |

| GND    | 10    | Ground                                                                                         |

<sup>©</sup> PM7545 S/UNI-PDH-EVBD

PRELIMINARY INFORMATION, Issue 2, January 11, 1995

S/UNI-PDH REFERENCE DESIGN

#### Headers J13, J12, J9, J20 (pages 3, 4, 5, 6 of schematics)

Headers J13, J12, J9, J20 are 8 row by 2 column headers. These headers are described together because they serve identical functions for each S/UNI-PDH device. They are used to monitor HDLC signals as well as TICLK and LCD for the four S/UNI-PDH devices. They are also used to bring an external source of 8 kHz signal via EXTC13 for C13/CADD generation, and to control the TSEN input for each S/UNI-PDH device. J13 services S/UNI-PDH device 1, J12 is for device 2, J9 is for device 3, and J20 is for device 4. The signals on the headers are described in the next table. Note that each signal has an \* at the end of its name. When referring to a specific signal on the header for a S/UNI-PDH device, just replace the \* with the S/UNI-PDH device number (1 to 4).

| Signal  | PIN # | Description                                                                                                                                                               |

|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND     | 1     | Ground                                                                                                                                                                    |

| TDLSIG* | 2     | HDLC transmit data input to S/UNI-PDH.                                                                                                                                    |

| GND     | 3     | Ground                                                                                                                                                                    |

| TDLCLK* | 4     | HDLC transmit data clock.                                                                                                                                                 |

| GND     | 5     | Ground                                                                                                                                                                    |

| TSEN*   | 6     | Tristate enable for RDAT bus, RXPRTY, and RSOC<br>pins. When TSEN is a logic 0 RDAT bus, RXPRTY,<br>and RSOC are always active and are forced to digital<br>logic values. |

| GND     | 7     | Ground                                                                                                                                                                    |

| RDLCLK* | 8     | HDLC receive data clock.                                                                                                                                                  |

| GND     | 9     | Ground                                                                                                                                                                    |

| RDLSIG* | 10    | HDLC receive data output from S/UNI-PDH.                                                                                                                                  |

| GND     | 11    | Ground                                                                                                                                                                    |

| EXTC13* | 12    | External source for 8 kHz signal for C13/CADD generation.                                                                                                                 |

| GND     | 13    | Ground                                                                                                                                                                    |

| TICLK*  | 14    | TICLK is the S/UNI-PDH transmission system baud clock.                                                                                                                    |

| GND     | 15    | Ground                                                                                                                                                                    |

| LCD*    | 16    | Loss of Cell Delineation indication. LCD transitions to a logic 1 when an out of cell delineation is found.                                                               |

<sup>©</sup> PM7545 S/UNI-PDH-EVBD

PRELIMINARY INFORMATION, Issue 2, January 11, 1995

S/UNI-PDH REFERENCE DESIGN

#### Headers J11, J10, J7, J14 (pages 3, 4, 5, 6 of schematics)

Headers J11, J10, J7, J14 are 20 pin headers. These headers are described together because they serve identical functions for each S/UNI-PDH device. They are used to monitor PLCP as well as overhead stuff signals for the four S/UNI-PDH devices. They are also used to bring external PLCP and overhead stuff signals to each S/UNI-PDH device. These headers are also used to monitor LOF, OOF, TCELL, RCELL, TCA, and RCA for each S/UNI-PDH device. J11 services S/UNI-PDH device 1, J10 is for device 2, J7 is for device 3, and J14 is for device 4. The signals on the header are described in the next table. Note that each signal has an \* at the end of its name. When refering to a specific signal on the header for a S/UNI-PDH device, just replace the \* with the S/UNI-PDH device number (1 to 4).

| Signal    | PIN #    | Description                                                                                                   |

|-----------|----------|---------------------------------------------------------------------------------------------------------------|

| XTOHCLK*  | 1        | Buffered transmit overhead clock. XTOH*,                                                                      |

|           |          | XTOHINS*, are sampled on the rising edge of                                                                   |

|           |          | XTOHCLK*                                                                                                      |

| XTOHFP*   | 2        | Buffered transmit overhead frame position. XTOHFP*                                                            |

|           |          | is updated on the falling edge of XTOHCLK*.                                                                   |

| XTOHINS*  | 3        | Buffered transmit overhead insertion. Controls                                                                |

|           |          | insertion of overhead bit into XTOH* stream.                                                                  |

| XTOH*     | 4        | Buffered transmit overhead data. Contains overhead                                                            |

|           |          | bits that are inserted into DS3, E3 transmit streams.                                                         |

| XTPOHCLK* | 5        | Buffered transmit PLCP overhead clock. XTPOH*,                                                                |

|           |          | and XTPOHINS* are sampled on the rising edge of                                                               |

|           |          | XTPOHCLK*.                                                                                                    |

| XTPOHFP*  | 6        | Buffered transmit PLCP overhead frame position.                                                               |

|           |          | XTPOHFP* is updated on the falling edge of                                                                    |

|           |          | XTPOHCLK*.                                                                                                    |

| XTPOHINS* | 1        | Buffered transmit PLCP overhead insertion. Controls                                                           |

|           |          | insertion of PLCP overhead bits into XTPOH* stream.                                                           |

| XTPOH*    | 8        | Buffered transmit PLCP overhead data. Contains                                                                |

|           |          | PLCP overhead bits that are inserted into the                                                                 |

|           |          | transmit PLCP frame.                                                                                          |

| TCELL*    | 9        | Transmit cell indication. TCELL* Pulses once for                                                              |

|           | 4.0      | every ATM cell transmitted.                                                                                   |

| TCA*      | 10       | Transmit cell available. TCA* is a logic 1 when the                                                           |

|           |          | cell based transmit FIFO is empty. It is a logic 0 when                                                       |

|           |          | the FIFO contains cells.                                                                                      |

| RCELL*    | 11       | Receive cell indication. RCELL* pulses once for                                                               |

| RCA*      | 10       | every ATM cell received.                                                                                      |

| KUA"      | 12       | Receive cell available. RCA* is a logic 1 when the<br>cell based received FIFO contains at least one cell. It |

|           |          |                                                                                                               |

|           | <u> </u> | is logic 0 when the FIFO is empty (or nearly empty).                                                          |

PMC-Sierra, Inc. PM7545 S/UNI-PDH-EVBD

PRELIMINARY INFORMATION, Issue 2, January 11, 1995

|           | -  |                                                                                                                        |

|-----------|----|------------------------------------------------------------------------------------------------------------------------|

| LOF*      | 13 | PLCP Loss of frame. LOF* is asserted to a logic 1 while the PLCP receiver is in a loss of frame state.                 |

| OOF*      | 14 | PLCP Out of frame. OOF* is asserted to a logic 1 while the PLCP receiver is in a loss of frame state.                  |

| XRPOHFP*  | 15 | Buffered receive PLCP overhead frame position.<br>XRPOHFP* is updated on the falling edge of<br>XRPOHCLK*.             |

| XRPOHCLK* | 16 | Buffered receive PLCP overhead clock. XRPOHFP*<br>and XRPOH* are updated on the falling edge of<br>XRPOHCLK*.          |

| XRPOH*    | 17 | Buffered receive PLCP overhead data. Contains<br>PLCP overhead bits that are extracted from the<br>receive PLCP frame. |

| XROHFP*   | 18 | Buffered receive overhead frame position. XROHFP* is updated on the falling edge of XROHCLK*.                          |

| XROHCLK*  | 19 | Buffered receive overhead clock. XROH*, and<br>XROHFP*, are updated on the falling edge of<br>XROHCLK*                 |

| XROH*     | 20 | Buffered receive overhead data. Contains overhead bits that are extracted from DS3, E3 receive streams.                |

PM7545 S/UNI-PDH-EVBD

PRELIMINARY INFORMATION, Issue 2, January 11, 1995

S/UNI-PDH REFERENCE DESIGN

#### Headers J16, J17, J19 (page 6 of schematics)

Headers J16, J17, J19 are 14 pin headers. These headers are used to put S/UNI-PDH device 4 into either normal ATM bus mode or ATM Loopback mode. A 14 row by 2 column jumper block is used to short across headers J16 and J19 for normal ATM bus mode. A jumper block is used to short headers J17 and J16 for ATM Loopback mode. The following table describes signals on J16. J16 signals connect directly to inputs on S/UNI-PDH device 4 TDAT bus side.

| Signal   | PIN # | Description                                                                                 |  |

|----------|-------|---------------------------------------------------------------------------------------------|--|

| TFCLK4   | 1     | ATM Transmit FIFO clock. Clock for transferring ATM parallel data into S/UNI-PDH devices 4. |  |

| RFCLK4   | 2     | ATM Receive FIFO clock. Clock for transferring ATM parallel data out of S/UNI-PDH device 4. |  |

| TDAT4(0) | 3     | Parallel ATM transmit data bus bit 0.                                                       |  |

| TDAT4(1) | 4     | Parallel ATM transmit data bus bit 1.                                                       |  |

| TDAT4(2) | 5     | Parallel ATM transmit data bus bit 2.                                                       |  |

| TDAT4(3) | 6     | Parallel ATM transmit data bus bit 3.                                                       |  |

| TDAT4(4) | 7     | Parallel ATM transmit data bus bit 4.                                                       |  |

| TDAT4(5) | 8     | Parallel ATM transmit data bus bit 5.                                                       |  |

| TDAT4(6) | 9     | Parallel ATM transmit data bus bit 6.                                                       |  |

| TDAT4(7) | 10    | Parallel ATM transmit data bus bit 7.                                                       |  |

| TSOC4    | 11    | Transmit start of cell. Marks start of cell on TDAT4 bus.                                   |  |

| TXPRTY4  | 12    | Transmit parity. Indicates parity on TDAT4 bus.                                             |  |

| TWREN4B4 | 13    | Transmit write enable. Used to enable write TDAT bus data to S/UNI-PDH device 4 only.       |  |

| RRDEN4B4 | 14    | Receive Read output enable. Enables read data onto RDAT bus for S/UNI-PDH device 4 only.    |  |

S/UNI-PDH REFERENCE DESIGN

The following table describes signals on J17. J17 signals are connected to J16 inputs on S/UNI-PDH device 4 TDAT bus side in Loopback mode with shorting jumpers.

| Signal  | PIN # | Description                                                                                 |

|---------|-------|---------------------------------------------------------------------------------------------|

| NC      | 1     | Not connected. This pin is left open for external                                           |

|         |       | TFCLK source to be connected in Loopback mode.                                              |

| NC      | 2     | Not connected. This pin is left open for external                                           |

|         |       | source of RFCLK to be connected in Loopback                                                 |

|         |       | mode.                                                                                       |

| RDAT(0) | 3     | Parallel ATM receive data bus bit 0. Connected to                                           |

|         |       | TDAT4(0) in Loopback mode.                                                                  |

| RDAT(1) | 4     | Parallel ATM receive data bus bit 1. Connected to                                           |

|         |       | TDAT4(1) in Loopback mode.                                                                  |

| RDAT(2) | 5     | Parallel ATM receive data bus bit 2. Connected to                                           |

|         |       | TDAT4(2) in Loopback mode.                                                                  |

| RDAT(3) | 6     | Parallel ATM receive data bus bit 3. Connected to                                           |

|         |       | TDAT4(3) in Loopback mode.                                                                  |

| RDAT(4) | 7     | Parallel ATM receive data bus bit 4. Connected to                                           |

|         |       | TDAT4(4) in Loopback mode.                                                                  |

| RDAT(5) | 8     | Parallel ATM receive data bus bit 5. Connected to                                           |

|         |       | TDAT4(5) in Loopback mode.                                                                  |

| RDAT(6) | 9     | Parallel ATM receive data bus bit 6. Connected to                                           |

|         |       | TDAT4(6) in Loopback mode.                                                                  |

| RDAT(7) | 10    | Parallel ATM receive data bus bit 7. Connected to                                           |

|         |       | TDAT4(7) in Loopback mode.                                                                  |

| RSOC    | 11    | Receive start of cell. Marks start of cell on RDAT bus.                                     |

|         |       | This signal is connected to TSOC4 in Loopback                                               |

|         | -10   | mode.                                                                                       |

| RXPRTY  | 12    | Receive parity. Indicates parity on RDAT bus. This                                          |

|         | 4.0   | signal is connected to TXPRTY4 in Loopback mode.                                            |

| BRCA4   | 13    | Inverted Receive Cell Available. Indicates when a                                           |

|         |       | cell is available for output on the RDAT bus.                                               |

| BTCA4   | 14    | Connected to TWREN4B4 in Loopback mode.<br>Inverted Transmit Cell Available. Indicates when |

|         | 14    |                                                                                             |

|         |       | transmit cell FIFO is empty. Connected to<br>RRDEN4B4 in Loopback mode.                     |

|         |       |                                                                                             |

S/UNI-PDH REFERENCE DESIGN

The following table describes signals on J19. J19 signals are normally connected to J16 inputs on S/UNI-PDH device 4 TDAT bus side with shorting jumpers.

| Signal  | PIN # | Description                                                                                                              |  |

|---------|-------|--------------------------------------------------------------------------------------------------------------------------|--|

| TFCLK   | 1     | ATM Transmit FIFO clock. Clock for transferring ATM<br>parallel data into S/UNI-PDH device 4 from SCI-PHY<br>connector.  |  |

| RFCLK   | 2     | ATM Receive FIFO clock. Clock for transferring ATM parallel data out of S/UNI-PDH device 4 to SCI-PHY connector.         |  |

| TDAT(0) | 3     | Parallel ATM transmit data bus bit 0 from SCI-PHY connector.                                                             |  |

| TDAT(1) | 4     | Parallel ATM transmit data bus bit 1 from SCI-PHY connector.                                                             |  |

| TDAT(2) | 5     | Parallel ATM transmit data bus bit 2 from SCI-PHY connector.                                                             |  |

| TDAT(3) | 6     | Parallel ATM transmit data bus bit 3 from SCI-PHY connector.                                                             |  |

| TDAT(4) | 7     | Parallel ATM transmit data bus bit 4 from SCI-PHY connector.                                                             |  |

| TDAT(5) | 8     | Parallel ATM transmit data bus bit 5 from SCI-PHY connector.                                                             |  |

| TDAT(6) | 9     | Parallel ATM transmit data bus bit 6 from SCI-PHY connector.                                                             |  |

| TDAT(7) | 10    | Parallel ATM transmit data bus bit 7 from SCI-PHY connector.                                                             |  |

| TSOC    | 11    | Transmit start of cell. Marks start of cell on TDAT bus.                                                                 |  |

| TXPRTY  | 12    | Transmit parity. Indicates parity on TDAT bus from SCI-PHY connector.                                                    |  |

| TWREN4B | 13    | Transmit write enable. Used to enable a write of TDAT bus data to S/UNI-PDH device 4 from SCI-PHY connector.             |  |

| RRDEN4B | 14    | Receive Read output enable. Enables a read of data<br>onto RDAT bus on the SCI-PHY connector from<br>S/UNI-PDH device 4. |  |

"" PM7545 S/UNI-PDH-EVBD

PRELIMINARY INFORMATION, Issue 2, January 11, 1995

S/UNI-PDH REFERENCE DESIGN

### Headers J21 (page 7 of schematics)

Headers J21 is a 17 pin header. This header is a used to test and monitor signals connected to the PM4341 T1XC T1 framer transceiver. The following table describes signals on J21.

| Signal   | PIN # | Description                                                                                                                                                   |  |

|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GND      | 1     | Ground                                                                                                                                                        |  |

| T1BRFPI  | 2     | Backplane frame pulse input. This signal is used to frame align the received data to the system backplane. It is pulled up with 10 kohms.                     |  |

| T1BRCLK  | 3     | Backplane Receive clock. This input can be fed with<br>a 1.544 MHz clock. It is pulled up with 10 kohms.                                                      |  |

| T1RDLCLK | 4     | Receive data link clock. This output is the clock for the HDLC receiver T1RDLSIG signal.                                                                      |  |

| T1RDLSIG | 5     | Receive data link signal. This output is the HDLC receiver data signal.                                                                                       |  |

| T1RDN    | 6     | Receive Digital Negative Line Pulse. This input can receive the negative phase NRZ or RZ line receive data stream. It is pulled up with 10 kohms.             |  |

| T1RDP    | 7     | Receive Digital Positive Line Pulse. This input can receive the positive phase NRZ or RZ line receive data stream. It is pulled up with 10 kohms.             |  |

| T1BRSIG  | 8     | Backplane Receive Signalling. The T1BRSIG output contains extracted signalling bits for each channel in the receive frame.                                    |  |

| T1BRPCM  | 9     | Backplane Receive PCM. This output contains the recovered receive line data stream.                                                                           |  |

| T1BRFPO  | 10    | Backplane Frame Pulse Output. This output indicates the frame alignment of the T1BRPCM data stream.                                                           |  |

| T1RCLKI  | 11    | Receive Line Clock Input. This input can be an externally recovered 1.544 MHz clock used to sample the T1RDP and T1RDN inputs. It is pulled up with 10 kohms. |  |

| T1TDLSIG | 12    | Transmit Data Link Signal. HDLC transmit data is<br>input to this pin to be inserted in the line transmit<br>stream. It is pulled up with 10 kohms.           |  |

| T1TDLCLK | 13    | Transmit Data Link Clock. This input provides<br>clocking for the T1TDLSIG signal.                                                                            |  |

| T1TDN    | 14    | Transmit Digital Negative Line Pulse. This output represents the negative phase line transmit data stream with RZ or NRZ CMOS levels.                         |  |

| T1TDP    | 15    | Transmit Digital Positive Line Pulse. This output represents the positive phase line transmit data stream with RZ or NRZ CMOS levels.                         |  |

| T1TCLKO | 16 | Transmit Clock Output. The T1TDP, and T1TDN outputs can be clocked on the rising or falling edge of T1TCLKO. |

|---------|----|--------------------------------------------------------------------------------------------------------------|

| T1TCLKI | 17 | Transmit Clock Input.This input can be used to generate the TCLKO signal. It is pulled up with 10 kohms.     |

PM7545 S/UNI-PDH-EVBD

PRELIMINARY INFORMATION, Issue 2, January 11, 1995

S/UNI-PDH REFERENCE DESIGN

#### Headers J15 (page 8 of schematics)

Headers J15 is a 17 pin header. This header is a used to test and monitor signals connected to the PM6341 E1XC E1 framer transceiver. The following table describes signals on J15.

| Signal     | PIN # | Description                                                                                                                                                              |  |

|------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GND        | 1     | Ground                                                                                                                                                                   |  |

| E1BRFPI    | 2     | Backplane Frame Pulse Input. This signal is used to frame align the received data to the system backplane. It is pulled up with 10 kohms.                                |  |

| E1BRCLK    | 3     | Backplane Receive Clock. This input can be fed with a 2.048 MHz clock. It is pulled up with 10 kohms.                                                                    |  |

| RFP        | 4     | Receive Frame Pulse. This output indicates frame alignment of the RDPCM data stream.                                                                                     |  |

| E1RDLCLK   | 5     | Receive Data Link Clock. This is the output clock for the HDLC receiver E1RDLSIG signal.                                                                                 |  |

|            | 6     | Receive Data Link Signal. This is the HDLC receiver data signal output.                                                                                                  |  |

| RDPCM_RPCM |       | Recovered Decoded PCM. This output is the recovered receive PCM data stream.                                                                                             |  |

|            | 8     | Receive Digital Negative Line Pulse. This input can receive the negative phase NRZ or RZ line receive data stream. It is pulled up with 10 kohms.                        |  |

| E1RDP      | 9     | Receive Digital Positive Line Pulse. This input can receive the positive phase NRZ or RZ line receive data stream. It is pulled up with 10 kohms.                        |  |

| E1BRSIG    | 10    | Backplane Receive Signalling. The E1BRSIG output<br>contains extracted signalling bits for each channel in<br>the receive frame.                                         |  |

| E1RCLKI    | 11    | Receive Line Clock Input. This input could be an<br>externally recovered 2.048 MHz clock used to<br>sample the E1RDP and E1RDN inputs. It is pulled up<br>with 10 kohms. |  |

| E1TDLSIG   | 12    | Transmit Data Link Signal. HDLC transmit data is input to this pin to be inserted in the line transmit stream. It is pulled up with 10 kohms.                            |  |

| E1TDLCLK   | 13    | Transmit Data Link Clock. This input provides<br>clocking for the E1TDLSIG signal.                                                                                       |  |

| E1TDN      | 14    | Transmit Digital Negative Line Pulse. This output represents the negative phase line transmit data stream with RZ or NRZ CMOS levels.                                    |  |

S/UNI-PDH REFERENCE DESIGN

| E1TDP   | 15 | Transmit Digital Positive Line Pulse. This output represents the positive phase line transmit data stream with RZ or NRZ CMOS levels. |

|---------|----|---------------------------------------------------------------------------------------------------------------------------------------|

| E1TCLKO | 16 | Transmit Clock Output. The E1TDP, and E1TDN outputs can be clocked on the rising or falling edge of E1TCLKO.                          |

| E1TCLKI | 17 | Transmit Clock Input.This input can be used to generate the TCLKO signal. It is pulled up with 10 kohms.                              |

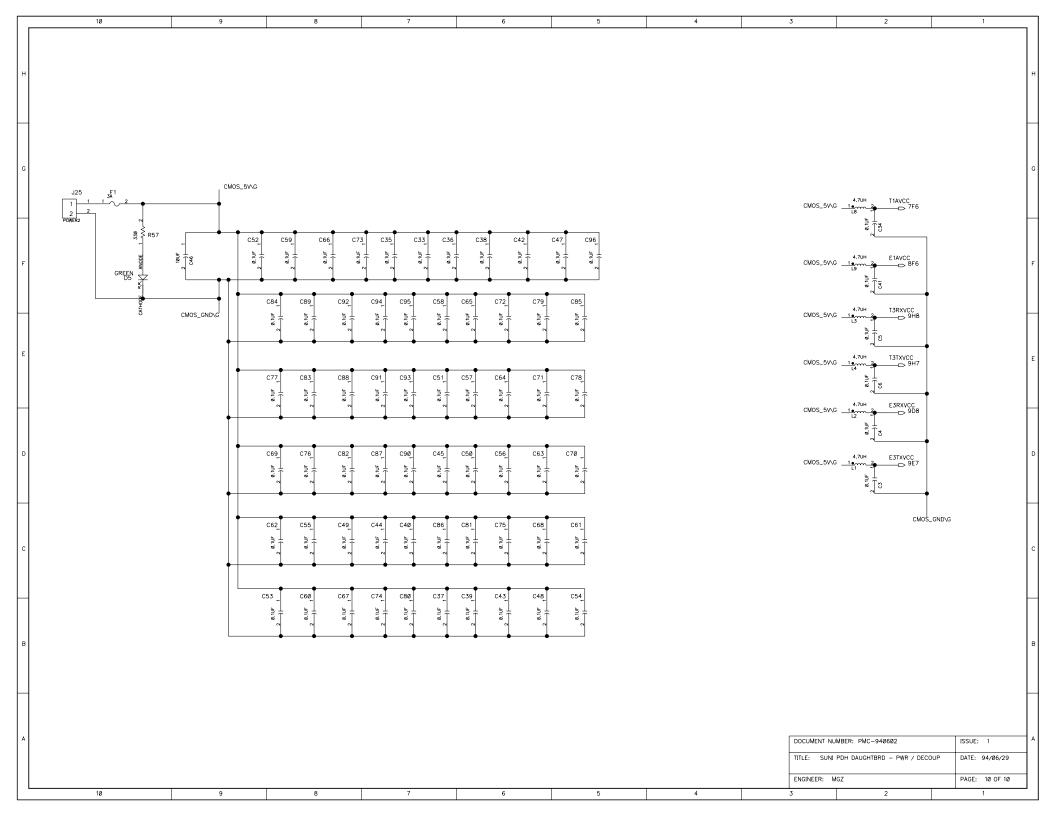

#### Power Connector

A supply of +5V and ground is normally provided by the SCI-PHY EVBD via the 96 pin DIN connectors when the SCI-PHY EVBD is attached to the S/UNI-PDH EVBD. When the S/UNI-PDH EVBD is used in Loopback mode, a 2 position barrier strip power connector, J25 (on schematic page 10), is provided to supply +5V and ground to the board. The +5V connection is fused with a 3 Amp quick blow fuse (F1). J25 connections are listed in the next table.

| Signal | PIN # | Description |

|--------|-------|-------------|

| GND    | 1     | Ground      |

| +5V    | 2     | Power       |

PM7545 S/UNI-PDH-EVBD

PRELIMINARY INFORMATION, Issue 2, January 11, 1995

S/UNI-PDH REFERENCE DESIGN

# **OPERATION**