PM4344 TQUAD

Quadruple T1 Framer

# PM4344 TQUAD

## TQUAD with QDSX Reference Design

Issue 1: June, 1996

ISSUE 1

Quadruple T1 Framer

#### **CONTENTS**

| REFERENCES                                       | 1   |

|--------------------------------------------------|-----|

| OVERVIEW                                         | 2   |

| FUNCTIONAL DESCRIPTION                           | 3   |

| Block Diagram                                    | 3   |

| PM4344 TQUAD                                     | 4   |

| PM4314 QDSX                                      | 5   |

| PIC16C74 Microcontroller                         | 6   |

| Dual-Port RAM                                    | 6   |

| IMPLEMENTATION DESCRIPTION                       | 8   |

| Address Decode/Demultiplex Logic                 | .8  |

| PIC16C74 Microcontroller                         | 8   |

| Dual-Port RAM                                    | .14 |

| TQUAD Functional Block                           | 15  |

| QDSX Functional Block                            |     |

| Line Interface Circuitry                         |     |

| Timing Distribution                              | .16 |

| Header Blocks                                    |     |

| 96-Pin Connector                                 |     |

| APPENDIX A: DESIGN CONSIDERATIONS                | 20  |

| Power Supply Voltage Transients                  |     |

| Ground Noise                                     | 20  |

| Noise-Bypassing at Power Pins                    |     |

| Values of Noise-Bypassing Capacitors             |     |

| Placement of Noise-Bypassing Capacitors          |     |

| Ferrite Beads                                    |     |

| Unused CMOS Inputs                               |     |

| APPENDIX B: MATERIAL LIST                        |     |

| APPENDIX C: SCHEMATICS                           | 25  |

| APPENDIX D: FIRMWARE DESCRIPTION AND SOURCE CODE | 26  |

| CONTACTING PMC-SIERRA                            | 27  |

| NOTES                                            | .28 |

### REFERENCES

- American National Standards for Telecommunications, ANSI T1.107 (1988), "Digital Hierarchy - Formats Specifications"

- American National Standards for Telecommunications, ANSI T1.107 (Draft 1995), "Digital Hierarchy - Formats Specifications"

- American National Standards for Telecommunications, ANSI T1.231 (1993), "Digital Hierarchy - Layer 1 In-Service Digital Transmission Performance Monitoring"

- American National Standards for Telecommunications, ANSI T1.403 (1994), "Network-to-Customer Installation — DS1 Metallic Interface"

- Integrated Device Technology, Data Book (1995), "Specialized Memories, FIFOs & Modules"

- International Telecommunications Union, Recommendation G.703 (1991), "Physical/Electrical Characteristics of Hierarchical Digital Interfaces"

- International Telecommunications Union, Recommendation G.704 (1991), "Synchronous Frame Structures Used at Primary and Secondary Hierarchical Levels"

- Microchip Technology Inc., Data Book (1994)

- PMC-Sierra, PMC-950857, Data Book (Issue 3), "PM4314 QDSX Quadruple T1/E1 Line Interface Device"

- PMC-Sierra, PMC-940910, Data Book (Issue 4), "PM4344 TQUAD Quadruple T1 Framer"

Quadruple T1 Framer

### OVERVIEW

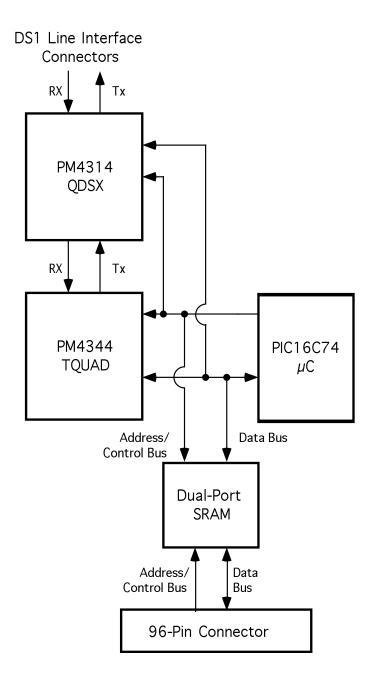

This document describes an implementation of a design based on both PMC-Sierra's PM4344 TQUAD and PM4314 QDSX devices. The TQUAD with QDSX Reference Design embodies PMC-Sierra's guidelines and suggestions for designing a four port DSX-1 interface card.

In addition to the PM4344 TQUAD and PM4314 QDSX devices, the TQUAD with QDSX Reference Design incorporates an on-board microcontroller (Microchip PIC16C74) for providing the local maintenance functions — including termination of the ESF datalink in the DS1 overhead.

The TQUAD with QDSX Reference Design communicates with the host system using a 96-pin connector. The pin-out of this connector is compatible for connection with the PMC-Sierra's PM1501 Evaluation Motherboard, but is intended to be a generic 8-bit microprocessor interface to a multiplexed bus.

The host does not have a direct connection to the microprocessor port of the TQUAD or QDSX. Rather, a dual-port RAM, shared by the host and the local PIC16C74, is used to pass control and status information about the TQUAD and QDSX to and from the host — the actual register accesses to the TQUAD and QDSX are performed by the PIC16C74. The host system and PIC16C74 also communicate through the "mailbox" communication channels in the dual-port RAM.

The advantage to this architecture is that the host system is not burdened by the lowlevel monitoring and control functions related to the physical layer.

ISSUE 1

Quadruple T1 Framer

### FUNCTIONAL DESCRIPTION

#### **Block Diagram**

Quadruple T1 Framer

#### PM4344 TQUAD

The PM4344 Quadruple T1 Framer (TQUAD) is a feature-rich device suitable for use in many T1 systems with a minimum of external circuitry. Each of the framers and transmitters is independently software-configurable, allowing feature selection without changes to external wiring.

On the receive side, the TQUAD can be configured to frame to any of the common DS-1 signal formats: SF, ESF, T1DM (DDS), or SLC®96. The TQUAD also supports detection of various alarm conditions such as loss of signal, pulse density violation, red alarm, yellow alarm, and AIS alarm. The TQUAD detects and indicates the presence of yellow and AIS patterns and also integrates yellow, red, and AIS alarms as per industry specifications.

Performance monitoring with accumulation of CRC-6 errors, framing bit errors, line code violations, and loss of frame events is provided. The TQUAD also detects the presence of in-band loopback codes, ESF bit-oriented codes, and detects and terminates HDLC messages on the ESF data link. An elastic store for slip buffering and rate adaptation is provided, as is a signaling extractor that supports signaling debounce, signaling freezing, idle code substitution, digital milliwatt tone substitution, data inversion, and signaling bit fixing — all on a per-channel basis. Receive-side data and signaling trunk conditioning is also provided.

On the transmit side, the TQUAD generates framing for SF, ESF, and T1DM (DDS) DS1 formats, or framing can be optionally disabled. The transmission of SLC®96 format is not supported in this design. The TQUAD supports signaling insertion, idle code substitution, digital milliwatt tone substitution, data inversion, and zero code suppression — all on a per-channel basis. The zero code suppression is selectable to Bell (bit 7), GTE, or DDS standards, and can also be disabled. Transmit-side data and signaling trunk conditioning is provided.

The TQUAD can also generate in-band loopback codes, ESF bit oriented codes, and transmit HDLC messages on the ESF data link. The TQUAD can generate a low jitter transmit clock and provides a FIFO for transmit jitter attenuation. When not used for jitter attenuation, the full or empty status of this FIFO is made available to facilitate higher order multiplexing applications by controlling bit-stuffing logic.

The TQUAD provides a parallel microprocessor interface for controlling the operation of the TQUAD device. Serial PCM interfaces allow 1.544 Mbit/s or 2.048 Mbit/s backplanes to be directly supported. Tolerance of gapped clocks allows other backplane rates to be supported with a minimum of external logic.

For a complete description of the TQUAD, please refer to PMC-Sierra's TQUAD databook (document number PMC-940910).

Quadruple T1 Framer

#### PM4314 QDSX

The PM4314 QDSX Quad T1/E1 Line Interface Device is a monolithic integrated circuit that supports DSX-1 and CEPT E1 compatible transmit and receive interfaces for four 1.544 Mbit/s or 2.048 Mbit/s data streams.

In the receive direction, clock and data are recovered from the received signal using a digital phase-locked loop that provides excellent high frequency jitter accommodation. The recovered data is decoded using B8ZS, HDB3, or AMI line code rules. Loss of signal and line code violations are detected. Line code violations are accumulated in internal counters.

In the transmit direction, each quadrant of the QDSX can transmit either a DS-1/E1 stream encoded using B8ZS, HDB3, or AMI line code rules. The digital data is converted to high drive, dual rail RZ pulses that drive the DSX-1/E1 interface through a coupling transformer. The shape of the pulses is programmable to ensure that the DSX-1/E1 pulse template is met after the signal is passed through different cable lengths or types. Driver performance monitoring is provided and can generate interrupts upon driver failure.

A jitter attenuation function comprised of a digital phase-locked loop and data FIFO is available for use in either the transmit or receive path of each channel.

Diagnostic loopback is provided and the loopback may be invoked past the analog transmit outputs using the driver performance monitors or invoked prior to the conversion to analog. Line loopback with jitter attenuation is provided and may be enabled for automatic operation based on detected inband loopback codes.

The QDSX detects framed or unframed inband loopback code sequences from the received input pulses. Any arbitrary code from three to eight bits in length can be declared to be the activate and deactivate codes by writing to configuration registers. The inband loopback code detector can optionally be moved to the transmit side where it detects inband loopback codes in the unipolar input transmit data stream. For framed inband loopback code sequences, it is expected that the framing bit overwrites the inband loopback code bit.

The QDSX may insert unframed inband loopback code sequences (programmable codes from three to eight bits in length) into the transmit or receive path of each channel. The QDSX detects framed or unframed inband loopback code sequences in either the transmit or receive path of each channel. Two arbitrary codes can be searched for simultaneously, each programmable between three to eight bits in length.

The QDSX may insert an unframed  $2^{15}$ -1 O.151 compatible pseudo-random bit sequence into the transmit or receive path of each channel. The QDSX can detect an unframed  $2^{15}$ -1 O.151 compatible pseudo-random bit sequence in either the transmit or receive path of each channel.

The QDSX operates in conjunction with external line coupling transformers, resistors, and capacitors. An external crystal oscillator may be used for high speed timing generation. The QDSX is configured, controlled, and monitored using registers that are accessed via a generic microprocessor interface. If microprocessor access is not available, the QDSX may be configured through hardware pins.

Internal high speed timing for all quadrants of the QDSX is provided by a common 37.056 MHz or 49.152 MHz master clock. This master clock rate is required for applications where QDSX provides jitter attenuation.

For a complete description of the QDSX, please refer to PMC-Sierra's QDSX Data Book (document number PMC-950857).

#### PIC16C74 Microcontroller

The Microchip PIC16C74 is a low-cost, high-performance, CMOS, fully-static EPROMbased 8-bit microcontroller. It employs a Harvard RISC-like architecture with 14-bit instruction words. Its two stage instruction pipeline allows most instructions to be executed in a single cycle. The PIC16C74 has enhanced core features, an eight-level deep stack, and multiple internal and external interrupt sources.

The PIC16C74 has 192 bytes of on-chip RAM and a 4k by 14-bit EPROM for program memory.

It has 33 I/O pins, each of which can source/sink 25mA.

The PIC16C74 also has a number of peripheral features (A/D converters, timer/counters, capture/compare/PWM modules, and two serial ports) which are not used in this reference design.

In the TQUAD with QDSX Reference Design, the PIC16C74 is devoted to the local maintenance functions for the DS1 transmission (including termination of the ESF datalinks, if active).

The program firmware is described in Appendix D. The firmware was developed in Assembly language using Microchip's PC-hosted symbolic assembler, MPASM, available free from Microchip's bulletin board (MCHIPBBS on Compuserve). Also available free from Microchip is a C compiler and a simulator. The PIC16C74 can be programmed on universal programmers from Sprint and Data I/O. Additionally, Microchip sells programmers for this device.

#### Dual-Port RAM

This a high-speed 2K by 8-bit dual-port static RAM with internal interrupt logic for interprocessor communications. Many manufacturers (such as Integrated Device Technology, and Cypress Semiconductors) produce pin-compatible versions of this device. **REFERENCE DESIGN**

PM4344 TQUAD

#### ISSUE 1

Quadruple T1 Framer

The dual-port RAM has two independent ports with separate control, address and data pins that permit independent, asynchronous access for both reads and writes to any location in memory.

Depending on the functionality required, a memory map is defined to pass status and control information between the host and the local PIC16C74. This memory map is discussed further in the firmware description in Appendix D.

Quadruple T1 Framer

### IMPLEMENTATION DESCRIPTION

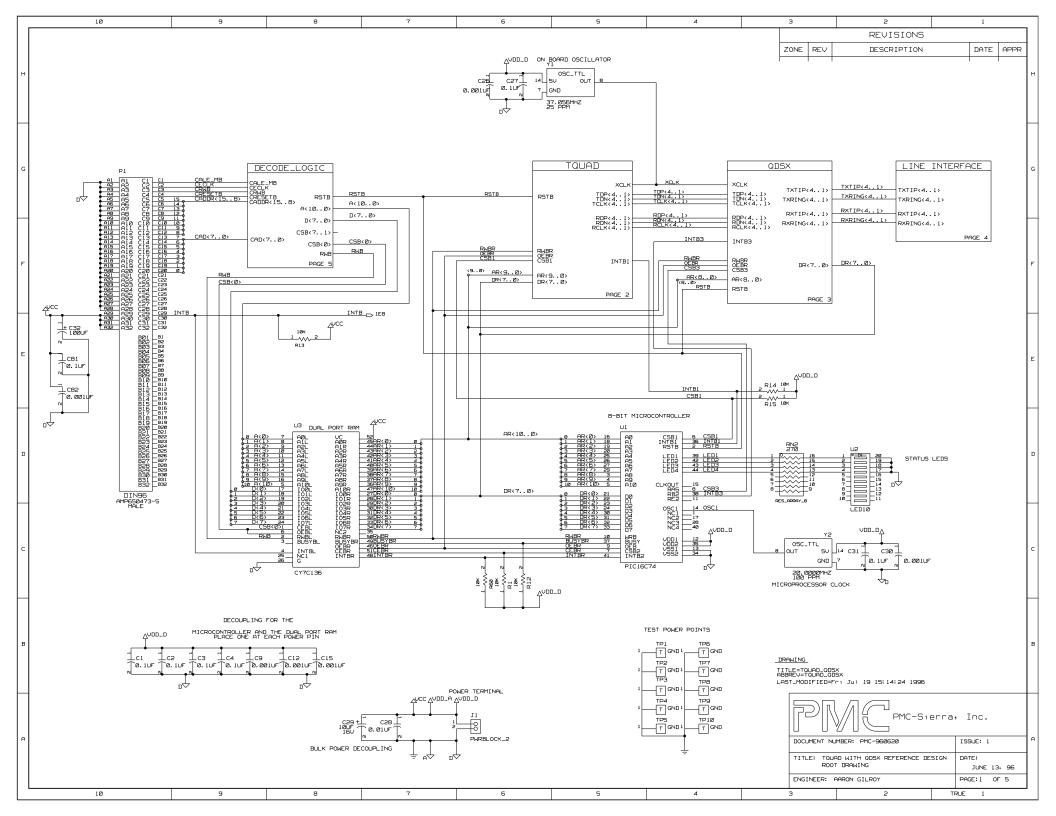

The schematic diagram of the TQUAD with QDSX Reference Design is contained in Appendix E. This section explains that schematic diagram.

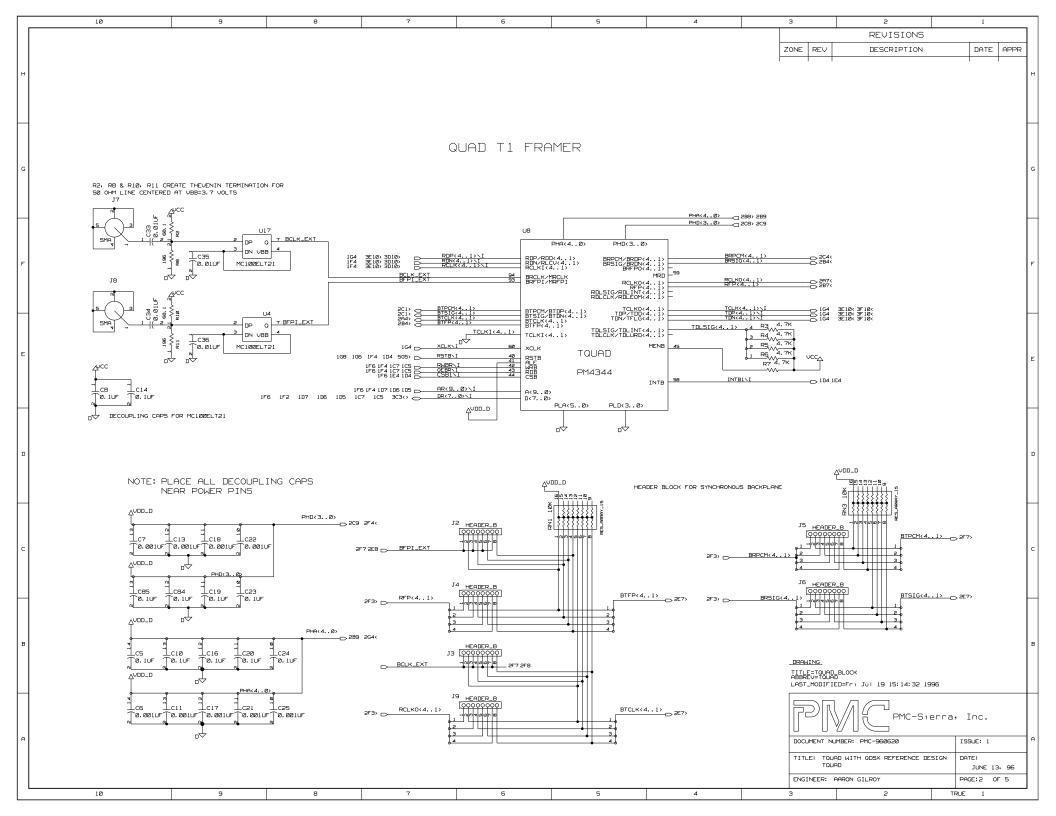

The TQUAD with QDSX Reference Design schematic shows six main functional blocks: address decode/demultiplex logic, a PIC16C74 microcontroller, dual-port RAM, a PM4344 TQUAD, a PM4314 QDSX, and line interface circuitry. Additionally, the schematic contains connectors, timing sources and miscellaneous "glue" circuitry. Each functional block is described below.

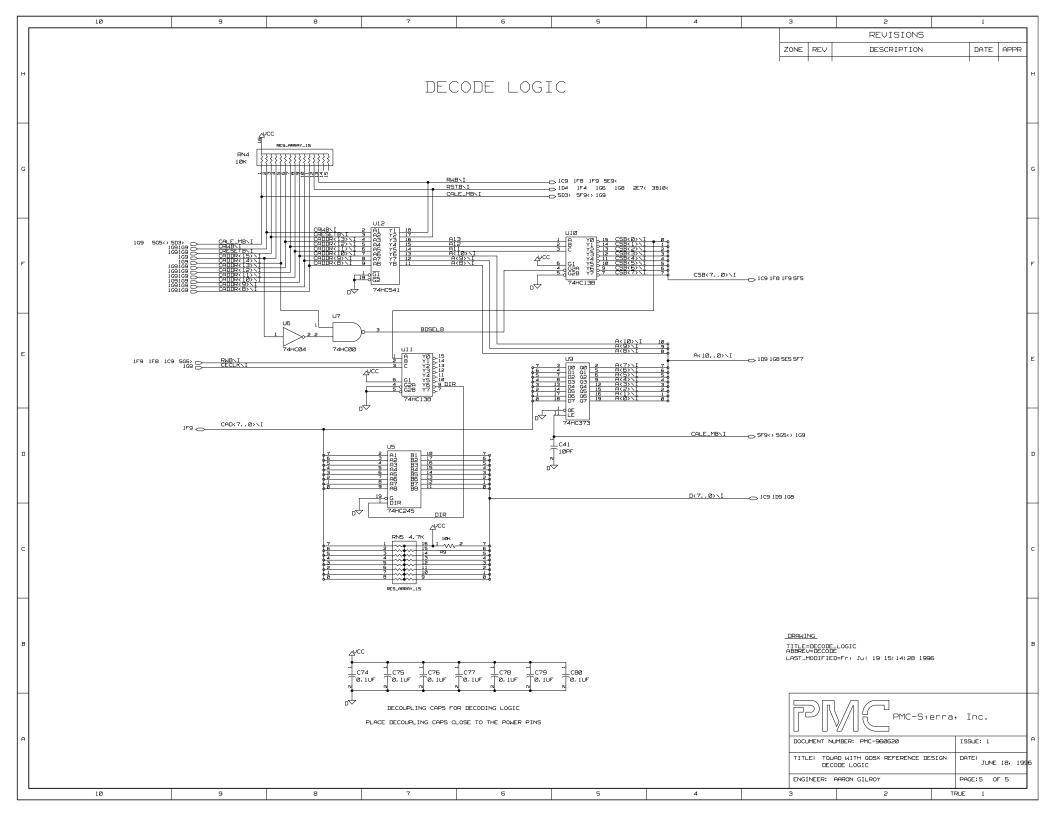

#### Address Decode/Demultiplex Logic

The DECODE\_LOGIC functional block provides the chip select decoding of the address on the microprocessor bus. Additionally, this block de-multiplexes the AD[7:0] address/data lines from the 96-pin connector interface. The DECODE\_LOGIC functional block buffers the remaining signals, and pulls up any that are tristateable.

The chip selects control access to the dual-port RAM. The outputs of the DECODE\_LOGIC functional block go to the Left Port of the dual-port RAM.

The host cannot directly address the TQUAD or QDSX. Rather, the dual-port RAM mailbox register must be used to pass a command to the PIC16C74 to initiate a register access.

#### PIC16C74 Microcontroller

This subsection explains the connections and considerations concerning use of the PIC16C74 to provide the local maintenance functions on the TQUAD with QDSX Reference Design.

#### Interrupt Handling

The only efficient way of processing events that may have a low frequency of occurrence is to use interrupt-driven routines (instead of polling). The events (alarm conditions, timers, datalink servicing, and dual-port mailbox events) on the TQUAD, QDSX and the dual-port RAM will, on average, be low frequency. Therefore, the PIC16C74 firmware developed for this reference design is based on an interrupt-driven scheme.

When the PIC16C74 detects an interrupt indication on its external interrupt input pins, it has to determine the source of the interrupt — first by polling its internal interrupt source register to determine if it was the TQUAD, QDSX or the dual-port RAM that interrupted. If it was the TQUAD or QDSX, then the appropriate device's registers need to be polled to determine what event caused the interrupt.

#### ISSUE 1

Once the PIC16C74 has determined the interrupt source, it can jump to a routine specific to that interrupt. Below, brief descriptions are given of service routines for each type of interrupt source. The full description is reserved for Appendix D, which contains a full source listing of Assembly language firmware that can be used to implement these service routines. The source code can be assembled using Microchip's PC-hosted symbolic assembler, MPASM, available free from Microchip's bulletin board (MCHIPBBS on Compuserve).

#### **External Memory Accesses**

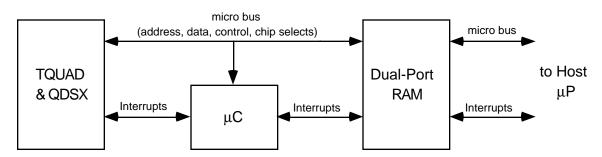

The PIC16C74 does not have a microprocessor bus suitable to access registers and memory within the TQUAD, QDSX and dual-port RAM. Therefore I/O pins on the PIC16C74 are defined to act as the address bus, data bus, chip selects, RDB, WRB and other signals necessary. Since the PIC16C74 is only accessing two external devices, it generates the chip selects instead of relying on external decode logic. Figure 1 shows a block diagram of the connections.

#### Figure 1. Block Diagram of PIC16C74 Connections

The firmware includes subroutines that operate dedicated I/O pins as the micro bus during external accesses. Since the interrupt service routines will alternate between accessing the TQUAD, QDSX and the dual-port RAM, it saves instruction cycles to have separate subroutines dedicated to each, where the address would be taken from different pre-defined registers. There are six access routines: RD\_TQUAD, RD\_QDSX, RD\_RAM, WR\_TQUAD, WR\_QDSX and WR\_RAM. All four routines share a common Data register so that data transfers could be optimized. The micro bus is put in high-impedance (all pins configured as inputs) when the bus was not being used.

The full description is reserved for Appendix D, which contains a full source listing of Assembly language firmware that can be used to implement these service routines.

#### Initialization

The firmware initializes the TQUAD and QDSX to enable the appropriate interrupts, set the framing format, configure the interfaces, set the timing options, and initialize the HDLC serial controllers.

#### REFERENCE DESIGN

#### ISSUE 1

The dual-port RAM is initialized so that the vectors and pointers are in their default state. Additionally, a loop is used to verify the memory (write, read back, compare, then clear all the memory locations).

Lastly, the initialization routine enables the interrupts within the PIC16C74, and falls into a main loop.

The full description is reserved for Appendix D, which contains a full source listing of Assembly language firmware that can be used to implement these service routines.

#### Datalink Service Routines (RFDL/XFDL)

The ESF facility datalink is a 4kbps channel provided for three functions: a remote alarm indication (Yellow Alarm), a bit-oriented code FEAC channel, and an HDLC datalink. The Yellow Alarm and FEAC procession are explained in the "Maintenance Functions" subsection below. This subsection explains the HDLC processing.

The PM4344 TQUAD provides detection and generation of the HDLC packet overhead, by using its internal RFDL and XFDL functional blocks. The RFDL and XFDL functional blocks can generate interrupt indications on the common INTB output.

The procedure for handling the interrupts from the RFDL and XFDL blocks is explained in the "Operations" section of the TQUAD databook (p. 183-92 in Issue 4). At a minimum, the service routines will have to perform the three steps detailed in the TQUAD databook. Added to these steps would be house-keeping operations in the dual-port RAM to inform the host of the datalink status.

The full description is reserved for Appendix D, which contains a full source listing of Assembly language firmware that can be used to implement these service routines.

#### Maintenance Functions

There are a number of maintenance functions specified in ANSI T1.107, T1.231, and T1.403. These include Yellow Alarm, Alarm Indication Signal, Loopbacks, and Performance Reports. All of these functions can be handled via interrupts from the TQUAD, as described in the following subsections. The full description is reserved for Appendix D, which contains a full source listing of Assembly language firmware that can be used to implement these service routines.

Note: Each quadrant within the TQUAD has independent registers for maintenance functions. Below, where specific registers are referred to, the address is for the first quadrant; the other quadrants would be accessed via their equivalent registers.

Quadruple T1 Framer

#### YELLOW ALARM

A DS1 Yellow Alarm should be indicated to the remote DS1 equipment in response to a out-of-frame condition, or receipt of an AIS defect. In SF format, the Yellow Alarm consists of forcing Bit 2 of every DS0 channel to a logic 0; in ESF format, the Yellow Alarm consists of sending eight ones followed by eight zeros repeatedly over the facility datalink channel.

The simplest implementation is to set the XYEL bit in Register 044H (or equivalent) to logic one when an INFRI interrupt occurs with INFR=0 (in Register 022H and equivalent). The XYEL bit should be cleared to logic zero when an INFRI interrupt occurs where INFR=1.

#### ALARM INDICATION SIGNAL (AIS)

The AIS should be sent upon loss of originating signal, or when any action is taken that would cause a service disruption (such as some loopbacks).

The firmware will not automatically transmit AIS in response to any condition. If AIS transmission is desired, the XAIS bit in Register 045H (or equivalent) should be set to logic one by the host (using the mailbox communication channel in the dual-port RAM).

#### LOOPBACKS

Loopbacks are used by carriers and customers as a maintenance tool to aid problem resolution. The carrier uses loopbacks for trouble isolation, and the customer uses them for CI-to-CI testing.

There are two loopbacks defined by ANSI T1.403: Line and Payload. In SF, only Line Loopback is applicable, but in ESF, both loopbacks apply.

Both Line and Payload loopbacks are supported in the TQUAD.

#### Superframe (SF) Loopbacks

In SF, loopbacks are controlled by in-band signaling. There are two in-band codes defined: Loopback Activate and Loopback Deactivate. The Loopback Activate code is a framed "00001..." repeating pattern. The Loopback Deactivate code is a framed "001..." repeating pattern. The IBCD TSB in the TQUAD or QDSX can be configured (during initialization) to look for these patterns and interrupt when one is detected. In response to these interrupts, the service routine should enable or disable Line Loopback with the LINELB bit in Register 00AH (or equivalent) of the TQUAD or Register 005H (or equivalent) of the QDSX.

Quadruple T1 Framer

#### Extended Superframe (ESF) Loopbacks

In ESF, loopbacks are controlled by bit-oriented codes sent over the facility datalink. (Note some provisions are made for framed or unframed in-band codes to control ESF Line Loopbacks.) There are six bit-oriented codes defined relating to loopbacks:

- Line-Loopback-Activate: 00001110 1111111

Line-Loopback-Deactivate: 00111000 11111111

Payload-Loopback-Activate: 00010100 11111111

- Payload-Loopback-Deactivate:

- Universal-Loopback-Deactivate:

- Loopback-Retention:

The RBOC TSB in the TQUAD can detect any valid bit-oriented code, generating an interrupt when one is detected or removed.

The Line Loopback should not be activated until the Line-Loopback-Activate code is removed, so that the activate code is not looped back to the NI. Payload Loopback can be activated immediately on detection of the Payload-Loopback-Activate code since the datalink is regenerated — hence the bit-oriented codes will not be looped back.

The deactivation for both loopbacks can be accomplished in several ways:

- upon detection of the Universal-Loopback-Deactivate code

- upon detection of AIS

- upon the receipt of two occurrences of the one-second performance report messages separated by uninterrupted IDLE code.

Additionally, the Loopback-Retention code is optionally sent in framed test signals during loopbacks as a positive confirmation of the presence of a Line Loopback.

#### Performance Monitoring

All the performance monitoring parameters required by ANSI T1.231 are available within registers of the TQUAD and QDSX. Therefore, with a timer interrupt setting the accumulation interval, the PIC16C74 can transfer all the performance monitoring indicators and parameters to known memory locations in the dual-port RAM. The host system could then process these parameters.

Additionally, ANSI T1.403 specifies that a performance report should be sent once each second using a bit-assigned structure within a LAPD packet transmitted over the facility datalink.

ISSUE 1

Quadruple T1 Framer

Therefore, a timer interrupt is enabled within the microcontroller to interrupt once each second. The service routine for the timer interrupt collects the required performance parameters (detailed below) and constructs a packet in the Transmit Channel Memory. It initiates the transmission of the first byte of the packet in the associated XFDL TSB, and relies on the datalink service routines to transmit the remainder of the packet.

The performance report packet is 15 octets long, including the opening and closing LAPD Flags. The format is:

| Octet No.       | Octet Contents | Interpretation                    |

|-----------------|----------------|-----------------------------------|

| 1               | 01111110       | Opening LAPD Flag                 |

| 2               | 00111000       | From CI: SAPI=14, C/R=0, EA=0     |

|                 | 00111010       | From NI: SAPI=14, C/R=1, EA=0     |

| 3               | 0000001        | TEI=0, EA=1                       |

| 4               | 00000011       | Unacknowledged Frame              |

| 5, 6            | Variable       | Data for latest second (T')       |

| 7, 8            | Variable       | Data for previous second (T'-1)   |

| 9, 10           | Variable       | Data for earlier second (T'-2)    |

| 11, 12          | Variable       | Data for earlier second (T'-3)    |

| 13, 14 Variable |                | CRC-16 Frame Check Sequence (FCS) |

| 15              | 01111110       | Closing LAPD Flag                 |

The format for each second's two octets of data (transmitted right to left) is:

| Octet No.    | Bit Definition |    |    |    |    |    |    |    |

|--------------|----------------|----|----|----|----|----|----|----|

| 5, 7, 9, 11  | G3             | LV | G4 | U1 | U2 | G5 | SL | G6 |

| 6, 8, 10, 12 | FE             | SE | LB | G1 | R  | G2 | Nm | NI |

| Where | G1=1 | indicates | that | exactly | one | CRC | Error | Event | occurred | during | the |

|-------|------|-----------|------|---------|-----|-----|-------|-------|----------|--------|-----|

|       |      | interval, |      |         |     |     |       |       |          |        |     |

- G2=1 indicates that between two and five (inclusive) CRC Error Events occurred during the interval,

- G3=1 indicates that between six and ten (inclusive) CRC Error Events occurred during the interval,

- G4=1 indicates that between 11 and 100 (inclusive) CRC Error Events occurred during the interval,

- G5=1 indicates that between 101 and 319 (inclusive) CRC Error Events occurred during the interval,

- G6=1 indicates that more than 319 CRC Error Events occurred during the interval,

SE=1 indicates that one or more Severely Errored Framing Events occurred during the interval,

- FE=1 indicates that one or more Frame Sync Bit Error Events occurred during the interval,

- LV=1 indicates that one or more Line Code Violation Events occurred during the interval,

- SL=1 indicates that one or more Line Code Violation Events occurred during the interval,

- LB=1 indicates that Payload Loopback is active,

- U1, U2=0 under study for synchronization,

- R=0 Reserved

- NmNI One-second report modulo-4 counter

#### Dual-Port Mailboxes

The dual-port RAM contains two mailboxes, one in each direction, for passing data between the two ports. When the micro bus on one port writes a data byte to a specified location, the other port is interrupted. Using these mailboxes, a proprietary messaging scheme can be arranged for diagnostic operations. These interrupts from the dual-port RAM must be processed by the PIC16C74.

For example, a useful feature is to allow the host system to peek and poke registers within the TQUAD and QDSX devices (which is not in directly in the host address space). A simple protocol would be that the host would write a byte to the mailbox indicating that it wishes to perform a Read or Write, as well as putting the address and, if necessary, data within pre-defined locations within the dual-port RAM. Then, when the PIC16C74 services the mailbox indicating that the access has been completed.

#### Dual-Port RAM

The dual-port RAM is shared by the host system and the local PIC16C74 microcontroller. The PIC16C74 performs all the local maintenance functions (including termination of the facility datalink), while the dual-port RAM is used to pass information to and from the host system. This arrangement greatly reduces the real-time burden on the host system, allowing the host to interact with the TQUAD with QDSX Reference Design at a higher level than direct access to the individual physical layer devices.

The dual-port RAM holds, as a minimum, the following information:

- packets received by the TQUAD over the ESF facility datalink

- packets to be transmitted by the TQUAD over the ESF facility datalink, including T1.403 performance reports constructed by the PIC16C74.

- status of the TQUAD and QDSX. This includes performance monitoring indications and parameters as specified in ANSI T1.231.

The TQUAD with QDSX Reference Design has been given 2 kbytes of space starting at 4000H.

REFERENCE DESIGN

PM4344 TQUAD

#### ISSUE 1

Quadruple T1 Framer

The two ports on the dual-port RAM are denoted the "Left" and "Right" ports. In this design, the Left Port is connected to the 100-pin connector which carries the host microprocessor bus (which is decoded, de-multiplexed and buffered on the D3MX Module). The Right Port is connected to the PIC16C74's microprocessor bus (shared with the microprocessor port of the TQUAD and QDSX).

The two ports are entirely independent from each other and allow asynchronous Read and Write accesses from either port.

Each port also has an interrupt indication line used for processing a "mailbox" communications channel within the dual-port RAM. Each port has a memory location, which, when it is written to, alerts the other port via the interrupt indication signal. Therefore, a protocol can be used to pass information through these mailboxes. Uses of this communications channels include:

- allowing the host to "peek" and "poke" registers in the TQUAD and QDSX,

- initiating different configuration routines, and

- initiating different diagnostic routines.

#### TQUAD Functional Block

The TQUAD is a full-featured quadruple DS1 framer which provides most standard DS1 framing functions and performance monitoring.

The full register set of the TQUAD, including Test Mode registers are accessible to the PIC16C74 block. For a full description of these registers, refer to the TQUAD Data Book.

The backplane signals of the TQUAD are connected to header blocks. In a real application, these signals would be further processed. The header blocks are arranged to allow easy physical (payload) loopbacks on the TQUAD with QDSX Reference Design.

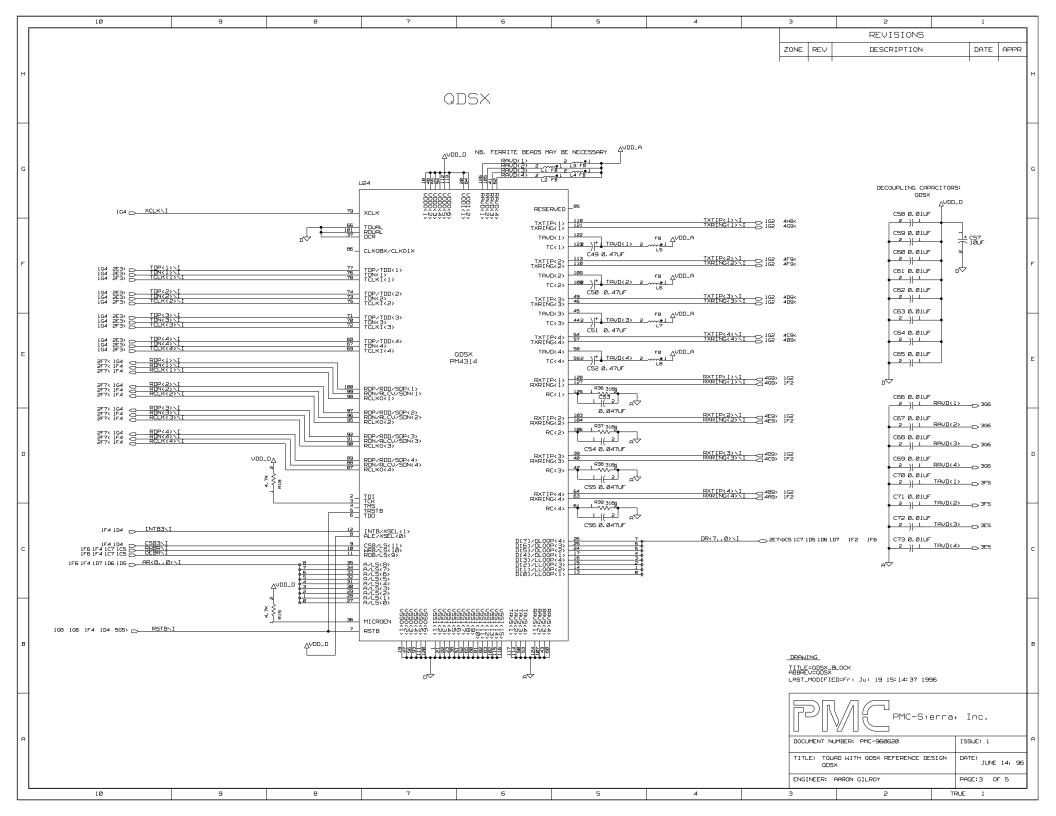

#### **QDSX Functional Block**

The QDSX is a full-featured quadruple T1/E1 line interface unit which provides a G.703compliant interface for 1544 kbit/s and 2048 kbit/s rates.

The full register set of the QDSX, including Test Mode registers are accessible to the PIC16C74 block. For a full description of these registers, refer to the QDSX Data Book.

In this reference design, the QDSX is being used solely to provide a DSX-1 interface for the four duplex DS-1 serial data streams.

Although the QDSX supports a stand-alone mode in which it does not need a microprocessor interface, that mode is not used in this reference design.

Quadruple T1 Framer

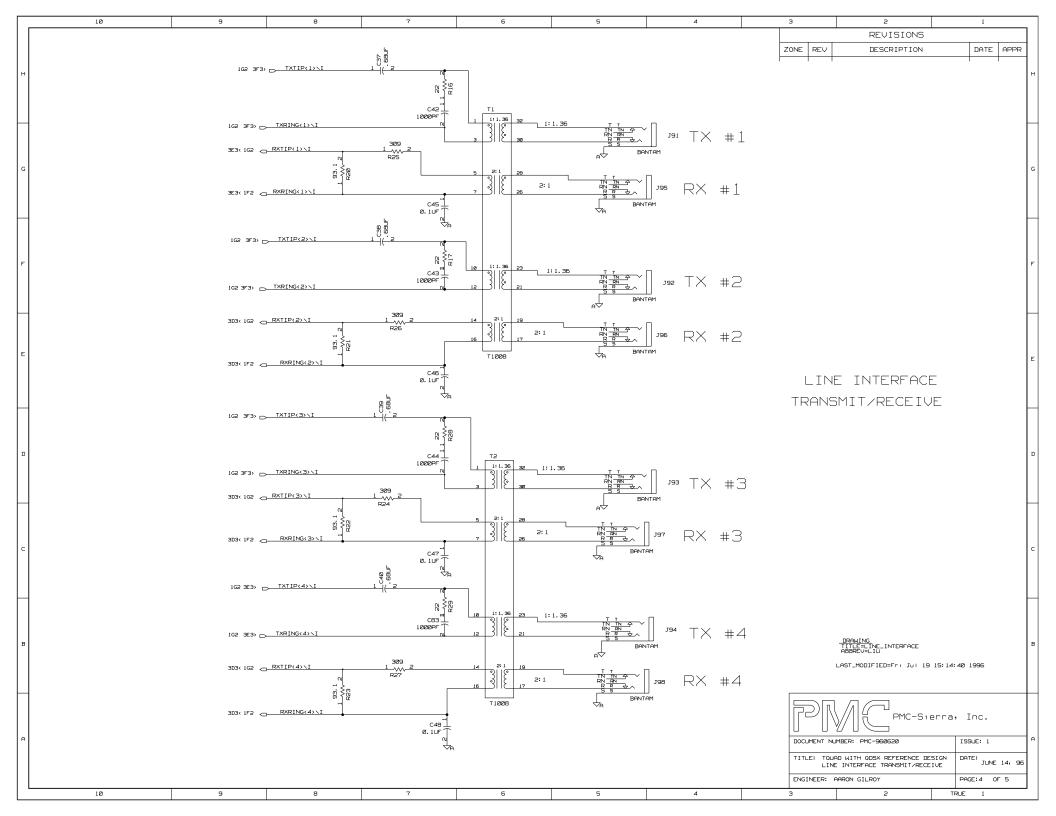

#### Line Interface Circuitry

The line interface circuitry consists of the transformers, connectors and passive networks necessary to interface the QDSX device to cables carrying G.703-compliant 1544 kbit/s signals. This circuitry reflects recommendations in the QDSX data book.

The transformer shown is a new product, the T1008 from Pulse Engineering. Other manufacturers which produce suitable transformers are BH Electronics, Filtran, Midcom, and Schott. The characteristics of the transformer should match those recommended in the QDSX data book.

#### Timing Distribution

The high-speed timing to both the TQUAD and QDSX devices is sourced from a 37.056 MHz crystal oscillator.

The high-speed timing to the PIC16C74 is sourced from a 20.0 MHz crystal oscillator.

There are also two SMA connectors for providing two signals, BCLK\_EXT and BFPI\_EXT, to source the backplane timing signals to the TQUAD. The BCLK\_EXT clock signal can be 1.544 MHz, 2.048 MHz, 12.352 MHz or 16.384 MHz depending on the backplane format chosen for the TQUAD. The BFPI\_EXT frame pulse signal must be a valid frame pulse meeting the timing requirements of the BRFPI, BTFP, MRFP or MTFP (depending on the ones used) inputs of the TQUAD as specified in the TQUAD data book.

In this reference design, the BCLK\_EXT and BFPI\_EXT signals are shown going through MC100ELT21 PECL-to-TTL converters. This is done to provide an easy interface to frequency synthesizers in PMC-Sierra's in-house laboratories. In customer applications, the BCLK\_EXT and BFPI\_EXT signal could be sourced directly from a TTL-compatible clock source.

Additionally, there are header blocks available which can be jumpered to provide looptiming of the backplane to the receive timing.

#### Header Blocks

To keep this reference design generic, the backplane signals of the TQUAD are not processed but rather brought out to headers for observation and as a point for interconnection. In a customer applications, these signals would be further processed as appropriate (e.g. DS0 cross-connection, frame relay, ATM, etc.).

The following signals are brought to headers:

• BRPCM[4:1] are the four Backplane Receive PCM serial data streams.

- BRSIG[4:1] are the four Backplane Receive Signaling serial data streams which indicate the extracted robbed-bit signaling information of each PCM timeslot on BRPCM.

- RFP[4:1] are the four Receive Frame Pulse Outputs which indicate the frame alignment found within the associated receive serial stream.

- BFPI\_EXT is an external frame pulse for controlling the frame alignment of the TQUAD's synchronous backplane, provided via an SMA connector.

BFPI\_EXT is common to all of the quadrants within the TQUAD due to its connection to the BRFPI input.

- RCLKO[4:1] are the four Receive Clock Outputs. If an Elastic Store (ELST) within the TQUAD is bypassed, then the associated BRPCM and BRSIG signals are timed to this clock.

- BTCLK[4:1] are the four Backplane Transmit Clock inputs.

- BCLK\_EXT is an external clock for controlling the timing of the TQUAD's synchronous backplane, provided via an SMA connector. BCLK\_EXT is common to the receive backplane of all the quadrants within the TQUAD due to its connection to the BRCLK input.

For more detailed information on the use of these signals, refer to the TQUAD data book.

The headers are physically arranged to facilitate physical loopbacks. Each backplane receive PCM stream can be looped back by physically connecting the BRPCM[n] and BRSIG[n] signals to BTPCM[n] and BRSIG[n] respectively. Additionally, either the RCLKO[n] or the BRCLK\_EXT signal should be connected to BTCLK[n] (depending whether the ELST is bypassed or not).

#### 96-Pin Connector

The 96-pin connector interface carries all the signals required to connect the TQUAD with QDSX Reference Design to a host 8-bit multiplexed microprocessor bus.

The connector is a 96-pin female connector, with the pin defined as described in the table below (only 64 of the pins are used). This connector was chosen because it is compatible with the PMC-Sierra PM1501 Evaluation Motherboard (described in PMC-910501).

Signals are provided for a Motorola-type multiplexed microprocessor bus (including interrupts, and a hardware RESET signal). Additionally, power and ground are provided through this connector. TTL signal levels are assumed on this interface.

In the following table the signal type is one of: I (input), O (output), I/O (bi-directional), N/C (no-connect), PWR (power), or GND (ground). The direction of the signal is with reference to this design.

ISSUE 1

Quadruple T1 Framer

| Signal<br>Name | Туре | Pin | Function                                                                                                                                                                                                                            |

|----------------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE            | Ι    | C1  | Address latch enable. When high, identifies that address is valid on AD[7:0]. This signal is used for de-multiplexing the microprocessor bus.                                                                                       |

| E              | I    | C2  | External data access indication. Active high.                                                                                                                                                                                       |

| RWB            | I    | C3  | Active low write enable, active high read enable                                                                                                                                                                                    |

| RSTB           | I    | C4  | Active low hardware RESET. This is connected to<br>all devices providing a hardware RESET pin.<br>After a hardware RESET, the D3MX Module<br>should be re-initialized unless operating in stand-<br>alone mode (no microprocessor). |

| A[15]          | I    | C5  | Address bus bit 15                                                                                                                                                                                                                  |

| A[14]          | I    | C6  | Address bus bit 14                                                                                                                                                                                                                  |

| A[13]          | I    | C7  | Address bus bit 13                                                                                                                                                                                                                  |

| A[12]          | I    | C8  | Address bus bit 12                                                                                                                                                                                                                  |

| A[11]          | I    | C9  | Address bus bit 11                                                                                                                                                                                                                  |

| A[10]          | I    | C10 | Address bus bit 10                                                                                                                                                                                                                  |

| A[9]           | I    | C11 | Address bus bit 9                                                                                                                                                                                                                   |

| A[8]           | I    | C12 | Address bus bit 8                                                                                                                                                                                                                   |

| AD[7]          | I/O  | C13 | Multiplexed address/data bus bit 7                                                                                                                                                                                                  |

| AD[6]          | I/O  | C14 | Multiplexed address/data bus bit 6                                                                                                                                                                                                  |

| AD[5]          | I/O  | C15 | Multiplexed address/data bus bit 5                                                                                                                                                                                                  |

| AD[4]          | I/O  | C16 | Multiplexed address/data bus bit 4                                                                                                                                                                                                  |

| AD[3]          | I/O  | C17 | Multiplexed address/data bus bit 3                                                                                                                                                                                                  |

| AD[2]          | I/O  | C18 | Multiplexed address/data bus bit 2                                                                                                                                                                                                  |

| AD[1]          | I/O  | C19 | Multiplexed address/data bus bit 1                                                                                                                                                                                                  |

| AD[0]          | I/O  | C20 | Multiplexed address/data bus bit 0                                                                                                                                                                                                  |

| PA3            | I    | C21 | 68HC11 Processor Port A bit 3                                                                                                                                                                                                       |

| PA4            | I    | C22 | 68HC11 Processor Port A bit 4                                                                                                                                                                                                       |

| PA5            | I    | C23 | 68HC11 Processor Port A bit 5                                                                                                                                                                                                       |

| PA6            | I    | C24 | 68HC11 Processor Port A bit 6                                                                                                                                                                                                       |

Quadruple T1 Framer

| PD2         | 0   | C25         | Master In Slave Out (MISO) of 68HC11 Port D bit 2 acting as SPI. Pulled up on motherboard.                                           |

|-------------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| PD3         | Ι   | C26         | Master Out Slave In (MOSI) of 68HC11 Port D bit 3 acting as SPI. Pulled up on motherboard.                                           |

| PD4         | Ι   | C27         | Serial Clock (SCK) of 68HC11 Port D bit 4 acting as SPI. Pulled up on motherboard.                                                   |

| PD5         | Ι   | C28         | Slave Select (SS) of 68HC11 Port D bit 5 acting as SPI active low. Pulled up on motherboard.                                         |

| IRQB        | 0   | C29         | Maskable 68HC11 interrupt. Pulled up on motherboard.                                                                                 |

| BRB (XIRQB) | 0   | C30         | Non Maskable 68HC11 interrupt. Pulled up on motherboard.                                                                             |

| DISB        | 0   | C31         | EVMB memory disable. Pulling this signal low will disable MPU access to the EVMB's on-board RAM and EPROM. Pulled up on motherboard. |

| SP          | Ι   | C32         | Spare                                                                                                                                |

| GND         | GND | A1-<br>A28  | Ground                                                                                                                               |

| +5V         | PWR | A29-<br>A32 | +5 Volts                                                                                                                             |

Quadruple T1 Framer

### APPENDIX A: DESIGN CONSIDERATIONS

#### Power Supply Voltage Transients

High currents drawn during IC switching causes power supply voltage transients due to the inductance of the power lines. The magnitude of the noise voltage can be reduced by minimizing the inductance of the power lines and by decreasing the magnitude of the transient currents. The power line inductance can be minimized by using a power plane. The transient currents on the power rails can be minimized by supplying the power from a local source such as a de-coupling capacitor near the circuit drawing the current.

The de-coupling capacitance and the inductance of the connection between the capacitor and the power pin determine the noise voltage at the power pin. The effectiveness of the de-coupling capacitor depends on the frequencies of the transients. Large "bulk" de-coupling capacitors are used to supply the low-frequency current variations and the small "noise-bypassing" capacitors are used to supply the high-frequency transient current that is required when the circuit is switching.

#### Ground Noise

Return currents and power supply transients during high current consumption produce most of the ground noise. Since ground noise cannot be controlled by de-coupling capacitors, the only way to minimizing the effect of ground noise is to minimize ground impedance. The best way to minimize ground impedance is to use a ground plane. It is not advisable to use ferrite beads in the ground path as this will inhibit the return currents from leaving and raise the ground noise level.

#### Noise-Bypassing at Power Pins

The TQUAD can generate a lot of simultaneous switching noise, especially if the line rate clocks are synchronous. It is important to provide a noise-bypassing capacitor at every power pin so that the switching currents can be supplied locally, thereby reducing the noise introduced into the power plane.

#### Values of Noise-Bypassing Capacitors

A rule of thumb is that the "bulk" noise-bypassing capacitor (placed where the power enters the circuit board) should have 10 times the value of all the noise-bypassing capacitors combined. Capacitors with low internal inductance should be used such as a tantalum electrolytic. Stay away from aluminum electrolytic as their inductances are an order of magnitude larger than tantalum capacitors.

The noise-bypassing capacitors (placed near the power pins) must be able to supply all the switching current. The minimum capacitance can be calculated by:

Quadruple T1 Framer

$$C = \frac{\Delta i \times \Delta t}{\Delta v}$$

The transient voltage drop  $\Delta V$  in the supply voltage is caused by the transient current  $\Delta i$  occurring over time  $\Delta t$  across capacitance C. This equation shows that the voltage drop will be minimized as the capacitance is increased. However, using capacitors that are too large should be avoided due to their resonance characteristics.

Since all capacitors have some stray inductance in series with the capacitance, there will be a self-resonance at a certain frequency given by the equation:

$$f = \frac{1}{2\pi\sqrt{LC}}$$

Note that the larger the capacitance (for the same inductance) the lower the resonant frequency. If the capacitor is too large, the self-resonance will be too low to be an effective bypass but if the capacitor is not large enough, there will be insufficient current to supply the transient current during switching. The smallest value capacitor to satisfy the above equations should be used. It is rarely necessary that a capacitor larger than 0.01  $\mu$ F be used.

#### Placement of Noise-Bypassing Capacitors

The de-coupling capacitor should be placed as close to the IC power pin as possible to reduce the wiring inductance. There are five sources of inductance: the parasitic inductance of the capacitor, the inductance of the wiring between the capacitor and the IC power pin, the power pin lead inductance inside the IC, the ground pin lead inductance inside the IC, and the ground inductance between the IC pin and ground. The capacitor inductance is negligible if the correct capacitor is used. There is no control over the lead frame inductance. To keep the inductance low, both the power lead and the ground lead should be keep as short as possible (less than 1.5 inches). The inductance for a trace is given by:

$$L = 0.005 \log^{-1} \left( 2\pi \frac{h}{w} \right) \ \mu \text{H/inch}$$

where **h** is the height between the power or ground lead and the ground plane and **w** is the width of the power or ground lead. Note that doubling the width of the trace or reducing **h** will only decrease **L** approximately by 20%, but decreasing the length by 50% will decrease the inductance by 50%. A typical PCB trace has about 15nH of inductance per inch.

ISSUE 1

Quadruple T1 Framer

#### Ferrite Beads

Ferrite beads are mainly used on power rails to pass DC current but to attenuate the higher frequency noise that is riding on the DC rail. The impedance of ferrite beads increases with frequency; at DC the ferrite bead is like a short but at higher frequency the impedance of a ferrite bead can increase to over 100 ohms (depending on the bead and frequency). Ferrite beads attenuate high frequency noise from the power supply from getting into a circuit, but they also stop high frequency switching currents required by digital ICs. It is important, therefore, to use proper noise bypass capacitors when using ferrite beads to provide a local source of switching current.

Ferrite beads should be avoided on CMOS I/O power pins as the high current switching of the CMOS circuits causes a  $\Delta I/\Delta t$  noise to be introduced into the power rail. This noise is induced because the ferrite beads "starve" the digital circuitry, causing the voltage to fluctuate locally. Ferrite beads should also be avoided on the ground bus as this inhibits the return currents.

#### Unused CMOS Inputs

"Floating" CMOS inputs (those that are left unconnected) may switch unpredictably, causing unwanted noise and power consumption. Therefore, all unused inputs should be connected to their inactive state: to ground or to the power rail (Vcc). Unused bidirectionals should be "pulled" through a series resistor (4.7k or greater) to avoid shortcircuits occuring if the bi-directionals are erroneously configured as outputs.

ISSUE 1

Quadruple T1 Framer

### APPENDIX B: MATERIAL LIST

| NO. | Part Name - Value                      | Jedec Type   | Ref. Des.                                                                                | Qty |

|-----|----------------------------------------|--------------|------------------------------------------------------------------------------------------|-----|

| 1   | 74XXX00_SOIC-HCMOS                     | SOIC14       | U7                                                                                       | 1   |

| 2   | 74XXX04_SOIC-HCMOS                     | SOIC14       | U6                                                                                       | 1   |

| 3   | 74XXX138_SOIC-HCMOS                    | SOIC16       | U10,U11                                                                                  | 2   |

| 4   | 74XXX245_SOIC-HCMOS                    | SOIC20W      | U5                                                                                       | 1   |

| 5   | 74XXX373_SOIC-HCMOS                    | SOIC20W      | U9                                                                                       | 1   |

| 6   | 74XXX541_SOIC-HCMOS                    | SOIC20W      | U12                                                                                      | 1   |

| 7   | BANTAM-BASE                            | BANTAM       | J91-J98                                                                                  | 8   |

| 8   | CAP68UF,METAL POLY                     | CAP200       | C37-C40                                                                                  | 4   |

| 9   | CAP-0.001UF                            | SMDCAP805    | C6,C7,C9,<br>C11-C13,C15,<br>C17,C18,C21,<br>C22,C25,C26,<br>C30,C82                     | 15  |

| 10  | CAP-100000PF                           | SMDCAP1206   | C1-C5,C8,C10,<br>C14,C16,C19,<br>C20,C23,C24,<br>C27,C31,<br>C45-C48,<br>C74-C81,C84,C85 | 29  |

| 11  | CAP-10000PF                            | SMDCAP805    | C28,C33-C36,<br>C58-C73                                                                  | 21  |

| 12  | CAP-1000PF,NPO_805                     | SMDCAP805    | C42-C44,C83                                                                              | 4   |

| 13  | CAP-10PF,NPO_805                       | SMDCAP805    | C41                                                                                      | 1   |

| 14  | CAP-47000PF                            | SMDCAP1206   | C53-C56                                                                                  | 4   |

| 1 5 | CAPACITOR<br>POL-0.47UF,25V,<br>TANT A | SMDTANCAP_A  | C49-C52                                                                                  | 4   |

| 16  | CAPACITOR POL-100UF,<br>16V,ELECTRO    | CAP320       | C32                                                                                      | 1   |

| 17  | CAPACITOR POL-10UF,<br>16V,TANT TEH    | SMDTANCAP_C  | C29,C57                                                                                  | 2   |

| 18  | CY7C136BASE                            | PLCC52       | U3                                                                                       | 1   |

| 19  | DIN96_MALE-BASE                        | AMP_650473-5 | P1                                                                                       | 1   |

| 20  | HEADER8-BASE                           | SIP8         | J2-J6,J9                                                                                 | 6   |

| 21  | INDUCTOR-FB,50,<br>FAIR RITE           | BEAD_1       | L1-L8                                                                                    | 8   |

| 22  | LED10-RED,25MA,2.1V                    | DIP20_LED    | U2                                                                                       | 1   |

| 23  | MC100ELT21_SOIC-BASE                   | SOIC8        | U4,U17                                                                                   | 2   |

| 24  | OSC_TTL_DIP-20.0000M<br>HZ,100 PPMA    | CRYS14       | Y1,Y2                                                                                    | 2   |

ISSUE 1

Quadruple T1 Framer

| NO. | Part Name - Value     | Jedec Type | Ref. Des.             | Qty |

|-----|-----------------------|------------|-----------------------|-----|

| 25  | PIC16C74-BASE         | PIC16C74   | U1                    | 1   |

| 26  | PWRBLOCK_2-BASE       | CONN2END   | J1                    | 1   |

| 27  | QDSX-BASE             | PQFP128    | U24                   | 1   |

| 28  | RESISTOR-10K,5%       | SMDRES805  | R1,R9,R12-R15,<br>R60 | 7   |

| 29  | RESISTOR-196,1%       | SMDRES805  | R8,R11                | 2   |

| 30  | RESISTOR-22,5%        | SMDRES805  | R16,R17,R28,R29       | 4   |

| 31  | RESISTOR-309,1%       | SMDRES805  | R24-R27               | 4   |

| 32  | RESISTOR-316K,1%      | SMDRES805  | R36-R39               | 4   |

| 33  | RESISTOR-4.7K,5%      | SMDRES805  | R3-R7,R18,R19         | 7   |

| 34  | RESISTOR-68.1,1%      | SMDRES805  | R2,R10                | 2   |

| 35  | RESISTOR-93.1,1%      | SMDRES805  | R20-R23               | 4   |

| 36  | RES_ARRAY_15_SMD-10K  | SOIC16     | RN1,RN3,RN4           | 3   |

| 37  | RES_ARRAY_15_SMD-4.7K | SOIC16     | RN5                   | 1   |

| 38  | RES_ARRAY_8_SMD-270   | SOIC16     | RN2                   | 1   |

| 39  | SMA-BASE              | SMA        | J7,J8                 | 2   |

| 4 0 | TQUAD-BASE            | PQFP128    | U8                    | 1   |

| 4 1 | TST_PT-BASE           | TST_PT_1   | TP1-TP10              | 10  |

| 42  | T1008-BASE            | T1008      | T1,T2                 | 2   |

Quadruple T1 Framer

### APPENDIX C: SCHEMATICS

Quadruple T1 Framer

# APPENDIX D: FIRMWARE DESCRIPTION AND SOURCE CODE

This section will be completed at a later date

Quadruple T1 Framer

### CONTACTING PMC-SIERRA

PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, B.C. Canada V5A 4V7

Telephone: 604-415-6000 Facsimile: 604-415-6200

Product Information: info@pmc-sierra.bc.ca Applications information: apps@pmc-sierra.bc.ca

World Wide Web Site: http://www.pmc-sierra.com

Quadruple T1 Framer

ISSUE 1

NOTES

Seller will have no obligation or liability in respect of defects or damage caused by unauthorized use, mis-use, accident, external cause, installation error, or normal wear and tear. There are no warranties, representations or guarantees of any kind, either express or implied by law or custom, regarding the product or its performance, including those regarding quality, merchantability, fitness for purpose, condition, design, title, infringement of third-party rights, or conformance with sample. Seller shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon, the information contained in this document. In no event will Seller be liable to Buyer or to any other party for loss of profits, loss of savings, or punitive, exemplary, incidental, consequential or special damages, even if Seller has knowledge of the possibility of such potential loss or damage and even if caused by Seller's negligence.

© 1996 PMC-Sierra, Inc.

PMC-960620

Printed in Canada

Issue date: June, 1996.