RCMP Egress Routing Logic in VHDL

## PM7322

# RCMP EGRESS ROUTING LOGIC IN VHDL

Issue 1: March, 1997

PMC-Sierra, Inc.

105-8555 Baxter Place Burnaby, BC Canada V5A 4V7 604 415 6000

ISSUE 1

#### RCMP Egress Routing Logic in VHDL

## **TABLE OF CONTENTS**

| INTRODUCTION             | 1  |

|--------------------------|----|

| FEATURES                 | 3  |

| ARCHITECTURE             | 4  |

| OPERATION                | 5  |

| Direct Mode              | 5  |

| Indirect Addressing Mode | 10 |

| Stuttering               | 12 |

| DESIGN CONSIDERATIONS    | 14 |

| SUMMARY                  | 15 |

| APPENDIX A: VHDL CODE    | 16 |

ISSUE 1

RCMP Egress Routing Logic in VHDL

## **INTRODUCTION**

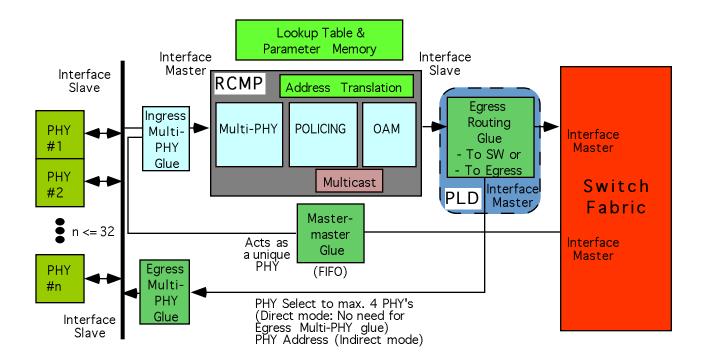

The RCMP-800<sup>1</sup> can be configured to process both the Ingress and Egress cell traffic in a port card, where the bandwidth in either direction is less than half of the maximum bandwidth of the RCMP (ie. less than 400Mbps for the RCMP-800). As shown in Figure 1, with the RCMP positioned on the Ingress side, Egress cell traffic can be "looped" into the RCMP input as if it is sourced from another PHY. The output of the RCMP will thus consists of both Ingress and Egress cell traffic. As such, external glue logic is needed to route these cells to the appropriate destination (ie. to the switch or to the PHY).

This appnote describes a VHDL implementation of the Egress Routing glue logic as described above. The functionality, the timing aspects and a reference VHDL code implementation (included in Appendix A) are included. This glue logic can be implemented in a simple PLD.

This implementation is based on Appendix A of the appnote, PMC-951205, Issue 2, "RCMP in Egress Operation".

Figure 1 Egress "Loop" Port Card System

Although Figure 1 shows only the Egress "loop" application of the Egress Routing glue logic, this design can be easily modified to be used to interface with an existing Egress

<sup>&</sup>lt;sup>1</sup>Hereafter referred to as "RCMP"

PM7322 RCMP-800

#### ISSUE 1

#### RCMP Egress Routing Logic in VHDL

device. In this case, the Egress cell traffic from the switch will need to be muxed together with the "backwards" cell traffic from the RCMP output. This is especially useful for applications where only certain OAM cells from the RCMP are to be routed "backwards" to the Egress side, thus bypassing the switch fabric.

This design has been implemented and simulated in a Cypress CY7C374 PLD. This PLD contains 128 macrocells, which is roughly 4K gates, of which approximately 60% is utilized in this design. This PLD has 84 pins, 63 of which are I/O pins. This design uses 58 I/O pins.

This design applies equally to PM7323, the RCMP-200. The only difference with the RCMP-200 is that it has an 8-bit interface that runs at a maximum clock frequency of 25MHz.

## PM7322 RCMP-800

ISSUE 1

RCMP Egress Routing Logic in VHDL

## **FEATURES**

- Supports Backwards Routing of cells from the RCMP output . Decodes the prepend word to determine whether a cell is destined to the switch fabric or one of the PHY devices in the Transmit direction.

- Supports either Direct Multi-PHY interface or Indirect-addressing Multi-PHY interface for up to 32 PHY's.

- Supports cell format with one prepend and 27 words (16-bit wide). Prepend word is stripped off.

- Supports back-pressure flow control (referred to as stuttering in the code) from the switch.

ISSUE 1

RCMP Egress Routing Logic in VHDL

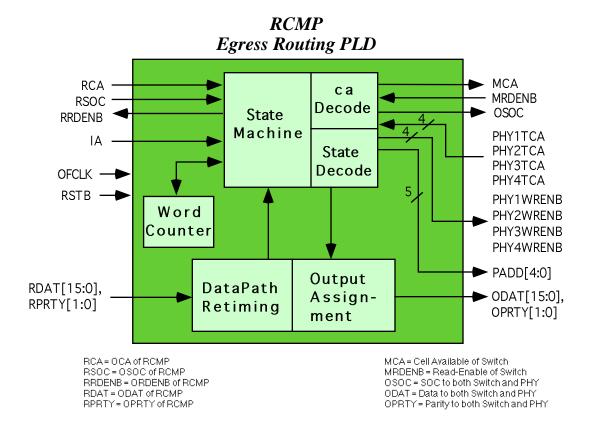

## ARCHITECTURE

Figure 2 is a block diagram of the Egress Routing Logic. The State machine handles all the cell-transfer handshaking. The interface to the RCMP consists of the control signals RCA, RSOC and RRDENB, plus the 16-bit data RDAT and the parity RPRTY. RCMP is a UTOPIA "slave", which receives the read-enable signal, RRDENB. The interface to the switch includes MCA and MRDENB. The switch is assumed to be a UTOPIA "master", which sources the read-enable signal, MRDENB. The interface to the PHY devices consists of the 4 PHYTCA's, the 4 PHYWRENB's (in Direct mode), and the 5-bit PHY address, called PADD (in Indirect-addressing mode). All PHY devices are assumed to be UTOPIA "slaves". The retimed data and parity output (ODAT and OPRTY) are connected to both the switch and the PHY devices.

Note that signals that end with a 'B' are active-low (ie. asserted if equal to 0).

Figure 2 Egress Routing Design Block Diagram

PM7322 RCMP-800

ISSUE 1

RCMP Egress Routing Logic in VHDL

## **OPERATION**

There are two modes of operation, direct and indirect mode, which correspond to the interface mode to the PHY devices. The interface to the switch is identical in both modes.

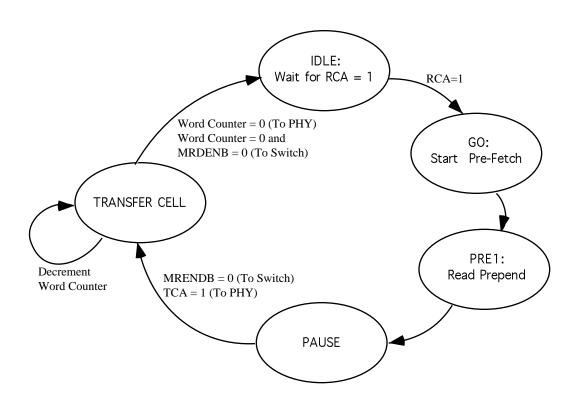

The state diagram is shown in Figure 3 as a reference.

## Figure 3 Egress Routing State Machine Diagram

## **Direct Mode**

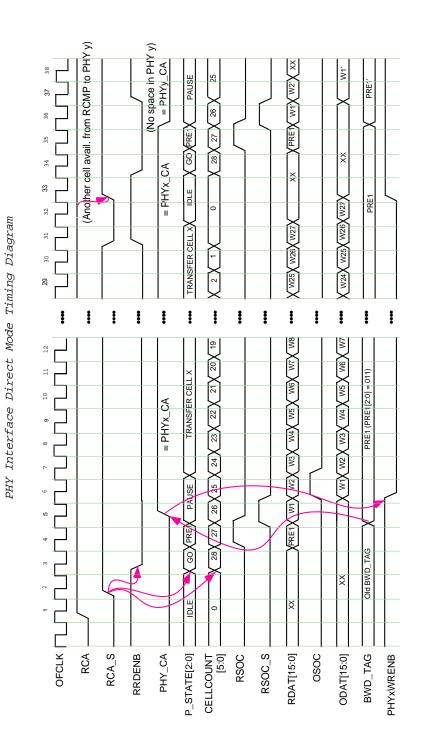

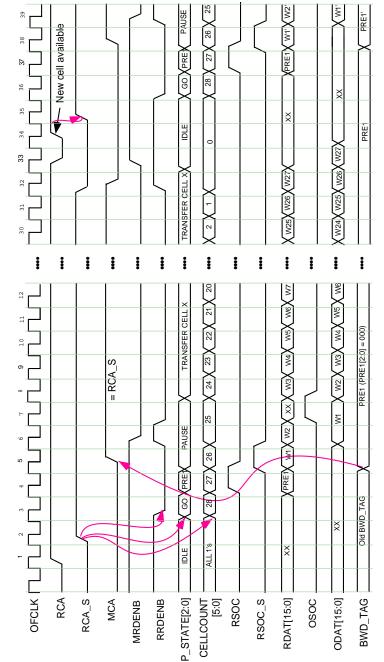

The operation in the Direct mode for **cell transfer to the PHY devices** is shown in the timing diagram in Figure 4. The state machine starts off in the IDLE mode, waiting for RCA to be asserted by the RCMP, indicating a cell is available to be transferred. Once RCA is sampled high, 3 words are "pre-read" from the RCMP, with the first word containing the backward routing tag. The following describes in detail the sequence of events for each cell transfer:

RCMP Egress Routing Logic in VHDL

ISSUE 1

PM7322 RCMP-800

ISSUE 1

- Clock cycle 1: RCMP indicates a cell is available by asserting RCA.

- Clock cycle 2: Glue logic samples the RCA.

- Clock cycle 3: Glue logic asserts RRDENB to read out the first prepend word. P\_STATE becomes GO, and the CELL\_COUNT initializes to 28 (which is the number of words to be read from the RCMP).

- Clock cycle 4: The first prepend word (RDAT[15:0]) and parity (not shown), along with RSOC, are read out from the RCMP. P\_STATE becomes PRE1, which aligns with RDAT.

- Clock cycle 5: Glue logic samples the prepend word, the parity (not shown) and RSOC(as RSOC\_S). Word 1 of the 27-word cell is read out from the RCMP. The BWD\_TAG is decoded from the prepend word (Bits 15 to 8), which indicates that the cell is destined to one out of eight PHY devices. P\_STATE enters PAUSE state, to wait for the PHY device to indicate that space is available in its transmit FIFO. Here the PHY\_CA signal is shown to be asserted in this cycle.

- Clock cycle 6: The PHY\_CA signal from the appropriate PHY device is sampled. If the PHY\_CA signal is sampled to be high (as shown in the figure), RRDENB will continued to be asserted to read the rest of the 27-word cell from the RCMP. Otherwise, the glue logic will stay in the PAUSE state until PHY\_CA is sampled high. Word 2 of the 27-word cell is read out from the RCMP. Word 1 and OSOC are presented on the output to the PHY device. PHYWRENB to the appropriate PHY device is asserted to write the cell into the PHY transmit FIFO.

- Clock cycle 7-31: P\_STATE enters the TRANSFER CELL state, and the RCMP to outputs the remaining 26 words of the cell. In Cycle 34, RRDENB is deasserted to end the cell transfer. RCA\_S is forced low for the cell transfer state machine to reset itself.

- Clock cycle 32: P\_STATE resets to the IDLE state after the cell transfer. Word 27 of the cell is output.

- Clock cycle 33: Glue logic samples RCA. If RCA is sampled high (which is the case shown), indicating another cell is available from the RCMP, the entire cell transfer process begins again. Note that in this figure, the new prepend, PRE1', indicates a cell transfer to PHYy. However, PHYy does not have space in its FIFO, hence the low PHY\_CA. The glue logic will stay in the PAUSE state until PHYy\_CA is asserted.

RCMP Egress Routing Logic in VHDL

Switch Interface Timing Diagram

PM7322 RCMP-800

ISSUE 1

RCMP Egress Routing Logic in VHDL

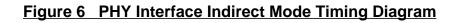

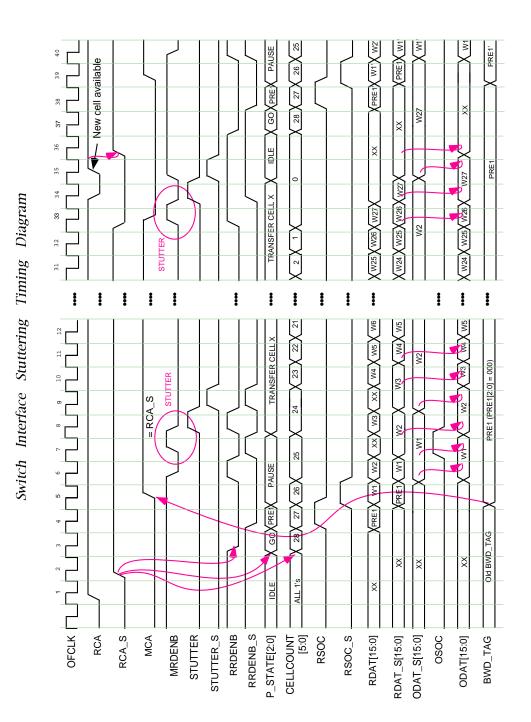

The operation in the Direct mode for a **cell transfer to the switch** is shown in the timing diagram in Figure 5. The state machine starts off in the IDLE mode, waiting for RCA to be asserted by the RCMP, indicating a cell is available to be transferred. The prepend decode process is identical to the process when interfacing with the PHY devices. The difference here is that the cell transfer control is basically handed over to the switch (the switch controls the read-enable). The following describes the sequence of events for each cell transfer:

- Clock cycle 1: RCMP indicates a cell is available by asserting RCA.

- Clock cycle 2: Glue logic samples the RCA.

- Clock cycle 3: Glue logic asserts RRDENB to read out the first prepend word. P\_STATE becomes GO, and the CELL\_COUNT initializes to 28.

- Clock cycle 4: The first prepend word (RDAT[15:0]) and parity (not shown), along with RSOC, are read out from the RCMP. P\_STATE becomes PRE1, which aligns with RDAT.

- Clock cycle 5: Glue logic samples the prepend word, the parity (not shown) and RSOC(as RSOC\_S). Word 1 of the 27-word cell is read out from the RCMP. The BWD\_TAG is decoded from the prepend word (Bits 15 to 8), which indicates that the cell is destined to the switch. MCA is thus asserted. P\_STATE enters PAUSE state, to wait for the switch to sample MCA and assert MRDENB.

- Clock cycle 6: The switch samples MCA, asserts MRDENB and starts the cell transfer. Note that the switch now has full control of the cell transfer process. If it decides to postpone MRDENB assertion, the glue logic will stay in the PAUSE state. Word 2 is read from the RCMP. RRDENB is deasserted.

- Clock cycle 7: MRDENB is sampled. RRDENB asserted as a result. Word 1 and OSOC is output to the switch.

- Clock cycle 8: P\_STATE enters the TRANSFER CELL state, and the RCMP outputs Word 2 of the cell.

- Clock cycle 9-32: The rest of the ATM cell is transferred. RRDENB is deasserted in Cycle 32. MCA is forced to 0. RCA\_S is forced low for the cell-transfer state machine to reset itself.

- Clock cycle 33: P\_STATE enters the IDLE state. MRDENB is deasserted by the switch to end the cell transfer. Word 27 is output. Meanwhile, RCA from the RCMP is shown to have deasserted.

PM7322 RCMP-800

## ISSUE 1

## RCMP Egress Routing Logic in VHDL

Clock cycle 34: Glue logic samples RCA. If RCA is sampled high (not in cycle 34), indicating another cell is available from the RCMP, the entire cell transfer process begins again. Otherwise, the glue logic will stay in the IDLE state until RCA is sampled high (as in Cycle 35).

Note that at any time during the cell transfer, the switch can deassert MRDENB to pause the transfer and resume at a later time. The cell count will stop decrementing until MRDENB is asserted again. This is to support the switch back-pressuring mechanism, and is called "stuttering" here. This mechanism will be described in a latter section.

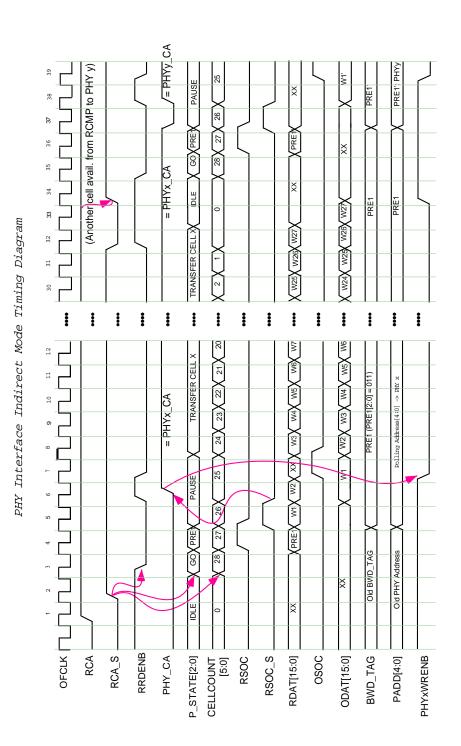

## Indirect Addressing Mode

The operation in the Indirect-addressing mode for a **cell transfer to the switch** is identical to that in the Direct mode. The operation in the Indirect-addressing mode for **cell transfer to the PHY device** is shown in the timing diagram in Figure 6. The state machine starts off in the IDLE mode, waiting for RCA to be asserted by the RCMP, indicating a cell is available to be transferred. The prepend decode process is identical to the process when interfacing with the PHY devices. The difference here is that, instead of the 4 direct PHYWRENB signals, a 5-bit PHY address (PADD) is output. PADD can be decoded to address a maximum of 32 PHY devices that are interfaced to this PLD. The PHY device samples this address and the selected PHY asserts the cell-available (PHY\_CA) signal in the next cycle. The remaining sequence of events for the cell transfer is identical to the Direct Mode case.

ISSUE 1

RCMP Egress Routing Logic in VHDL

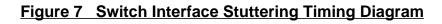

## **Stuttering**

Figure 7 shows two representative stuttering situations. The first case is when the switch deasserts read-enable just after the first word. The second case is when the switch deasserts read-enable just before the last word. In both cases, a special mechanism in the PLD effectively "buffers" the data read from the RCMP, and holds the data until the switch is ready to transfer again. Specifically, the internal registers RDAT\_S and ODAT\_S provides the "buffering" to read and hold the data in a stuttering situation.

ISSUE 1

RCMP Egress Routing Logic in VHDL

## **DESIGN CONSIDERATIONS**

- The same clock, OFCLK, is assumed to be used by all interfaces.

- Signals on the RCMP interface, ie. rca, rsoc, data/parity, are all sampled and retimed in the PLD due to the propagation delay and setup times in the RCMP, so that this design can be used in 50MHz operation.

- With this design, it is transparent to the PHY device and the switch in terms of the UTOPIA protocol, since there is no extra delay between the cell-available signals, the read-enable signals and the data.

- With this PLD, some extra bandwidth is required to transition from cell to cell and to decode the routing tag. If the cell is going to a PHY, 3 extra cycles are required. If the cell is going to the switch, 4 extra cycles are required.

- This design can be modified to support an 8-bit interface, by changing the counter initial value.

- This design supports only one prepend. To support more prepend words, the counter initial value can be modified, and simply treat the additional prepend words as part of the cell, assuming the first prepend word contains the routing tag.

- The reset signal (RSTB), which is not shown in the timing diagrams, is active low and should be asserted for at least 2 clock cycles for a proper device reset.

- AC timing: This VHDL design can be implemented in any programmable device that contains adequate internal logic and pins. For 50MHz operation, the UTOPIA interface requirements are such that the maximum setup and hold times are 4ns and 1ns respectively, and the maximum propagation delay from the active clock edge is 16ns. The AC characteristics of the device must be such that it satisfies the timing requirements at the operating clock frequencies, with enough margins to cover routing delay and clock skew.

PM7322 RCMP-800

ISSUE 1

RCMP Egress Routing Logic in VHDL

## **SUMMARY**

A VHDL design for the RCMP Egress cell routing was described in this appnote. The design acts as the routing function which sits in between the RCMP output, the switch input, and the PHY inputs. It provides both the direct and indirect (using PHY addresses) interface modes with the PHY devices. It supports stuttering or back-pressuring by the switch input interface.

PM7322 RCMP-800

ISSUE 1

ROMP Egress Routing Logic in VHDL

## APPENDIX A: VHDL CODE

The following is the RCMP Egress Routing Logic design in VHDL.

\_\_\_\_\_

- -- Name : RCMP Egress Routing Logic for Appnote (AN6)

- -- File Name : RCMP\_MPE.VHD

- -- Company : PMC Sierra, Inc

- -- Date : Feb. 10, 1997

- --

- --

- -- Description :

- -- Performs the multi-PHY Egress Routing logic for the RCMP-800/200.

- ---

- -- The main function that this logic supports is Backward Routing.

- -- It decodes the Backward Tag in the first prepend word (bits 15 to 8)

- -- to decide whether the cell is destined for the ATM switch or

- -- should be routed backwards to a PHY.

- -- If the cell is going to a PHY, it then selects 1 out of 32 PHY devices to receive

- -- the cell as decoded from the Backward Tag.

- --

- -- Supports 2 modes of PHY select: 1) Direct mode, 2) Indirect-addressing mode.

- -- In Direct mode:

- -- It monitors the cell-available (PHY\_CA) signal from the correct PHY and provides

- -- the appropriate control signal (PHYxWRENB) to the correct PHY.

- -- In Indirect-addressing mode:

- -- It outputs a 2-bit address (PADD[1:0]) extracted from the Backward Tag

- -- (bits 1 to 0). It monitors the cell-available (PHYxCA) signal from the

- -- correct PHY, as selected based on the Backward Tag (bits 4 to 2).

- -- Then it provides the control signal (PHYxWRENB) to the correct PHY device.

- -- The Indirect mode is used to interface with "Quad-PHY" devices, which have

- -- PHY address-decoding built-in. For example, the PM7344, the S/UNI-MPH

- -- device, has 4 T1/E1 ports, which are selected based on a 2-bit address.

---

- -- If the cell is going to the switch, it then proceed with the regular cell transfer,

- -- using MCA and MRDENB signals for control. "Stuttering", or deassertion of

- -- MRDENB, during cell transfer by the switch is supported.

- --

- -- Note that RSOC from the RCMP must align with the first prepend word. It is

-- not optional.

- -- Only 16-bit interface supported. Cellcounts will need to be modified for

- -- 8-bit interface.

- --

- -- Supports prepend only. Prepend word is stripped off at output.

- -- Supports only 27-word cells (plus the prepend).

PM7322 RCMP-800

RCMP Egress Routing Logic in VHDL

-- The output data, ODAT[15:0], and OSOC should be connected to BOTH -- the switch and the PHY's. -- Note that the this logic always "preread" the cell words, so that there will not be -- any extra clock cycle latency from the point of view of the switch. (ie. when the -- switch asserts MRDENB, cell data will be valid to be sampled at the end of the -- NEXT clock cycle). -- DISCLAIMER: PMC does not guarantee that this VHDL code is correct and functional in all applications. It is intended to be used as a reference only. --\_\_\_\_\_ -- Compiler specific directives USE work.int math.all: USE work.bv math.all; ENTITY rcmp mpe IS PORT ( IN BIT VECTOR(15 downto 0); -- rcmp data rdat: IN BIT VECTOR(1 downto 0); -- rcmp data partity rprty: odat: OUT BIT\_VECTOR(15 downto 0); -- output data OUT BIT VECTOR(1 downto 0); -- output data partity oprty: IN BIT; -- 1: Indirect-addressing mode, 0: Direct mode ia: OUT BIT VECTOR(4 downto 0); -- PHY address in Indirect mode padd: IN BIT; -- rcmp osoc rsoc: osoc: OUT BIT: -- output soc IN BIT; -- rcmp oca rca: rrdenb: OUT BIT: mrdenb: IN BIT; -- ATM Switch read-enable OUT BIT; -- cell-available to ATM Switch mca: IN BIT; -- From PHY 1 in Direct mode; Shared phy\_ca in Indirect mode phy1tca: phy1wrenb: OUT BIT; -- To PHY 1 in Direct mode; Shared phywrenb in Indirect mode IN BIT; -- From PHY 2 phy2tca: phy2wrenb: OUT BIT; IN BIT; -- From PHY 3 phy3tca: phy3wrenb: OUT BIT; IN BIT: -- From PHY 4 phv4tca: phy4wrenb: OUT BIT; ofclk: IN BIT: rstb: IN BIT); ATTRIBUTE order code of rcmp mpe:ENTITY is "CY7C374-83JC"; ATTRIBUTE part name of rcmp mpe:ENTITY IS "C374";

ATTRIBUTE pin\_numbers of rcmp\_mpe:ENTITY IS "rdat(0):76 rdat(1):77 rdat(2):78 rdat(3):79 " & "rdat(4):80 rdat(5):81 rdat(6):82 rdat(7):83 " & "rdat(8):3 rdat(9):4 rdat(10):5 rdat(11):6 " & "rdat(12):7 rdat(13):8 rdat(14):9 rdat(15):10 " & "rprty(0):73 rprty(1):75 "

ISSUE 1

RCMP Egress Routing Logic in VHDL

& "odat(0):51 odat(1):50 odat(2):49 odat(3):48 " & "odat(4):47 odat(5):46 odat(6):45 odat(7):58 " & "odat(8):40 odat(9):39 odat(10):38 odat(11):37 " & "odat(12):36 odat(13):35 odat(14):34 odat(15):33 " & "oprty(0):54 oprty(1):52 & "ia:27 & "padd(0):15 padd(1):16 padd(2):17 padd(3):18 padd(4):19 " & "rrdenb:70 rca:71 rsoc:72 " & "mrdenb:12 mca:13 & "phy3tca:60 phy3wrenb:61 & "phy2wrenb:56 phy4tca:57 & "phy1wrenb:30 phy1tca:29 " osoc:31 & "phy2tca:28 phy4wrenb:66 & "ofclk:65 rstb:41";

END rcmp\_mpe;

ARCHITECTURE behav OF rcmp\_mpe IS

SUBTYPE wount IS integer range 0 to 63;

SIGNAL phywrenb: bit: SIGNAL phy ca: bit: SIGNAL cellcount: wcount; SIGNAL bwd tag: bit vector(7 downto 0); bit; -- internal version of rrdenb (output to RCMP) SIGNAL rrdenbi: SIGNAL rrdenbi s: bit: -- sampled version of rrdenbi SIGNAL stutter: bit; -- indicates mrdenb deassertion during cell transfer SIGNAL stutter s: bit: -- stutter retimed

TYPE state\_type IS (idle, go, transfer\_pre1, transfer\_cell, pause); signal n\_state : state\_type; signal p\_state : state\_type;

-- Sampled versions of rcmp outputs SIGNAL rdat\_s: bit\_vector(15 downto 0); SIGNAL odat\_s: bit\_vector(15 downto 0); SIGNAL rprty\_s : bit\_vector(1 downto 0); SIGNAL oprty\_s : bit\_vector(1 downto 0); SIGNAL rca\_s : bit; SIGNAL rsoc\_s: bit;

-- "to\_switch" is set to "000", so that a default prepend of 0's will mean -- cell transfer to switch CONSTANT to\_switch:bit\_vector(7 downto 0) := "00000000"; CONSTANT to\_phy:bit\_vector(7 downto 0) := "00000011";

BEGIN

## PM7322 RCMP-800

#### ISSUE 1

RCMP Egress Routing Logic in VHDL

\_\_\_\_\_ \_\_\_\_\_ -- Process: output\_assignment -- Purpose: Assigns the output data, parity, soc, and other -- control signals. \_\_\_\_\_ output\_assignment: PROCESS (rdat\_s, rprty\_s) BEGIN IF (p state = pause) THEN odat <= odat\_s; -- for Word 1 only oprty <= oprty\_s;</pre> ELSIF (stutter\_s = '1') THEN odat <= odat\_s; -- Hold the word during stutter oprty <= oprty\_s; ELSE odat <= rdat\_s; -- 1-stage pipeline oprty <= rprty\_s;</pre> END IF; rrdenb <= rrdenbi; padd <= bwd\_tag(7 downto 3);</pre> IF (rrdenbi = '0' and cellcount = 25) THEN  $\operatorname{osoc} \leq '1';$ ELSE  $\operatorname{osoc} \leq 0';$ END IF: END PROCESS output\_assignment; \_\_\_\_\_ \_\_\_\_\_ -- Process: state transition, state assign -- Purpose: This process implements the main state machine that -- controls the cell transfer/routing process. It supports only prepends. state\_transition: PROCESS (rca\_s, p\_state, cellcount) BEGIN CASE p\_state IS WHEN idle => -- The RCMP has a cell available, so get the first word and -- see which PHY it is destined to. IF  $(rca_s = '1')$  THEN n\_state <= go; ELSE n state  $\leq$  idle; END IF; WHEN go =>

## PM7322 RCMP-800

ISSUE 1

RCMP Egress Routing Logic in VHDL

-- Sample the first word. n\_state <= transfer\_pre1; -- "Pause" to wait for bwd\_tag to be decoded WHEN transfer pre1 =>n state  $\leq$  pause; WHEN pause => IF (rrdenbi = '0' and cellcount = 25) THEN n\_state <= transfer\_cell;</pre> ELSE n\_state <= pause; END IF; -- End of "Pause" logic WHEN transfer cell => IF (cellcount = 0) THEN IF (bwd tag(2 downto 0) = to switch(2 downto 0)) and mrdenb = '0') THEN n state  $\leq$  idle; ELSIF (bwd\_tag(2 downto 0) = to\_phy(2 downto 0)) THEN n state  $\leq$  idle; ELSE n state <= transfer cell; END IF; ELSIF (cellcount = 63) THEN n state  $\leq$  idle; ELSE n state <= transfer cell; END IF: WHEN others =>-- Included to handle any unknown case out of reset n state  $\leq$  idle; END CASE; END PROCESS state transition; state\_assign: PROCESS (rstb, ofclk) BEGIN IF (rstb = '0') THEN p state <= idle; ELSIF (ofclk'EVENT and ofclk = '1') THEN p\_state <= n\_state;</pre> END IF; END PROCESS state\_assign; \_\_\_\_\_ \_\_\_\_\_ -- Process: ca decode -- Purpose: This process decodes the phy\_ca. Also controls -- mca. \_\_\_\_\_

## PM7322 RCMP-800

ISSUE 1

```

ca_decode: PROCESS (p_state, bwd_tag)

BEGIN

IF (bwd_tag(2 downto 0) = to_switch(2 downto 0)

and (p state = pause or p state = transfer cell)) THEN

mca <= rca s; -- cell is headed for Switch

ELSE

mca <= '0';

END IF;

IF (bwd tag(2 downto 0) = to phy(2 downto 0)) THEN

IF(ia = '1') THEN

IF (rsoc_s = '1') THEN

phy_ca <= '0'; -- Null phy_ca until PHY device have

-- time to output valid tca

ELSE

phy_ca <= phy1tca; -- All PHY's share phy1tca

END IF:

ELSE

CASE bwd_tag(4 downto 3) IS

WHEN "00" =>

phy_ca <= phy1tca;

WHEN "01" =>

phy_ca <= phy2tca;

WHEN "10" =>

phy_ca <= phy3tca;

WHEN others =>

phy ca \leq phy4tca;

END CASE;

END IF;

ELSE

phy ca \leq 0';

END IF:

END PROCESS ca decode;

-- Process: state decode

-- Purpose: This process implements UTOPIA signal processing and

-- Backward routing processing functions.

_____

state_decode: PROCESS (rstb, ofclk)

BEGIN

IF (rstb = '0') THEN

rdat_s <= "000000000000000";

rprty_s <= "00";

rsoc s \le 0';

bwd_tag <= to_switch;</pre>

ELSIF (ofclk'EVENT and ofclk = '1') THEN

```

PM7322 RCMP-800

```

ISSUE 1

```

RCMP Egress Routing Logic in VHDL

- -- Section: UTOPIA signal processing

- -- Purpose: This section samples the RDAT, RPRTY, RSOC, RCA signals

- -- from the RCMP. It samples the prepend word that contains the

- -- Backward Routing Information.

- -- It generates the correct SOC, and thus strips the

- -- prepend word if the cell is going to a PHY.

- -- It generates the RRENDB signal to the RCMP, which controls the

- -- actual cell transfer out of the RCMP.

- --

\_\_\_

```

-- Preread circuit used to eliminate extra latency to switch. When RCA=1,

```

- -- the prepend, Word 1, Word 2 will always be preread.

- -- "Stutter" is used to handle the case where MRDENB is deasserted

- -- during cell transfer.

```

-----

```

IF (rrdenbi\_s = '0') THEN rdat  $s \leq rdat;$ rprty\_s <= rprty;</pre> ELSE rdat\_s <= rdat\_s; rprty\_s <= rprty\_s;</pre> END IF; IF  $(rsoc_s = '1')$  THEN odat  $s \leq rdat;$ oprty\_s <= rprty; ELSIF (stutter = '1' and stutter\_s = '0') THEN odat  $s \ll rdat s$ ; -- Hold the data during stutter oprty\_s <= rprty\_s; ELSE odat\_s <= odat\_s; oprty\_s <= oprty\_s; END IF; rsoc\_s <= rsoc;</pre> IF (p\_state = transfer\_cell and (cellcount = 1 or cellcount = 0)) THEN -- This is done just to force a transition on the sampled version of rca. -- so that the state machine can go to idle after a cell transfer rca  $s \le 0';$ ELSE rca  $s \leq rca;$ END IF; IF (rsoc = '1') THEN bwd tag  $\leq$  rdat(15 downto 8); -- Get Backward Tag from RDAT[15:8]

```

ISSUE 1

```

```

ELSE

bwd_tag <= bwd_tag;</pre>

END IF;

rrdenbi s <= rrdenbi; -- for odat retime control

stutter s <= stutter; -- for odat retime control during stutter

IF (rca_s = '1' and p_state = idle) THEN

rrdenbi <= '0'; -- Read prepend

ELSIF (bwd tag(2 downto 0) = to phy(2 downto 0)) THEN

IF (p state = go) THEN

rrdenbi <= '0'; -- preread Word 1

ELSIF (p state = transfer pre1) THEN

rrdenbi <= '0'; -- preread Word 2

ELSIF (p state = pause and phy ca = '1') THEN

rrdenbi <= '0'; -- Start cell transfer to PHY; read Word 3

ELSIF (p state = transfer cell and cellcount /= 1

and cellcount \neq 0) THEN

rrdenbi \leq 0';

ELSE

rrdenbi \leq 1':

END IF;

ELSIF (bwd_tag(2 downto 0) = to_switch(2 downto 0)) THEN

IF (p state = go) THEN

rrdenbi <= '0'; -- preread Word 1

ELSIF (p state = transfer pre1) THEN

rrdenbi <= '0'; -- preread Word 2

ELSIF (p state = pause) THEN

rrdenbi <= mrdenb; -- transfer control to switch

ELSIF (p_state = transfer_cell and cellcount \neq 0

and cellcount \neq 1 and cellcount \neq 61 and

cellcount \neq 62 and cellcount \neq 63) THEN

rrdenbi <= mrdenb;

ELSIF (p_state = transfer_cell and cellcount = 1) THEN

IF (stutter = '1') THEN

rrdenbi <= mrdenb;

ELSE

rrdenbi \leq 1';

END IF;

ELSE

rrdenbi <= '1';

END IF;

ELSE

rrdenbi <= '1';

END IF;

IF (rca_s = '1' and p_state = idle) THEN

stutter <= '0'; -- initialize stutter

ELSIF (bwd tag(2 downto 0) = to switch(2 downto 0)) THEN

IF (rrdenbi = '0' and cellcount = 25) THEN

```

PM7322 RCMP-800

#### **ISSUE** 1

```

stutter <= mrdenb; -- To handle stuttering right after Word1

ELSIF (p state = transfer cell) THEN

stutter <= mrdenb;

ELSE

stutter \leq 0';

END IF;

ELSE

stutter \leq 0';

END IF;

_____

-- Section: Backward Tag Decoding for PHY

-- Purpose: This section decodes the backward tag to determine

-- if the cell is to be routed to the switch or to a PHY.

-- If bwd tag[2:0] = to phy[2:0], then use bwd tag[4:3] to determine PHY#

-- else the cell is going to the switch.

-- The decoding circuit to handle cells going to the switch is found

-- in the ca decode section.

IF ((p state = transfer cell) or

(p state = pause and phy ca = (1)) THEN

IF (bwd_tag(2 downto 0) = to_phy(2 downto 0)) THEN

IF (ia = '1') THEN -- Indirect Addressing Mode

phy1wrenb \leq 0';

phv2wrenb <= '1':

phy3wrenb <= '1';

phy4wrenb <= '1':

ELSE -- Direct Mode

CASE bwd_tag(4 downto 3) IS

WHEN "00" =>

phy1wrenb \leq 0';

phy2wrenb \leq 1';

phy3wrenb <= '1';

phy4wrenb <= '1';

WHEN "01" =>

phy1wrenb <= '1':

phy2wrenb \leq 0';

phy3wrenb <= '1';

phy4wrenb <= '1';

WHEN "10" =>

phy1wrenb <= '1';

phy2wrenb \leq 1';

phy3wrenb \leq 0';

phy4wrenb <= '1';

WHEN others =>

phy1wrenb <= '1';

phy2wrenb \leq 1';

phy3wrenb <= '1';

phy4wrenb <= '0';

```

**ISSUE 1**

PM7322 RCMP-800

```

END CASE;

END IF; -- ia

ELSE

phv1wrenb \leq 1':

phy2wrenb <= '1';

phy3wrenb <= '1';

phy4wrenb <= '1';

END IF; -- bwd_tag

ELSE

phy1wrenb \leq 1';

phy2wrenb \leq 1';

phy3wrenb <= '1';

phy4wrenb <= '1';

END IF; -- p_state

END IF; -- rstb

END PROCESS state_decode;

_____

-- Process: counter

-- Purpose: This process implements a cell transfer counter.

_____

_____

counter : PROCESS (rstb, ofclk)

BEGIN -- PROCESS counter

IF (rstb = '0') THEN

cellcount \leq 0;

ELSIF (ofclk'EVENT and (ofclk = '1')) THEN

IF (rca s = '1' and p state = idle) THEN

cellcount \le 28; -28 = prepend + (27-word cell) + 1

ELSIF ((bwd_tag(2 downto 0) = to_switch(2 downto 0))

and p_state = transfer_cell and

((\text{cellcount} = 0) \text{ or } (\text{cellcount} = 1))

and mrdenb = '1' and stutter = '0') THEN

cellcount \leq 63 - cellcount - 1;

ELSIF ((bwd_tag(2 downto 0) = to_switch(2 downto 0))

and p_state = transfer_cell and

((cellcount = 61) or (cellcount = 62)) and mrdenb = '0') THEN

cellcount <= cellcount + 1;

ELSIF ((bwd tag(2 downto 0) = to switch(2 downto 0)))

and cellcount = 63) THEN

cellcount \leq 0;

ELSIF (rrdenbi = '0') THEN

cellcount \leq cellcount - 1;

ELSE

cellcount <= cellcount;

```

#### ISSUE 1

RCMP Egress Routing Logic in VHDL

END IF; END IF; END PROCESS counter;

END behav;