REFERENCE DESIGN PMC-198-0322 PMC-Sierra, Inc.

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

# PM5351

# S/UNI-TETRA

# S/UNI-TETRA REFERENCE DESIGN WITH WAN CLOCKING

# **REFERENCE DESIGN**

**ISSUE 3: JANUARY 2000**

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE

REFERENCE DESIGN PMC-198-0322 PMC-Sierra, Inc.

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

# **PUBLIC REVISION HISTORY**

| lssue<br>No. | Issue<br>Date   | Details of Change                                                                                                        |

|--------------|-----------------|--------------------------------------------------------------------------------------------------------------------------|

| 3            | January<br>2000 | Added WAN clocking implementation suggestion.<br>Added Design Consideration Section. Revised filtering<br>recommendation |

| 2            | Dec 1998        | Revised power filtering recommendation                                                                                   |

| 1            | Sept 1998       | Document created.                                                                                                        |

PMC-Sierra, Inc.

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

# **CONTENTS**

| 1 | INTRODUCTION1 |                               |  |  |  |  |  |  |

|---|---------------|-------------------------------|--|--|--|--|--|--|

| 2 | FEAT          | FEATURES 2                    |  |  |  |  |  |  |

| 3 | APPLICATIONS  |                               |  |  |  |  |  |  |

| 4 | DESI          | DESIGN OVERVIEW 5             |  |  |  |  |  |  |

| 5 | BLOO          | CK DIAGRAM 7                  |  |  |  |  |  |  |

| 6 | FUN           | CTIONAL DESCRIPTION           |  |  |  |  |  |  |

|   | 6.1           | S/UNI-TETRA                   |  |  |  |  |  |  |

|   | 6.2           | OPTICAL LINE INTERFACE 10     |  |  |  |  |  |  |

|   | 6.3           | MICROCONTROLLER BLOCK 10      |  |  |  |  |  |  |

|   | 6.4           | WAN CIRCUITRY BLOCK11         |  |  |  |  |  |  |

|   | 6.5           | SYSTEM SIDE LOOPBACK 12       |  |  |  |  |  |  |

|   | 6.6           | EXTERNAL CONNECTOR 13         |  |  |  |  |  |  |

| 7 | DESI          | GN CONSIDERATIONS 19          |  |  |  |  |  |  |

|   | 7.1           | PECL INTERFACE                |  |  |  |  |  |  |

|   |               | 7.1.1 RECEIVE INPUTS 19       |  |  |  |  |  |  |

|   |               | 7.1.2 TRANSMIT OUTPUTS 20     |  |  |  |  |  |  |

|   | 7.2           | FILTERING AND DECOUPLING 21   |  |  |  |  |  |  |

|   | 7.3           | UNUSED INPUT PINS AND CHANNEL |  |  |  |  |  |  |

|   | 7.4           | JTAG PORT 23                  |  |  |  |  |  |  |

|   | 7.5 ROUTING   |                               |  |  |  |  |  |  |

| 8 | IMPL          | EMENTATION DESCRIPTION 25     |  |  |  |  |  |  |

|   | 8.1           | ROOT DRAWING, SHEET 1 25      |  |  |  |  |  |  |

REFERENCE DESIGN

PMC-Sierra, Inc.

PM5351 S/UNI-TETRA

| PMC-198-0322 |      | ISSUE 3                     | S/UNI-TETRA REFERENCE DESIGN |

|--------------|------|-----------------------------|------------------------------|

|              | 8.2  | TETRA_BLOCK, SHEET 2 & 3    |                              |

|              | 8.3  | LOOPBACK_BLOCK, SHEET 4 & 5 | 25                           |

|              | 8.4  | SYS_INTERFACE, SHEET 6 & 7  |                              |

|              | 8.5  | MICRO_BLOCK, SHEET 8        |                              |

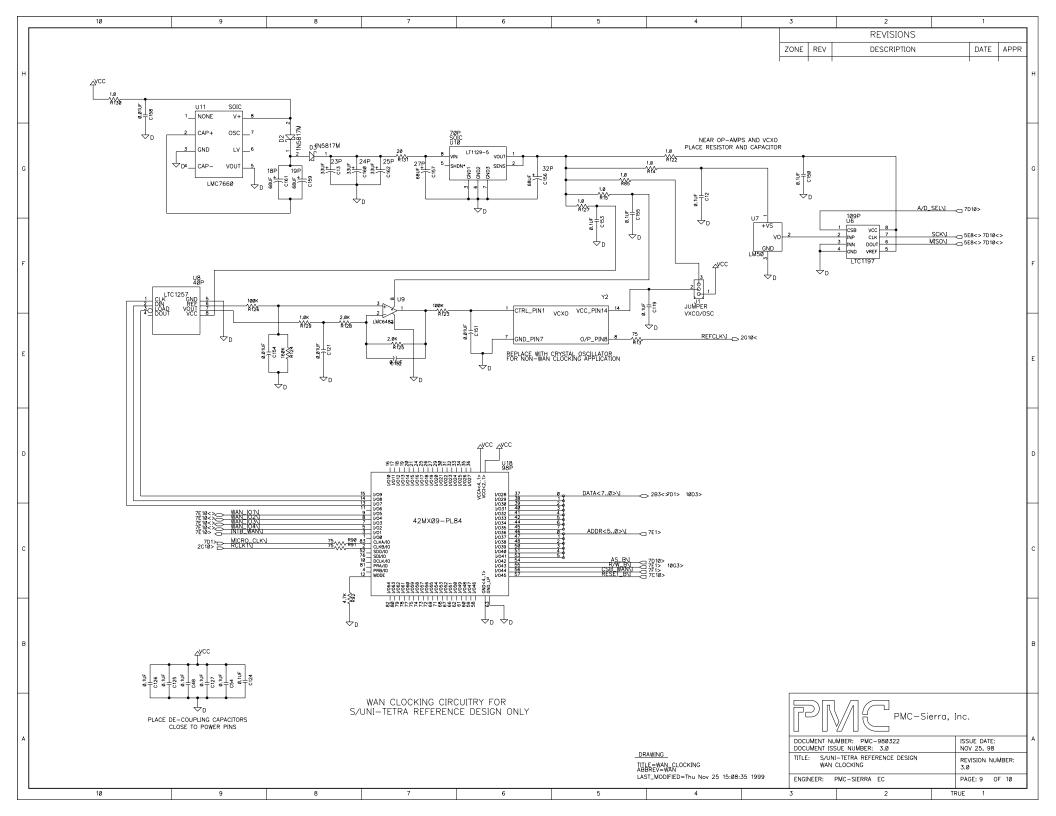

|              | 8.6  | WAN_CLOCKING, SHEET 9       |                              |

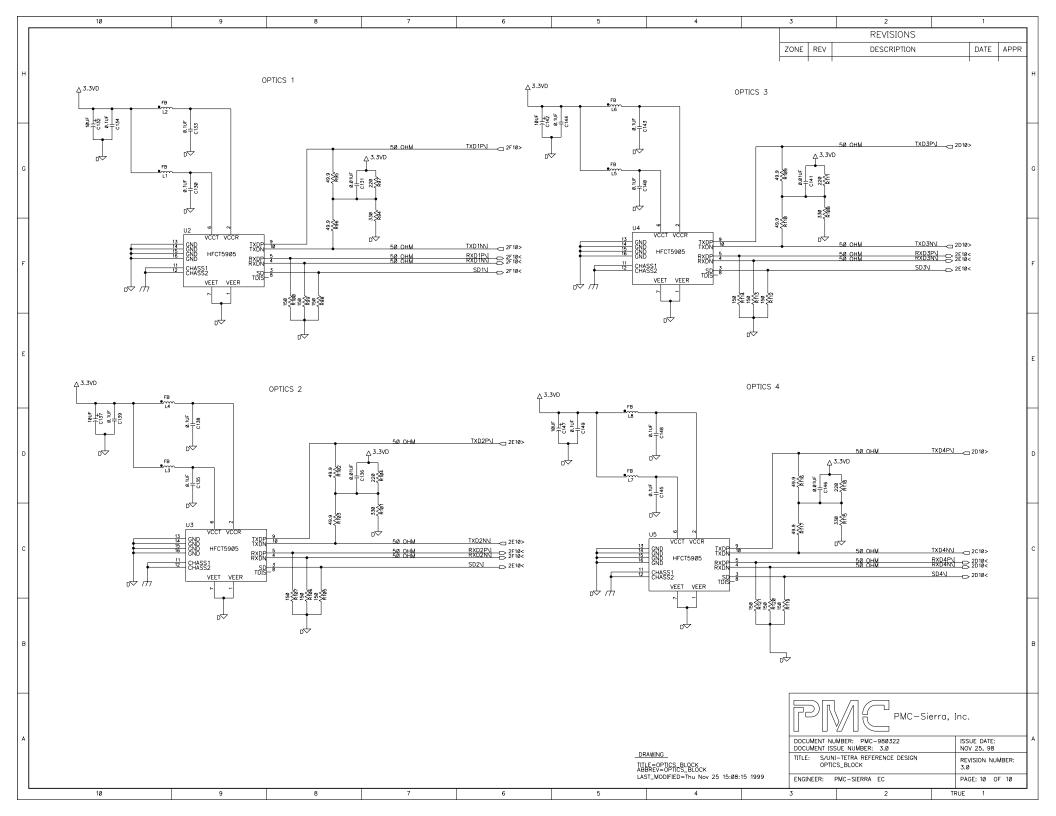

|              | 8.7  | OPTICS_BLOCK, SHEET 10      |                              |

| 9            | WAN  | CLOCKING PLL ALGORITHMS     |                              |

|              | 9.1  | FREQUENCY ACQUISITION       |                              |

|              | 9.2  | PHASE ACQUISITION           | 30                           |

|              | 9.3  | TRACKING                    |                              |

|              | 9.4  | HOLDOVER                    |                              |

| 10           | SCH  | EMATICS                     | 35                           |

|              | 10.1 | BILL OF MATERIALS           | 35                           |

| 11           | REFE | ERENCES                     |                              |

| 12           | APPE | ENDIX A                     |                              |

REFERENCE DESIGN PMC-198-0322 PMC-Sierra, Inc.

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

### **LIST OF FIGURES**

| FIGURE 1 : S/UNI-TETRA RD WITH PMC-SIERRA ATM CHIPSETS       | 3 |

|--------------------------------------------------------------|---|

| FIGURE 2 : S/UNI-TETRA REF DESIGN WITH POS LINK LAYER DEVICE | 4 |

| FIGURE 3 : STS-3C FRAME                                      | 8 |

| FIGURE 4 : DIGITAL PLL BLOCK DIAGRAM1                        | 1 |

| FIGURE 5 : LOOPBACK DIAGRAM 1                                | 2 |

| FIGURE 6 : RECEIVE RXD+/- INTERFACE 1                        | 9 |

| FIGURE 7 : RECEIVE SD INTERFACE 2                            | 0 |

| FIGURE 8 : TRANSMIT TXD+/- INTERFACE 2                       | 1 |

| FIGURE 9 : S/UNI-TETRA ANALOG FILTERING 2                    | 2 |

| FIGURE 10 : PLL ALGORITHM STATE DIAGRAM 2                    | 8 |

| FIGURE 11 : LOOP FILTER BLOCK DIAGRAM 3                      | 1 |

REFERENCE DESIGN PMC-198-0322 PMC-Sierra, Inc.

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

# LIST OF TABLES

| TABLE 1 : INTERFACE CONNECTOR ONE            | 13 |

|----------------------------------------------|----|

| TABLE 2 : INTERFACE CONNECTOR TWO            | 15 |

| TABLE 3 : PHASE TRANSIENT MTIE SPECIFICATION | 33 |

| TABLE 4 : MAJOR COMPONENTS LIST              | 35 |

REFERENCE DESIGN PMC-198-0322

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

# 1 INTRODUCTION

The PM5351 S/UNI-TETRA standard product is a Quad SATURN User Network Interface with SONET/SDH processing, ATM and Packet mapping functions at the STS-3c (STM-1) 155.52 Mbit/s rate. The S/UNI-TETRA is intended for use in equipment implementing Asynchronous Transfer Mode (ATM) User-Network Interface (UNI), ATM Network-Network Interfaces (NNI), and Packet over Sonet (POS) interfaces. The POS interface can be used to support several packet based protocols, including the Point-to-Point Protocol (PPP). The S/UNI-TETRA may find application at either end of switch-to-switch links or switch-to-terminal links, both in public network (WAN) and private network (LAN) situations.

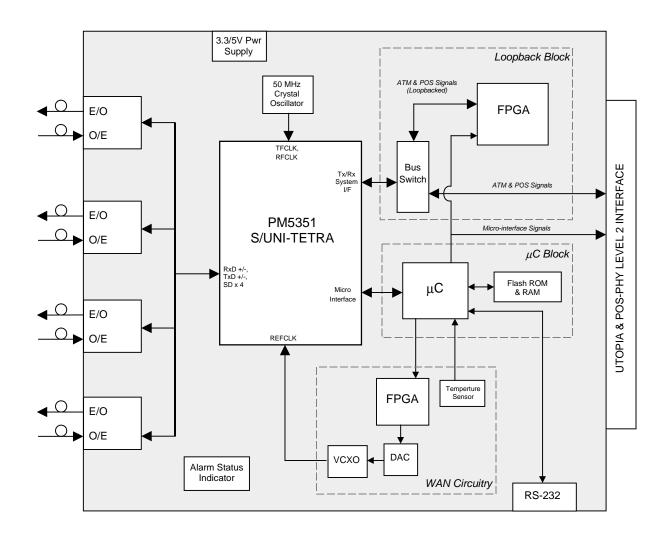

The S/UNI-TETRA reference design provides a physical interface implementation of a SONET/SDH line card for both ATM and POS applications. It provides four optical interfaces at OC-3 rates and a system side interface of 25MHz to 50MHz for a 16-bit wide bus. For WAN applications, this reference design provides an example implementation of a Digital PLL for satisfying Bellcore Stratum 3 Clock synchronization requirements.

All recommendations in this document are preliminary and are subject to change. Please check PMC-Sierra website for newest updates on new document releases and errata. If change notification is nessesary, customers can sign up for the change notification mailing list on the PMC-Sierra website.

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

#### 2 FEATURES

- Provides four OC-3 rate 155.52 Mbits/s SONET/SDH Physical Layer Ports

- Provides a Utopia Level 2, 50 MHz, 16-bit ATM Multi-PHY System Interface

- Provides a POS-PHY Level 2, 50 MHz, 16-bit Packet Over Sonet Multi-PHY System Interface

- Contains an on-board microcontroller to provide WAN clocking requirements related to wander transfer, holdover and long time stability when using external VCXO

- Provides Dropside Loopback for Diagnostic Purposes

- Provides a software package for demonstration and evaluation of the S/UNI-TETRA reference board

REFERENCE DESIGN PMC-198-0322

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

## 3 APPLICATIONS

The S/UNI-TETRA reference design demonstrates the physical interface implementation for both ATM or POS applications. The list below shows the networking equipment that can incorporate the S/UNI-TETRA device:

- WAN and Edge ATM switches physical Interface

- LAN switches and hubs physical Interface

- Packet switches and hubs physical interface

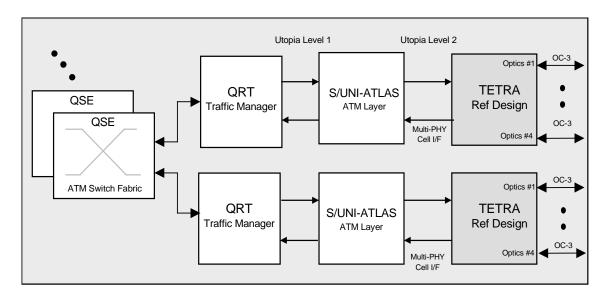

In an ATM application, the S/UNI-TETRA reference designs interfaces to four OC-3 rate SONET/SDH signal on the line side. On the drop side, the S/UNI-TETRA interfaces directly with ATM layer processors and switching or adaptation functions using a Utopia Level 2 compliant synchronous FIFO style interface. Figure 1 shows an example of the S/UNI-TETRA reference design in a complete ATM switching design using PMC-Sierra's ATM chipsets.

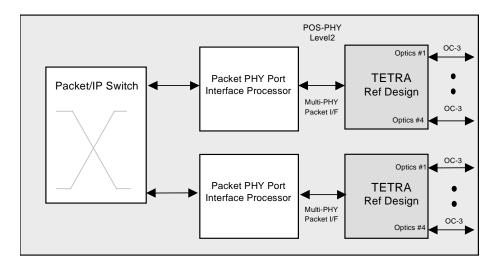

In a Packet Over Sonet application, using PPP protocol, the S/UNI-TETRA reference design interfaces to a OC-3 rate SONET/SDH signal on the line side. On the drop side, the S/UNI-TETRA reference design interfaces directly with a PPP link layer processor using a 256 byte synchronous FIFO interface over

S/UNI-TETRA REFERENCE DESIGN

which packets are transferred. Figure 2 shows the S/UNI-TETRA reference design in a POS application.

# Figure 2 : S/UNI-TETRA Ref Design with POS Link Layer Device

REFERENCE DESIGN PMC-198-0322

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

## 4 DESIGN OVERVIEW

The S/UNI-TETRA reference design consists of a S/UNI-TETRA device and four optical transceivers in a four port optical physical interface for either Asynchronous Transfer Mode (ATM) or Packet Over Sonet (POS) applications. The S/UNI-TETRA reference design contains an on-board microcontroller, Motorola 68332, and related WAN circuitry to perform WAN synchronization using the S/UNI-TETRA's WANS block. The dropside Loopback function is provided by an on-board FPGA. The S/UNI-TETRA reference design is capable of a maximum bandwidth of approximately 622 Mbps and can be used as an ATM or POS line card.

The S/UNI-TETRA reference design provides a dual-mode physical layer interface to upper link layer devices. For ATM application, the S/UNI-TETRA reference design supports the Utopia level 2 ATM PHY to ATM Layer specification. Since the S/UNI-TETRA is a quad PHY chip, the PHY interface can be configured as multi-PHY address polling at 50 MHz over a 16 bit bus.

For Packet over Sonet, the S/UNI-TETRA reference design supports POS-PHY level 2 standard for interfacing to a packet link layer device. The S/UNI-TETRA reference design connects to an upper POS layer device using a 16 bit wide data bus running at 50MHz. The S/UNI-TETRA supports both byte and packet level transfer modes as defined in the POS-PHY Level II specification.

The S/UNI-TETRA reference design also implements a WAN synchronization circuit that meets Bellcore GR-253-CORE SONET Stratum 3 or lower NE clocking requirements. The WAN circuitry generates a reference clock that satisfies wander transfer, long term and holdover stability according to the Bellcore specification by utilizing the S/UNI-TETRA's WANS block.

The loopback feature allows the receive data to be looped back to the transmit stream at the drop side. This allows the evaluation of both the line side and drop side interface. An external Field Programmable Gate Array (FPGA) implements the loopback feature and provides a microprocessor interface to the 68322 microcontroller. This FPGA also provides transmit data reclocking. The FPGA reclocks the transmit data and control signals to meet the setup and hold times of the S/UNI-TETRA device.

The S/UNI-TETRA reference design can be run either as a stand-alone evaluation platform or interfaced to other S/UNI reference designs. As a standalone board, the S/UNI-TETRA reference design allows access to on-chip registers, performs WAN clocking function, and performs system side loopback feature for both ATM and POS. When interfaced to other reference boards, cell

REFERENCE DESIGN PMC-198-0322

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

and packet generation functions are provided by these external boards for further demonstration and evaluation of the S/UNI-TETRA device.

REFERENCE DESIGN PMC-198-0322 PMC-Sierra, Inc.

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

## 5 BLOCK DIAGRAM

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE 7

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

#### 6 FUNCTIONAL DESCRIPTION

#### 6.1 S/UNI-TETRA

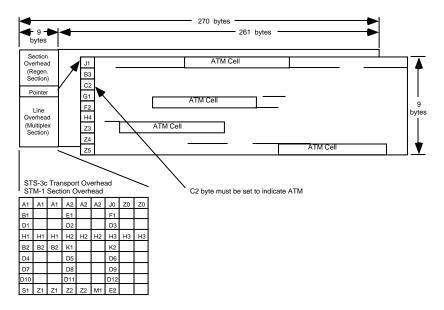

The PM5351 S/UNI-TETRA SATURN User Network Interface is a monolithic integrated circuit that implements four channel SONET/SDH processing, ATM mapping and Packet over SONET mapping functions at the STS-3c (STM-1) 155.52 Mbit/s rate. Figure 3 shows the overhead of a STS-3c frame.

#### Figure 3 : STS-3c Frame

The S/UNI-TETRA receives the SONET/SDH streams using a bit serial interface, recovers the clock and data and processes section, line, and path overhead. It performs framing (A1, A2), descrambling, detects alarm conditions, and monitors section, line, and path bit interleaved parity (B1, B2, B3) while accumulating error counts at each level for performance monitoring purposes. Line and path far end block error indications (M1, G1) are also accumulated. The S/UNI-TETRA interprets the received payload pointers (H1, H2) and extracts the synchronous payload envelope which carries the received ATM cell or POS packet payload.

When used to implement an ATM UNI or NNI, the S/UNI-TETRA frames to the ATM payload using cell delineation. HCS error correction is provided. Idle/unassigned cells may be dropped according to a programmable filter. Cells are also dropped upon detection of an uncorrectable header check sequence error. The ATM cell payloads are descrambled. The ATM cells that are passed are written to a four cell FIFO buffer. The received cells are read from the FIFO using a generic 16 wide Utopia level 2 compliant datapath interface. Counts of

REFERENCE DESIGN PMC-198-0322

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

received ATM cell headers that are errored and uncorrectable and also those that are errored and correctable are accumulated independently for performance monitoring purposes. For the transmit stream, ATM cells are written to an internal four cell FIFO using a generic 16-bit wide datapath interface. Idle/unassigned cells are automatically inserted when the internal FIFO contains less than one cell. The S/UNI-TETRA provides generation of the header check sequence and scrambles the payload of the ATM cells. Each of these transmit ATM cell processing functions can be enabled or bypassed.

When used to implement Packet transmission over a SONET/SDH link, the S/UNI-TETRA extracts Packet over SONET (POS) frames from the SONET/SDH synchronous payload envelope. Frames are verified for correct construction and size. The Control Escape characters are removed. The error check sequence is optionally verified for correctness and the extracted packet is placed in a received FIFO. The received packets are read from the FIFO through the drop side interface. Valid and errored packet counts are provided for performance monitoring. The S/UNI-TETRA Packet over SONET implementation is flexible enough to support several link layer protocols, including HDLC, PPP and Frame Relay. For the transmit stream, the S/UNI-TETRA inserts POS frames into the SONET/SDH synchronous payload envelope. Packets to be transmitted are written into a 256-byte FIFO through the System Interface. POS Frames are built by inserting the flags, Control Escape characters and the FCS fields. Either the CRC-CCITT or CRC-32 can be computed and added to the frame. Several counters are provided for performance monitoring.

No line rate clocks are required directly by the S/UNI-TETRA as it synthesizes the transmit clock and recovers the receive clock using a 19.44 MHz reference clock. Normally the S/UNI-TETRA outputs only a differential PECL line data (TXD+/-). Optionally, the S/UNI-TETRA can output a differential transmit line rate clock (TXC+/-). The S/UNI-TETRA also provides a WAN Synchronization controller that can be used to control an external VCXO in order to fully meet Bellcore GR-253-CORE jitter, wander, holdover and stability requirements. Details of the S/UNI-TETRA can be found in the S/UNI-TETRA datasheet, PMC-971028.

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

#### 6.2 Optical Line Interface

The S/UNI-TETRA reference design provides four optical line interfaces at the 155.52 Mbit/s OC-3 rate. The line interface consists of four optical data links (ODL) and a termination scheme for the PECL signals into and out from the four S/UNI-TETRA transmit and receive signal pairs. The suggested termination scheme is discussed in the design consideration section.

In normal operation, the S/UNI-TETRA performs clock recovery and serial to parallel conversion on the incoming data stream. In a loss of signal condition, indicated on each of the four SD pins, the S/UNI-TETRA will squelch the receive data and the clock recovery unit and will switch to the reference clock (19.44MHz) to keep the recovered clock in range. This technique guarantees that the S/UNI-TETRA will generate an LOS indication when the ODL loses the incoming optical signal.

For this reference design, 3.3V ODL transceivers are used to reduce power consumption and match PECL level signals.

#### 6.3 Microcontroller Block

The S/UNI-TETRA reference design uses the 32-bit Motorola 68332 microcontroller running at 16.7MHz as its on-board processor. The microcontroller block contains separate flash ROM and RAM for program data storage and run-time program execution. The S/UNI-TETRA registers are accessed through a 10-bit address and a 8-bit data bus microprocessor interface by the 68322.

The microcontroller can be accessed through either the RS-232 port or the Background Debugging Mode (BDM) connector on the reference board. The RS-232 port allows the access to the serial port on the 68332. The RS-232 port can be connected to a serial COM port on a PC by using a DB9 to DB9 cable. The firmware for the reference design resides in the FLASH ROM. A user can use any VT100 terminal emulation program to interface to the firmware and access the hardware on the reference board. The serial port terminal should be set to 9600 Baud, 8 data bits, no parity, and 1 stop bit.

The microcontroller also provides additional control to external adapter cards through the Utopia/POS-PHY interface connector. This allows the microcontroller to access external devices.

S/UNI-TETRA REFERENCE DESIGN

#### REFERENCE DESIGN PMC-198-0322

# 6.4 WAN Circuitry Block

Note: Due to the complexity and the nature of the design, WAN clocking is shown as a reference only and will not be supported by the PMC Applications Department

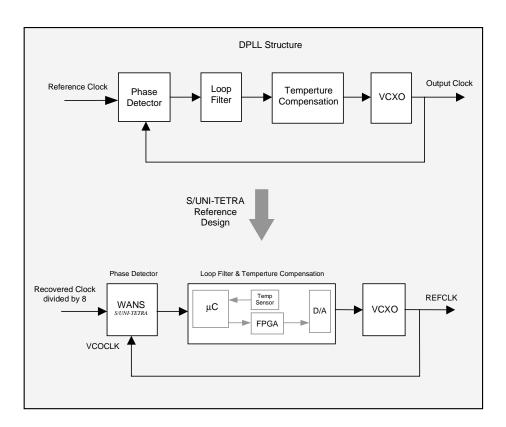

The WAN Circuitry Block consists of a VCXO, a DAC, and a temperature sensor. The WAN circuitry utilizes the S/UNI-TETRA's WANS phase comparator function block. Together with the WANS block, the S/UNI-TETRA reference design provides a complete digital PLL clocking design for generating a stratum level 3 clock that satisfies wander, jitter transfer, long term and holdover stability. It can provide a timing reference for a SONET network element (NE), such as an Add-Drop Multiplexer (ADM), a Service Access Multiplexer (SAM), or an Enterprise ro Edge Switch. The circuitry is designed to meet the requirements for the line timing mode of SONET NE as specified in GR-235-CORE Issue 2.

The general block structure of a digital PLL and the block diagram of the PLL implementation on the S/UNI-TETRA can be seen in Figure 5 below.

#### Figure 4 : Digital PLL Block Diagram

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

The WANS block derives a 31 bit phase value based on the phase relationship between the recovered clock, RCLK and the VCXO clock, VCOCLK. The digital PLL algorithm is performed by the FPGA on-board to reduce microprocessor load. The PLL algorithm can also be entirely implemented in software using the 68322 microcontroller. Together with the DAC and temperature sensor, the WAN circuitry block provides temperature and VCXO linearity compensation. Section 9 describes the operation of the PLL algorithm.

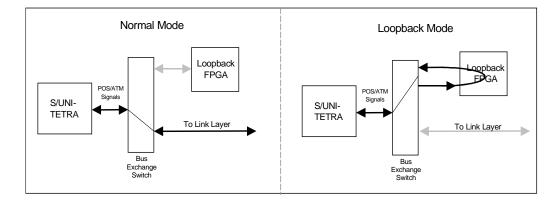

## 6.5 System Side Loopback

The Loopback block consists of a FPGA and a bus exchange switch. The Bus exchange switch allows the S/UNI-TETRA's system side to be either connected to an external FPGA for loopback functionality or to a link layer interface board. The bus exchange switch adds minimum delay and presents low capacitance and impedance to the line. The loopback setup is as shown in Figure 6 below.

## Figure 5 : Loopback Diagram

In normal mode, the S/UNI-TETRA's Dropside data and control signals are connected to the system interface connector. In loopback mode, the receive data and control signals are input into and loopbacked out of the FPGA as transmit signals. The FPGA supports both ATM and POS loopbacks. The loopback block supports multi-PHY direct status addressing mode with each PHY having a separate cell/packet available signals for receive interface(DRCA/DRPA).

In loopback mode, the FPGA polls for both receive and transmit cells/packets available signals. The FPGA starts to receive and transmit cells/packets only when a PHY received data is available. This eliminates the need to implement a FIFO inside the FPGA.

PM5351 S/UNI-TETRA

REFERENCE DESIGN PMC-198-0322

S/UNI-TETRA REFERENCE DESIGN

#### 6.6 External Connector

The S/UNI-TETRA reference design contains two Molex connectors for interfacing to a link layer board. The Molex connectors have been measured with a network analyzer and showed adequate results for running at 50MHz.

The first connector is used for microprocessor communication between the two microcontroller on the S/UNI-TETRA reference and an in-house motherboard. It supplies both 3.3V and 5V power supply to the S/UNI-TETRA board. It is also used for the FIFO clock signals for both the Utopia and POS-PHY interface. The second connector is used for interfacing Utopia and POS-PHY data and control signals.

| Pin<br>Name | Туре              | Pin<br>No. | Function                                                                                                                                                                                                          |

|-------------|-------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK         | Input /<br>Output | D17        | Serial Clock. Clock for the microcontroller's QSPI module                                                                                                                                                         |

| MISO        | Input /<br>Output | D19        | Master In Slave Out. Serial Data for the microcontroller's QSPI module.                                                                                                                                           |

| MOSI        | Input /<br>Output | D18        | Master Out Slave In. Serial Data for the microcontroller's QSPI module.                                                                                                                                           |

| CS_MICRO    | Input /<br>Output | D20        | Chip select for communication between the microcontrollers on the S/UNI-TETRA and a motherboard.                                                                                                                  |

| M/S_MICRO   | Input             | D21        | Signal to indicate if the MB1503 is the<br>master or slave for the QSM bus. For<br>M_MICRO = 0, the micro on the TETRA<br>board is the master. For M_MICRO = 1, the<br>motherboard acts as the master.            |

| INTB_TETRA  | Output            | D27        | Interrupt signal from the S/UNI-TETRA device                                                                                                                                                                      |

| RFCLK-      | Output            | D35        | Negative differential receive clock signal.<br>This signal, along with RFCLK+ comprise<br>the differential RFCLK clock signal sent<br>across the connector. RFCLK is to be used<br>as a reference to sample RDAT. |

#### Table 1 : Interface Connector One

PMC-Sierra, Inc.

PM5351 S/UNI-TETRA

REFERENCE DESIGN PMC-198-0322

ISSUE 3

| Pin<br>Name | Туре   | Pin<br>No.                                                                                                      | Function                                                                                                                                                                                                          |

|-------------|--------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RFCLK+      | Output | D36                                                                                                             | Positive differential receive clock signal.<br>This signal, along with RFCLK- comprise<br>the differential RFCLK clock signal sent<br>across the connector. RFCLK is to be used<br>as a reference to sample RDAT. |

| TFCLK+      | Input  | D39                                                                                                             | Positive differential transmit clock signal.<br>This signal, along with TFCLK+ comprise<br>the differential TFCLK clock signal sent<br>across the connector. TFCLK is used as a<br>reference to sample TDAT.      |

| TFCLK-      | Input  | D40                                                                                                             | Negative differential transmit clock signal.<br>This signal, along with TFCLK- comprise the<br>differential TFCLK clock signal sent across<br>the connector. TFCLK is used as a<br>reference to sample TDAT.      |

| RMOD        | Output | A39                                                                                                             | <u>POS-PHY: Receive Modulo</u><br>This signal indicates the number of bytes<br>carried by the RDAT bus                                                                                                            |

| RVAL        | Output | A40                                                                                                             | POS-PHY: Receive Data Valid<br>This signal indicates the validity of the<br>receive data signal                                                                                                                   |

| NC          | NC     | A20 -<br>A38,<br>B17 -<br>B30,<br>C1 -<br>C30,<br>D1 -<br>D16,<br>D20 -<br>D22,<br>D28 -<br>D34,<br>D37,<br>D38 | Not Connected.                                                                                                                                                                                                    |

| + 5V        | Input  | A1,<br>A2,<br>B1, B2                                                                                            | + 5 Volt supply                                                                                                                                                                                                   |

REFERENCE DESIGN PMC-198-0322

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

| Pin<br>Name | Туре  | Pin<br>No.                                                      | Function          |

|-------------|-------|-----------------------------------------------------------------|-------------------|

| + 3.3V      | Input | A3-A9,<br>B3-B9,                                                | + 3.3 Volt supply |

| GND         | Input | A10 -<br>A19,<br>B10 -<br>B16,<br>B31 -<br>B40,<br>C31 -<br>C40 | Ground            |

# Table 2 : Interface Connector Two

| Pin Name | Туре   | Pin<br>No. | Function                                                                            |

|----------|--------|------------|-------------------------------------------------------------------------------------|

| RDAT[0]  | Output | A1         | UTOPIA: Receive Cell Data Bus                                                       |

| RDAT[1]  |        | D1         | This bus carries the ATM cell octets that are                                       |

| RDAT[2]  |        | A2         | read from the selected receive FIFO.                                                |

| RDAT[3]  |        | D2         |                                                                                     |

| RDAT[4]  |        | A3         |                                                                                     |

| RDAT[5]  |        | D3         |                                                                                     |

| RDAT[6]  |        | A4         |                                                                                     |

| RDAT[7]  |        | D4         | POS-PHY: Receive Packet Data Bus                                                    |

| RDAT[8]  |        | A5         | This bus carries Packets that are read from                                         |

| RDAT[9]  |        | D5         | the selected receive FIFO                                                           |

| RDAT[10] |        | A6         |                                                                                     |

| RDAT[11] |        | D6         |                                                                                     |

| RDAT[12] |        | A7         |                                                                                     |

| RDAT[13] |        | D7         |                                                                                     |

| RDAT[14] |        | A8         |                                                                                     |

| RDAT[15] |        | D8         |                                                                                     |

| RPRTY    | Output | A9         | Receive bus parity. The receive parity signal indicates the parity of the RDAT bus. |

REFERENCE DESIGN PMC-198-0322

ISSUE 3

| Dia Mara                                                 | <b>T</b> | <b>D</b> :                     | <b>F</b> unction                                                                                                                                            |

|----------------------------------------------------------|----------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                 | Туре     | Pin<br>No.                     | Function                                                                                                                                                    |

| DRCA[1]<br>DRCA[2]<br>DRCA[3]<br>DRCA[4]                 | Output   | A10<br>A11<br>A12<br>A13       | UTOPIA: Direct Receive Cell Available<br>These signals indicate available cells to be<br>transferred across the UTOPIA bus.                                 |

| DRPA[1]<br>DRPA[2]<br>DRPA[3]<br>DRPA[4]                 |          | A10<br>A11<br>A12<br>A13       | POS-PHY: Direct Receive Packet Available<br>These signals indicate available packet to<br>be transferred across the POS-PHY bus.                            |

| RADDR[0]<br>RADDR[1]<br>RADDR[2]<br>RADDR[3]<br>RADDR[4] | Input    | D9<br>D10<br>D11<br>D12<br>D13 | Receive PHY port address. These signals are used to select the PHY port to be read from or polled.                                                          |

| RENB                                                     | Input    | A14                            | Receive Multi-Phy Write Enable. The RENB signal is an active low input which is used to initiate reads from the receive FIFOs.                              |

| RCA                                                      | Output   | A15                            | UTOPIA: Receive Multi-PHY Cell Available<br>This signal indicates an available cell during<br>receive PHY port polling                                      |

| PRPA                                                     |          | A15                            | POS-PHY: Polled multi-PHY Receive<br>Packet Available. This signal indicates<br>when data is available in the polled receive<br>FIFO.                       |

| RSOC                                                     | Output   | D14                            | UTOPIA: Receive Start of Cell<br>This signal marks the start of cell on the<br>RDAT bus.                                                                    |

| RSOP                                                     |          | D14                            | POS-PHY: Receive Start of Packet<br>This signal marks the start of packet on the<br>RDAT bus.                                                               |

| RERR                                                     | Output   | D15                            | POS-PHY: Receive Error<br>This signal indicates that the current packet<br>has been aborted.                                                                |

| REOP                                                     | Output   | D16                            | POS-PHY: Receive End of Packet<br>This signal marks the end of packet on the<br>RDAT bus                                                                    |

| TENB                                                     | Input    | A27                            | Utopia and POS-PHY:<br>Transmit Multi-Phy Write Enable. The<br>TENB signal is an active low input which is<br>used to initiate writes to the transmit FIFOs |

PMC-198-0322

REFERENCE DESIGN

ISSUE 3

| Pin Name                                                 | Туре   | Pin<br>No.                      | Function                                                                                                                                                                               |

|----------------------------------------------------------|--------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCA                                                      | Output | D26                             | Utopia: Transmit cell available signal<br>This signal is used to indicate available cell<br>FIFO space by polled PHY ports.                                                            |

| ΡΤΡΑ                                                     |        | D26                             | POS-PHY: Polled Transmit multi-PHY<br>Packet Available. This signal transitions to<br>high when a programmable minimum<br>number of bytes is available in the polled<br>transmit FIFO. |

| TSOC                                                     | Input  | A28                             | Utopia: Transmit Start of Cell<br>The transmit start of cell signal marks the<br>start of cell on the TDAT bus.                                                                        |

| TSOP                                                     |        | A28                             | POS-PHY: Transmit Start of Packet<br>This signal indicates the first word of a<br>packet.                                                                                              |

| TADDR[0]<br>TADDR[1]<br>TADDR[2]<br>TADDR[3]<br>TADDR[4] | INPUT  | D27<br>D28<br>D29<br>D30<br>D31 | Transmit Address. The TADR[4:0] bus is used to select the port that is to be written to or being polled.                                                                               |

| DTCA[1]<br>DTCA[2]<br>DTCA[3]<br>DTCA[4]                 | Output | A29<br>A30<br>A31<br>A32        | Utopia: Direct Transmit Cell Available<br>These signals indicate available cells to be<br>transferred across the UTOPIA.                                                               |

| DTPA[1]<br>DTPA[2]<br>DTPA[3]<br>DTPA[4]                 |        | A29<br>A30<br>A31<br>A32        | POS-PHY: Direct Transmit Packet Available<br>These signals provide direct status<br>indication of when some programmable<br>number of bytes is available in the transmit<br>FIFO.      |

| TERR                                                     | Input  | A22                             | POS-PHY: Transmit Error<br>This signal indicates the current packet<br>must be aborted.                                                                                                |

| TEOP                                                     | Input  | A25                             | POS-PHY: Transmit End of Packet<br>This signal marks the end of a packet on the<br>TDAT bus.                                                                                           |

| STPA                                                     | Output | A25                             | POS-PHY: Selected multi-PHY Transmit<br>Packet Available<br>This signal transitions high when a<br>predefined minimum number of bytes is<br>available in the selected transmit FIFO.   |

PM5351 S/UNI-TETRA

REFERENCE DESIGN PMC-198-0322

ISSUE 3

|                                                                                                                                                                                               | Туре  | Pin<br>No.                                                                                                          | Function                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMOD                                                                                                                                                                                          | Input | A26                                                                                                                 | POS-PHY: Transmit Word Modulo<br>This signal indicates the size of the current<br>word.                                                                                                                                                                                   |

| TPRTY                                                                                                                                                                                         | INPUT | D32                                                                                                                 | Transmit bus parity. The transmit parity signal indicates the parity of the TDAT bus.                                                                                                                                                                                     |

| TDAT[0]<br>TDAT[1]<br>TDAT[2]<br>TDAT[3]<br>TDAT[4]<br>TDAT[5]<br>TDAT[6]<br>TDAT[6]<br>TDAT[7]<br>TDAT[8]<br>TDAT[9]<br>TDAT[10]<br>TDAT[10]<br>TDAT[11]<br>TDAT[12]<br>TDAT[13]<br>TDAT[14] | INPUT | A40<br>D40<br>A39<br>D39<br>A38<br>D38<br>A37<br>D37<br>A36<br>D37<br>A36<br>D36<br>A35<br>D35<br>A34<br>D34<br>A33 | Utopia: Transmit Cell Data Bus<br>This bus carries the ATM cell octets that are<br>written to the selected transmit FIFO.<br><u>POS-PHY:</u> Transmit Packet Data Bus<br>This data bus carries the POS packet octets<br>that are written to the selected transmit<br>FIFO |

REFERENCE DESIGN PMC-198-0322

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

### 7 DESIGN CONSIDERATIONS

#### 7.1 PECL INTERFACE

#### 7.1.1 RECEIVE INPUTS

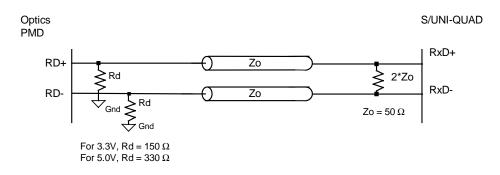

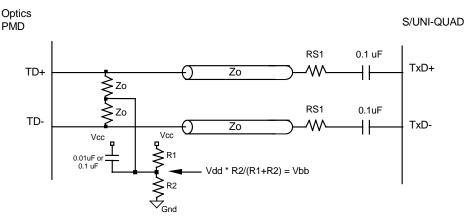

The S/UNI-TETRA's receive RxD+/- inputs are implemented as a true differential PECL receiver. The receive signals are high-speed signals and must be properly terminated to reduce reflection. Unlike previous generation S/UNI products, the S/UNI-TETRA RxD+/- pair are not self-biased to the PECL Vbb level. Given that the RxD+/- inputs have wide common mode operating voltage, the receive inputs can be directly DC-coupled from the optics.

Most of the commercially available optics on the market today provide PECL level RxD+/- outputs. The emitter on these PECL outputs need to be biased through a series resistor ground to provide adequate signal levels on the outputs. For 3.3V PECL drivers, a 150 Ohm series resistor is recommended. For 5V PECL drivers, a 330 Ohm series resistor is recommeded. The bias resistor location and value is shown in Figure 6. The RxD+/- differential signals require termination at the S/UNI-TETRA's input. With 50 ohm controlled impedence lines, a 100 ohm resistor connected across the RxD+/- pair can properly terminate the signal with minimum current draw.

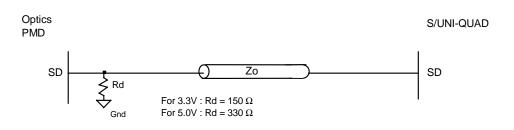

## Figure 6 : Receive RxD+/- Interface

The SD detect input can also be DC-coupled from the SD output from an Optics. Similar to the optics RxD+/-'s outputs, the optic's SD output needs a emitter biasing resistor. Since SD is a relative slow signal, termination is not required at the S/UNI-TETRA. The SD input on the S/UNI-TETRA can also be supplied from a TTL or CMOS source as long as the input signal level doesn't exceed the receiver voltage reference(3.3V or 5V).

REFERENCE DESIGN PMC-198-0322

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

#### Figure 7 : Receive SD Interface

PMC-Sierra, Inc.

#### 7.1.2 TRANSMIT OUTPUTS

The S/UNI-TETRA's transmit TxD+/- outputs are 3.3V CMOS rail to rail outputs. Since most of the optics have PECL level TxD+/- inputs, the TxD+/- signal from the S/UNI-TETRA needs to be converted to PECL level.

The PECL level conversion is done by first AC-coupling the TxD+/- outputs and attenuating the output voltage swing to PECL level. The PECL voltage swing is typically 800mV where as the S/UNI-TETRA outputs provide 3.3V swing. The 800mV swing can be attained by inserting a series resistor between the 50 Ohm impedance line and the AC-coupled resistor. The exact calculation of this attenuation resistor value is shown in figure 8. At the optics TxD+/- inputs, the 800mV voltage level needs to swing around the PECL bias point. For 5V PECL, the bias point is 3.7V and for 3.3V LVPECL, the bias point is 2.0V. A simple voltage divider network is shown in figure 8 for biasing the TxD+/- inputs to the PECL center point. The Vdd reference for the resistor and capacitor should be the same as the optics Vdd. Two 50 ohm resistors between the TxD+/- line and the PECL bias point provide the proper termination

The S/UNI-TETRA's transmitter and external termination circuity have been designed and throughly tested to meet Bellcore and ANSI jitter generation requirements. Using single-ended transmit output is not recommended due to duty-cycle distortion and poor jitter performance.

PM5351 S/UNI-TETRA

REFERENCE DESIGN PMC-198-0322

S/UNI-TETRA REFERENCE DESIGN

Notes: Vpp is minimum input swing required by the optical PMD device.

Vbb is the switching threshold of the PMD device (typically Vdd - 1.3 volts)

$\begin{array}{l} \mbox{Vpp is Voh - Vol (typically 800 mVolts)} \\ \mbox{Vpp } = (Zo/((RS1+Rs)+Z0) * Vdd \\ & - Vdd (S/UNI-QUAD's analog transmit power) 3.3V \\ & - Zo (trace impedance) typically 50\Omega \\ & - Rs (TxD source impedance) typically 15-20\Omega \\ & - RS1 : ~ 158\Omega \\ \\ \mbox{Vcc} = Optics Power (5.0V or 3.3V) \\ \mbox{For interfacing to 5.0V ODL, R1 : 237\Omega, R2 : 698\Omega \\ \\ \mbox{For interfacing to 3.3V ODL, R1 : 220\Omega, R2 : 330\Omega \\ \end{array}$

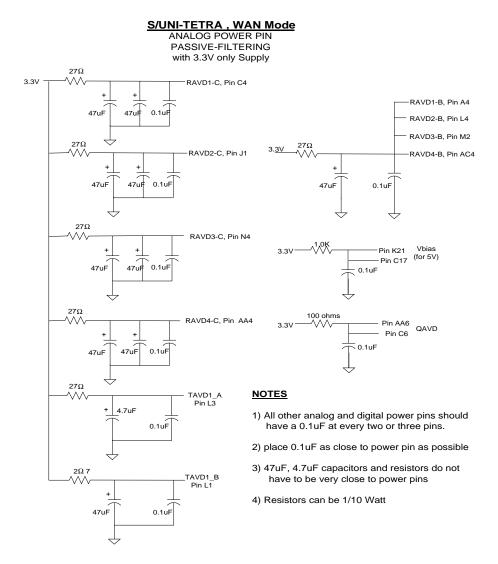

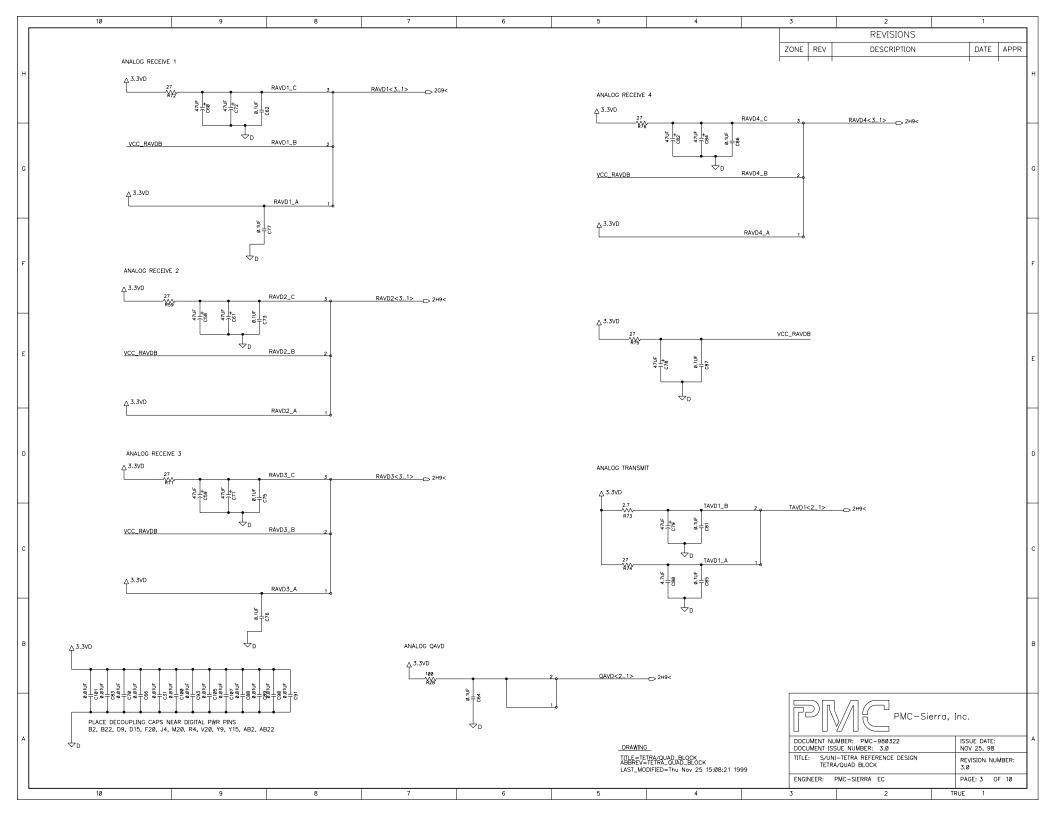

## 7.2 FILTERING AND DECOUPLING

High speed analog circuitry is generally sensitive to any amount of broadband noise on its power supply. The S/UNI-TETRA analog clock recovery and synthesize circuitry has been designed to meet all the stringent Bellcore/ANSI requirements on jitter generation, tolerance, and transfer. For this reason, the analog power supply rail must be well filterd and decoupled to achieve optimum jitter performance.

Care should be taken to reduce the noise at the CSU power pins, TAVD1\_A and TAVD2\_B and CRU power pins, RAVDBs and RAVDCs. Since each board design can have different noise levels on the power rail, the analog filtering circuit shown in figure 9 is recommended to ensure that the S/UNI-TETRA will be within 10% of its optimal jitter performance even when powered in a noisy environment.

The RC filtering circuitry provides a pole of around 63Hz for the purpose of filtering out low frequency noise. A single uncut ground plane can be used for all

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

S/UNI-TETRA board designs for both digital and analog circuitry. Ferrite beads are not recommended as a large big ferrite value will be needed to have a pole at the same frequency as an RC circuit and because LC circuity self-resonates at certain frequencies.

For the digital power pins, place  $0.1\mu$ F caps near the following VDD pins: B2, B22, D9, D15, F20, J4, M20, R4, V20, Y9, Y15, AB2, and AB22. A 100 Ohm resistor should be added in series with the quiet analog pins QAVD1 and 2. This impedance will protect the device from latching-up during power up. The filtering scheme below assumes the digital and analog power pins are connected to the same 3.3V power plane since 0.1µF decoupling capacitors are shared among some digital and analog power pins.

# Figure 9 : S/UNI-TETRA Analog Filtering

REFERENCE DESIGN PMC-198-0322

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

# 7.3 UNUSED INPUT PINS AND CHANNEL

All unused input pins on the S/UNI-QUAD must be tied to their inactive state. If the inputs are left floating, noise can coupled into the CMOS gates and cause the S/UNI-QUAD device to malfunction. For tying an used input to 3.3V/5V, a 4.7K Ohm pull-up resistor can be used to prevent latchup during power up.

If one of the four channels is not being used, the analog differential inputs, RxD+/-, should be also be tied to ground to avoid chattering the receiver. For any unused channel, power still needs to be supplied to the analog power pins due to S/UNI-QUAD internal power structure.

# 7.4 JTAG PORT

When the JTAG is unused for boundary scan, the TRSTB on the S/UNI-QUAD should be tied to RSTB. This will reset the JTAG port as the same time as system reset. TMS, TCK, and TDI should all be tied high. In addition, TCK can be optionally tied to a free-running clock to ensure that the JTAG port logic is continuously put back to the correct initial state.

## 7.5 ROUTING

Routing is based on the design considerations as well as manufacturability. Several suggestions are listed below:

- Allow at least 10 mil clearance between vias, traces, and pads to prevent shorts and reduce crosstalk. If possible, allow 20 mil or more clearance around vias as manufacturers may have minimum clearance requirements.

- The differential signal pairs should be of equal length so that both signals arrive at the inputs at the same time. They should also run parallel and close to one another for as long as possible so that noise will couple onto both lines and become common mode noise which is ignored by the differential inputs.

- All power and ground traces should be made as wide as possible to provide low impedance paths for the supply current as well as to allow quick noise dissipation.

REFERENCE DESIGN PMC-198-0322

ISSUE 3

PM5351 S/UNI-TETRA

S/UNI-TETRA REFERENCE DESIGN

• Since vias have an impedance, avoid them where possible, especially on critical traces such as TXD± and RXD±. Also where decoupling is critical, try to place capacitors at the pins (component side) and not have vias in series with the capacitors.

REFERENCE DESIGN PMC-198-0322

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

## 8 IMPLEMENTATION DESCRIPTION

The S/UNI-TETRA and S/UNI-QUAD reference designs share the same schematics as the S/UNI-TETRA/QUAD schematics mnemonic. The S/UNI-QUAD and S/UNI-TETRA devices are pin compatible and both provide SONET ATM functionality. The WANS block and Packet Over Sonet functionality on the S/UNI-TETRA/QUAD reference design schematics are implemented for the S/UNI-TETRA device. In this document, the S/UNI-TETRA schematics refer to the schematics titled "S/UNI-TETRA/QUAD reference design".

The S/UNI-TETRA reference design schematics were captured using Cadence software, Concept Schematics Capture Tool.

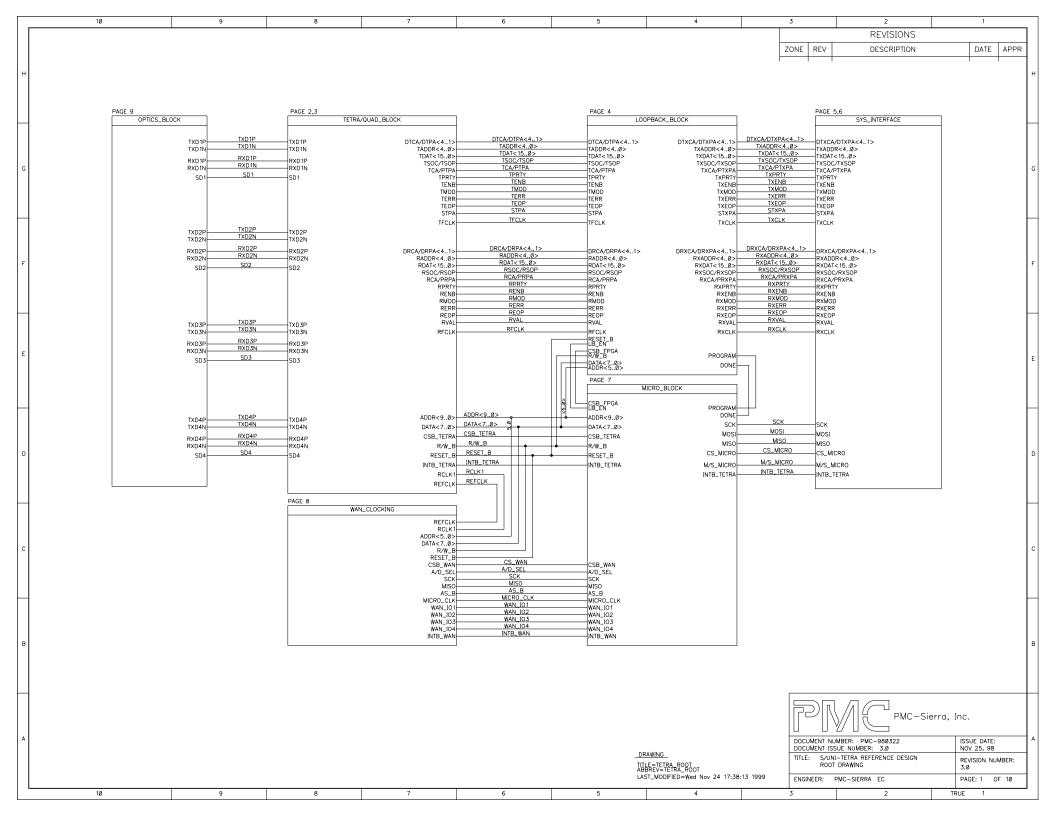

## 8.1 ROOT DRAWING, Sheet 1

This sheet provides an overview of the major functional blocks of the S/UNI-TETRA reference design. It shows interconnections between the TETRA\_BLOCK, LOOPBACK\_BLOCK, SYS\_INTEFACE, MICRO\_BLOCK, WAN\_CLOCKING, OPTICS\_1, OPTICS\_2, OPTICS\_3, and OPTICS\_4 blocks.

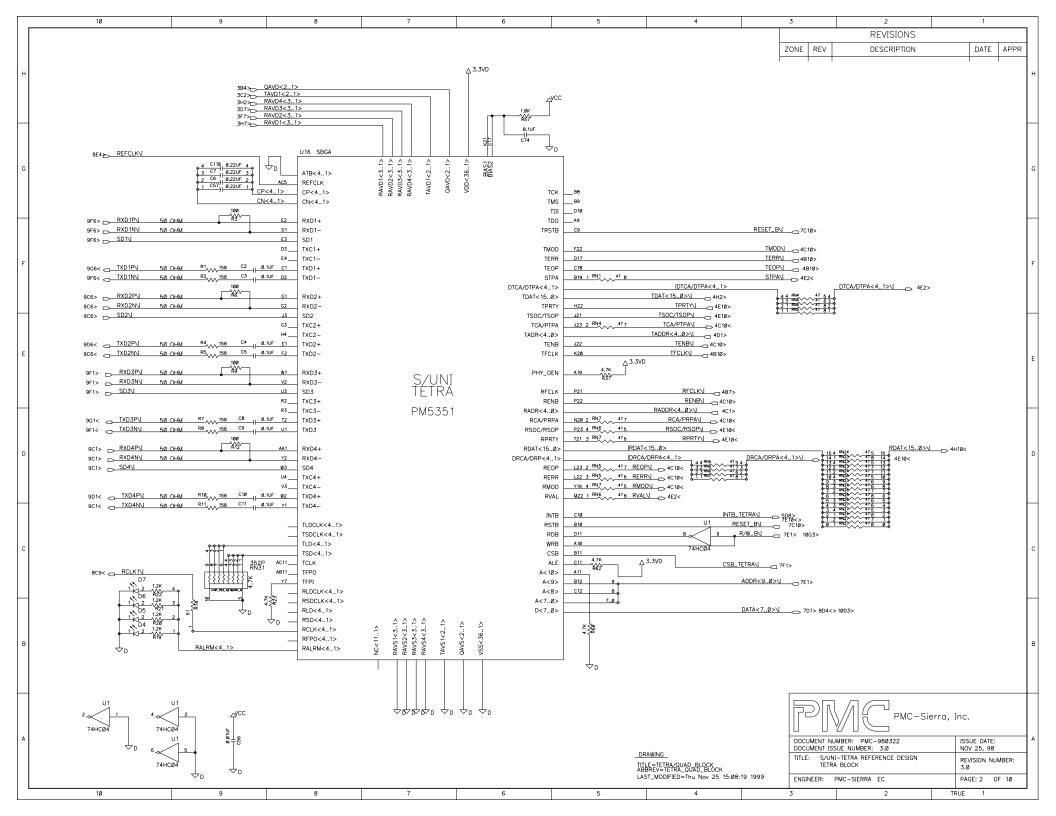

## 8.2 TETRA\_BLOCK, Sheet 2 & 3

The TETRA\_BLOCK shows the S/UNI-TETRA's signals and the power circuitry. Series resistors are used to source terminate the Utopia/POS-PHY bus lines. The 51 Ohms source termination resistor together with the output impedance of the Utopia/POS-PHY bus pads matches the impedance of the trace at 75 Ohms. A 75 Ohm series end termination resistor is provided to reduce initial overshoot and undershoot due to parasitic capacitance of the input pins.

220 nF capacitors are used for the loop filter pins, CP and CN. Four LEDs are provided to display alarm status from each of the four channels in the S/UNI-TETRA. A 1K Ohm resistor is placed in series with Vbias power rail to limit the Vbias current to prevent Vbias latchup.

The digital and analog ground pins are connected to a single ground plane. Layout of the PCB must ensure that noise from the digital circuitry does not get coupled into the analog pins.

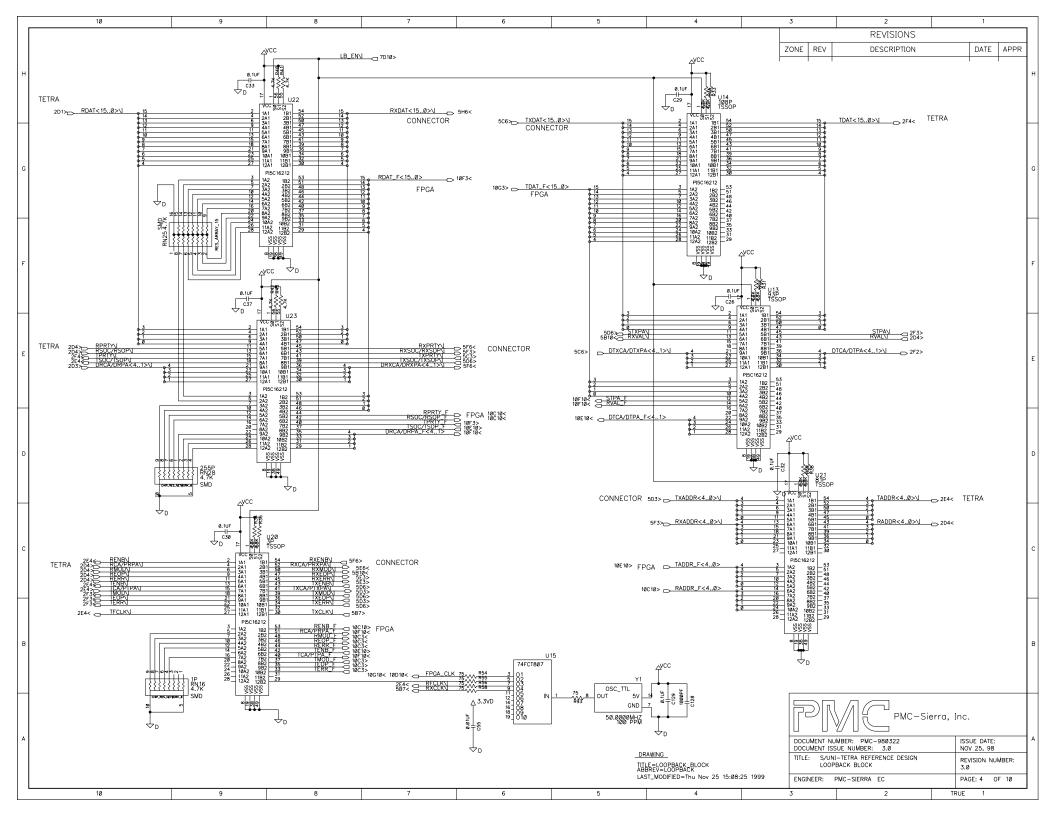

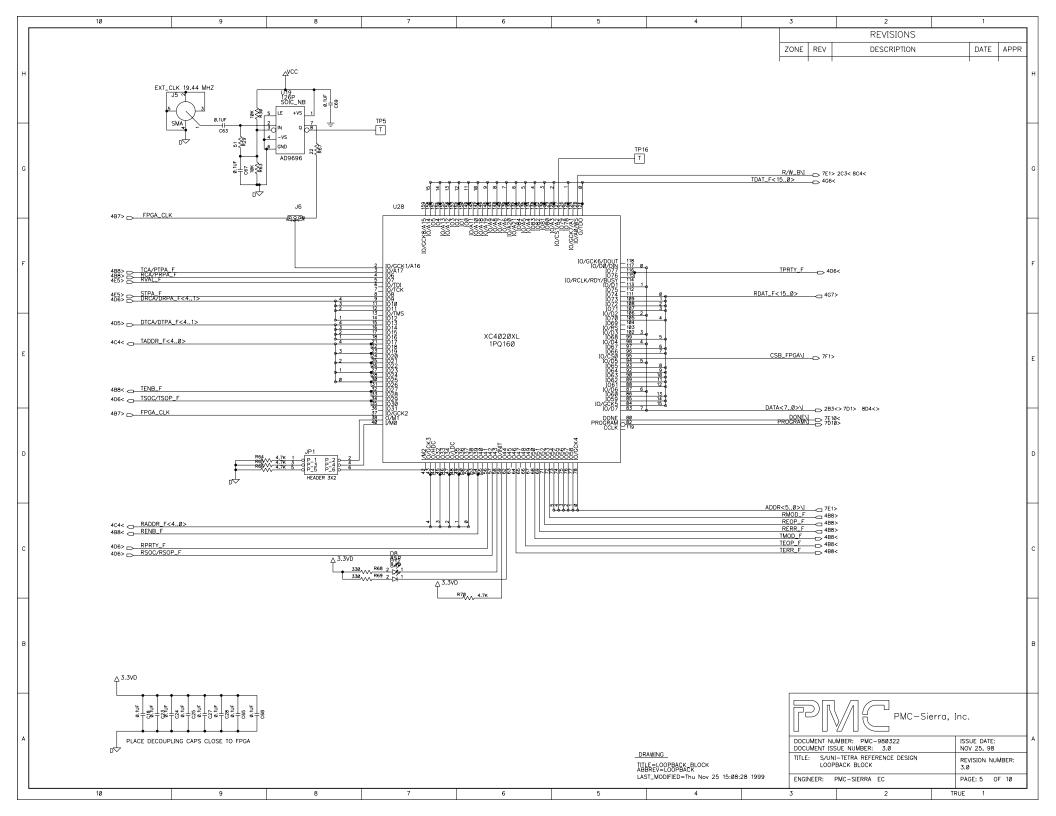

## 8.3 LOOPBACK\_BLOCK, Sheet 4 & 5

This sheet shows the loopback function implemented for the TETRA's Utopia/POS-PHY Level2 interface signals. P15C16212 bus exchange switches are connected to Utopia/POS-PHY signals from and to both the S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

and the loopback FPGA. These bus switches are controlled by the LB\_EN signal. When in loopback, the signals driving the board connector are tied low by the resistor arrays connected through the bus switches.

The 74FCT3807 3.3V clock driver supplies receive clocks to both the S/UNI-TETRA and the board connector for the ATM/POS layer devices. The transmit clock is supplied from the board connector during regular mode. When in loopback mode, both the transmit and receive clocks are supplied by the 74FCT3807 clock driver. The FPGA operates in mixed 5/3.3V mode. The FPGA output level is at 3.3V due to Utopia/POS-PHY signals 3.3V requirement.

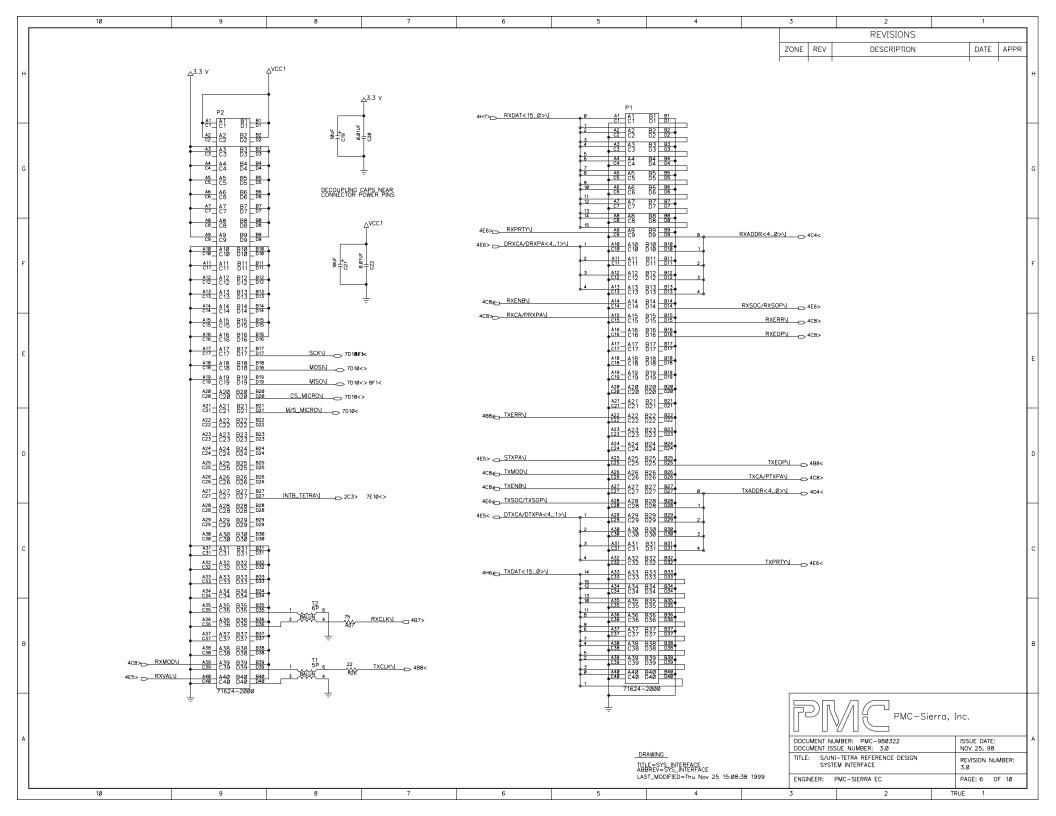

# 8.4 SYS\_INTERFACE, Sheet 6 & 7

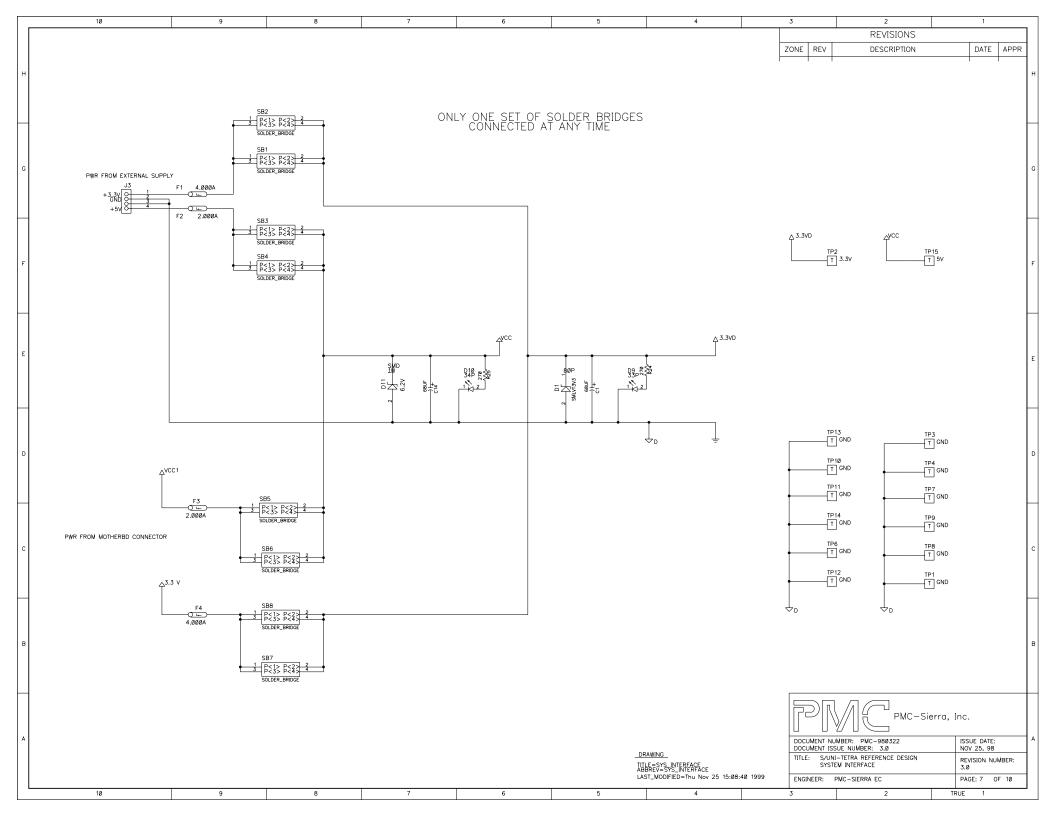

The SYS\_INTERFACE block contains the board connectors and the power supply circuitry. On Sheet 5, two MOLEX 160 pins connectors are shown. Balun transformers are used to transform differential transmit and receive clock signals to single-ended signal for the S/UNI-TETRA.

Sheet 6 shows power to the reference board may be supplied either from an external power supply or through the board connectors. Solder bridges are used to select the desired power source. Fuses and transils are provided to protect the board from over-voltage and over-current.

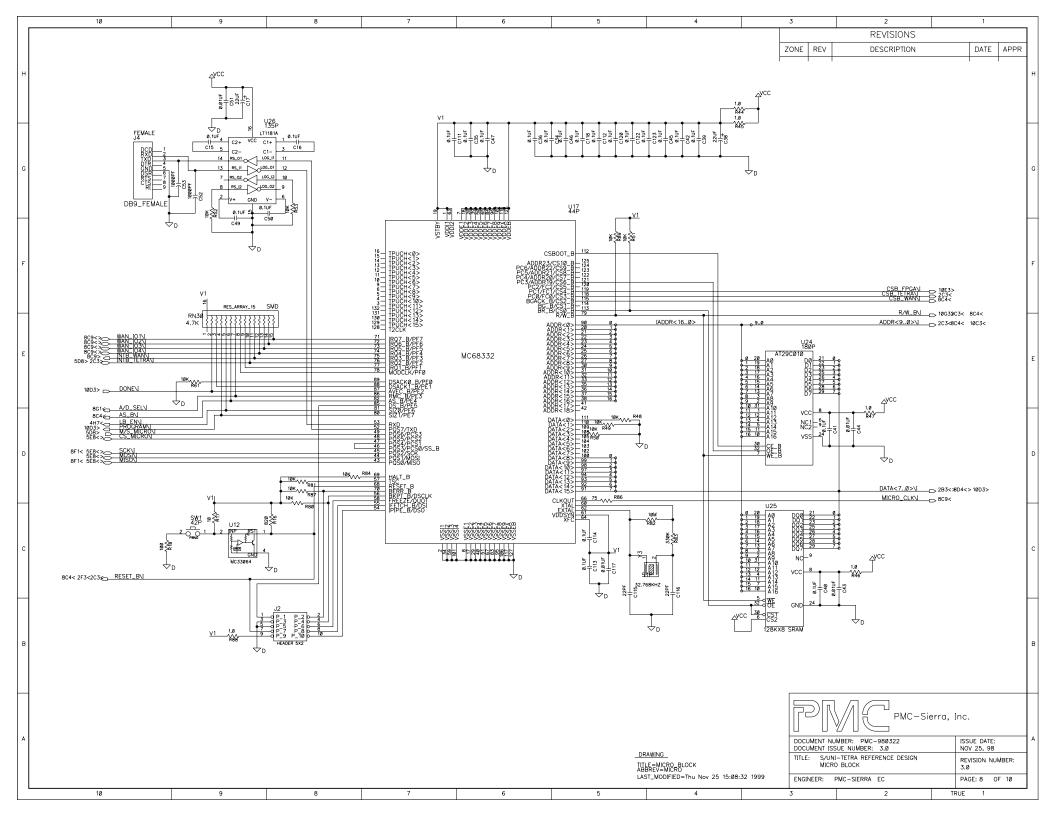

## 8.5 MICRO\_BLOCK, Sheet 8

The MICRO\_BLOCK sheet shows the 68322 microcontroller and its external circuitry. The 68322 operates at 16.337 MHz using a 37.7KHz crystal. 1 MB (128K x 8) Flash and SRAM are provided for program storage and run-time execution. The BDM header allows the microcontroller to be ran in background debug mode for downloading the program to the FLASH and debugging purposes. The MC33064 low voltage sensing circuit put the 68322 in reset mode when the voltage supply drops below 4.5V. Three LEDs are provided for displaying board status.

#### 8.6 WAN\_CLOCKING, Sheet 9

This sheet shows the WAN clocking circuitry used to implement a local clock reference compliant to SONET Stratum 3 clock specifications. A precise power supply regulation circuitry is used for supplying power to the temperature sensor, DAC, Op-Amp, and the VCXO. The power supply regulation circuitry consists of a LMC7660 voltage doubler, and a LT1129-5 low drop voltage regulator. This ensures the power to the clocking circuitry component will have a clean and stable 5V supply.

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

The temperature sensor is connected to a 10-bit ADC that outputs the digitized data to the microcontroller through the SPI port. The DAC is used to supply control voltage to the VCXO. The VCXO operates nominally at 19.44 MHz. The Op-Amp is used to map 0V to 2.04V output voltage range of the DAC to the VCXO. The DAC inputs come from the FPGA.

The FPGA implements the digital filtering and the PLL algorithm for providing clocking to the board. It is controlled by the microcontroller through the data and address bus.

#### 8.7 OPTICS\_BLOCK, Sheet 10

This sheet shows the four Optical Data Link (ODL) that provides the optical to electrical (O/E) function for the S/UNI-TETRA device. The PECL signal runs on 50 Ohm controlled impedance signal lines and are properly terminated at the ODL and at the S/UNI-TETRA device.

The S/UNI-TETRA device interfaces to four HP HFCT-5905 Singlemode Fiber Transceivers. The HFCT-5905 transceivers are in a 2x5 DIP package with a mini MT-RJ connector interface. The smaller footprint MT-RJ interface allows higher optical port density on a typical ATM or POS line card.

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

#### 9 WAN CLOCKING PLL ALGORITHMS

This section provides an implementation suggestion for the PLL algorithm controlling the WAN clocking circuitry described in the functional description section.

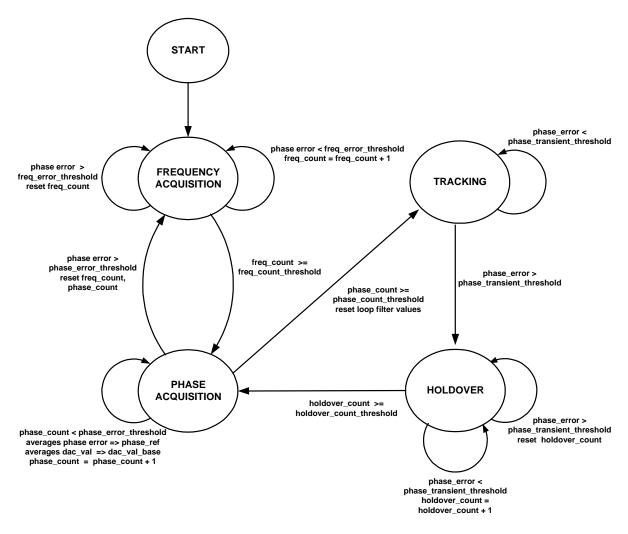

Figure 10 shows the state diagram for the WAN clocking PLL algorithm. The algorithm can either be implemented in software using a microprocessor or hardware using a FPGA.

#### Figure 10 : PLL Algorithm State Diagram

REFERENCE DESIGN PMC-198-0322

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

The PLL algorithm operates within four states: Frequency acquisition, Phase acquisition, Tracking and Holdover. After initialization, the PLL algorithm enters the Frequency Acquisition State. In both the Frequency and Phase Acquisition States, the PLL adjusts the VCXO output clock to lock to the reference clock. In Frequency Acquisition State, the algorithm pulls the VCXO frequency close in with the reference clock frequency. In Phase Acquisition State, the VCXO provides a finer adjustments to the VCXO output to lock to the reference clock. Once the VCXO has locked to the reference clock, the PLL enters the Tracking state. During the Tracking state, the PLL implements a digital loop filter to maintain tracking to the reference clock. The PLL also checks to see if the reference clock is maintaining its stability. If the phase difference exceeds a preset threshold, the PLL switches to the Holdover state. The PLL can also enters the HOLDOVER states based on detected alarms (BIP-8, AIS, LOS, LOF, OOF, or SSM) or an external request. In Holdover state, the PLL keeps the VCXO output at the last locked value from the Tracking state. In the Holdover state, the PLL continues to examine the reference clock to see if it has recovered. If a good stable reference clock exists, the PLL switches back to the Phase Acquisition state. The details of each states as applicable for the TETRA WAN clocking circuity is described as below.

#### 9.1 Frequency Acquisition

The TETRA WANS blocks implements a digital phase comparator between all four channel's recovered clocks and the REFCLK supplied by the VCXO. The results are stored in registers as a 31-bit Phase Word.

During initialization, variables are set for the operation of the PLL algorithm. To minimize the time required for the output to lock to the reference clock, a base value for the DAC, DAC\_VAL\_BASE, can be set to the middle of the VCXO's frequency tuning range. In Frequency Acquisition, the loop bandwidth is much wider for it to pull in the output frequency close to the reference frequency. The PLL calculates the difference between the current Phase Word and the previous Phase Word obtained from the S/UNI-TETRA WANS block and stores it as PHASE\_ERROR.

Current value of the Phase Word is accumulated and averaged by the WANS block over the period specified in the WANS registers. The PHASE\_ERROR is updated every 125 usec. If current Phase Word is larger than the previous one, this means that the VCXO output frequency is too high. To reduce the VCXO output frequency has to be reduced by decreasing control voltage to the DAC. The output of the DAC is buffered through the inverting Op-amp, serving as a voltage level shifter as well. If the current Phase Word is smaller than the previous one, this implies that the VCXO output frequency is too low. The VCXO frequency can be adjusted by increasing the control voltage to the VCXO.

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

The loop operation implemented in the Frequency Acquisition State performs frequency lock, not a phase lock because it uses phase-detector hardware as a frequency discriminator. The loop is sensitive to large frequency offsets between the VCXO and reference frequencies. For small frequency offsets, the loop is not very sensitive. When the frequency offset is smaller than the predefined threshold (FREQ\_ERROR\_THRESHOLD) for a predefined number of times (FREQ\_COUNT\_THRESHOLD), the PLL switches to the phase acquisition state.

#### 9.2 Phase Acquisition

In Phase Acquisition State, the PLL acquires two parameters for the Tracking State. The two parameters are DAC\_VAL\_BASE and PHASE\_REFERENCE.

DAC\_VAL\_BASE is obtained by averaging the DAC\_VAL sent to the DAC while the PLL in the Phase Acquisition State. PHASE\_REFERNECE is the average value of the Phase Word during phase acquistion. Samples of the values are taken at the same rate as in the frequency acquisiton at 125us. The number of values to be averaged is shown as PHASE\_COUNT\_THRESHOLD. A larger number of samples improves the averaged value but requires a longer time to determine.

During Phase Acquisition, if the absolute value of the PHASE\_ERROR exceeds PHASE\_ERROR\_THRESHOLD, the PLL switches back to Frequency Acquisition State. The PHASE\_COUNT is reset when this occurs. The PLL enteres Tracking State when the PHASE\_COUNT reaches PHASE\_COUNT\_THRESHOLD.

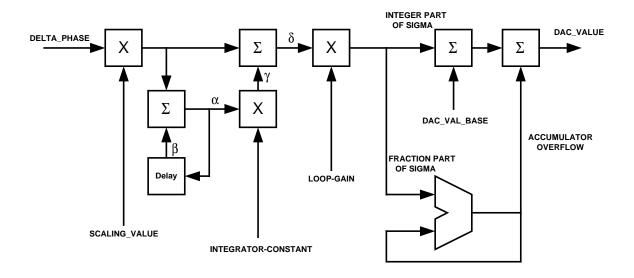

#### 9.3 Tracking

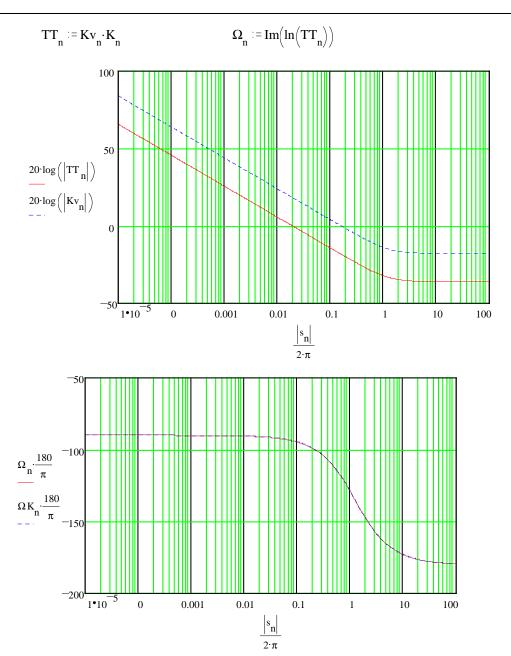

The PLL performs phase locking and reference filtering in tracking state using a digital loop filter. The block digram for the digital loop filter is shown in figure 11.

In the tracking state, the PLL calculates the difference between the PHASE\_REFERENCE derived in the Phase Acquisition State and new PHASE WORD from the TETRA's WANS block and stores as DELTA\_PHASE. The loop filter is implemented as a lead-lag filter structure. The filter consists of a perfect integrator added with the scaled direct path value. The input to the loop filter, DELTA\_PHASE, is scaled by the preassigned SCALING\_VALUE. The ratio of the perfect accumulator path and the direct path transfer function determine the position of the transmission zero. The positional change of this transmission zero can be achieved by setting different values for the Integrator\_Constant parameter.

S/UNI-TETRA REFERENCE DESIGN

In the lead-lag part of the filter, the value of DELTA\_PHASE is added to a previous sum  $\beta$  and the total is stored in  $\alpha$ . The value  $\alpha$  is then used for the next iteration of a new  $\alpha$  calculation. The integrator output,  $\alpha$ , is muliplied with the INTEGRATOR\_CONST by right shifting the  $\alpha$  value by the amount specified in INTEGRATOR\_CONST to obtain  $\gamma$ . To simply the multiplication, the INTEGRATOR\_CONST is approximated by an integer value, Ki. The deriviation of Ki is shown in appendix A. Since right shifting will remove information from the  $\alpha$  output, the DELTA\_PHASE value is amplified at the input by left shifting it by the amount specified in SCALED\_VALUE. All the digital values are stored as 32 bit values.

Next, the value of  $\gamma$  is added to the scaled value of DELTA\_PHASE in order to compensate the open-loop phase. One inherent problem with this implementation is that there are two perfect integrators presented in this PLL, one in the VCXO and the other resulting from the summing of  $\beta$  and DELTA\_PHASE. This can make the PLL unstable at various frequencies. To make the loop more stable, the effect of the second integrator formed by the sum of  $\beta$  and DELTA\_PHASE must be minimized. This is accomplished by dividing  $\alpha$  (right shifting) by INTEGRATOR\_CONST and adding it to the DELTA\_PHASE, making the effect of the second integrator only evident at very, very low frequencies. These frequencies are defined by the time required for  $\alpha$  to accumulate to a value in the same magnitude as DELTA\_PHASE. The sampling time and value of INTEGRATOR\_CONST further define the range of frequencies over which two perfect integrators exist in the loop. Above these frequencies the

REFERENCE DESIGN PMC-198-0322

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

loop contains only one perfect integrator as a result fo the VCXO. The sum of the scaled value of DELTA\_PHASE and  $\gamma$  produce the value  $\delta$ , which is further adjusted to result in a specific open-loop gain crossing of the 0 dB value.

The loop gain can be adjusted by setting values for LOOP\_GAIN. The loop gain allows fine tuning and adjusting of the close loop transfer function. The VCXO sensitivity is the only analog value in this PLL calculation. Therefore, it allows us to accurately predict the behavior of the PLL behavior for a wide range of termperature, independent of the spread of individual VCXO sensitivity. Different batches of oscillators were tested over a wide temperature range, and it was noticed that a frequency sensitivity ( $\Delta$ frequency/ $\Delta$ control-voltage) is limited to +/-10%. A +/-20% margin is used in the calculation to provide a safety margin. The DAC temperature sensitivity is also included in this calculation. For information about PLL calculation, please refer to Appendix A.

The loop gain is adjusted by left shifting the  $\delta$  value by the amount of specified in LOOP\_GAIN. The idea is to create a 32 bit value word that when split into two 16 bits words, it can be used for controlloing the VCXO output. The higher word of the 32 bit long word is added with DAC\_VAL\_BASE as the DAC\_VALUE for controlling the VCXO. PHASE\_REF and DAC\_VAL\_BASE defined the initial condition for the behaviour of the PLL in the Tracking State. The PLL stays locked to this defined condition when in tracking.

The lower word of the 32 bit long word is passed to the Numeric Control Oscillator (NCO) routine. The lower word is masked since only the 5 most significant bits are used. The NCO routine asserts accumulator overflow bit when the accumulator overflows. The accumulator overflow bit is added to the DAC\_VALUE sent to the DAC. The overflow value is used for dithering the DAC\_VALUE. This process improves the accuracy of a 12 bit DAC. The output of the DAC is then filtered through a low-pass filter to obtain an optimum averaged value. The dithering allows the 12-bit DAC to improve the accuracy to the accuracy of a 17-bit DAC.

#### 9.4 Holdover

The holdover mode is entered when excessive phase variations are detected, faults being declared, or a external request. When entering the Holdover State, the DAC\_VAL\_BASE will be added to the last upper word from the direct path and store as the new DAC\_VAL\_BASE. This value will stay as the DAC control voltage in the Holdover State. To ensure that the phase transients generated by switching to holdover does not exceed the maximum defined in the Bellcore GR-253-CORE specification, the actual phase transients are limited by the algorithm. The MTIE specification for the phase transient when entering holdover is:

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

### Table 3 : Phase Transient MTIE specification

| Observation time S                                  | MTIE (nanoseconds) |

|-----------------------------------------------------|--------------------|

| (in seconds)                                        |                    |

| S<0.014                                             | N/A                |

| 0.014 <s<0.5< td=""><td>7.6+(885 x S)</td></s<0.5<> | 7.6+(885 x S)      |

| 0.5 <s< 2.33<="" td=""><td>300+(300 x S)</td></s<>  | 300+(300 x S)      |

| 2.33 < S < 64                                       | 884+(50 x S)       |

| S > 64                                              | N/A                |

In addition, there is a requirement that the initial frequency offset be less than 0.05 ppm, measured during the first minute after the 64th second.

The frequency drift rate shall be less than  $5.8 \times 10^{-6}$  ppm/sec. It is defined as the fractional frequency difference over the time period. The fractional frequency offset under varying temperature conditions shall be less than 4.1 ppm.

MTIE linearly increasing with observation time indicates the maximum frequency difference between an ideal clock and the observed clock.

To evaluate what relative frequency offset produces a specific MTIE value for a given observation time, we can use the following equations

$$\int_{0}^{S} \Delta freq \bullet dt = \Delta \Phi$$

$$\frac{1}{f_{0}} \bullet \int_{0}^{S} \Delta freq \bullet dt = \frac{\Delta \Phi}{f_{0}}$$

$$\Delta Freq \bullet S \bullet 10^{-6} \bullet 10^{9} = MTIE$$

In this expression, the observation time, S, is in units of seconds; MTIE is in nanoseconds; and relative frequency offset is in ppm.

Using this formula, we can calculate that to meet the GR-253-CORE requirement, the fractional frequency offset (in ppm) must be: less than 0.900 ppm for an observation time between 0.014 seconds and 0.5 seconds; less than 0.429 ppm for an observation time between 0.5 seconds and 2.33 seconds; and less than 0.064 ppm for an observation time between 2.33 seconds and 64 seconds.

The WAN synchronization PLL can change the DAC value once every 125 ms. Any phase or frequency change of the input reference clock is accumulated by the algorithm during this time and does not cause any change in the VCXO. For the current implementation with a VCXO sensitivity of approximately:

REFERENCE DESIGN PMC-198-0322

PM5351 S/UNI-TETRA

S/UNI-TETRA REFERENCE DESIGN

```

K_{vcxo} = \frac{8000}{3.2} Hz/V

```

and using a 12-bit DAC with DAC sensitivity of:

$K_{DAC} = \frac{3.2}{4096} V/quant$

Therefore, a single quantization step change in the DAC will create a frequency offset of approximately 2 Hz, or equivalently 0.038 ppm. If the software restricts the changes in the DAC value to a one DAC-step maximum, then even in the case of a reference clock failure and a total failure in all other methods to detect this signal fault, the VCXO will not move faster than 0.050 ppm. This is well below the limit of the GR-253-CORE specification.

Once in the holdover mode, the circuit monitors ambient temperature changes. The LM50 temperture sensor sensitivity is 10 mV/°C. The VCXO change with temperature is lower than +/-0.3 ppm/°C, so storing compensation values for the DAC in increments of 0.5°C is sufficient. The program monitors the change in temperature and calculates the correction to be added to DAC\_VAL.

Finally, while in holdover, if an eligible reference source is detected, the algorithm will start the acquisition to that new source by entering the Phase Acquisition State. This process consists of the determining the new PHASE\_REFERENCE value, and flushing out all accumulated values during the previous lock. Only the current DAC\_VAL\_BASE is kept. This method is also very useful in reducing the phase buildout during phase transients. If a phase transient is captured, then the unit will enter holdover, stay in holdover for 2 seconds and then recapture the new phase. This eliminates tracking sudden phase jumps.

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

# 10 SCHEMATICS

#### 10.1 Bill of Materials

### Table 4 : Major Components List

| Ref. No   | Component Description                | Package<br>Type | Quantity |

|-----------|--------------------------------------|-----------------|----------|

| U16       | PMC-Sierra, Inc.                     | SBGA304         | 1        |

|           | PM5351 S/UNI-TETRA                   |                 |          |

| U2-U5     | Hewlett Packard Co.                  | 2x5 DIP         | 4        |

|           | HFCT-5905                            | Style           |          |

| U7        | National Semiconductor               | SOT23           | 1        |

|           | LM50                                 |                 |          |

| U8        | Linear Technology                    | SOIC8           | 1        |

|           | LTC1257                              |                 |          |

| U9        | National Semiconductor               | SOIC8           | 1        |

|           | LMC6482                              |                 |          |

| U11       | National Semiconductor LMC7660       | SOIC8           | 1        |

|           | Switched Capacitor Voltage Converter |                 |          |

| U12       | Motorola                             | SOIC8           | 1        |

|           | MC33064                              |                 |          |

| U13, U14, | Pericom                              | TSSOP 54        | 6        |

| U20-U23   | PI5C16212                            |                 |          |

| U15       | Pericom                              | SOIC20          | 1        |

|           | 74FCT807                             |                 |          |

| U17       | Motorola                             | PQFP 100        | 1        |

|           | MC68332                              |                 |          |

| U18       | Actel                                | PLCC84          | 1        |

|           | 42MX-09-PL84                         |                 |          |

| U28       | Xilinx 4020XL                        | PQ160           | 1        |

PMC-Sierra, Inc.

PM5351 S/UNI-TETRA

REFERENCE DESIGN PMC-198-0322

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

| Ref. No | Component Description               | Package<br>Type | Quantity |

|---------|-------------------------------------|-----------------|----------|

| U24     | Atmel                               | TSOP 32         | 1        |

|         | AT29C010A                           |                 |          |

| U25     | Cypress                             | TSOP 32         | 1        |

|         | CY62128                             |                 |          |

| U26     | Linear Technology                   | SOIC16          | 1        |

|         | LT1181A                             |                 |          |

| U27     | Linear Technology                   | SOT223          | 1        |

|         | LT1121CST-3.3                       |                 |          |

| Y1      | MMD                                 | 4 Pins          | 1        |

|         | 50.00 MHz 100 ppm                   |                 |          |

| Y2      | For VXCO                            | 4 pin           | 1        |

|         | Raltron                             |                 |          |

|         | VC7220A-LZ-30-19.440-PMC            |                 |          |

|         | For Crystal Oscillator              |                 |          |

|         | MMD                                 |                 |          |

|         | 19.44 MHz Crystal Oscillator 50 ppm |                 |          |

| D1      | SGS-Thomson                         | SMB             | 1        |

|         | SMLVT3V3                            |                 |          |

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

#### 11 REFERENCES

- PMC-Sierra, Inc., PM5351 S/UNI-TETRA Data Sheet, Issue 2, March 1998

- Bell Communication Research SONET Transport Systems: Common Generic Criteria, GR-253-CORE, Issue 2, December 1995

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

## 12 APPENDIX A

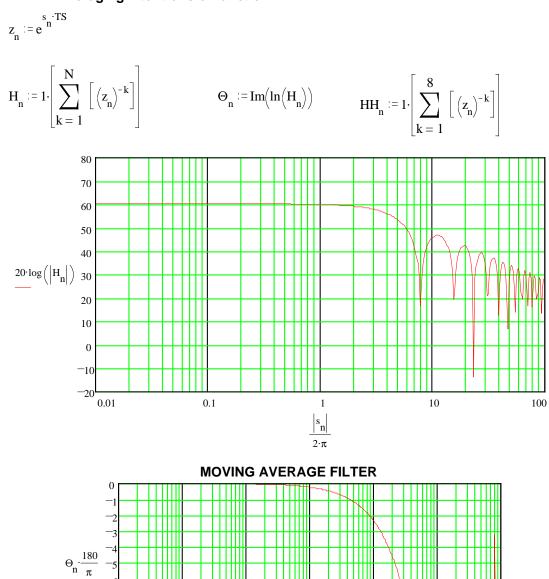

# SWAN PLL Calculation

| n =1,2700                                                                                                                  | index for frequ      | iency                  |                                                  |

|----------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------|--------------------------------------------------|

| $v_n := 10^{\frac{n-301}{100}}$                                                                                            |                      |                        |                                                  |

| $fs := 8 \cdot 10^3$                                                                                                       | $TS := \frac{1}{fs}$ | Sampl                  | ing interval                                     |

| N = 512·2                                                                                                                  | Averaging            | $N = 1.024 \cdot 10^3$ | samples                                          |

| $T := N \cdot TS$ T                                                                                                        | = 0.128              |                        |                                                  |

| $s_n := i \cdot 2 \cdot \pi \cdot 0.01 \cdot v_n$                                                                          | Complex              | frequency              |                                                  |

| $z_{n} := \frac{1}{1 - s_{n} \cdot T}$ $Kpd := \frac{405}{2 \cdot \pi}$ $Kvco := \frac{2 \cdot \pi \cdot 8000}{3 \cdot 2}$ | 51.84MH<br>3.24MHz   |                        |                                                  |

| CO := 6480                                                                                                                 | Division             | factor in PLL          | $\frac{51.8410^6}{8\cdot 10^3} = 6.48\cdot 10^3$ |

| Kdac := $\frac{3.2}{2^{12}}$                                                                                               | DAC set              | nsitivity in vol       | ts/step                                          |

$K_{n} := Kpd \cdot Kvco \cdot Kdac \cdot \frac{1}{CO}$  $Kv_{n} := \frac{T}{z_{n} - 1}$  $\Omega K_{n} := Im(ln(Kv_{n}))$

REFERENCE DESIGN PMC-198-0322

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

REFERENCE DESIGN PMC-198-0322 PMC-Sierra, Inc.

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

0

0.001

0.01

$\begin{vmatrix} s_n \end{vmatrix}$ 2· $\pi$  0.1

10

1

1•10

| PRELIMINARY |

|-------------|

|-------------|

PM5351 S/UNI-TETRA

S/UNI-TETRA REFERENCE DESIGN

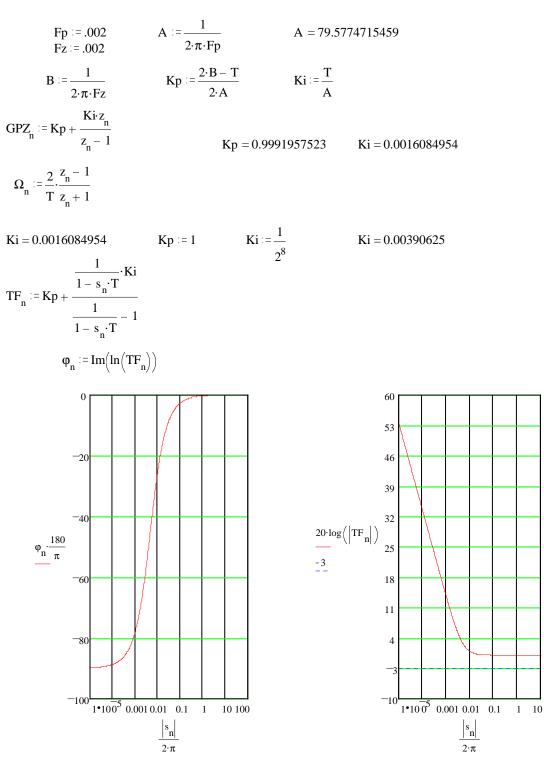

#### Lead-lag porton of the loop

**ISSUE 3**

G1 := 1

REFERENCE DESIGN PMC-198-0322

ISSUE 3

PM5351 S/UNI-TETRA

S/UNI-TETRA REFERENCE DESIGN

REFERENCE DESIGN PMC-198-0322

PM5351 S/UNI-TETRA

ISSUE 3

S/UNI-TETRA REFERENCE DESIGN

#### **CONTACTING PMC-SIERRA, INC.**

PMC-Sierra, Inc. 105-8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000

Fax: (604) 415-6200

Document Information: Corporate Information: Application Information: document@pmc-sierra.com info@pmc-sierra.com apps@pmc-sierra.com (604) 415-4533 http://www.pmc-sierra.com

Web Site: