ISSUE 3

FREEDM-32P672 REVISION C DEVICE ERRATA

# PM7380 FREEDM-32P672

# **REVISION C DEVICE ERRATA**

**Issue 3**

December 2001

PMC-2000951

ISSUE 3

FREEDM-32P672 REVISION C DEVICE ERRATA

# **TABLE OF CONTENTS**

| 1.  | Introd                                                      | uction1                                                                |  |  |  |

|-----|-------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|

|     | 1.1.                                                        | Device Identification1                                                 |  |  |  |

|     | 1.2.                                                        | Reference1                                                             |  |  |  |

| 2.  | FREEDM-32P672 Revision C Functional Deficiency List2        |                                                                        |  |  |  |

|     | 2.1.                                                        | FREEDM may not generate PCI disconnect if host attempts a read         |  |  |  |

|     | multiple command which reads beyond register address 0xFFF3 |                                                                        |  |  |  |

|     | 2.2.                                                        | FREEDM may under-report number of Transmit FIFO underrun events if     |  |  |  |

|     | two su                                                      | uch events occur close together4                                       |  |  |  |

| 3.  | Documentation Errors                                        |                                                                        |  |  |  |

|     | 3.1.                                                        | PROV and DELIN bits in Register 0x204 are Write-Only6                  |  |  |  |

|     | 3.2.                                                        | 7BIT, INVERT, CRC[1], and CRC[0] bits in Register 0x208 are Write-Only |  |  |  |

|     |                                                             | 7                                                                      |  |  |  |

| Con | tacting                                                     | PMC-Sierra                                                             |  |  |  |

ISSUE 3

FREEDM-32P672 REVISION C DEVICE ERRATA

### 1. Introduction

In this document, Section 2 lists the known functional errata for revision C of PM7380 FREEDM-32P672 and Section 3 lists errors found in Issue 5 of the FREEDM-32P672 datasheet (PMC-1990262).

## 1.1. <u>Device Identification</u>

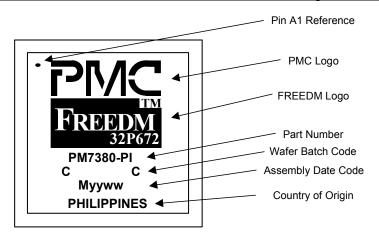

The information contained in Section 2 relates to <u>Revision C</u> of PM7380 FREEDM-32P672 only. The device revision code is marked at the end of the Wafer Batch Code on the face of the device (as shown in Figure 1.1). PM7380 FREEDM-32P672 Revision C is packaged in a 329-pin Plastic Ball Grid Array (PBGA).

### Figure 1.1: PM7380 FREEDM-32P672 Branding Format.

Not to Scale

# 1.2. <u>Reference</u>

• PMC-1990262, FREEDM-32P672 Long Form Data Sheet, Issue 5.

ISSUE 3

FREEDM-32P672 REVISION C DEVICE ERRATA

### 2. FREEDM-32P672 Revision C Functional Deficiency List

This section lists the known functional deficiencies for Revision C of FREEDM-32P672 (as of the publication date of this document). For each deficiency, the known work-around and the operating constraints, with and without the work-around, are also described.

Please report any functional deficiencies not covered in this document to PMC-Sierra.

### 2.1. FREEDM may not generate PCI disconnect if host attempts a read multiple command which reads beyond register address 0xFFF.

### **Description:**

If a host incorrectly attempts a read multiple command whose address range spans beyond a point 4K bytes from the start of the FREEDM-32P672 register space, the FREEDM-32P672 may not issue a PCI disconnect and the PCI bus may hang.

#### Workarounds:

Ensure that the PCI host only accesses valid FREEDM-32P672 register addresses.

### Performance with workaround:

FREEDM-32P672 works correctly.

### Performance without workaround:

PCI bus may hang necessitating a system reset.

# 2.2. FREEDM may under-report number of Transmit FIFO underrun events if two such events occur close together.

### **Description:**

The FREEDM-32P672 reports underrun events on a per-channel basis to the host by setting bit STATUS[2] when a TDR is returned to the TDR Free Queue. If a packet underflows near the end of the packet and the next packet on the same channel underflows near the start of the packet, it is possible that only one TDR is returned to the TDR Free Queue with STATUS[2] set even though 2 underrun events occurred.

#### Workarounds:

None.

### Performance without workaround:

Per channel underrun events can occasionally go unreported.

ISSUE 3

FREEDM-32P672 REVISION C DEVICE ERRATA

### 3. <u>Documentation Errors</u>

This section lists the known documentation errors in Issue 5 of PMC-1990262 FREEDM-32P672 Datasheet (as of the publication date of this document).

Please report any documentation errors not covered in this document to PMC-Sierra.

ISSUE 3

FREEDM-32P672 REVISION C DEVICE ERRATA

### 3.1. PROV and DELIN bits in Register 0x204 are Write-Only

PROV and DELIN bits in Register 0x204 are write-only and not read/write. Changes to the register table are shown below.

| Bit    | Туре                    | Function | Default |

|--------|-------------------------|----------|---------|

| Bit 15 | <del>R/W</del> <b>W</b> | PROV     | 0       |

| Bit 14 | R/W                     | STRIP    | 0       |

| Bit 13 | <del>R/W</del> <b>W</b> | DELIN    | 0       |

| Bit 12 | R                       | TAVAIL   | Х       |

| Bit 11 | W                       | Reserved | Х       |

| Bit 10 | W                       | FPTR[10] | Х       |

| Bit 9  | W                       | FPTR[9]  | Х       |

| Bit 8  | W                       | FPTR[8]  | Х       |

| Bit 7  | W                       | FPTR[7]  | Х       |

| Bit 6  | W                       | FPTR[6]  | Х       |

| Bit 5  | W                       | FPTR[5]  | Х       |

| Bit 4  | W                       | FPTR[4]  | Х       |

| Bit 3  | W                       | FPTR[3]  | Х       |

| Bit 2  | W                       | FPTR[2]  | Х       |

| Bit 1  | W                       | FPTR[1]  | Х       |

| Bit 0  | W                       | FPTR[0]  | X       |

## Register 0x204 : RHDL Indirect Channel Data Register #1

ISSUE 3

### 3.2. 7BIT, INVERT, CRC[1], and CRC[0] bits in Register 0x208 are Write-Only

7BIT, INVERT, CRC[1], and CRC[0] bits in Register 0x208 are write-only and not read/write. Changes to the register table are shown below.

| Bit    | Туре                    | Function  | Default |

|--------|-------------------------|-----------|---------|

| Bit 15 | <del>R/W</del> <b>W</b> | 7BIT      | 0       |

| Bit 14 | R/W                     | PRIORITY  | 0       |

| Bit 13 | <del>R/W</del> <b>W</b> | INVERT    | 0       |

| Bit 12 |                         | Unused    | Х       |

| Bit 11 | <del>R/W</del> <b>W</b> | CRC[1]    | 0       |

| Bit 10 | <del>R/W</del> <b>W</b> | CRC[0]    | 0       |

| Bit 9  | R/W                     | OFFSET[1] | 0       |

| Bit 8  | R/W                     | OFFSET[0] | 0       |

| Bit 7  |                         | Unused    | Х       |

| Bit 6  |                         | Unused    | Х       |

| Bit 5  |                         | Unused    | Х       |

| Bit 4  |                         | Unused    | Х       |

| Bit 3  | R/W                     | XFER[3]   | 0       |

| Bit 2  | R/W                     | XFER[2]   | 0       |

| Bit 1  | R/W                     | XFER[1]   | 0       |

| Bit 0  | R/W                     | XFER[0]   | 0       |

## Register 0x208 : RHDL Indirect Channel Data Register #2

ISSUE 3

FREEDM-32P672 REVISION C DEVICE ERRATA

### **Contacting PMC-Sierra**

PMC-Sierra, Inc. 105 - 8555 Baxter Place Burnaby, BC V5A 4V7 Tel: (604) 415-6000 Fax: (604) 415-6200

Product information: Applications information: Internet: info@pmc-sierra.bc.ca apps@pmc-sierra.bc.ca <u>http://www.pmc-sierra.com</u>

ISSUE 3

FREEDM-32P672 REVISION C DEVICE ERRATA

# **NOTES**

Seller will have no obligation or liability in respect of defects or damage caused by unauthorized use, mis-use, accident, external cause, installation error, or normal wear and tear. There are no warranties, representations or guarantees of any kind, either express or implied by law or custom, regarding the product or its performance, including those regarding quality, merchantability, fitness for purpose, condition, design, title, infringement of third-party rights, or conformance with sample. Seller shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon, the information contained in this document. In no event will Seller be liable to Buyer or to any other party for loss of profits, loss of savings, or punitive, exemplary, incidental, consequential or special damages, even if Seller has knowledge of the possibility of such potential loss or damage and even if caused by Seller's negligence.

© 2001 PMC-Sierra, Inc.

Issue date: December, 2001