ISSUE 1

S/UNI-622-POS REFERENCE DESIGN ERRATA

PM5357

# S/UNI-622-POS

# SATURN USER NETWORK INTERFACE (622-POS)

# **REFERENCE DESIGN ERRATA**

**ISSUE 1: DECEMBER 2000**

ISSUE 1

S/UNI-622-POS REFERENCE DESIGN ERRATA

# **REVISION HISTORY**

| lssue<br>No. | Issue Date        | Details of Change                                                                                                                                                                           |

|--------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | December,<br>2000 | This document contains errata information corresponding to the issue 2 of Reference Design document PMC-1981070. This fixes minor documentation errors, improvements and application hints. |

## **CONTENTS**

| 1 | ISSUE ?                                       | 1 ERRATA                                                                                  |  |  |

|---|-----------------------------------------------|-------------------------------------------------------------------------------------------|--|--|

| 2 | REFERENCE DESIGN DOCUMENTATION DISCREPANCIES: |                                                                                           |  |  |

|   | 2.1                                           | TRACE IMPEDANCE SHOULD BE 500HMS NOT 100 OHMS IN FIGURE 16                                |  |  |

|   | 2.2                                           | CHANGE THE 5V 77.76MHZ OSCILLATOR TO A LOW JITTER TYPE                                    |  |  |

|   | 2.3                                           | C47 CLARIFICATION IN THE BOM                                                              |  |  |

|   | 2.4                                           | VCC TO XC1701L SHOULD BE 3.3 V AND NOT 5V                                                 |  |  |

| 3 | APPLICATION NOTES:                            |                                                                                           |  |  |

|   | 3.1                                           | CAUTION ON USING INDUCTORS TO FILTER POWER SUPPLIES 4                                     |  |  |

|   | 3.2                                           | CONNECTING A TTL SD FROM ODL TO SD PECL TYPE INPUT OF S/UNI-622-POS5                      |  |  |

|   | 3.3                                           | INTERFACING A TTL SINGLE ENDED 77.76MHZ OSCILLATOR INTERFACE TO<br>REFCLK+/- PECL INPUTS6 |  |  |

S/UNI-622-POS REFERENCE DESIGN ERRATA

# LIST OF FIGURES

| FIGURE 1: TRACE IMPEDANCE CORRECTION                   | . 2 |

|--------------------------------------------------------|-----|

| FIGURE 2: INDUCTOR TRANSIENTS MAY DAMAGE CMOS CIRCUITS | . 4 |

| FIGURE 3: INDUCTOR TRANSIENTS CLAMPED BY DIODES        | . 5 |

| FIGURE 4: TTL TO PECL SD INPUT OF S/UNI-622-POS        | . 6 |

| FIGURE 5: TTL TO SINGLE ENDED PECL INTERFACE           | . 6 |

S/UNI-622-POS REFERENCE DESIGN ERRATA

#### **ISSUE 1 ERRATA** 1

ERRATA PMC-2001584

> This issue 1 contains errata applied to the Issue 2 PMC-1981070, S/UNI-622-POS Reference Design. The issue 2 Reference Design and issue 1 errata supersede all prior editions and versions.

S/UNI-622-POS REFERENCE DESIGN ERRATA

# 2 REFERENCE DESIGN DOCUMENTATION DISCREPANCIES:

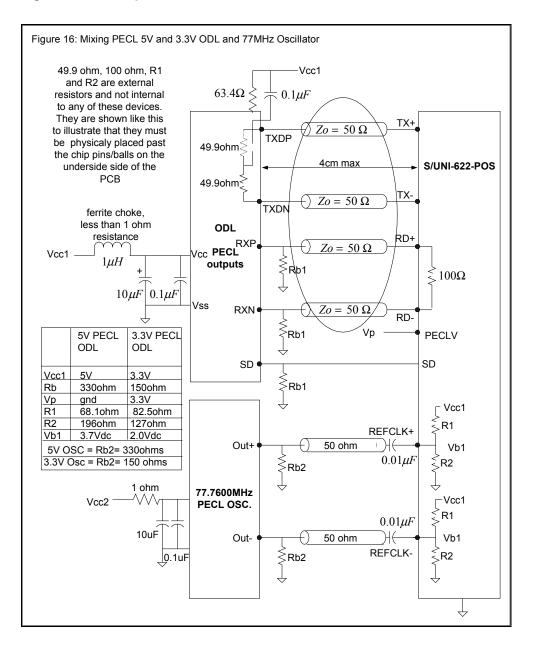

#### 2.1 Trace Impedance should be 500hms not 100 ohms in Figure 16

The controlled trace impedance for the RXD+/- and TXD+/- were wrongly labeled as being 100 ohms each in Figure 16 of the reference design document. In Figure 1: Trace Impedance Correction, the circled traces are shown correctly as being 50 ohms each (100 ohms differential).

#### Figure 1: Trace Impedance Correction

ERRATA PMC-2001584

S/UNI-622-POS REFERENCE DESIGN ERRATA

### 2.2 Change the 5V 77.76MHz Oscillator to a low Jitter type

In section 16, Rev 3 BOM (Bill of Materials), page 2, under item OSC\_PECL\_77.76MHZ., 200ppm, column Manufacturer, remove the 5V type Saronix 99T27M. In it's place, insert (add) the following low jitter oscillator:

Saronix PECL SONET oscillator with low jitter output, (3.5ps rms and 1ps cycle to cycle). Series SEL2400/SEL3400.

PECL3401AA-77.76

77.76 MHz, 20ppm, 0-70 C, 5V (for WAN applications)

PECL3401B-77.76

77.76 MHz, 50ppm, 0-70 C, 5V (for LAN applications)

# 2.3 C47 clarification in the BOM

C47 in the BOM on page 1 of section 16 is listed as a 0.1uF X7R. It should be listed as a 10uF, 10V Tantalum.

### 2.4 Vcc to XC1701L should be 3.3 V and not 5V

The XC1701L PROMS on page 6 of 8 of Revision 3 schematics are 3.3V type and they are connected to a 3.3V FPGA. VCC of U9, U12, U16, and U17 should be connected to 3.3VD and not to Vcc as shown. Also, R1, R2 and C1on this page should be connected to 3.3VD and not Vcc

S/UNI-622-POS REFERENCE DESIGN ERRATA

# 3 APPLICATION NOTES:

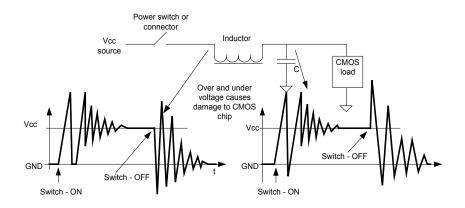

### 3.1 Caution on using Inductors to filter power supplies.

**ISSUE 1**

Sometimes inductors are used to filter power supplies to CMOS semiconductors and to reduce currents in hot-card insert applications. In such cases, care must be exercised to prevent damage to CMOS IC's. When power is applied to LC circuits, the ringing at the load and line side can cause voltages that exceed the chips maximum ranges and cause permanent damage to the device. Also on power down, such as hot card insertion and extraction, the voltage spikes induced by the inductor can cause permanent device damage and cause sparking at the connector/switch thus reducing component life. See figures below for more detail.

Because the LC forms a tank circuit, the resultant ringing voltage could be greater than Vcc and lower than ground on both sides of the inductor as shown in Figure 2: Inductor Transients may damage CMOS circuits.

## Figure 2: Inductor Transients may damage CMOS circuits

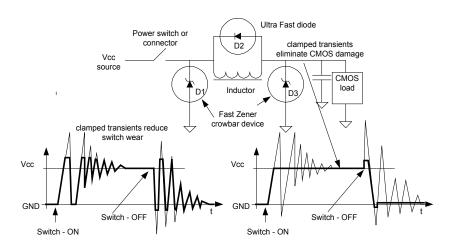

In Figure 2: Inductor Transients may damage CMOS circuits, D2 acts to commute the inductor voltage generated when power is abruptly removed from the primary side of the inductor. The voltage across the inductor is clamped by D2 to max 0.7V in the reverse direction.

D1 acts to prevent the primary side from high voltages which may cause arcing across the switch.

D3 acts to prevent the secondary side from over voltage by clamping action of the zener type device. Also, the under voltage is clamped to -0.7 V.

S/UNI-622-POS REFERENCE DESIGN ERRATA

Figure 3: Inductor Transients Clamped by Diodes

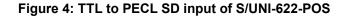

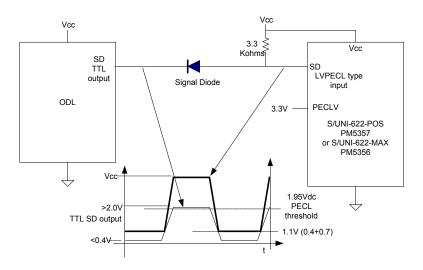

# 3.2 Connecting a TTL SD from ODL to SD PECL type input of S/UNI-622-POS

The SD input of the POS has a much bigger dynamic range than the standard true PECL receiver. Also the SD signal switches so infrequently that it can be considered as a DC signal. The figure below shows how to connect a TTL level signal to a single ended PECL input using a standard signal diode and a pullup resistor. TTL outputs typically are less than 0.4V for a low and more than 2.0V for a logic high. TTL drivers can sink a lot more current than they can source.

When the ODL's TTL SD output is low (<0.4V), current is drawn through the 3.3K resistor and the diode is forward biased. The voltage on the anode side of the diode now will be less than 1.1V (ground plus 0.4V plus the diode drop of 0.7 V). A 1.1V is lower than the 1.95V LVPECL threshold and will be recognized as a low.

When the TTL SD output switches high, theoretically its output will be greater than 2.4 V. The diode will be off and the voltage on the anode side of the diode will be higher than 2.4V+0.7V = 3.1V which is well above than 1.95V required for a LVPECL high.

S/UNI-622-POS REFERENCE DESIGN ERRATA

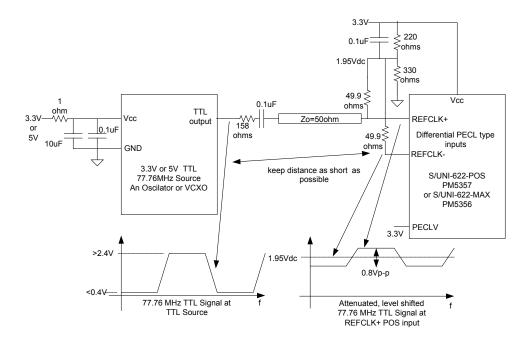

#### 3.3 Interfacing a TTL single ended 77.76MHz Oscillator Interface to REFCLK+/- PECL inputs

In some cases, a PECL oscillator or VCXO may be substituted for a cheaper TTL type. The circuit below will interface a single ended TTL signal to the PECL-like inputs of the S/UNI's differential REFCLK+/- inputs. Filter the power supply well to the TTL clock source as any power supply noise may frequency modulate the output. Depending on the current draw, use a small 1 ohm resistor to keep the voltage drop (IR) across the resistor as low as possible.

# Figure 5: TTL to Single ended PECL Interface

| <u>PMC</u> | PMC-Sierra, Inc. |

|------------|------------------|

| ISSUE 1    | S/L              |

S/UNI-622-POS REFERENCE DESIGN ERRATA

The TTL signal has to be attenuated from about 2.4Vdc p-p about to 0.8 Vp-p. This is done as a simple resistor divider using the 158 ohms and 49.9 ohms.

Then we have to ac couple to level shift so that the 0.8V signal is centered around 1.95Vdc, which is the sweet spot of the PECL like differential receivers of the S/UNI device.

The single ended signal is terminated into the 49.9 (50 ohm) resistor to reduce reflections and thus jitter. The REFCLK- input is biased at the mid point of the LVPECL at 1.95 V. So the input at REFCLK+ will swing above and below this voltage at REFCLK-. Do not use a TTL to PECL converter chip as it will generate too much jitter for this application.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE 7

S/UNI-622-POS REFERENCE DESIGN ERRATA

### **CONTACTING PMC-SIERRA, INC.**

Please report any functional discrepancies or datasheet errors to:

PMC-Sierra, Inc. 105-8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000

Fax: (604) 415-6200

Document Information: document@pmc-sierra.com Corporate Information: info@pmc-sierra.com Application Information: apps@pmc-sierra.com (604) 415-4533 Web Site: http://www.pmc-sierra.com

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

© 1999.2000 PMC-Sierra. Inc.

PMC-2001584 (R1) ref PMC-1981070 (R2) Issue date: October, 2000