# T1 Framer

# Features

- Monolithic T1 Framing Device

- Both Framers Support SF(D4<sup>®</sup>) and ESF Framing Formats

- CS62180B Supports SLC-96<sup>®</sup> and T1DM Framing Formats

- CS62180B Contains Updated AIS and Carrier Loss Detection Criteria

- CS62180B is Pin Compatible with CS62180A, DS2180A, and DS2180

# **General Description**

The CS62180A and CS62180B are monolithic CMOS devices which encode and decode T1 framing formats. The devices support bit-seven and B8ZS zero suppression, and bit-robbed signaling. Clear channel mode can be selected on a per channel basis.

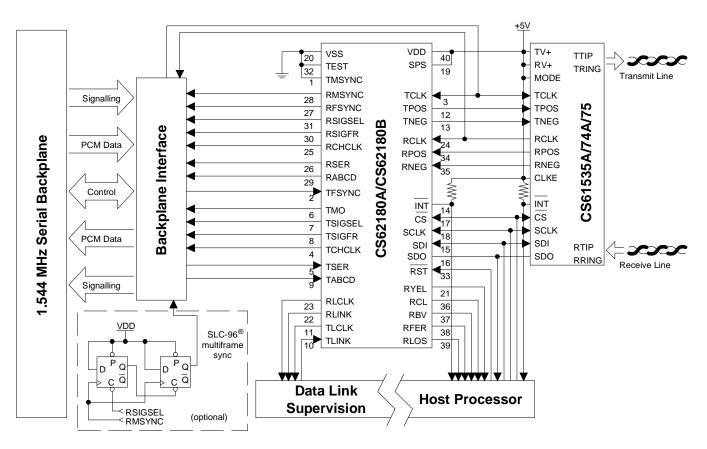

The serial interface has been enhanced to allow the CS62180A and CS62180B to share a chip select signal and register address space with the CS61535A, CS61574A, and CS61575 Line Interface Units.

# Applications

- T1 Line Cards

- ISDN Primary Rate Line Cards

# **Ordering Information:**

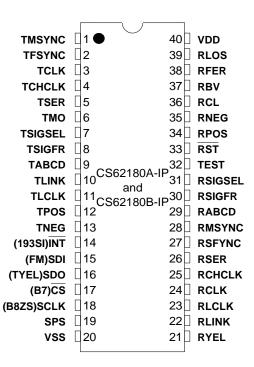

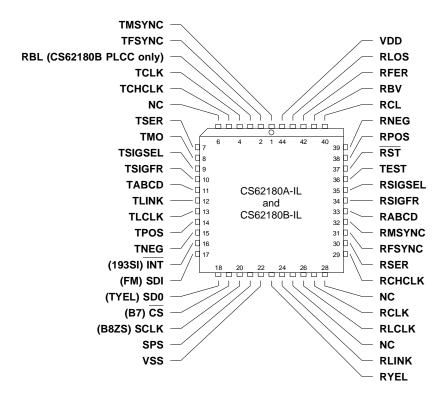

|             |                    | 40.1- 05.00  |

|-------------|--------------------|--------------|

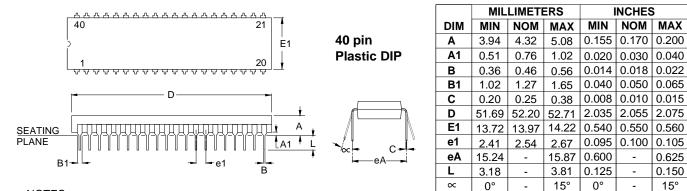

| CS62180A-IP | 40 Pin Plastic DIP | -40 to 85 °C |

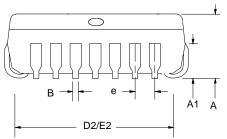

| CS62180A-IL | 44 Pin PLCC        | -40 to 85 °C |

| CS62180B-IP | 40 Pin Plastic DIP | -40 to 85 °C |

| CS62180B-IL | 44 Pin PLCC        | -40 to 85 °C |

#### ABSOLUTE MAXIMUM RATINGS

| Parameter                       |                     |     | Min  | Тур | Max | Units |

|---------------------------------|---------------------|-----|------|-----|-----|-------|

| DC Supply                       | (Referenced to GND) | Vdd | -    | -   | 6.0 | V     |

| Input voltage, any pin          | (Referenced to GND) | Vin | -1.0 | -   | +7  | V     |

| Input Current, any pin (Note 1) |                     |     | -10  | -   | +10 | mA    |

| Ambient Operating Temperature   |                     |     | -40  | -   | 85  | °C    |

| Storage Temperature             |                     |     | -65  | -   | 150 | °C    |

| Soldering Temperature for 10 s. |                     |     | -    | -   | 260 | °C    |

Notes: 1. Transient current of up to 100 mA will not cause SCR latch-up.

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

#### RECOMMENDED OPERATING CONDITIONS

| Parameter                         | Symbol          | Min | Тур | Max | Units |

|-----------------------------------|-----------------|-----|-----|-----|-------|

| DC Voltage                        | Vdd             | 4.5 | 5.0 | 5.5 | V     |

| Supply Current (Notes 2 and 3)    | I <sub>DD</sub> | -   | 3   | 10  | mA    |

| Ambient Operating Temperature     | TA              | -40 | 25  | 85  | °C    |

| Power Consumption (Notes 2 and 3) | Pc              | -   | 15  | 85  | mW    |

Notes: 2. TCLK = RCLK = 1.544 MHz. If RCLK is static and RST is high, I<sub>DD</sub> will typically be 1.0 mA. 3. Outputs open.

#### DIGITAL CHARACTERISTICS (T<sub>A</sub> = -40 to 85 °C; $V_{DD}$ = 5.0 V ±10%; GND = 0 V)

| Parameter                 |                 | Symbol | Min                   | Тур | Max                  | Units |

|---------------------------|-----------------|--------|-----------------------|-----|----------------------|-------|

| High-Level Input Voltage  | (Note 4)        | VIH    | 2.0                   | -   | V <sub>DD</sub> +0.3 | V     |

| Low-Level Input Voltage   |                 | HIL    | -0.3                  | -   | +0.8                 | V     |

| High-level Output Voltage | (Note 5)        | Vон    | V <sub>DD</sub> - 1.0 | -   | -                    | V     |

| Low-Level Output Voltage  | V <sub>OL</sub> | -      | -                     | 0.4 | V                    |       |

| Output Current @ 2.4 V    | (Note 6)        | Іон    | -                     | -   | -1                   | mA    |

| Output Current @ 0.4 V    | (Note 7)        | lol    | +4                    | -   | -                    | mA    |

| Input Leakage Current     |                 | ١L     | -                     | -   | 1                    | μA    |

| Output Leakage Current    | (Note 8)        | Ilo    | -                     | -   | 1                    | μA    |

| Input Capacitance         |                 | CIN    | -                     | -   | 5                    | pF    |

| Output Capacitance        |                 | Соит   | -                     | -   | 7                    | pF    |

Notes: 4. V<sub>IH</sub> (min) = 2.2 V for V<sub>DD</sub> = 5.25 to 5.5 V and T<sub>A</sub> > 70 °C.

5. IOUT = -100  $\mu$ A. This guarantees the ability to drive one TTL load (V<sub>OH</sub> = 2.4 V @ I<sub>OUT</sub> = -40  $\mu$ A).

6. All outputs except INT, which is open drain.

7. All outputs.

8. Applies to SDO when tristated.

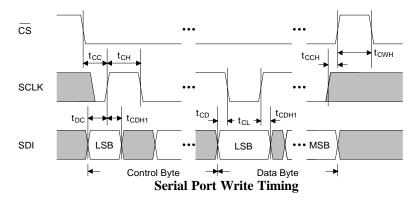

#### SWITCHING CHARACTERISTICS - SERIAL PORT

$(T_A = -40 \text{ to } 85 \text{ }^\circ\text{C}; V_{DD} = 5V \pm 10\%; V_{IH} = 2.0V; V_{IL} = 0.8V; Maximum input rise & fall times of 10 ns)$

| Parameter                                      | Symbol                                | Min | Тур | Max | Units |

|------------------------------------------------|---------------------------------------|-----|-----|-----|-------|

| SDI to SCLK Setup                              | tDC                                   | 50  | -   | -   | ns    |

| SCLK to SDI Hold                               | tCDH1                                 | 50  | -   | -   | ns    |

| SDI to SCLK Falling Edge (Applies to CS62180A) | tCD                                   | 50  | -   | -   | ns    |

| SCLK Low Time                                  | t <sub>CL</sub>                       | 250 | -   | -   | ns    |

| SCLK High Time                                 | tсн                                   | 250 | -   | -   | ns    |

| SCLK Rise & Fall Times (No                     | te 9) t <sub>R</sub> , t <sub>F</sub> | -   | -   | 500 | ns    |

| CS to SCLK Set up                              | tcc                                   | 50  | -   | -   | ns    |

| SCLK to CS Hold                                | tссн                                  | 50  | -   | -   | ns    |

| CS Inactive Time                               | tсwн                                  | 250 | -   | -   | ns    |

| SCLK to SDO Valid (No                          | te 9) t <sub>CDV</sub>                | -   | -   | 200 | ns    |

| SCLK Rising to MSB of SDO Hold (Note           | e 10) tcdh2                           | 25  | -   | -   | ns    |

| CS to SDO High-Z                               | tCDZ                                  | -   | -   | 75  | ns    |

Notes: 9. Output load capacitance = 100 pF.

10. SDO goes High-Z after rising edge of SCLK for MSB, regardless of the state of  $\overline{CS}$ .

- For the CS62180A only, data bytes must be valid across low clock periods to prevent transients in operating modes. t<sub>CD</sub> is not a requirement for the CS62180B. In the CS62180B data is latched on the rising edge of SCLK.

- 12. Shaded regions indicate *don't care* states.

- 13. Serial port write must precede a port read to provide address information.

- 14. SDO will go High-Z: 1) if  $\overline{CS}$  returns high at anytime; 2) after outputing MSB.

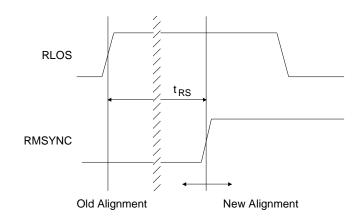

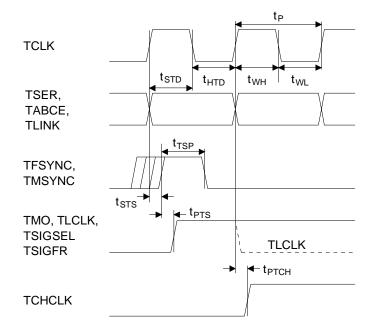

#### SWITCHING CHARACTERISTICS - TRANSMITTER

$(T_A = -40 \text{ to } 85 \text{ }^{\circ}\text{C}; V_{DD} = 5\text{V} \pm 10\%; V_{IH} = 2.0\text{V}; V_{IL} = 0.8\text{V}; \text{Maximum input rise \& fall times of 10 ns})$

| Parameter                                 | Symbol                            | Min  | Тур | Max | Units |

|-------------------------------------------|-----------------------------------|------|-----|-----|-------|

| TCLK Period                               | tP                                | 250  | 648 | -   | ns    |

| TCLK Pulse Width                          | t <sub>WL</sub> , t <sub>WH</sub> | 125  | 324 | -   | ns    |

| TCLK Rise & Fall Times                    | t <sub>F</sub> , t <sub>R</sub>   | -    | 20  | -   | ns    |

| TSER, TABCD, TLINK Setup to TCLK Falling  | tstd                              | 50   | -   | -   | ns    |

| TSER, TABCD, TLINK Hold from TCLK Falling | tнтр                              | 50   | -   | -   | ns    |

| TFSYNC, TMSYNC Setup to TCLK Rising       | tsts                              | -125 | -   | 125 | ns    |

| TFSYNC, TMSYNC Pulse Width                | t <sub>TSP</sub>                  | 100  | -   | -   | ns    |

| Propagation Delays                        |                                   |      |     |     |       |

| TFSYNC to TMO, TSIGSEL, TSIGFR, TLCLK     | <b>t</b> PTS                      | -    | -   | 75  | ns    |

| TCLK Rising to TCHCLK                     | tртсн                             | -    | -   | 75  | ns    |

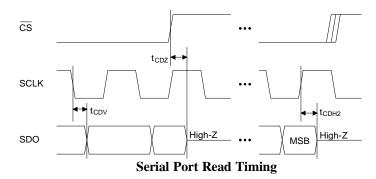

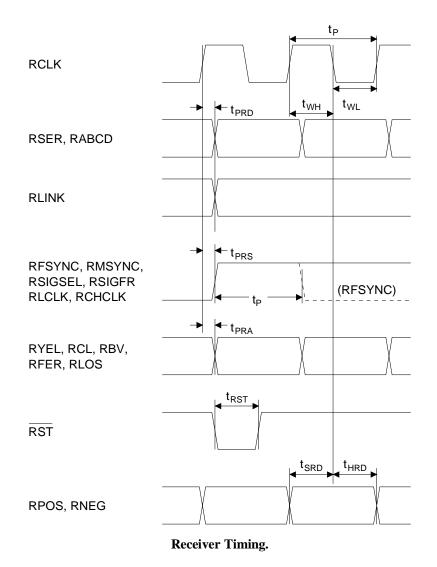

#### SWITCHING CHARACTERISTICS - RECEIVER

$(T_A = -40 \text{ to } 85 \text{ }^{\circ}\text{C}; V_{DD} = 5\text{V} \pm 10\%; V_{IH} = 2.0\text{V}; V_{IL} = 0.8\text{V}; \text{Maximum input rise \& fall times of 10 ns})$

| Parameter                                            | Symbol                 | Min                               | Тур | Max          | Units |          |

|------------------------------------------------------|------------------------|-----------------------------------|-----|--------------|-------|----------|

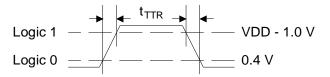

| Transition Time, All Outputs                         | t <sub>TTR</sub>       | -                                 | -   | 20           | ns    |          |

| RCLK Period                                          |                        | tP                                | 250 | 648          | -     | ns       |

| RCLK Pulse Width                                     |                        | t <sub>WL</sub> , t <sub>WH</sub> | 100 | 324          | -     | ns       |

| RCLK Rise & Fall Times                               |                        | t <sub>F</sub> , t <sub>R</sub>   | -   | 20           | -     | ns       |

| RPOS, RNEG Setup to RCLK Fallir                      | ng                     | tSRD                              | 50  | -            | -     | ns       |

| RPOS, RNEG Hold to RCLK Falling                      | )                      | thrd                              | 50  | -            | -     | ns       |

| Minimum RST Pulse Width on Syst                      | em Power Up or Restart | tRST                              | 1   | -            | -     | μs       |

| Propagation Delays                                   |                        |                                   |     |              |       |          |

| RCLK to RMSYNC, RFSYNC,RSIG<br>RSIGFR, RLCLK, RCHCLK | SEL,                   | tprs                              | -   | -            | 75    | ns       |

| RCLK to RSER, RABCD, RLINK                           |                        | tPRD                              | -   | -            | 75    | ns       |

| RCLK to RYEL, RCL, RFER, RLOS                        | S, RBV                 | t <sub>PRA</sub>                  | -   | -            | 75    | ns       |

| Average Reframe Time                                 | (Notes 15 and 16)      |                                   |     |              |       |          |

|                                                      | .2 = 0<br>.2 = 1       | t <sub>RS</sub>                   | -   | 3.75<br>7.25 | -     | ms<br>ms |

|                                                      | .2 = 0<br>.2 = 1       | tRS                               | -   | 7.5<br>14.5  | -     | ms<br>ms |

| T1DM                                                 |                        | tRS                               | -   | 750          | -     | μs       |

| SLC-96 <sup>®</sup>                                  |                        | tRS                               | -   | 6.0          | -     | ms       |

Notes: 15. Average reframe time is the time from the rising edge of RLOS until the rising edge of RMSYNC which updates the receiver output timing.

16. With error free data.

#### **Reframe Timing.**

TAL

Rise and Fall Times for RCLK & TCLK.

#### **Transition Times for All Receiver Outputs.**

Note: TMO, TLCLK, TSIGSEL and TSIGFR are generally coincident with the rising edge of TCLK.

**Transmitter Timing.**

# **GENERAL DESCRIPTION**

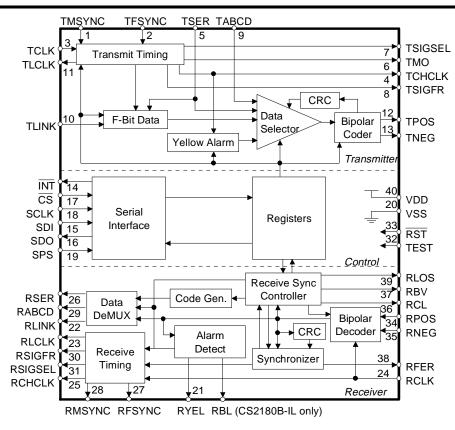

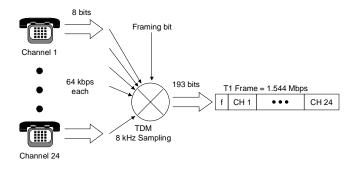

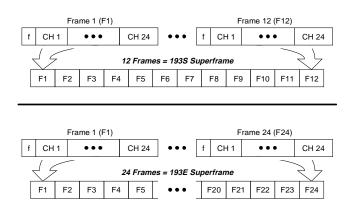

The CS62180A is a monolithic CMOS circuit that encodes and decodes T1 (1.544 MHz) digital transmission formats for SF(D4<sup>®</sup>) (193S: 12 frames per superframe), and ESF (193E: 24 frames per superframe) framing formats. The CS62180B also encodes and decodes the SLC-96<sup>®</sup> (SLC-96<sup>®</sup>: 72 frames per superframe) and DDS<sup>®</sup> T1DM (T1DM: 12 frames per superframe plus unique channel number 24) formats.

Both the CS62180A and the CS62180B provide full support for individual clear channels, bitrobbed signaling, alarm detection and generation, zero suppression, and idle channels. An overview of the 193S, 193E, SLC-96<sup>®</sup> and T1DM framing formats is provided in the Applications Section. The device provides independent transmit and receive sides, with a shared serial controller interface for use with a host processor. A hardware mode is also available for operation independent of a host controller. The SLC-96<sup>®</sup> and T1DM formats can be selected only via the CS62180B serial controller interface.

The serial interface provides access to 16 onchip control and status registers. The control registers are used to configure global parameters such as the framing format and zero suppression mode, as well as transmitter or receiver specific parameters. A hardware interrupt is provided, which can be configured via interrupt mask and status registers to signal any combination of alarm conditions.

Transmitter commands include enabling external framing bit, CRC, or S-bit insertion, declaring individual DS0 channels clear and/or idle, and enabling yellow and blue alarm modes in different formats. The receiver can be configured to replace individual incoming channels with idle or digital milliwatt ( $\mu$ -LAW) codes, and a large variety of resync options are provided. Bipolar violations, CRC and framing errors are automat-

ically counted in another set of registers which can be arbitrarily reset via the serial interface to provide variable saturation points. The Receive Status Register (RSR) provides data on all error and alarm conditions, and in conjunction with the Receive Interrupt Mask Register (RIMR), can be configured to signal an interrupt on INT in response to any alarm condition.

Note: there are two different naming conventions in practice concerning the numbering of bits within a word. The most common convention in EE and Computer Science is to number the bits as 0 - 7, starting from the LSB. This is the convention used throughout this data sheet when referring to register bits. A different convention is used in the telecom literature when referring to the bits in a digital transmission stream. In this case, they are numbered 1 - 8, *starting from the MSB*. This convention is maintained in this data sheet whenever referring to the bits of a DS0 channel word.

# CS62180B ENHANCEMENTS

Enhancements made in the CS62180B include the following. The SLC-96<sup>®</sup> and DDS<sup>®</sup> T1DM framing formats are supported in host mode. The AIS (Blue Code) detection is made compatible with TR-TSY-000191 requirements (unframed all ones), and a received-blue-alarm output pin is added to the PLCC package. The Receive Carrier Loss detection criteria is made compatible with the industry standard requirement of 175 ±75 zeros. The receiver line code decoder is now universal. The decoder will automatically decode either AMI or B8ZS. The CS62180B B8ZS control option controls only the transmitter's encoder. The universal decoder simplifies the provisioning of B8ZS in the network. Lastly, the serial control interface was simplified. When writing data bytes on SDI, it is no longer necessary to have SDI valid for both the rising and falling edges of SCLK. Rather, SDI need be stable only on the rising edge of SCLK.

# HOST MODE

# Serial Interface

For applications in which the device is to interface with a host processor, the CS62180A and CS62180B can be configured to run in host mode by tying the Serial Port Select pin (SPS) to the +5 V supply (VDD). This allows access to the serial port, providing a large number of configuration options via the 16 on-chip control and status registers.

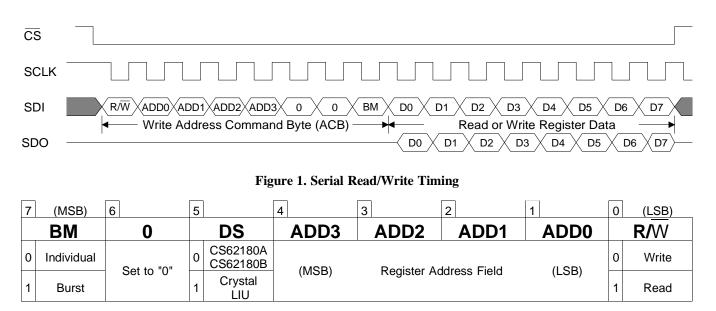

Serial read/write timing, controlled by SCLK, is entirely independent of the transmit and receive timing. This allows the host microcontroller to monitor the status register and counters, modify configuration options, and issue commands asynchronously with the T1 system. A serial timing overview is provided in Figure 1.

All data transfers are initiated by setting Chip Select  $(\overline{CS})$  low. Any read or write to the serial port is initiated by writing an 8-bit command word. The command word consists of 4 separate fields (see Figure 2). When reading from the port, data is output on the falling edge of SCLK, and held until the next falling edge.

**CS62180A Only:** All data is written to and read from the port LSB first. When writing to the port, input data is not latched, and the device registers are open to the bus during SCLK low. *To avoid transient corruption of the device registers, data must be valid for the entire low period of SCLK*.

**CS62180B Only:** All data is written to and read from the port LSB first. When writing to the port, SDI input data is sampled on the rising edge of SCLK.

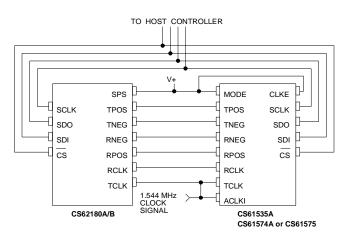

D0 (LSB) is the  $R/\overline{W}$  field, and specifies whether the current operation is to be a read or a write: 1 = read, 0 = write. The second 4 bits (D1 - D4) contain the address field. Written LSB first, they specify which of the sixteen registers to access. D5 (Device Select) should be set to zero when addressing the CS62180A or CS62180B. However, if the CS62180A or CS62180B shares the same serial interface lines with a Crystal TI Line Interface (see Figure 3), D5 will be set to a "1" when addressing the Line Interface device. The CS62180A and CS62180B will ignore any read/write commands with a "1" in D5, allowing both parts to share  $\overline{CS}$ . D6 is reserved, and must be set to 0 for normal operation.

Figure 2. Address Command Byte (ACB)

Figure 3. Interfacing to a Crystal T1 LIU.

D7 (MSB) specifies burst mode if set to 1. When using burst mode, the address field of the command word must be "0000", any other value will invalidate the command, and the CS62180A and CS62180B will simply ignore it. This effectively means that the command for a burst write is 80 (hex) and a burst read is 81 (hex).

Burst mode allows the sixteen registers to be consecutively read or written. Writing all registers allows fast initialization at power-up or system reset. (Note that the Receiver Status Register, RSR, is read-only, so a write during burst mode will have no effect.) When using burst mode, registers are read or written in address order, 0000 (RSR) to 1111 (RMR3). Burst mode ends on the first rising edge of  $\overline{\text{CS}}$ . See Table 1 for a complete list of the CS62180A and CS62180B on-chip registers.

| ADDR | REGISTE | (T) TRAN<br>R NAME AND DESCRIPTION (R) RECE                                                                                                                           |     |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 0000 | RSR     | <b>Receive Status Register</b> - A read only register which reports all active receiver alarm conditions.                                                             | R   |

| 0001 | RIMR    | <b>Receive Interrupt Mask Register</b> - A mask which allows selection of individual alarm conditions for generation of hardware interrupt.                           | R   |

| 0010 | BVCR    | <b>Bipolar Violation Count Register</b> - A bipolar violation alarm is generated after this 8 bit counter surpasses it's user definable limit.                        | R   |

| 0011 | ECR     | <b>Error Count Register</b> - Two separate 4 bit counters, which record OOF errors, and frame bit or CRC errors. Like BVCR, each can be preset to a saturation point. | R   |

| 0100 | CCR     | <b>Common Control Register</b> - Selects global configuration options, such as: framing mode, zero suppression, or loopback.                                          | T/R |

| 0101 | RCR     | <b>Receive Control Register</b> - Selects receiver specific options, such as the resync algorithm or insertion of digital milliwatt codes.                            | R   |

| 0110 | TCR     | <b>Transmit Control Register</b> - Selects transmitter specific options, such as alarm generation, clear or idle channel enable, and external S-bit or CRC insertion. | Т   |

| 0111 | TIR1    | Transmit Idle Registers - Each bit of the three TIR registers corresponds to an                                                                                       | Т   |

| 1000 | TIR2    | individual DS0 channel. When set, that channel is replaced with an idle code.                                                                                         |     |

| 1001 | TIR3    |                                                                                                                                                                       |     |

| 1010 | TTR1    | Transmit Transparent Registers - Each bit corresponds to a DS0 channel. When                                                                                          | Т   |

| 1011 | TTR2    | set, that signaling and B7 zero suppression is disabled for that channel.                                                                                             |     |

| 1100 | TTR3    |                                                                                                                                                                       |     |

| 1101 | RMR1    | Receive Mark Registers - Each bit corresponds to a DS0 channel. When set, the                                                                                         | R   |

| 1110 | RMR2    | channel data is replaced with an idle or digital milliwatt code.                                                                                                      |     |

| 1111 | RMR3    |                                                                                                                                                                       |     |

Table 1. On-Chip Registers

| 7 (MSB)     | 6 |      | 5 |       | 4           | 3 |       | 2 |         | 1 |             | 0 | (LSB)    |

|-------------|---|------|---|-------|-------------|---|-------|---|---------|---|-------------|---|----------|

| FM1         | F | RSR2 | Ε | YELMD | FM          |   | YELS  |   | B8ZS    |   | <b>B7</b>   |   | LPBK     |

| Soo Eig. 4b | 0 | B8ZS | 0 | FDL   | Soo Fig. 4b | 0 | Bit 2 | 0 | Disable | 0 | Transparent | 0 | Normal   |

| See Fig. 4b | 1 | COFA | 1 | Bit 2 | See Fig. 4b | 1 | S-bit | 1 | Enable  | 1 | B7 Stuffing | 1 | Loopback |

Figure 4a. Common Control Register (CCR)

#### **Common Control Register**

The Common Control Register (CCR) determines global operating characteristics common to both the transmitter and receiver. It currently provides for selection of the framing mode (193S, 193E, SLC-96<sup>®</sup> or T1DM), the format of yellow alarms, the zero suppression format (B7 or B8ZS), loopback operation, and control of output to RSR.2. In the CS62180A, CCR.7 is reserved for future use, and should always be set 0 for proper operation. See Figure 4a for an overview of the CCR.

# Loopback CCR.0: LPBK

Setting LPBK (CCR.0) to "1" puts the CS62180A and CS62180B into loopback mode. While in loopback, the TPOS/TNEG and TCLK outputs are internally rerouted directly to the RPOS/RNEG and RCLK inputs, while an unframed, all "1's" stream is output on the TPOS/TNEG pins. All operating modes, except blue alarm transmission, remain functional during loopback. Note that enabling loopback will usually invoke an out-of-frame (OOF) error until the receiver can resync to the new framing alignment. See the section on the Receive Control Register (RCR) for a description of the resync options available.

Zero Suppression CCR.1: B7 CCR.2: B8ZS

B7 and B8ZS select the zero suppression mode. Setting B7 (CCR.1) to "1" will enable bit 7 zero substitution. This causes any channel word with all zeros to be transmitted with bit 7 (2<sup>nd</sup> LSB) forced to a "1". B7 mode only affects the transmitter, the receiver does not decode B7. Note that bit 7 stuffing can be disabled on an individual channel basis for clear channel transmission via the Transmit Transparent Registers TTR1 - TTR3 (see description of transmitter which follows).

B8ZS coding operates independent of channel boundaries, and is transparent to all other functions. When using B8ZS, the final transmission stream is examined before transmission, and any eight consecutive zeros will be replaced with a B8ZS code word before transmission.

**CS62180A Only**: If B8ZS (CCR.2) is set to a "1", B8ZS zero substitution will be enabled in both the transmitter and receiver. Incoming B8ZS codes will be intercepted by the receiver and replaced with 8 zeros before being processed by the rest of the receive side.

**CS62180B Only**: If B8ZS (CCR.2) is set to a "1", B8ZS zero substitution will be enabled in the transmitter. Independent of the setting of CCR.2, any incoming B8ZS codes will be intercepted by the receiver and replaced with 8 zeros before being processed by the rest of the receive side. The receiver is always capable of receiving either AMI or B8ZS encoded data.

Note: For T1DM, CCR.1 and CCR.2 should be set to a "0" since DDS<sup>®</sup> equipment assures a 1-in-8 one's density.

193S Yellow Alarm Format CCR.3: YELS

The CS62180A and CS62180B supports two different yellow alarm formats for 193S framing. Whichever format is selected, it will be used by both the transmit side, for yellow alarm generation, and the receive side, for alarm detection.

When using 193S framing, a "0" in YELS (CCR.3) will encode/decode yellow alarms as a "0" in bit 2 (2<sup>nd</sup> MSB) of all channels. Setting CCR.3 to "1" will cause yellow alarms to be encoded/decoded as a "1" is the S-bit position of frame 12.

Note: For T1DM and SLC-96<sup>®</sup>, CCR.3 should be set to a "0".

Framing Format CCR.4: FM CCR.7: FM1

As shown in Figure 4b, CCR.4 and CCR.7 select the framing format. Note that in the CS62180A, CCR.7 must be set to "0", and the SLC-96<sup>®</sup> and T1DM formats are not available. See the text for the Transmit Control Register (TCR) and Receive Control Register (RCR) for further information on the particular options available for each framing format.

| 7   | 4  |                        |

|-----|----|------------------------|

| FM1 | FM | Format Selected        |

| 0   | 0  | 193S (D4)              |

| 0   | 1  | 193E (ESF)             |

| 1   | 0  | SLC-96 (CS62180B only) |

| 1   | 1  | T1DM (CS62180B only)   |

#### Figure 4b. Framing Format Selection

Note: Changing the framing mode does not force the receiver to resynchronize. A forced resync should be done to insure correct receiver synchronization after the framing mode is changed.

# 193E Yellow Alarm Format CCR.5: EYELMD

The CS62180A and CS62180B supports two different yellow alarm formats for 193E framing. Whichever format is selected, it will be used by both the transmit side, for yellow alarm generation, and the receive side, for alarm detection.

When using 193E framing, a "0" in EYELMD (CCR.5) will encode/decode yellow alarms as a repeating sequence of 00FF (hex) on the 4 kHz facility data link (FDL). If CCR.5 is set, 193E yellow alarms will be handled as a "0" in bit 2 (2<sup>nd</sup> MSB) of all channels.

Control of RSR.2 CCR.6: FRSR2

CCR.6 allows you to change the meaning of D2 in the Receive Status Register (RSR.2). If CCR.6 is clear, RSR.2 will report the detection of B8ZS codes in the received T1 input. If CCR.6 is set to a "1", RSR.2 will be used to signal a Change of Frame Alignment (COFA). A COFA is reported when the last receiver resync resulted in a change of framing or multiframing alignment. Refer to the description of the Receive Status Register for further information.

# TRANSMITTER

The transmit sides of the CS62180A and CS62180B have three types of inputs, the clock, sync, and data inputs. Control is handled through the serial port in host mode, and through the mode control pins in hardware mode (see the last section for a description of hardware mode operation).

# Input Data

None of the data inputs are buffered, so the data at each input must be available at the appropriate time for the CS62180A and CS62180B to multiplex into the output stream. All inputs are sampled on the falling edge of TCLK. The delay from input to output is 10 TCLK cycles.

NRZ data for DS0 channels is input on TSER. Framing bits ( $F_T$  or FPS bits) and CRC data may either be generated internally or supplied by the host system. If this data is to be externally supplied, it must be inserted into the DS0 input stream at the appropriate frames and input via TSER.

S-bits may be generated internally, or externally provided via TLINK. FDL bits are always provided externally on TLINK. Bit-robbed signaling, when enabled, is always sampled at TABCD. The CS62180A and CS62180B muxes in data from these 3 sources (TSER, TLINK, and TABCD) automatically depending on the transmitter configuration.

## Output Data

The completed T1 data stream, ready for line transmission, is output on TPOS/TNEG. For operation with a line interface which is transparent to line coding, the output can be set to dual-unipolar format by clearing bit 7 of the Transmit Control Register (TCR.7). TCR.7 should be set to a "1" for operation with a line interface which provides AMI or B8ZS coding. In this configura-

tion, the data will be output on TPOS in NRZ format, and TNEG will remain low. When operating in hardware mode, output defaults to the dual-unipolar format. TPOS and TNEG may not be tied together, so an external OR gate is recommended if NRZ output is required while in hardware mode.

## Frame/Multiframe Synchronization

The CS62180A and CS62180B maintain timing for frame and multiframe alignment with internal counters driven by TCLK. The timing signals generated by those counters are output on TCHCLK, TMO, TSIGSEL, TSIGFR, and TLCLK. These counters determine when the CS62180A and CS62180B will insert F-bits and sample external signaling data. The frame and multiframe counters can be reset independently via TMSYNC and TFSYNC. If left to run without a sync pulse, the CS62180A and CS62180B will arbitrarily choose a framing alignment.

A low to high transition of TMSYNC, occurring near the rising edge of TCLK, resets the CS62180A's and CS62180B's counters to mark the bit-period concurrent with the next falling edge of TCLK as the F-bit of the first frame of a new superframe. All other timing will be set to match the superframe alignment automatically. TMSYNC may be pulsed once at start-up and left low, or left running in sync with superframe timing.

A low to high transition of TFSYNC, occurring near the rising edge of TCLK, resets the CS62180A's and CS62180B's counters to mark the bit-period concurrent with the next falling edge of TCLK as the F-bit of a new frame. If TMSYNC is used to set superframe alignment, frame alignment will also be set, and TFSYNC may be tied low. There is, of course, no harm in using both TMSYNC and TFSYNC together, as TFSYNC has no effect on multiframe alignment if it is in sync. If, however, TFSYNC is used out of sync with TMSYNC, the superframe align-

| TCLK                                          |                                    |                                                         |

|-----------------------------------------------|------------------------------------|---------------------------------------------------------|

| TMSYNC                                        |                                    |                                                         |

| TFSYNC<br>TMO,<br>TSIGSEL,<br>TLCLK<br>TSIGFR |                                    |                                                         |

| TCHCLK                                        |                                    |                                                         |

| TSER                                          | 7 1 2 3 4 5 6 7                    | 1 2 3 4 5 6 7 8 1 2 3                                   |

| TABCD                                         | (D <sub>23</sub> ) (D <sub>2</sub> | 4                                                       |

| TLINK                                         |                                    |                                                         |

| TPOS,<br>TNEG                                 | ← 10 TCLK Cycle Delay              | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ |

Figure 5. Bit Level Transmit Timing (193E, signaling enabled)

ment will be moved forward by the least number of bits necessary to be in alignment with the new frame boundary.

Figure 5 shows the bit-level timing (with signalling enabled). Note that the delay from input to output is 10 TCLK cycles. TCHCLK transitions high at the beginning of every DS0 channel (50% duty cycle).

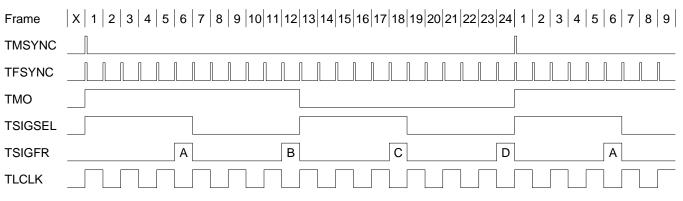

# 193S Timing

Frame and multiframe timing is output on TCHCLK, TMO, TSIGSEL, TSIGFR, and TLCLK. TMO transitions high at the beginning of every superframe (50% duty cycle). TSIGFR goes high during signaling frames (every 6 frames). TLCLK is a 4 kHz clock for the TLINK input. TLCLK goes high during odd frames (external S-bit insertion).

TSIGSEL runs at twice the frequency of TMO. Logical combination of TMO and TSIGSEL provides a way to distinguish the  $6^{\text{th}}$  and  $12^{\text{th}}$  frames for external multiplexing of signaling

channels. TMO is high for channel A, and low for B. See Figure 6 for timing diagram.

# 193E Timing

Frame and multiframe timing is output on TCHCLK, TMO, TSIGSEL, TSIGFR, and TLCLK. TMO transitions high at the beginning of every superframe (50% duty cycle). TSIGFR goes high during signaling frames (every 6 frames). TLCLK is a 4 kHz clock for the TLINK input. TLCLK goes high during odd frames (FDL insertion).

TSIGSEL runs at twice the frequency of TMO. Logical combination of TMO and TSIGSEL provides a way to distinguish the 6th, 12th, 18th, and 24th frames for external multiplexing of signaling channels. TMO is high for channels A and B, and TSIGSEL is high for channels A and C. See Figure 7 for timing diagram.

# CRYSTAL

| Frame   | X 1 2 3 4 5 6 7 8 9 10 11 12 1 2 3 4 5 6 7 8 9 10 11 12 1 9 3 4 5 6 7 8 9 10 11 12 1 2 3 4 5 6 7 8 |

|---------|----------------------------------------------------------------------------------------------------|

| TMSYNC  |                                                                                                    |

| TFSYNC  |                                                                                                    |

| ТМО     |                                                                                                    |

| TSIGSEL |                                                                                                    |

| TSIGFR  | A B A B A                                                                                          |

| TLCLK   |                                                                                                    |

Figure 6. 193S Multiframe Transmit Timing

Figure 7. 193E Multiframe Transmit Timing

# SLC-96<sup>®</sup> Timing

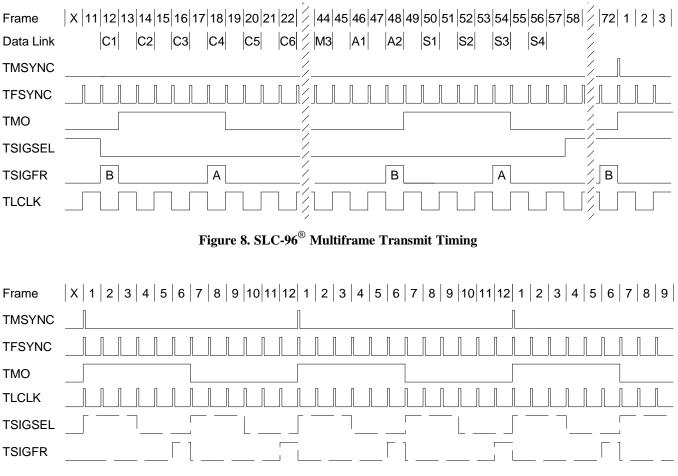

Figure A6 of the Application Section, shows the  $SLC-96^{\mathbb{R}}$  superframe structure. Note that in Figure A6, the first C bit (C1) resides in frame 12. A low to high transition of TMSYNC identifies Frame 1 of Figure A6.

Frame and multiframe timing is output on TCHCLK, TMO, TSIGSEL, TSIGFR and TLCLK. TSIGSEL can be used to identify the location of the DL bits. The TSIGSEL output is high during frames 58 to 11, and is low during frames 12 to 57. When TSIGSEL is low, the CS62180B accepts DL bits on TLINK at a 4 kHz rate, The DL bits which are input on

TLINK are: C1-C11, DC, DC, DC, M1-M3, A1, A2, S1-S4. "DC" signifies "don't care" bits. The DC-bit positions correspond to the spoiler bits. The CS62180B internally generates the spoiler bits. The data input on TLINK in the DC position is ignored by the CS62180B. TLCLK is a 4 kHz clock for the TLINK input. TLCLK goes high during odd frames.

TMO transitions high at the beginning of every 12th frame. TSIGFR goes high during signaling frames (every 6 frames). The rising edge of TMO identifies the  $6^{th}$  frame, and the falling edge of TMO identifies the  $12^{th}$  frame for external multiplexing of signaling channels. See Figure 8 for timing diagram.

Figure 9. T1DM Multiframe Transmit Timing

# **T1DM** Timing

Frame and multiframe timing is output on TCHCLK, TMO, and TLCLK. TMO transitions high at the beginning of every superframe (50% duty cycle). TSIGFR goes high during signaling frames (every 6 frames).

The channel 24 data link is input on TLINK using TLCLK. TLCLK is a 8 kHz clock with a duty cycle of 1 bit period high per frame. When TLCLK is high, TLINK will be sampled on the falling edge of TCLK. See Figure 9 and "Switching Characteristics - Transmitter" for timing diagrams. TSIGSEL and TSIGFR serve no purpose in the T1DM mode and can be ignored. However, TSIGSEL and TSIGFR operate as in 193S mode.

| 7 | (MSB)   | 6 |          | 5 |          | 4 |          | 3 |          | 2 |          | 1 |            | 0 | (LSB)      |

|---|---------|---|----------|---|----------|---|----------|---|----------|---|----------|---|------------|---|------------|

|   | ODF     |   | TFPT     |   | ТСР      |   | RBSE     |   | TIS      |   | 193SI    |   | TBL        |   | TYEL       |

| 0 | Bipolar | 0 | Internal | 0 | Internal | 0 | Disabled | 0 | 7F (Hex) | 0 | Internal | 0 | Normal     | 0 | Normal     |

| 1 | NRZ     | 1 | External | 1 | External | 1 | Enabled  | 1 | FF (Hex) | 1 | External | 1 | Blue Alarm | 1 | Yel. Alarm |

Figure 10. Transmit Control Register (TCR)

# Transmitter Control Register (TCR)

When in host mode, there are a number of options available for transmitter configuration which can be enabled via the Transmit Control Register (TCR), Transmit Transparent Registers (TTR1 - TTR3), and Transmit Idle Registers (TIR1 - TIR3). Serial read and write operations to access these registers are explained in the *Serial Interface* section above. When operating in hardware mode, all control bits in the TCR default to "0" (except TCR.4, which defaults to "1" to enable bit-robbed signaling), and dynamic control is limited to the mode control pins as described under hardware mode below.

The TCR provides control to enable bit-robbed signaling, external framing bit, CRC, or S-bit insertion, and yellow and blue alarm modes. It also provides for two different idle code formats, and selection of bipolar or NRZ output. Figure 10 shows an overview of the Transmit Control Register.

Transmit Yellow Alarm TCR.0: TYEL

Setting TYEL (TCR.0) to a "1" causes the CS62180A and CS62180B to automatically generate and transmit a yellow alarm in the appropriate format. In 193S mode the yellow alarm format used will be determined by the setting of CCR.3. In 193E mode, the yellow alarm format will be determined by the setting of CCR.5. See Common Control Register, above, for description of the available yellow alarm formats for 193S and 193E modes. In SLC-96<sup>®</sup> mode, the CS62180B does not generate the yellow alarm code. rather, the user transmits the

SLC-96<sup>®</sup> yellow alarm via the data link. In T1DM mode, the yellow alarm is transmitted in bit 5 of channel 24 (and CCR.3 should be set to a "0"). Clearing TCR.0 disables yellow alarm transmission.

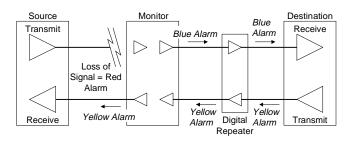

## Transmit Blue Alarm TCR.1: TBL

Setting TBL (TCR.1) to a "1" generates a blue alarm; an unframed sequence of all "1's". If a framed, all "1's" signal is required, an FF (hex) idle code may be output on all channels via appropriate settings of TCR.3 and the TIR registers (see Transmit Idle Code Select below). Blue alarm (Alarm Indication Signal, or AIS) overrides all other transmission data, and a blue alarm is automatically output during loopback. Clearing TCR.1 disables blue alarm transmission.

193S, SLC-96<sup>®</sup> and T1DM S-bit Insertion TCR.2: 193SI

TCR.2 is applicable to 193S,  $SLC-96^{\text{®}}$  and T1DM modes, but not to the 193E mode.

In the 193S and T1DM modes, setting 193SI (TCR.2) to a "1" allows the S-bit (all even F-bits) to be externally supplied via TLINK. When TCR.2 is clear, the S-bit will be internally generated.

In the SLC-96<sup>®</sup> mode, setting 193SI (TCR.2) to a "1" allows the S-bit (selected even F-bits) to be externally supplied via TLINK, and the user must input all Fs, spoiler and DL bits. When TCR.2 is clear, the CS62180B generates the SLC-96<sup>®</sup> spoiler bits and Fs bits, and the user inputs all other DL bits on TLINK using TLCLK.

Note: When using internal S-bit generation (TCR.2 = 0) in conjunction with external F<sub>T</sub> bit insertion (TCR.6 = 1), the CS62180A and CS62180B will logically 'OR' the value at TSER with the internally generated value. This means that the data on TSER during S-bit periods should always be "0" to avoid corrupting the generated FS pattern.

# Transmit Idle Code Select TCR.3: TIS

Individual DS0 channels can be replaced with idle codes by setting the corresponding bits in the Transmit Idle Registers (TIR1 - TIR3) described below. TIS (TCR.3) selects which of two codes to use. A "0" in TCR.3 will cause a 7F (hex) to be inserted into the channels specified in the TIR. Setting TCR.3 to a "1" will select an FF (hex) code. By asserting all 24 channels idle in the TIR, this setting can be used to generate a "framed" blue alarm. Whichever mode is selected, bit-robbed signaling will still effect idle channels unless they are programmed clear (see *Transmit Transparent Registers*, below).

# Robbed Bit Signaling Enable TCR.4: RBSE

A "0" in RBSE (TCR.4) will disable bit-robbed signaling. Setting TCR.4 to a "1" will enable signaling in all channels. In this mode, data on TABCD is inserted into the LSB of all DS0 channels during signaling frames. For mixed voice and data transmission, individual DS0 channels can be programmed clear by setting the corresponding bits in the Transmit Transparent Registers (TTR1 - TTR3) described below. CRC Pass-through TCR.5: TCP

In 193E framing mode, the CRC bits (F-bit of frames 2, 6, 10, 14, 18, and 22) may be either generated internally, or supplied by the user. Clearing TCP (TCR.5) causes the CS62180A and CS62180B to generate and insert the CRC bits automatically. If TCR.5 is set to a "1", data for the CRC channel may be externally supplied. When using this mode, CRC bits are sampled from TSER, and must be externally multiplexed into the DS0 channel data at the F-bit times of CRC frames.

F<sub>T</sub>/FPS Pass Through TCR.6: TFPT

When TFPT (TCR.6) is clear, the framing bits for 193S, T1DM and SLC-96<sup>®</sup> (F<sub>T</sub>), or 193E (FPS) are generated internally and automatically inserted into the outgoing data stream. Setting TCR.6 to a "1" allows the framing bits to be externally provided. When using this mode, framing bits are sampled from TSER, and must be externally multiplexed into the DS0 channel data at the F-bit times of the appropriate frames. See note under TCR.2, above.

*Output Data Format TCR.7: ODF*

ODF (TCR.7) allows the format of the output data at TPOS/TNEG to be set to either dualunipolar or NRZ format. Clearing TCR.7 selects for dual-unipolar format on TPOS/TNEG. Setting TCR.7 to a "1" causes data to be output on TPOS in NRZ format, and TNEG is held low. When operating in hardware mode, output defaults to the dual-unipolar format. TPOS and TNEG may not be tied together, so an external OR gate is recommended if NRZ is required while in hardware mode.

|      | 7 (MSB)      | 6            | 5              | 4                | 3                 | 2                | 1        | 0 (LSB) |

|------|--------------|--------------|----------------|------------------|-------------------|------------------|----------|---------|

| TTR1 | CH8          | CH7          | CH6            | CH5              | CH4               | CH3              | CH2      | CH1     |

| TTR2 | CH16         | CH15         | CH14           | CH13             | CH12              | CH11             | CH10     | CH9     |

| TTR3 | CH24         | CH23         | CH22           | CH21             | CH20              | CH19             | CH18     | CH17    |

|      | "0" = Normal | "1" = Corres | ponding DS0 Cl | hannel is Transp | parent. (Not sign | aling or B7 Inse | ertion.) |         |

|      |              | Figure11.    | Transmit Tr    | ansparent R      | egisters (TTR     | 1 - TTR3)        |          |         |

|      | 7 (MSB)      | 6            | 5              | 4                | 3                 | 2                | 1        | 0 (LSB) |

| TIR1 | CH8          | CH7          | CH6            | CH5              | CH4               | CH3              | CH2      | CH1     |

| TIR2 | CH16         | CH15         | CH14           | CH13             | CH12              | CH11             | CH10     | CH9     |

| TIR3 | CH24         | CH23         | CH22           | CH21             | CH20              | CH19             | CH18     | CH17    |

|      |              |              |                |                  |                   |                  |          |         |

Figure 12. Transmit Idle Registers (TIR1 - TIR3)

#### Transmit Transparent Registers (TTR)

The Transmit Transparent Registers allow individual DS0 channels to be programmed clear, disabling robbed bit signaling and B7 zero suppression for that channel (if selected, B8ZS is unaffected by transparent channels). There are 3 TTR registers: TTR1, TTR2, and TTR3. Each bit in the TTR registers corresponds to a DS0 channel: TTR1.0 = channel 1, TTR1.7 = channel 8, TTR2.7 = channel 16, etc. A channel is programmed clear by setting the bit which corresponds to that channel in the appropriate TTR register. See Figure 11.

## Transmit Idle Registers (TIR)

By setting the appropriate bits in the Transmit Idle Registers, individual DS0 channels can be replaced with the idle code selected via TCR.3 (see above). If the idle channel is not also programmed clear (via TTR1 - TTR3), the code may be corrupted during signaling frames if robbed bit signaling is enabled (TCR.4 = 1). There are 3 TIR registers: TIR1, TIR2, and TIR3. Each bit in the TIR registers corresponds to a DS0 channel: TIR1.0 = channel 1, TIR1.7 = channel 8, TIR2.7 = channel 16, etc. A channel is programmed idle by setting the bit which corresponds to that channel in the appropriate TIR register. See Figure 12.

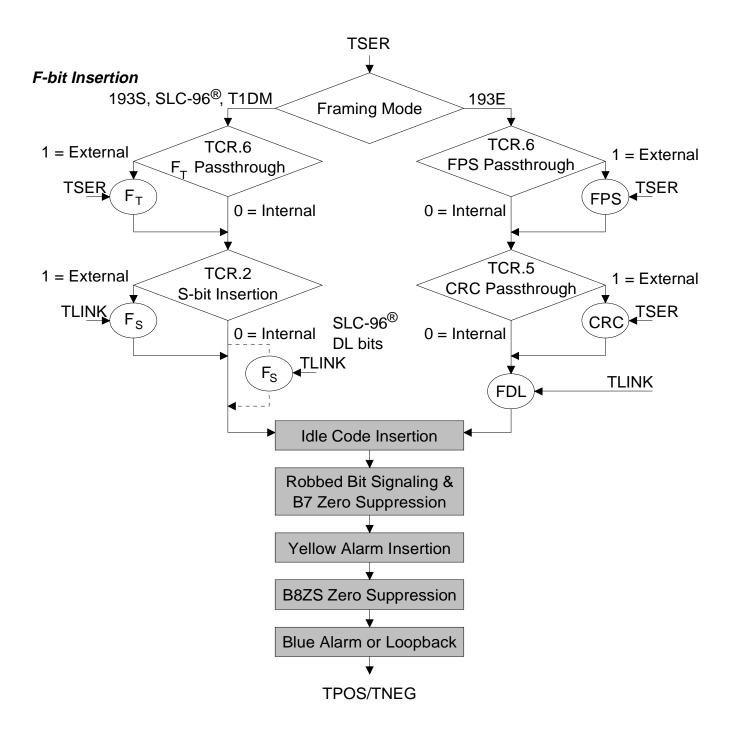

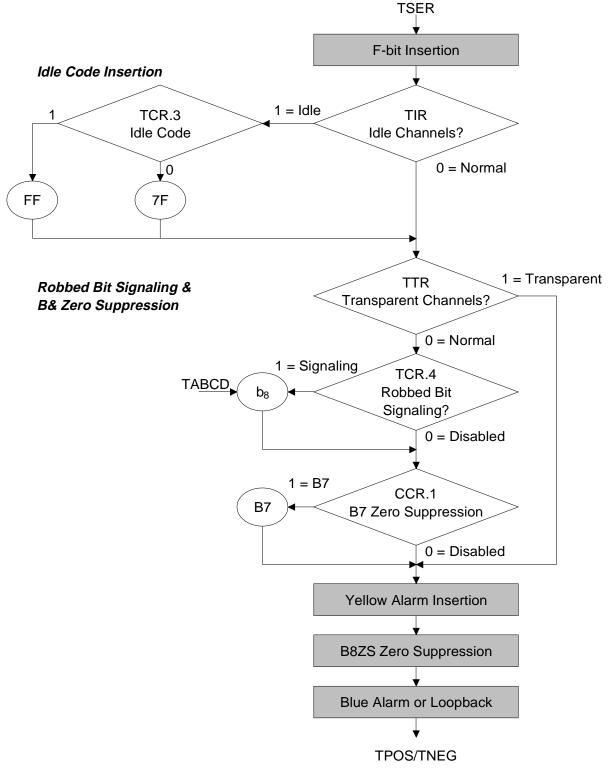

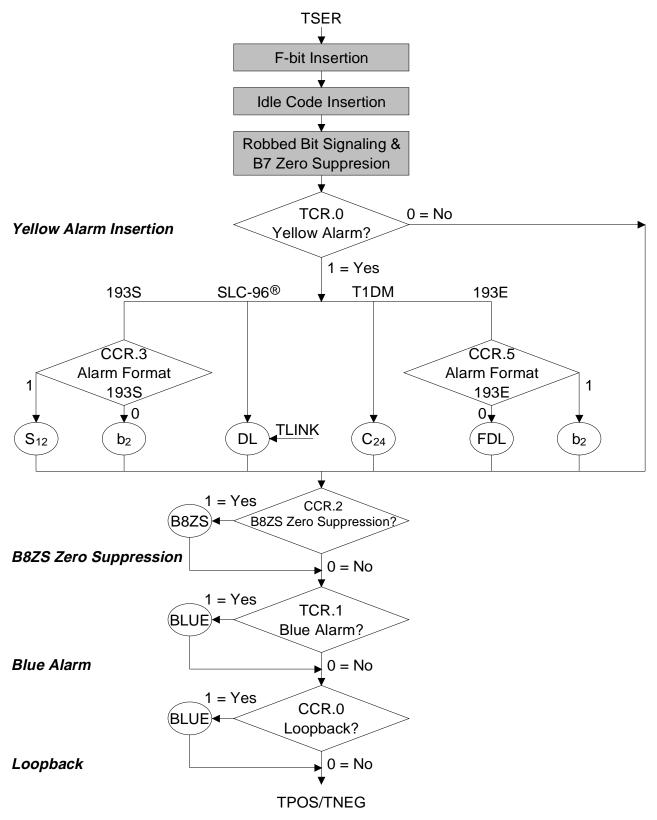

## Transmission Insertion Hierarchy

Figures 13a - 13c give an overview of the decision hierarchy which determines the final composition of the output stream. It shows the various control options as inputs into decision branches of the flow chart, and the order in which the various optional signals are muxed into the final data stream.

Figure 13a. Transmit Insertion Hierarchy: Framing Bits

Figure 13b. Transmit Insertion Hierarchy: Idle Codes, Signaling, and B7

Figure 13c. Transmit Insertion Hierarchy: Alarms, B8ZS, and Loopback

# RECEIVER

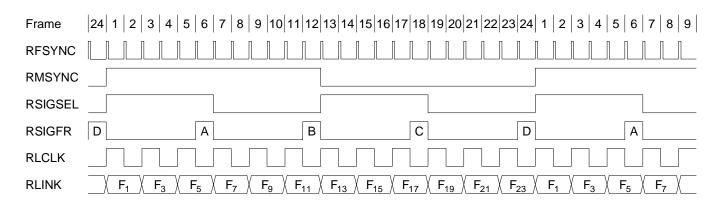

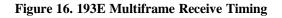

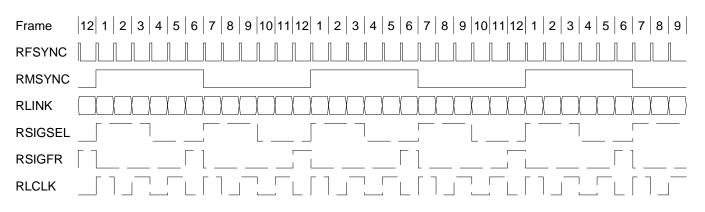

The receive sides of the CS62180A and CS62180B have only three inputs: the clock (RCLK), the incoming signal (RPOS/RNEG), and a reset pin (RST). The receiver determines the framing synchronization of the incoming data, and outputs the timing information on the six timing clocks: RLCLK, RCHCLK, RFSYNC, RMSYNC, RSIGFR, and RSIGSEL. Alarms and error conditions are recorded in the Receive Status Register, and output in real time on the five status pins: RYEL, RCL, RBV, RFER, and RLOS. The decoded data is separated into it's component channel, link, and signaling components and output on RSER, RLINK, and RABCD respectively.

When in host mode, the Receive Control Register allows control of the sync algorithm, and insertion of idle or digital milliwatt ( $\mu$ -LAW) codes into individual DS0 channels. The internal error counters can be accessed, and the Interrupt Mask Register can be programmed to specify the conditions under which a hardware interrupt is generated on INT. When running in hardware mode, receiver status can still be monitored on the status pins; and access to the error counters, sync algorithm, interrupt mask, and the insertion of idle codes are disabled.

# Input Data

The receiver accepts the incoming T1 stream via RPOS/RNEG in dual-unipolar format. Tying RPOS/RNEG together disables the bipolar violation alarm and allows reception of data in NRZ format. Input data is sampled on the falling edge of RCLK. Delay from input at RPOS/RNEG to output on RSER is 13 RCLK periods.

# Output Data

The receiver will attempt to sync and decode the framing format selected via CCR.4 and CCR.7. The decoded T1 stream is output in NRZ format on RSER, and updated every RCLK period. Output

data is latched on the rising edge of RCLK, and held until the next update.

Link and signaling data is always output on RLINK and RABCD respectively, independent of the transmitter configuration. RABCD outputs the LSB of every DSO channel word, whether it is currently a signaling frame or not. The data is updated on the channel boundary, concurrent with the MSB, and held until the next update (8 or 9 bits). RLINK outputs either S-bit, SLC-96<sup>®</sup> DL or FDL bits, depending on the framing format. Data is updated 1 bit period prior to the Fs or FDL frame and held until the next update (2 frames).

# **Output Clocks**

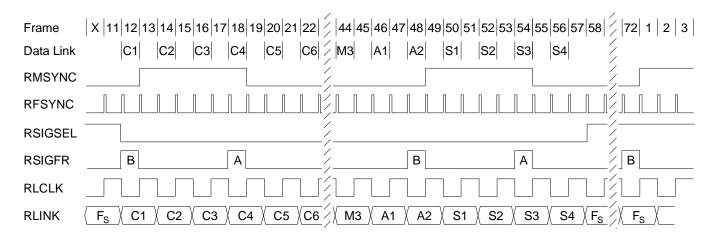

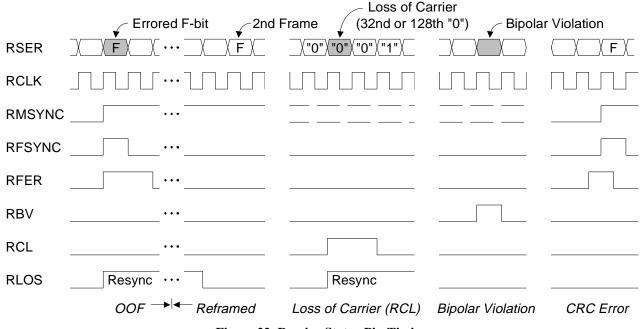

Several timing clocks are provided for identifying this data. The timing clocks are RLCLK, RCHCLK, RFSYNC, RMSYNC, RSIGFR, and RSIGSEL. Logical combination of these six signals allows easy extraction of any part of the received data stream. RMSYNC runs on a 50% duty cycle, and transitions high at the start of each new superframe output on RSER. RFSYNC transitions high at the start of every new frame. Individual DS0 channels are identified by RCHCLK, which runs on a 50% duty cycle and transitions high at the MSB of every individual time slot. Bit level timing is shown in Figure 14.

# **193S Timing**

Link data can be identified by RLCLK, which goes high for all odd numbered frames. RSIGFR is high for signaling frames, and low at all other times. RSIGSEL runs at twice the frequency of RMSYNC. Logical combination of RMSYNC and RSIGSEL provides a way to distinguish the 6<sup>th</sup> and 12<sup>th</sup> frames for external multiplexing of signaling channels. RMSYNC is high for those frames containing A signaling bits, and low for frames containing B bits. Refer to Figure 15 for a timing diagram.

| RCLK              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |                |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|

| RPOS,<br>RNEG     | $ \begin{array}{c c} & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & $ | 8 \ 1 \ 2 \ 3 \ 4 \ 5              | 6 7 8 1 2 3 4  |

| RFSYNC            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |                |

| RMSYNC,           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |                |

| RSIGSEL,<br>RLCLK |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |                |

| RSIGFR            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |                |

| KOIGEK            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |                |

| RCHCLK            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |                |

| RSER              | $\begin{array}{c c} \hline & 3 \\ \hline & 4 \\ \hline & 5 \\ \hline & 6 \\ \hline & 7 \\ \hline & D_{23} \\ \hline & 1 \\ \hline & 2 \\ \hline & 3 \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $4 \ 1 \ 5 \ 6 \ 7 \ D_{24} \ F_1$ | 1 2 3 4 5 6 7  |