# 3.3V, 32 Mbit (1024 Kbit x 32) TIMEKEEPER® SRAM

## **FEATURES SUMMARY**

- 3.3V ± 10%

- INTEGRATED ULTRA LOW POWER SRAM, REAL TIME CLOCK, POWER-FAIL CONTROL CIRCUIT, BATTERY, AND CRYSTAL

- PRECISION POWER MONITORING and POWER SWITCHING CIRCUITRY

- AUTOMATIC WRITE-PROTECTION WHEN V<sub>CC</sub> IS OUT-OF-TOLERANCE

- POWER-FAIL DESELECT VOLTAGE:

- $V_{CC} = 3.0 \text{ to } 3.6 \text{V}; 2.8 \text{V} \le V_{PFD} \le 2.97 \text{V}$

- BATTERY LOW PIN (BL)

- DUAL BATTERY SNAPHAT® HOUSING IS REPLACEABLE

- 85ns SRAM CHIP ENABLE ACCESS (70ns ADDRESS ACCESS)

- SLEEP MODE FUNCTION

- 150ns CLOCK ACCESS

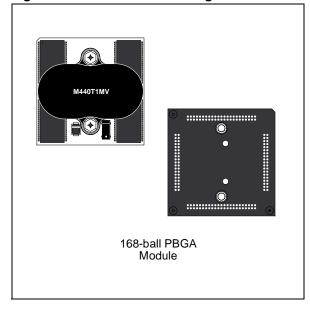

Figure 1. 168-ball PBGA Package

April 2003 1/27

## **TABLE OF CONTENTS**

| SUMMARY DESCRIPTION                                                                | 4  |

|------------------------------------------------------------------------------------|----|

| Figure 2. Logic Diagram                                                            |    |

| Figure 3. PBGA Connections (Top View)                                              |    |

| Figure 4. M440T1MV Hardware Hookup                                                 |    |

| Figure 5. M440T1MV PBGA Module Solution (Side/Top)                                 |    |

|                                                                                    |    |

| MAXIMUM RATINGS                                                                    | 7  |

| Table 2. Absolute Maximum Ratings                                                  | 7  |

| DC AND AC PARAMETERS                                                               | 8  |

| Table 3. DC and AC Measurement Conditions                                          | 8  |

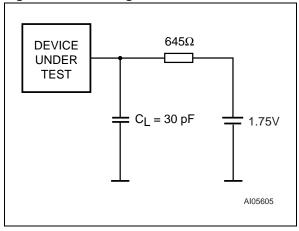

| Figure 6. AC Testing Load Circuit                                                  | 8  |

| Table 4. Capacitance                                                               |    |

| Table 5. DC Characteristics                                                        | 9  |

| OPERATION MODES                                                                    | 40 |

|                                                                                    |    |

| Memory READ Mode                                                                   | 10 |

| Clock READ Mode                                                                    | 10 |

| Table 6. Memory Operating Modes                                                    | 11 |

| Table 7. Clock Operating Modes                                                     |    |

| Figure 7. Memory READ Mode AC Waveforms, Chip Enable- or Output Enable-Controlled. |    |

| Figure 8. Memory READ Mode AC Waveforms, Address-Controlled                        |    |

| Figure 9. Clock READ Mode AC Waveforms, Chip Enable- or Output Enable-Controlled   |    |

| Figure 10. Clock READ Mode AC Waveforms, Address-Controlled                        |    |

| Table 8. Memory/Clock READ Mode AC Characteristics                                 |    |

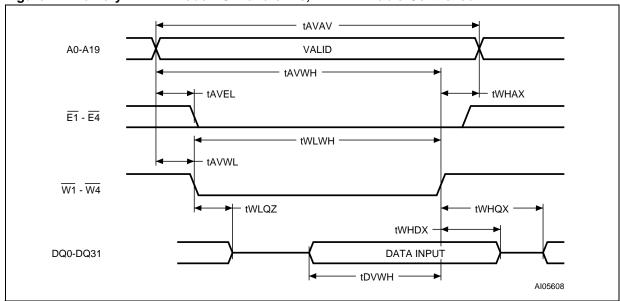

| Memory WRITE Mode                                                                  | 14 |

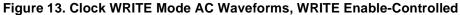

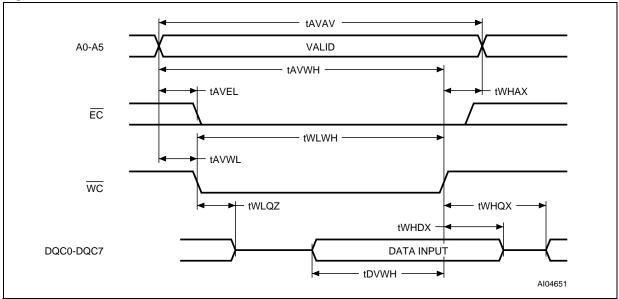

| Clock WRITE Mode                                                                   | 14 |

| Figure 11. Memory WRITE Mode AC Waveforms, WRITE Enable-Controlled                 | 14 |

| Figure 12. Memory WRITE Mode AC Waveforms, Chip Enable-Controlled                  |    |

| Figure 13. Clock WRITE Mode AC Waveforms, WRITE Enable-Controlled                  |    |

| Figure 14. Clock WRITE Mode AC Waveforms, Chip Enable-Controlled                   |    |

| Table 9. Memory/Clock WRITE Mode AC Characteristics                                | 16 |

| Data Retention Mode                                                                | 17 |

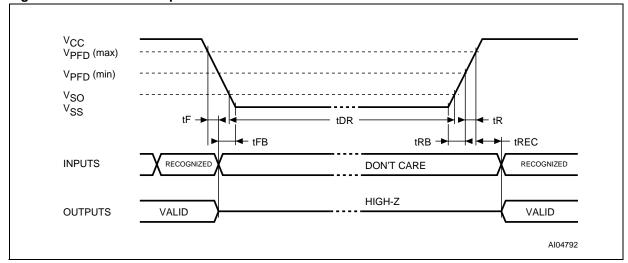

| Figure 15. Power Down/Up Mode AC Waveforms                                         | 17 |

| Table 10. Power Down/Up Trip Points DC Characteristics                             | 17 |

| Table 11. Power Down/Up AC Characteristics                                         | 18 |

| CLOCK OPERATION                                                                    | 18 |

| Clock Registers                                                                    | 18 |

| Reading and Setting the Clock                                                      | 18 |

|    | Clock Alarm Registers         | . 19 |

|----|-------------------------------|------|

|    | Watchdog Alarm Registers.     | . 20 |

|    | Command Register              | . 21 |

|    | Battery Low                   | . 22 |

|    | Sleep Mode                    | . 22 |

| PΑ | ACKAGE MECHANICAL INFORMATION | . 23 |

| PΑ | ART NUMBERING                 | . 25 |

| DE | EVISION HISTORY               | 26   |

## SUMMARY DESCRIPTION

The M440T1MV TIMEKEEPER® RAM is a 16Mbit, non-volatile static RAM organized as 1,024K by 32 bits and real time clock organized as 64 bytes by 8 bits. The special PBGA package provides a fully integrated battery back-up memory and real time clock solution. In the event of power instability or absence, a self-contained battery maintains the timekeeping operation and provides power for a CMOS static RAM. Control circuitry monitors  $V_{CC}$  and invokes write protection to prevent data corruption in the memory and RTC.

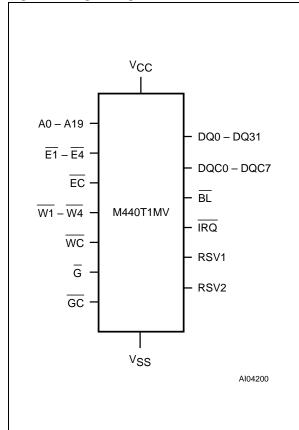

Figure 2. Logic Diagram

The clock keeps track of tenths/hundredths of seconds, seconds, minutes, hours, day, date, month, and year information. The last day of the month is automatically adjusted for months with less than 31 days, including leap year correction.

The clock operates in one of two formats:

- a 12-hour mode with an AM/PM indicator; or

- a 24-hour mode

The M440T1MV is in a 168-ball PBGA module that integrates the RTC, the battery, and SRAM in one package.

**Table 1. Signal Names**

| A0 - A19        | Address Inputs                  |

|-----------------|---------------------------------|

| DQ0 - DQ31      | NVRAM Data Input/Output         |

| DQC0 - DQC7     | Clock Data Input/Output         |

| E1 - E4         | NVRAM Chip Enable Inputs        |

| EC              | Clock Chip Enable Input         |

| W1 - W4         | NVRAM WRITE Enable Inputs       |

| WC              | Clock WRITE Enable Input        |

| G               | Output Enable Input             |

| GC              | Clock Output Enable Input       |

| BL              | Battery Low Output (Open Drain) |

| ĪRQ             | Interrupt Output (Open Drain)   |

| RSV1            | Reserved                        |

| RSV2            | Reserved                        |

| NC              | No Connect                      |

| V <sub>CC</sub> | Supply Voltage                  |

| V <sub>SS</sub> | Ground                          |

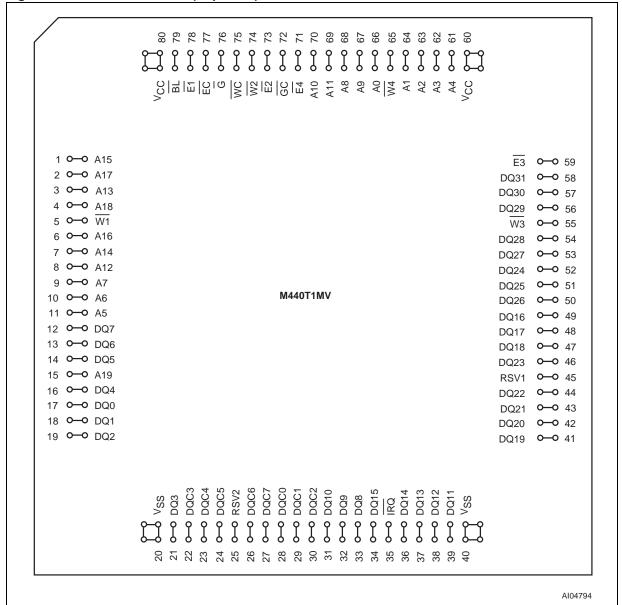

Figure 3. PBGA Connections (Top View)

Note: This diagram is TOP VIEW perspective (view through package).

∮8kΩ

VOUTA -

Figure 4. M440T1MV Hardware Hookup A0-A19 M48T224W 3.3V VOUTA Vcc VCC1M x 8 1M x 8 SRAM SRAM A0-A5  $\overline{\text{E1}}_{\text{CON}}$ Ġ  $\overline{\mathsf{W}}$ ā E2<sub>CON</sub> G  $\overline{\mathsf{G}}$  $\overline{\text{W1}}$ W2 EC -Ē DQ0 - DQ7 DQC0 - DQC7  $\overline{\mathsf{WC}}$  $\overline{\mathsf{W}}$ ĪRQ INTB/INTB DQ16-DQ23 GC -G <u>E1</u> -<u>=</u>1 - BL BL E2 <u>E2</u> <del>-</del> E3 -<del>-</del>3  $V_{\mathsf{OUTB}}$ <del>-</del> E4 -<u>=</u>4 Vcc  $^{VCC}$ SLEEP PAD SLEEP

E3<sub>CON</sub>

Ē4<sub>CON</sub>

THS

Vss

1M x 8

SRAM

G

$\overline{\mathsf{W}}$

G W3

1M x 8

SRAM

Ē  $\overline{\mathsf{W}}$

G W4

AI04795

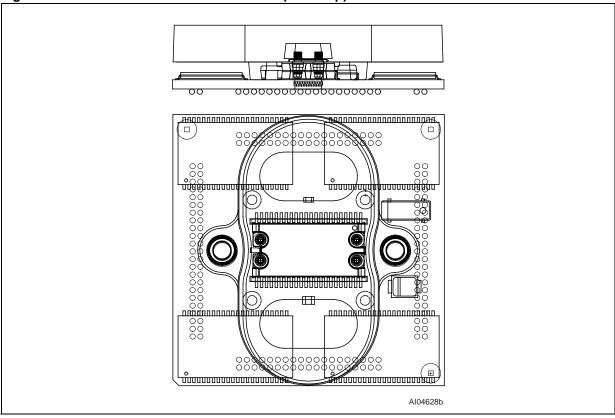

Figure 5. M440T1MV PBGA Module Solution (Side/Top)

## **MAXIMUM RATINGS**

Stressing the device above the rating listed in the "Absolute Maximum Ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is

not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

**Table 2. Absolute Maximum Ratings**

| Symbol           | Parameter                                              | Value                         | Unit |

|------------------|--------------------------------------------------------|-------------------------------|------|

| T <sub>A</sub>   | Operating Temperature                                  | -15 to 75                     | °C   |

| T <sub>STG</sub> | Storage Temperature (V <sub>CC</sub> , Oscillator Off) | -40 to 85                     | °C   |

| T <sub>SLD</sub> | Lead Solder Temperature for 10 seconds                 | 260                           | °C   |

| Vcc              | Supply Voltage (on any pin relative to Ground)         | -0.3 to + 4.6                 | V    |

| V <sub>IO</sub>  | Input or Output Voltages                               | -0.3 to V <sub>CC</sub> + 0.3 | V    |

| Io               | Output Current                                         | 20                            | mA   |

| P <sub>D</sub>   | Power Dissipation                                      | 1                             | W    |

CAUTION! Negative undershoots below -0.3V are not allowed on any pin while in the Battery Back-up Mode

#### DC AND AC PARAMETERS

This section summarizes the operating and measurement conditions, as well as the DC and AC characteristics of the device. The parameters in the following DC and AC Characteristic tables are derived from tests performed under the Measure-

ment Conditions listed in the relevant tables. Designers should check that the operating conditions in their projects match the measurement conditions when using the quoted parameters.

**Table 3. DC and AC Measurement Conditions**

| Parameter                             | M440T1MV    |

|---------------------------------------|-------------|

| V <sub>CC</sub> Supply Voltage        | 3.0 to 3.6V |

| Ambient Operating Temperature         | –15 to 75°C |

| Load Capacitance (C <sub>L</sub> )    | 30pF        |

| Input Rise and Fall Times             | ≤5ns        |

| Input Pulse Voltages                  | 0 to 3V     |

| Input and Output Timing Ref. Voltages | 1.5V        |

Note: Output Hi-Z is defined as the point where data is no longer driven.

Figure 6. AC Testing Load Circuit

**Table 4. Capacitance**

| Symbol                          | Parameter <sup>(1,2)</sup> | M440                   | Unit |    |    |

|---------------------------------|----------------------------|------------------------|------|----|----|

| Syllibol                        | Parameter/                 | Min                    | Max  |    |    |

|                                 | Input Capacitance          | A0 - A5                |      | 50 | pF |

| C <sub>IN</sub>                 |                            | A6 - A19, <del>G</del> |      | 40 | pF |

|                                 |                            | All Other Inputs       |      | 10 | pF |

| C <sub>OUT</sub> <sup>(3)</sup> | Output Capacitance (BL)    |                        |      | 10 | pF |

| C <sub>IO</sub> (3)             | Input / Output Capacitance |                        |      | 10 | pF |

Note: 1. Effective capacitance measured with power supply at 3V; sampled only; not 100% tested.

- 2. At 25°C, f = 1MHz.

- 3. Outputs were deselected.

**Table 5. DC Characteristics**

| Cum                             | Dovometer                            | T (0 (1)                                                              |      | M440T1MV |                       |      |  |  |

|---------------------------------|--------------------------------------|-----------------------------------------------------------------------|------|----------|-----------------------|------|--|--|

| Sym                             | Parameter                            | Test Condition <sup>(1)</sup>                                         | Min  | Тур      | Max                   | Unit |  |  |

| ILI                             | Input Leakage Current                | $0V \leq V_{IN} \leq V_{CC}$                                          |      |          | ±4                    | μA   |  |  |

| I <sub>LO</sub>                 | Output Leakage Current               | $0V \le V_{OUT} \le V_{CC}$                                           |      |          | ±4                    | μA   |  |  |

| Icc1                            | Supply Current                       |                                                                       |      |          | 210                   | mA   |  |  |

| I <sub>CC2</sub>                | Supply Current (TTL Standby)         | $\overline{E1}$ - $\overline{E4}$ , $\overline{EC} = V_{IH}$          |      | 5        | 12                    | mA   |  |  |

| I <sub>CC3</sub>                | V <sub>CC</sub> Power Supply Current | $\frac{\overline{E1} - \overline{E4}}{\overline{EC} = V_{CCI} - 0.2}$ |      | 2        | 3                     | mA   |  |  |

| V <sub>IL</sub> <sup>(2)</sup>  | Input Low Voltage                    |                                                                       | -0.3 |          | 0.6                   | V    |  |  |

| V <sub>IH</sub> <sup>(2)</sup>  | Input High Voltage                   |                                                                       | 2.2  |          | V <sub>CC</sub> + 0.3 | V    |  |  |

| V                               | Output Low Voltage                   | I <sub>OL</sub> = 2.0mA                                               |      |          | 0.4                   | V    |  |  |

| V <sub>OL</sub>                 | Output Low Voltage (Open drain)(3)   | I <sub>OL</sub> = 10mA                                                |      |          | 0.4                   | V    |  |  |

| V <sub>OH</sub>                 | Output High Voltage                  | $I_{OH} = -1.0$ mA                                                    | 2.2  |          |                       | V    |  |  |

| V <sub>PFD</sub> <sup>(2)</sup> | Power Fail Deselect                  |                                                                       | 2.80 |          | 2.97                  | V    |  |  |

| V <sub>SO</sub> <sup>(2)</sup>  | Battery Back-up Switchover           |                                                                       |      | 2.5      |                       | V    |  |  |

Note: 1. Valid for Ambient Operating Temperature:  $T_A = -15$  to  $75^{\circ}C$ ;  $V_{CC} = 3.0$  to 3.6V (except where noted).

<sup>2.</sup> All voltages are referenced to Ground.

<sup>3.</sup> For BL and IRQ (Open drain); if pulled-up to supply other than V<sub>CC</sub>, this supply must be equal to, or less than 3.0V when V<sub>CC</sub> = 0V (during battery back-up mode).

# **OPERATION MODES Memory READ Mode**

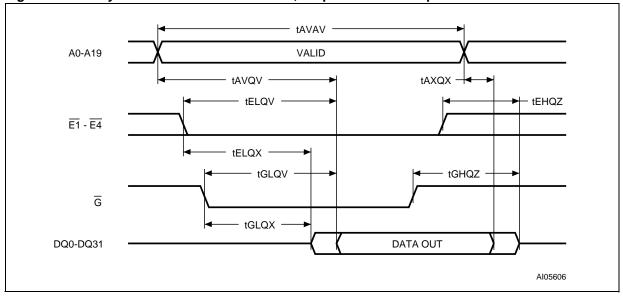

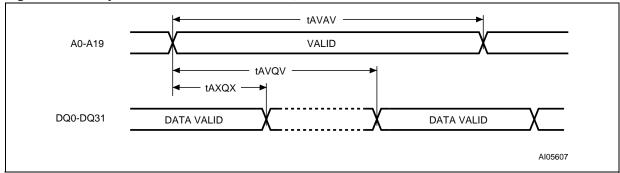

The  $\underline{\text{M440}\underline{\text{T1}}\text{MV}}$  is in the 32-bit READ Mode whenever  $\underline{\text{W1}}$  -  $\underline{\text{W4}}$  (WRITE Enable Byte 1 to 4) are high and  $\overline{\text{E1}}$  -  $\overline{\text{E4}}$  - Chip Enable Bytes 1 to 4 are low (see Table 6, page 11). The unique address specified by the 20 address inputs defines which one of the 1,048,576 long words of data is to be accessed. Valid data will be available at the Data I/O pins within Address Access Time ( $t_{\text{AVQV}}$ ) after the last address input signal is stable, providing the  $\underline{\text{E1-4}}$  and  $\underline{\text{G}}$  access times are also satisfied. If the  $\overline{\text{E1-4}}$  and  $\underline{\text{G}}$  access times are not met, valid data will be available after the latter of the Chip Enable Access Times ( $t_{\text{ELQV}}$ ) or Output Enable Access Time ( $t_{\text{GLQV}}$ ).

The state of the thirty-two three-state Data I/O signals is controlled by E1-4 and G. If the outputs are activated before  $t_{AVQV}$ , the data lines will be driven to an indeterminate state until  $t_{AVQV}$ . If the Address Inputs are changed while E1-4 and G remain active, output data will remain valid for Output Data Hold Time ( $t_{AXQX}$ ) but will go indeterminate until the next Address Access.

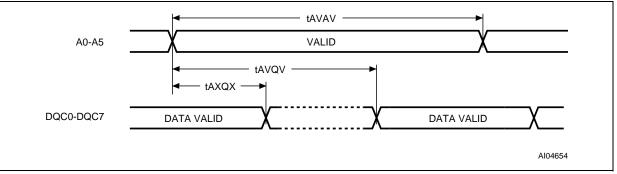

#### **Clock READ Mode**

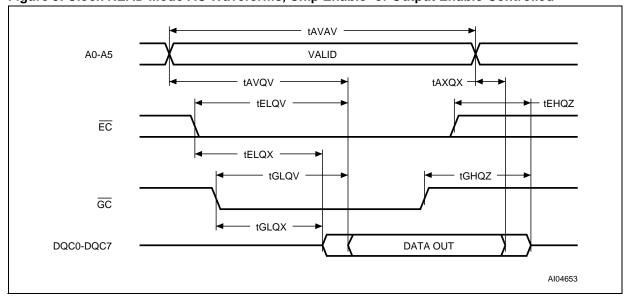

The clock is in the READ Mode whenever WC (Clock WRITE Enable) is high and  $\overline{EC}$  (Clock Chip Enable) is low. The unique address specified by the 6 Address Inputs defines which one of the 64 bytes of clock data is to be accessed. Valid data will be available at the Data I/O pins (DQC0-7) within Address Access Time ( $t_{AVQV}$ ) after the last address input signal is stable, providing the  $\overline{EC}$  and  $\overline{GC}$  access times are also satisfied. If the EC and  $\overline{GC}$  access times are not met, valid data will be available after the latter of the Chip Enable Access Times ( $t_{ELQV}$ ) or Output Enable Access Time ( $t_{GLQV}$ ).

The state of the <u>eig</u>ht three-state Data I/O signals is controlled by EC and G. If the outputs are activated before  $t_{AVQV}$ , the data lines will be driven to an indeterminate state until  $t_{AVQV}$ . If the Address Inputs are changed while EC and G remain active, output data will remain valid for Output Data Hold Time ( $t_{AXQX}$ ) but will go indeterminate until the next Address Access. See section on Reading and Setting the Clock under CLOCK OPERATION for more details.

**Table 6. Memory Operating Modes**

| Mode               | V <sub>CC</sub>                                             | E4 | E3 | E2 | E1 | G | W4 | W3 | W2 | W1 | DQ24-<br>DQ31    | DQ16-<br>DQ23    | DQ8-<br>DQ15     | DQ0-<br>DQ7      | Power                      |

|--------------------|-------------------------------------------------------------|----|----|----|----|---|----|----|----|----|------------------|------------------|------------------|------------------|----------------------------|

| Byte WRITE         |                                                             | Н  | Н  | Н  | L  | Н | Х  | Х  | Х  | L  | Hi-Z             | Hi-Z             | Hi-Z             | D <sub>IN</sub>  | Active                     |

| Byte WRITE         |                                                             | Н  | Н  | L  | Н  | Н | Х  | Х  | L  | Х  | Hi-Z             | Hi-Z             | D <sub>IN</sub>  | Hi-Z             | Active                     |

| Byte WRITE         |                                                             | Н  | L  | Н  | Н  | Н | Х  | L  | Х  | Х  | Hi-Z             | D <sub>IN</sub>  | Hi-Z             | Hi-Z             | Active                     |

| Byte WRITE         |                                                             | L  | Н  | Н  | Н  | Н | L  | Х  | Х  | Х  | D <sub>IN</sub>  | Hi-Z             | Hi-Z             | Hi-Z             | Active                     |

| Byte WRITE         |                                                             | Х  | Х  | Х  | L  | Н | Н  | Н  | Н  | L  | Hi-Z             | Hi-Z             | Hi-Z             | D <sub>IN</sub>  | Active                     |

| Byte WRITE         |                                                             | Х  | Х  | L  | Х  | Н | Н  | Н  | L  | Н  | Hi-Z             | Hi-Z             | D <sub>IN</sub>  | Hi-Z             | Active                     |

| Byte WRITE         |                                                             | Χ  | L  | Χ  | Χ  | Н | Н  | L  | Н  | Н  | Hi-Z             | D <sub>IN</sub>  | Hi-Z             | Hi-Z             | Active                     |

| Byte WRITE         | 2.97 to 3.6V                                                | L  | Х  | Х  | Х  | Н | L  | Н  | Н  | Н  | D <sub>IN</sub>  | Hi-Z             | Hi-Z             | Hi-Z             | Active                     |

| Long Word<br>WRITE | 2.97 10 3.00                                                | L  | L  | L  | L  | Н | L  | L  | L  | L  | D <sub>IN</sub>  | D <sub>IN</sub>  | D <sub>IN</sub>  | D <sub>IN</sub>  | Active                     |

| Byte READ          |                                                             | Н  | Н  | Н  | L  | L | Х  | Х  | Х  | Н  | Hi-Z             | Hi-Z             | Hi-Z             | D <sub>OUT</sub> | Active                     |

| Byte READ          |                                                             | Н  | Н  | L  | Н  | L | Х  | Х  | Н  | Х  | Hi-Z             | Hi-Z             | D <sub>OUT</sub> | Hi-Z             | Active                     |

| Byte READ          |                                                             | Н  | L  | Н  | Н  | L | Х  | Н  | Х  | Х  | Hi-Z             | D <sub>OUT</sub> | Hi-Z             | Hi-Z             | Active                     |

| Byte READ          |                                                             | L  | Н  | Н  | Н  | L | Н  | Х  | Х  | Х  | D <sub>OUT</sub> | Hi-Z             | Hi-Z             | Hi-Z             | Active                     |

| Long Word<br>READ  |                                                             | L  | L  | L  | L  | L | Н  | Н  | Н  | Н  | D <sub>OUT</sub> | D <sub>OUT</sub> | D <sub>OUT</sub> | D <sub>OUT</sub> | Active                     |

| Deselect           |                                                             | Н  | Н  | Н  | Н  | Χ | Х  | Х  | Х  | Х  | Hi-Z             | Hi-Z             | Hi-Z             | Hi-Z             | Stdby                      |

| Deselect           | V <sub>SO</sub> to<br>V <sub>PFD</sub> (min) <sup>(1)</sup> | Х  | Х  | Х  | Х  | Х | Х  | Х  | Х  | Х  | Hi-Z             | Hi-Z             | Hi-Z             | Hi-Z             | CMOS<br>Standby            |

| Deselect           | ≤ V <sub>SO</sub> <sup>(1)</sup>                            | Х  | Х  | Х  | Х  | Х | Х  | Х  | Х  | Х  | Hi-Z             | Hi-Z             | Hi-Z             | Hi-Z             | Battery<br>Back-up<br>Mode |

Note:  $X = V_{IH}$  or  $V_{IL}$ ;  $V_{SO}$  = Battery Back-up Switchover Voltage. 1. See Table 10, page 17 for details.

Table 7. Clock Operating Modes

| able 7. Glock Operating modes |                                                             |                 |                 |                 |                 |  |  |  |  |

|-------------------------------|-------------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|--|--|--|--|

| Mode                          | V <sub>CC</sub>                                             | EC              | GC              | WC              | DQC0 - 7        |  |  |  |  |

| Deselect                      |                                                             | V <sub>IH</sub> | Х               | Х               | Hi-Z            |  |  |  |  |

| WRITE                         | 2.97 to 3.6V                                                | V <sub>IL</sub> | Х               | V <sub>IL</sub> | D <sub>IN</sub> |  |  |  |  |

| READ                          | 2.97 10 3.60                                                | VIL             | V <sub>IL</sub> | V <sub>IH</sub> | Dout            |  |  |  |  |

| READ                          |                                                             | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Hi-Z            |  |  |  |  |

| Deselect                      | V <sub>SO</sub> to<br>V <sub>PFD</sub> (min) <sup>(1)</sup> | Х               | Х               | ×               | Hi-Z            |  |  |  |  |

| Deselect                      | ≤ V <sub>SO</sub> <sup>(1)</sup>                            | Х               | Х               | Х               | Hi-Z            |  |  |  |  |

Note:  $X = V_{IH}$  or  $V_{IL}$ ;  $V_{SO}$  = Battery Back-up Switchover Voltage. 1. See Table 10, page 17 for details.

Figure 7. Memory READ Mode AC Waveforms, Chip Enable- or Output Enable-Controlled

Figure 8. Memory READ Mode AC Waveforms, Address-Controlled

Figure 9. Clock READ Mode AC Waveforms, Chip Enable- or Output Enable-Controlled

Figure 10. Clock READ Mode AC Waveforms, Address-Controlled

Table 8. Memory/Clock READ Mode AC Characteristics

| Symbol           |                                  |                                         |     |      |       |     |      |

|------------------|----------------------------------|-----------------------------------------|-----|------|-------|-----|------|

|                  |                                  | - (1)                                   | Men | nory | Clock |     | Unit |

| 3                | /IIIDOI                          | Parameter <sup>(1)</sup>                | -8  | 35   | -15   |     | Unit |

|                  |                                  |                                         | Min | Max  | Min   | Max |      |

| t <sub>RC</sub>  | t <sub>AVAV</sub>                | READ Cycle Time                         | 85  |      | 150   |     | ns   |

| t <sub>ACC</sub> | t <sub>AVQV</sub>                | Address Valid to Output Valid           |     | 70   |       | 150 | ns   |

| tco              | t <sub>ELQV</sub>                | Chip Enable Low to Output Valid         |     | 85   |       | 150 | ns   |

| toE              | t <sub>GLQV</sub>                | Output Enable Low to Output Valid       |     | 45   |       | 70  | ns   |

| t <sub>CEL</sub> | t <sub>ELQX</sub>                | Chip Enable Low to Output Transition    | 5   |      | 10    |     | ns   |

| t <sub>OEL</sub> | t <sub>GLQX</sub>                | Output Enable Low to Output Transition  | 5   |      | 5     |     | ns   |

| t <sub>CEZ</sub> | t <sub>EHQZ</sub> (2)            | Chip Enable High to Output Hi-Z         |     | 40   |       | 50  | ns   |

| toez             | t <sub>GHQZ</sub> <sup>(2)</sup> | Output Enable High to Output Hi-Z       |     | 30   |       | 50  | ns   |

| toH              | t <sub>AXQX</sub>                | Address Transition to Output Transition | 5   |      | 5     |     | ns   |

Note: 1. Valid for Ambient Operating Temperature:  $T_A = -15$  to  $75^{\circ}C$ ;  $V_{CC} = 3.0$  to 3.6V (except where noted).

<sup>2.</sup>  $C_L = 5pF$ .

#### **Memory WRITE Mode**

The M440T1MV is in the WRITE Mode whenever any or all of W1-4 (WRITE Enable Byte 1 to 4) and any corresponding E1-4 (Chip Enable Byte 1 to 4) are in a low state after the address inputs are stable. Thus a Byte WRITE (8-bit), Word WRITE (16bit) or Long Word WRITE (32-bit) may be performed. The start of a WRITE is referenced from the latter occurring falling edge of W1-4 or E1-4. A WRITE is terminated by the earlier rising edge of W1-4 or E1-4. The addresses must be held valid throughout the cycle. E1-4 or W1-4 must return high for a minimum of t<sub>FHAX</sub> from Chip Enable or t<sub>WHAX</sub> from WRITE Enable prior to the initiation of another READ or WRITE cycle. Data-in must be valid t<sub>DVWH</sub> prior to the end of WRITE and remain valid for t<sub>WHDX</sub> afterward. G should be kept high during WRITE cycles to avoid bus contention; although, if the output bus has been activated by a low on E1-4 and G, a low on W1-4 will disable the outputs t<sub>WI OZ</sub> after W1-4 falls.

#### **Clock WRITE Mode**

The clock is in the WRITE Mode whenever WC (Clock WRITE Enable) and EC (Clock Chip Enable) are in the low state after the address inputs are stable. The start of a WRITE is referenced from the latter occurring falling edge of WC or EC. A WRITE is terminated by the earlier rising edge of WC or EC. The addresses must be held valid throughout the cycle. EC or WC must return high for a minimum of t<sub>EHAX</sub> from Chip Enable Clock or tWHAX from WRITE Enable Clock prior to the initiation of another READ or WRITE cycle. Data-in must be valid t<sub>DVWH</sub> prior to the end of WRITE and remain valid for t<sub>WHDX</sub> afterward. GC should be kept high during WRITE cycles to avoid bus contention; although, if the output bus has been activated by a low on EC and GC a low on WC will disable the outputs  $t_{WLQZ}$  after  $\overline{WC}$  falls. See section on Reading and Setting the Clock under CLOCK OPERATION for more details.

Figure 11. Memory WRITE Mode AC Waveforms, WRITE Enable-Controlled

Note: Output Enable  $(\overline{G})$  = Low

AI05609

→ tWHDX →

DATA INPUT

- tDVWH -

tAVAV A0-A19 VALID - tAVEH -**►** tEHAX - tAVEL → - tELEH E1 - E4 - tAVWL <del>W1</del> - <del>W4</del>

Figure 12. Memory WRITE Mode AC Waveforms, Chip Enable-Controlled

Note: Output Enable  $(\overline{G})$  = High

DQ0-DQ31

Note: Clock Output Enable  $(\overline{GC})$  = Low

tAVAV A0-A5 **VALID** tAVEH tELEH tEHAX - tAVEL -EC tAVWL WC - tWHDX -DQC0-DQC7 DATA INPUT tDVWH -AI04652

Figure 14. Clock WRITE Mode AC Waveforms, Chip Enable-Controlled

Note: Clock Output Enable  $(\overline{GC})$  = High

Table 9. Memory/Clock WRITE Mode AC Characteristics

|                  |                         |                                         |     | M440T1MV |     |      |    |  |

|------------------|-------------------------|-----------------------------------------|-----|----------|-----|------|----|--|

|                  | vmbol                   | - (1)                                   | Men | nory     | Clo | Unit |    |  |

| 3                | ymbol                   | Parameter <sup>(1)</sup>                | -8  | 35       | -15 |      |    |  |

|                  |                         |                                         | Min | Max      | Min | Max  |    |  |

| twc              | t <sub>AVAV</sub>       | WRITE Cycle Time                        | 85  |          | 150 |      | ns |  |

| t <sub>AW</sub>  | t <sub>AVWL</sub>       | Address Valid to WRITE Enable Low       | 0   |          | 0   |      | ns |  |

| LAVV .           | t <sub>AVEL</sub>       | Address Valid to Chip Enable Low        | 0   |          | 0   |      | ns |  |

| t <sub>WP</sub>  | t <sub>WLWH</sub>       | WRITE Enable Pulse Width                | 60  |          | 100 |      | ns |  |

| t <sub>CEW</sub> | t <sub>ELEH</sub>       | Chip Enable Low to Chip Enable High     | 65  |          | 150 |      | ns |  |

| turn             | twhax                   | WRITE Enable High to Address Transition | 0   |          | 10  |      | ns |  |

| twR              | t <sub>EHAX</sub>       | Chip Enable High to Address Transition  | 15  |          | 10  |      | ns |  |

| tno              | t <sub>DVWH</sub>       | Input Valid to WRITE Enable High        | 35  |          | 50  |      | ns |  |

| t <sub>DS</sub>  | t <sub>DVEH</sub>       | Input Valid to Chip Enable High         | 35  |          | 50  |      | ns |  |

| <b>+</b>         | t <sub>WHDX</sub>       | WRITE Enable High to Input Transition   | 0   |          | 0   |      | ns |  |

| t <sub>DH</sub>  | t <sub>EHDX</sub>       | Chip Enable High to Input Transition    | 15  |          | 0   |      | ns |  |

| t <sub>WEZ</sub> | t <sub>WLQZ</sub> (2,3) | WRITE Enable Low to Output Hi-Z         |     | 30       |     | 50   | ns |  |

|                  | t <sub>AVWH</sub>       | Address Valid to WRITE Enable High      | 70  |          | 150 |      | ns |  |

|                  | t <sub>AVEH</sub>       | Address Valid to Chip Enable High       | 70  |          | 150 |      | ns |  |

| t <sub>OEW</sub> | t <sub>WHQX</sub> (3)   | WRITE Enable High to Output Transition  | 5   |          | 5   |      | ns |  |

Note: 1. Valid for Ambient Operating Temperature:  $T_A = -15$  to  $75^{\circ}C$ ;  $V_{CC} = 3.0$  to 3.6V (except where noted).

<sup>2.</sup>  $C_L = 5pF$ . 3. If  $\overline{E1}$  -  $\overline{E4}$  and  $\overline{EC}$  goes low simultaneously with  $\overline{W1}$  -  $\overline{W4}$  and  $\overline{WC}$  going low, the outputs remain in the high impedance state.

#### **Data Retention Mode**

Should the supply voltage decay, the RAM will automatically deselect, write protecting itself when  $V_{CC}$  falls between  $V_{PFD}$  (max),  $V_{PFD}$  (min) window. All outputs become high impedance and all inputs are treated as "Don't care."

**Note:** A power failure during a WRITE cycle may corrupt data at the current addressed location, but does not jeopardize the rest of the RAM's content. At voltages below  $V_{PFD}$  (min), the memory will be in a write protected state, provided the  $V_{CC}$  fall time is not less than  $t_F$ . The M440T1MV may respond to transient noise spikes on  $V_{CC}$  that cross into the deselect window during the time the device is sampling  $V_{CC}$ .Therefore, decoupling of the

power supply lines is recommended. When  $V_{CC}$  drops below  $V_{SO}$ , the control circuit switches power to the internal battery, preserving data and powering the clock. The internal energy source will maintain data in the M440T1MV for an accumulated period of 5 years at 45°C. As system power rises above  $V_{SO}$ , the battery is disconnected, and the power supply is switched to external  $V_{CC}$ . Write protection continues until  $V_{CC}$  reaches  $V_{PFD}$  (min) plus  $t_{ER}$  (min). Normal RAM operation can resume  $t_{ER}$  after  $V_{CC}$  exceeds  $V_{PFD}$  (max). Refer to Application Note (AN1012) on the ST Web Site for more information on battery life.

Figure 15. Power Down/Up Mode AC Waveforms

Table 10. Power Down/Up Trip Points DC Characteristics

| Symbol                         | Parameter <sup>(1,2)</sup>         |     | Unit |      |       |

|--------------------------------|------------------------------------|-----|------|------|-------|

|                                |                                    | Min | Тур  | Max  | Offic |

| V <sub>PFD</sub>               | Power-fail Deselect Voltage        | 2.8 | 2.9  | 2.97 | V     |

| V <sub>SO</sub>                | Battery Back-up Switchover Voltage |     | 2.5  |      | V     |

| t <sub>DR</sub> <sup>(3)</sup> | Expected Data Retention Time       | 5   |      |      | YEARS |

Note: 1. Valid for Ambient Operating Temperature:  $T_A = -15$  to 75°C;  $V_{CC} = 3.0$  to 3.6V (except where noted).

<sup>2.</sup> All voltages referenced to V<sub>SS</sub>.

<sup>3.</sup> At  $45^{\circ}$ C,  $V_{CC} = 0$ V.

Table 11. Power Down/Up AC Characteristics

| Symbol                         | Parameter <sup>(1)</sup>                                                   | Min | Max | Unit |

|--------------------------------|----------------------------------------------------------------------------|-----|-----|------|

| t <sub>F</sub> <sup>(2)</sup>  | V <sub>PFD</sub> (max) to V <sub>PFD</sub> (min) V <sub>CC</sub> Fall Time | 300 |     | μs   |

| t <sub>FB</sub> <sup>(3)</sup> | V <sub>PFD</sub> (min) to V <sub>SS</sub> V <sub>CC</sub> Fall Time        | 10  |     | μs   |

| t <sub>R</sub>                 | V <sub>PFD</sub> (min) to V <sub>PFD</sub> (max) V <sub>CC</sub> Rise Time | 10  |     | μs   |

| t <sub>RB</sub>                | V <sub>SS</sub> to V <sub>PFD</sub> (min) V <sub>CC</sub> Rise Time        | 1   |     | μs   |

| t <sub>REC</sub>               | Power-up Deselect Time                                                     | 40  | 200 | ms   |

Note: 1. Valid for Ambient Operating Temperature:  $T_A = -15$  to  $75^{\circ}$ C;  $V_{CC} = 3.0$  to 3.6V (except where noted).

- V<sub>PFD</sub> (max) to V<sub>PFD</sub> (min) fall time of less than t<sub>F</sub> may result in deselection/write protection not occurring until 200µs after V<sub>CC</sub> passes V<sub>PFD</sub> (min).

- 3. V<sub>PFD</sub> (min) to V<sub>SS</sub> fall time of less than t<sub>FB</sub> may cause corruption of RAM data.

#### **CLOCK OPERATION**

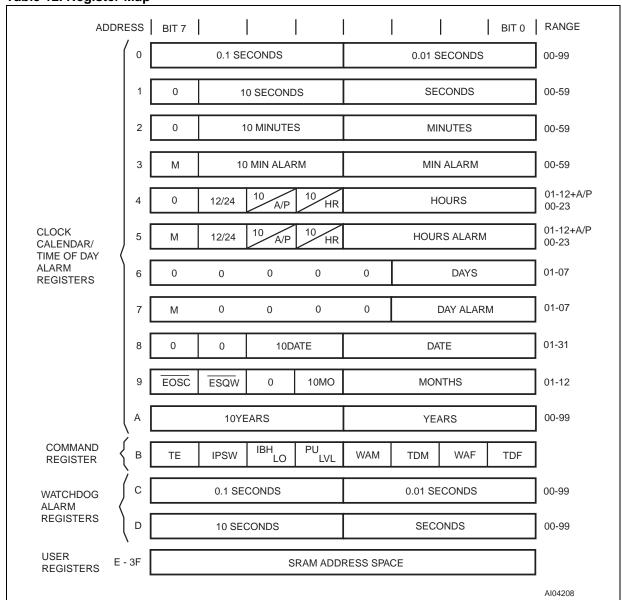

#### **Clock Registers**

Registers 00h, 01h, 02h, 04h, 06h, 08h, 09h, and 0Ah contain the time of day data in BCD. Eleven bits within these eight registers are not used and will always read '0' regardless of how they are written. Bits 6 and 7 in the Months Register (09h) are binary bits. When set to logic '0,' EOSC (Bit 7) enables the Real Time Clock oscillator. This bit will normally be turned on by the user during device initialization. However, the oscillator can be turned on and off as necessary by setting this bit to the appropriate level. Bit 6 of the Hours Register is defined as the 12- or 24-hour select bit. When set to logic '1,' the 12-hour format is selected. In the 12hour format, Bit 5 is the AM/PM bit with logic '1' being PM. In the 24-hour mode, Bit 5 is the second 10-hour bit (20-23 hours). The Clock Registers are updated every 0.01 seconds from the Real Time Clock, except when the TE Bit (Bit 7 of Register 0Bh) is set low or the clock oscillator is not running.

#### Reading and Setting the Clock

The preferred method of synchronizing data access to and from the TIMEKEEPER® is to access the Command Register by doing a WRITE cycle to address location 0Bh and setting TE Bit (Transfer Enable Bit) to a logic '0.' This will freeze the External Clock Registers at the present recorded time, allowing access to occur without danger of simul-

taneous update. When the clock registers have been read or written, a second WRITE cycle to location 0Bh and setting the TE Bit to a logic '1' will put the Clock Registers back to being updated every 0.01 second. No time is lost in the Real Time Clock because the internal copy of the Clock Register buffers is continually incremented while the external memory registers are frozen. An alternate method of reading and writing the Clock Registers is to ignore synchronization. However, any single READ may give erroneous data as the Real Time Clock may be in the process of updating the external memory registers as data is being read. The internal copies of seconds through years are incremented, and the time of day alarm is checked during the period that hundreds of seconds reads "99" to "00." A way of making sure data is valid is to do multiple READs and compare. Writing the registers can also produce erroneous results for the same reasons. A way of making sure that the WRITE cycle has caused proper update is to do a READ to verify and re-execute the WRITE cycle if data is not correct. While the possibility of erroneous results from READ and WRITE cycles has been stated, it is worth noting that the probability of an incorrect result is kept to a minimum due to the redundant structure of the TIMEKEEPER.

#### **Clock Alarm Registers**

Registers 03h, 05h, and 07h contain the Clock Alarm Registers. Bits 3, 4, 5, and 6 of Register 07h will always read '0' regardless of how they are written. Bit 7 of Registers 03h, 05h, and 07h are mask bits (see Table 12, page 20). When all of the mask bits are logic '0,' a Clock Alarm will only occur when Registers 02h, 04h, and 06h match the values stored in Registers 03h, 05h, and 07h. An alarm will be generated every day when Bit 7 of Register 07h is set to a logic '1.' Similarly, an alarm is generated every hour when Bit 7 of Registers 07h and 05h is set to a logic '1.' When Bit 7 of Registers 07h, 05h, and 03h is set to a logic '1,' an alarm will occur every minute when Register 1 (seconds) rolls from "59" to "00."

Clock Alarm Registers are written and read in the same format as the Clock Registers. The Clock Alarm Flag and Interrupt are always cleared when alarm Registers are read or written.

#### Watchdog Alarm Registers

Registers 0Ch and 0Dh contain the time for the watchdog alarm. The two registers contain a time count from 00.01 to 99.99 seconds in BCD. The value written into the Watchdog Alarm Registers can be written or read in any order. Any access to Register 0Ch or 0Dh will cause the watchdog alarm to re-initialize and clears the Watchdog Flag Bit and the Watchdog Interrupt Output. When a new value is entered or the Watchdog Registers are read, the watchdog timer will start counting down from the entered value to zero. When zero is reached, the Watchdog Interrupt Output will go to the active state. The watchdog timer countdown is interrupted and re-initialized back to the entered value every time either of the registers are accessed. In this manner, controlled periodic accesses to the watchdog timer can prevent the watchdog alarm from going to an active level. If access does not occur, the countdown alarm will be repetitive. The Watchdog Alarm Registers always read the entered value. The actual countdown register is internal and is not readable. Writing registers 0Ch and 0Dh to '0' will disable the watchdog alarm feature.

Table 12. Register Map

Table 13. Time of Day Alarm Mask Bits

| Register      |             |                                          |                                    |  |

|---------------|-------------|------------------------------------------|------------------------------------|--|

| (03h) Minutes | (05h) Hours | (07h) Days                               |                                    |  |

| 1             | 1           | 1                                        | Alarm once per minute              |  |

| 0             | 1           | 1                                        | Alarm when minutes match           |  |

| 0             | 0           | 1                                        | Alarm when hours and minutes match |  |

| 0             | 0           | 0 Alarm when hours, minutes, and days ma |                                    |  |

Note: Any other bit combinations of mask bit settings produce an illegal operation.

#### **Command Register**

Address location 0Bh is the Command Register where mask bits, control bits, and flag bits reside. The operation of each bit is as follows:

**TE - Bit 7 Transfer Enable.** This bit, when set to logic '0,' will disable the transfer of data between internal and external clock registers. The contents in the external clock registers are now frozen and READs or WRITEs will not be affected with updates. This bit must be set to a logic '1' to allow updates.

**IPSW - Bit 6 Interrupt Switch.** When set to a logic '1,' IRQ/(IRQ) is the Watchdog Alarm. When set to a logic '0,' IRQ/(IRQ) is the time of day alarm output.

## IBH/LO - Bit 5 IRQ Sink or Source Current.

When this bit is set to a logic '1' and  $V_{CC}$  is applied, IRQ/(IRQ) will source current (see Table 5, page 9, IOH). When this bit is set to a logic '0,' IRQ will sink current (see Table 5, page 9, IOL).

**PU/LVL - Bit 4 Interrupt Pulse Mode or Level Mode.** This bit determines whether the interrupt will output a <u>pulse</u> or level signal. When set to a logic '0,' IRQ/(IRQ) will be in the level mode. When this bit is <u>set</u> to a logic '1,' the pulse mode is selected. IRQ/(IRQ) will either sink or source current, depending on the condition of Bit 5, for a minimum of 3ms and then release. IRQ will only source current when there is voltage present on  $V_{CC}$ .

**WAM - Bit 3 Watchdog Alarm Mask.** When this bit is set to a logic '0,' the watchdog interrupt output will be activated. The activated state is determined

by bits 1, 4, 5, and 6 of the Command Register. when this bit is set to a logic '1,' the watchdog interrupt output is deactivated.

**TDM - Bit 2 Time of Day Alarm Mask.** When this bit is set to a logic '0,' the time of day alarm interrupt output will be activated. The activated state is determined by bits 0, 4, 5, and 6 of the Command Register. When this bit is set to a logic '1,' the time of day alarm interrupt output is deactivated.

**WAF - Bit 1 Watchdog Alarm Flag.** This bit is set to a logic '1' when a watchdog alarm interrupt occurs. This bit is "Read only." The bit is reset when any of the watchdog alarm registers are accessed.

When the interrupt is in the pulse mode (see PU/LVL - Bit 4 Interrupt Pulse Mode or Level Mode), this flag will be in the logic '1' state only during the time the interrupt is active.

**TDF - Bit 0 Time of Day Flag.** This is a "Read only" bit. This bit is set to a logic '1' when a time of day alarm has occurred, the time the alarm occurred can be determined by reading the time of day alarm registers. This bit is reset to a logic '0' state when any of the time of day registers are accessed.

When the interrupt is in the pulse mode (see PU/LVL - Bit 4 Interrupt Pulse Mode or Level Mode), this flag will be in the logic '1' state only during the time the interrupt is active.

#### **Battery Low**

The M440T1MV automatically performs battery voltage monitoring upon power-up, and at factory-programmed time intervals of at least 24 hours. The Battery Low (BL) signal will be asserted if the battery voltage is found to be less than approximately 2.5V. The BL signal will remain asserted until completion of battery replacement and subsequent battery low monitoring tests, either during the next power-up sequence or the next scheduled 24-hour interval (see application note, "AN1540, NVRAM PBGA Dual Battery Hat Mounting and Removal" for more information).

If a battery low is generated during a power-up sequence, this indicates that one of the batteries is below 2.5V and may not be able to maintain data integrity in the SRAM. Data should be considered suspect, and verified as correct. Fresh batteries should be installed.

If a battery low indication is generated during the 24-hour interval check, this indicates that the battery is near end of life. However, data is not compromised due to the fact that a nominal  $V_{\rm CC}$  is supplied. In order to insure data integrity during subsequent periods of battery back-up mode, the

batteries should be replaced. The SNAPHAT $^{\otimes}$  top should be replaced with valid V<sub>CC</sub> applied to the device.

The M440T1MV only monitors the batteries when a nominal  $V_{CC}$  is applied to the device. Thus applications which require extensive durations in the battery back-up mode should be powered-up periodically (at least once every few months) in order for this technique to be beneficial. Additionally, if a battery low is indicated, data integrity should be verified upon power-up via a checksum or other technique. The BL signal is an open drain output and an appropriate pull-up resistor should be chosen to control the rise time.

## Sleep Mode

Forcing the sleep pad more positive than +7.5V above ground will cause the batteries to be isolated from the RAM, preserving the remaining battery life. This mode may be used when device operation is not necessary for an extended period of time.

**Note:** Implementation of this Sleep Mode will result in complete loss of data.

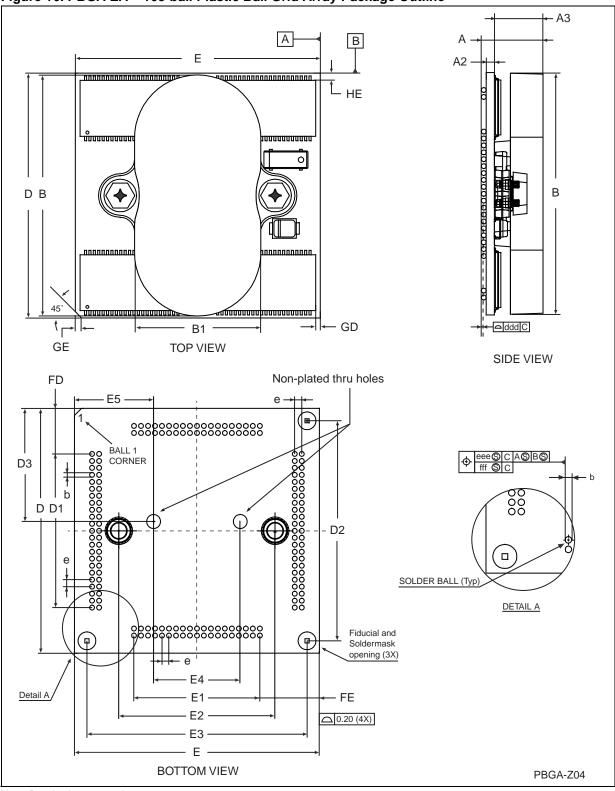

## PACKAGE MECHANICAL INFORMATION

Figure 16. PBGA-ZA - 168-ball Plastic Ball Grid Array Package Outline

Note: Drawing is not to scale.

Table 14. PBGA-ZA – 168-ball Plastic Ball Grid Array Package Mechanical Data

| Symb | mm        |       |       |           | inches |       |  |

|------|-----------|-------|-------|-----------|--------|-------|--|

|      | Тур       | Min   | Max   | Тур       | Min    | Max   |  |

| А    | 11.64     | 11.24 | 12.04 | 0.458     | 0.443  | 0.474 |  |

| A2   | 1.50      | 1.40  | 1.60  | 0.059     | 0.055  | 0.063 |  |

| A3   | 9.25      | 9.00  | 9.50  | 0.364     | 0.354  | 0.374 |  |

| В    | 44.95     | 44.90 | 45.00 | 1.770     | 1.768  | 1.772 |  |

| B1   | 23.17     | 23.12 | 23.22 | 0.912     | 0.910  | 0.914 |  |

| b    | 0.76      | 0.71  | 0.81  | 0.028     | 0.030  | 0.032 |  |

| D    | 44.50     | 44.30 | 44.70 | 1.752     | 1.744  | 1.760 |  |

| D1   | 27.94     |       |       | 1.100     |        |       |  |

| D2   | 40.00     | 39.80 | 40.20 | 1.575     | 1.567  | 1.583 |  |

| D3   | 20.56     | 20.46 | 20.66 | 0.809     | 0.806  | 0.813 |  |

| е    | 1.27      |       |       | 0.050     |        |       |  |

| Е    | 44.50     | 44.30 | 44.70 | 1.752     | 1.744  | 1.760 |  |

| E1   | 22.86     |       |       | 0.900     |        |       |  |

| E2   | 28.40     |       |       | 1.118     |        |       |  |

| E3   | 40.00     | 39.80 | 40.20 | 1.575     | 1.567  | 1.583 |  |

| E4   | 15.75     | 15.65 | 15.85 | 0.620     | 0.616  | 0.624 |  |

| E5   | 14.38     | 14.28 | 14.48 | 0.566     | 0.562  | 0.570 |  |

| FD   | 8.28      | 8.08  | 8.48  | 0.326     | 0.318  | 0.334 |  |

| FE   | 10.82     | 10.72 | 10.92 | 0.426     | 0.422  | 0.430 |  |

| GD   | 0.85      | 0.65  | 1.05  | 0.033     | 0.026  | 0.041 |  |

| GE   | 1.00      |       |       | 0.039     |        |       |  |

| HE   | 1.32      | 1.12  | 1.52  | 0.052     | 0.044  | 0.060 |  |

| n    | 168       |       | 168   |           |        |       |  |

|      | Tolerance |       |       | Tolerance |        |       |  |

| ddd  | 0.15      |       |       | 0.006     |        |       |  |

| eee  | 0.25      |       |       | 0.010     |        |       |  |

| fff  | 0.10      |       |       | 0.004     |        |       |  |

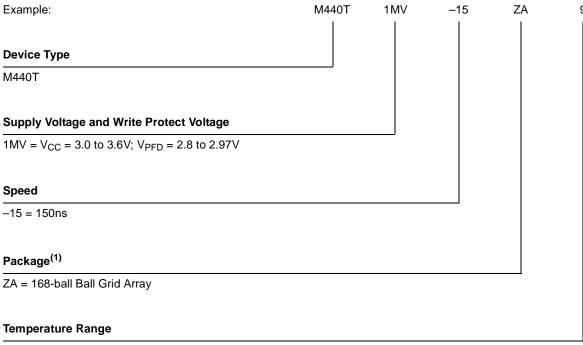

## **PART NUMBERING**

## **Table 15. Ordering Information Scheme**

$9 = -15 \text{ to } 75 \,^{\circ}\text{C}$

Note: 1. Where "Z" is the symbol for PBGA packages and "A" denotes 1.27mm ball pitch

For a list of available options (e.g., Speed, Package) or for further information on any aspect of this device, please contact the ST Sales Office nearest to you.

## **REVISION HISTORY**

**Table 16. Document Revision History**

| Date           | Rev. # | Revision Details                  |  |

|----------------|--------|-----------------------------------|--|

| September 2002 | 1.0    | First issue                       |  |

| 16-Jan-03      | 1.1    | Modify mechanical data (Table 14) |  |

| 31-Mar-03      | 1.2    | Update test condition (Table 10)  |  |

| 11-Apr-03      | 2.0    | Updated with template v2.2        |  |

**477**

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is registered trademark of STMicroelectronics All other names are the property of their respective owners.

© 2003 STMicroelectronics - All Rights Reserved

#### STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

www.st.com