## Features

- AVR<sup>®</sup> Microcontroller

- Clock Generator Provides CPU Rates up to 24 MHz

- Programmable UART with 16-byte FIFOs at the Receiver Side (1), with a Maximum Rate of 921K Baud

- Programmable SPI Interface

- Full-speed USB Function Controller

- On-chip 2K Bytes SRAM (for Data)

- On-chip 2K Bytes Dual-port RAM for Segmentation and Reassembly of Packets Exchanged between the USB and the UART Interfaces

- 8K x 16-bit In-system SRAM for Program Code

- On-chip Bootstrap ROM for Program Uploading to the Internal Program SRAM, Either from the USB or the SPI

- One USB Control Endpoint

- Five USB Programmable Endpoints (up to 64 Bytes) with Double-buffered FIFOs for Back-to-back Transfers

- One 8-bit Timer/Counter

- One 16-bit Timer/Counter

- External and Internal Interrupt Sources

- Programmable Watchdog Timer

- Independent UART BRG Oscillator

- 64-pin TQFP Package

- 3.3V Operation

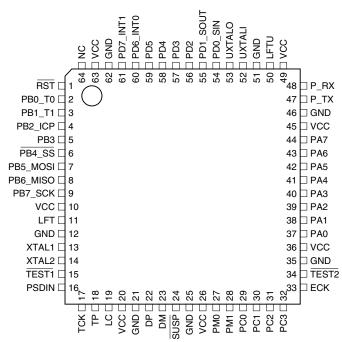

Figure 1. Pin Configuration

AVR<sup>®</sup>-based Bridge between Full-speed USB and Fast Serial Asynchronous Interfaces

# AT76C711

Rev. 1643AS-10/00

## Description

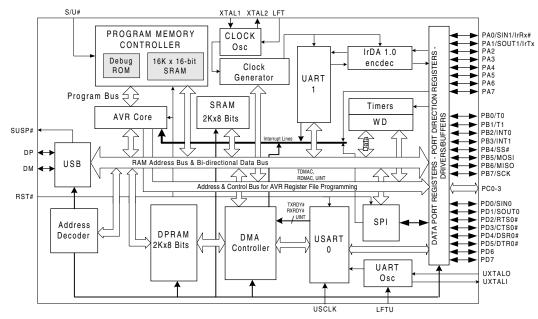

The Atmel AT76C711 is a compound USB device designed to provide a high-speed USB interface to devices that need to communicate with a base station through fast serial links, like UARTs and IrDA interfaces. It is based on the AVR-enhanced RISC architecture and consists of a USB function interface with a devoted DMA controller for fast transfers of data between the endpoint FIFOs and the DPRAM, a 2 KB internal RAM, a Synchronous Peripheral Interface (SPI), a UART, supporting a maximum rate of 921K baud, an 8K x 16-bit in-system SRAM for microcode storage, which is loaded from the SPI controller, 2K bytes dual-port RAM (DPRAM) and a programmable DMA controller for packet transfers between the UART and the DPRAM, without microcontroller intervention. An IrDA controller is also provided, attached to a second UART module and is able to communicate with an IrDA transceiver with a maximum rate of 1.2 Mbps. A hardwired Device Firmware Upgrade (DFU) protocol handler is implemented for programming an external AT45BDxxx serial Flash during the production phase. An internal bootstrap ROM contains the executable program for uploading the application code from an external serial Flash to the on-chip program SRAM. Alternatively, microcode can be stored in the program SRAM using the slave program mode while the chip is in the reset state. The USB and peripheral device controller function should be implemented in the microcontroller's firmware.

The device is suitable for applications where minimization of power dissipation is required, since there are no powerconsumable transactions with external parallel devices. The USB H/W block consists of a USB transceiver, the SIE, endpoint controllers and an interface to the microcontroller. The USB H/W interfaces to the USB host at the packet level. The microcontroller firmware handles the higher-level USB protocol layers that are not processed by the USB H/W and in addition, it performs the peripheral control functions.

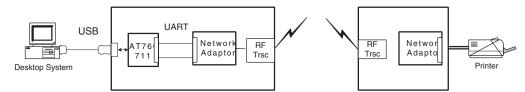

A typical application of AT76C711 and its functional diagram are shown in Figures 2 and 3.

## Applications

AT76C711 can be used in applications where peripherals supporting fast serial asynchronous or synchronous transfer of data have to communicate with a host or other peripherals through a high-speed serial link, like USB.

Typical areas of AT76C711 usage are:

- Connection of Network Interface Cards (NICs) to a host system

- Wireless communications

- Bridging of microcontrollers with different types of serial interfaces

- USB to UART bridge

- USB to IrDA bridge

- IrDA to UART bridge

- Packet adaptation of network protocol packets to USB requirements

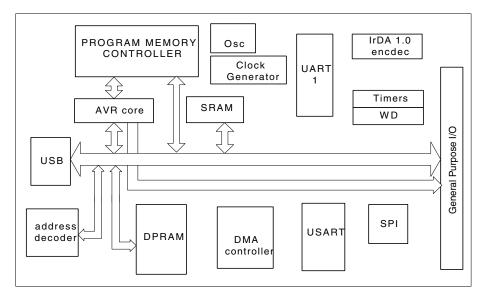

## **Block Diagram**

Figure 1. Block Diagram

Figure 2. Typical AT76C711 Application

## **Pin Summary**

### **Pin Assignment**

Type: I = Input

O = Output

OD = Output, open drain V = Power supply, ground

B = **Bi-directional**

Table 1. Pin Assignment in Alphabetical Order

|          | -                | -           |

|----------|------------------|-------------|

| Pin #    | Signal           | Туре        |

| 23       | DM               | В           |

| 22       | DP               | В           |

| 33       | ECK              | I           |

| 19       | LC               | I           |

| 14       | LFT              | I           |

| 50       | LFTU             | I           |

| *        | GND              | V           |

| 64       | NC               |             |

| 48       | P_IRX            | I           |

| 47       | P_ITX            | 0           |

| 37       | PA0              | В           |

| 38       | PA1              | В           |

| 39       | PA2              | В           |

| 40       | PA3              | В           |

| 41       | PA4              | В           |

| 42       | PA5              | В           |

| 43       | PA6              | В           |

| Notes: 1 | (*) GND: 12, 21, | 25. 35. 46. |

| Pin # | Signal   | Туре |

|-------|----------|------|

| 44    | PA7      | В    |

| 2     | PB0_T0   | В    |

| 3     | PB1_T1   | В    |

| 4     | PB2_ICP  | В    |

| 5     | PB3      | В    |

| 6     | PB4_SS   | В    |

| 7     | PB5_MOSI | В    |

| 8     | PB6_MISO | В    |

| 9     | PB7_SCK  | В    |

| 29    | PC0      | В    |

| 30    | PC1      | В    |

| 31    | PC2      | В    |

| 32    | PC3      | В    |

| 54    | PD0_SIN  | В    |

| 55    | PD1_SOUT | В    |

| 56    | PD2      | В    |

| 57    | PD3      | В    |

|       |          |      |

| Pin #  | Signal   | Туре |

|--------|----------|------|

| 58     | PD4      | В    |

| 59     | PD5      | В    |

| 60     | PD6_INT0 | В    |

| 61     | PD7_INT1 | В    |

| 16     | PSDIN    | I    |

| 1      | RST      | I    |

| 27, 28 | PM0, PM1 | I    |

| 24     | SUSP     | 0    |

| 17     | ТСК      | I    |

| 15     | TEST1    | I    |

| 34     | TEST2    | I    |

| 18     | ТР       | I    |

| **     | VCC      | V    |

| 51     | UXTALI   | I    |

| 52     | UXTALO   | 0    |

| 11     | XTAL1    | I    |

| 12     | XTAL2    | 0    |

Notes: 1. (\*) GND: 12, 21, 25, 35, 46, 51, 62

2. (\*) VCC: 10, 20, 24, 36, 45, 49, 63

# AT76C711

### Table 2. Pin Assignment in Numerical Order

| Pin # | Signal   | Туре |

|-------|----------|------|

| 1     | RST      | I    |

| 2     | PB0_T0   | В    |

| 3     | PB1_T1   | В    |

| 4     | PB2_ICP  | В    |

| 5     | PB3      | В    |

| 6     | PB4_SS   | В    |

| 7     | PB5_MOSI | В    |

| 8     | PB6_MISO | В    |

| 9     | PB7_SCK  | В    |

| 10    | VCC      | V    |

| 11    | LFT      | I    |

| 12    | GND      | V    |

| 13    | XTAL1    | I    |

| 14    | XTAL2    | 0    |

| 15    | TEST1    | I    |

| 16    | PSDIN    | I    |

| 17    | тск      | I    |

| 18    | ТР       | I    |

| 19    | LC       | I    |

| 20    | VCC      | V    |

| 21    | GND      | V    |

| 22    | DP       | В    |

| Pin # | Signal | Туре |

|-------|--------|------|

| 23    | DM     | В    |

| 24    | SUSP   | 0    |

| 25    | GND    | V    |

| 26    | VCC    | V    |

| 27    | PM0    | I    |

| 28    | PM1    | I    |

| 29    | PC0    | В    |

| 30    | PC1    | В    |

| 31    | PC2    | В    |

| 32    | PC3    | В    |

| 33    | ECK    | I    |

| 34    | TEST2  | I    |

| 35    | GND    | V    |

| 36    | VCC    | V    |

| 37    | PA0    | В    |

| 38    | PA1    | В    |

| 39    | PA2    | В    |

| 40    | PA3    | В    |

| 41    | PA4    | В    |

| 42    | PA5    | В    |

| 43    | PA6    | В    |

| 44    | PA7    | В    |

| Pin # | Signal   | Туре |

|-------|----------|------|

| 45    | VCC      | V    |

| 46    | GND      | V    |

| 47    | P_ITX    | 0    |

| 48    | P_IRX    | I    |

| 49    | VCC      | V    |

| 50    | LFTU     | I    |

| 51    | GND      | V    |

| 52    | UXTALI   | I    |

| 53    | UXTALO   | 0    |

| 54    | PD0_SIN  | В    |

| 55    | PD1_SOUT | В    |

| 56    | PD2      | В    |

| 57    | PD3      | В    |

| 58    | PD4      | В    |

| 59    | PD5      | В    |

| 60    | PD6_INT0 | В    |

| 61    | PD7_INT1 | В    |

| 62    | GND      | V    |

| 63    | VCC      | V    |

| 64    | NC       | V    |

## **Signal Description**

## Table 3. Signal Description

| Name             | Туре              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Program Memo     | ry Controller Sig | Inals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| PM0, PM1         | I                 | See Figure 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| PSDIN            | I                 | Program Serial Data In: In slave program mode, this signal carries the serial program data that are samples with the positive edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| ТР               | I                 | When $\overrightarrow{RST}$ is active (low), a high level of this signal, for at least two TCK pulses, forces the program address generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| LC               | I                 | Load Complete: A transition from low to high denotes the completion of program data transfer from the external device. The AVR will start executing instructions from the internal SRAM as soon as the $\overline{\text{RST}}$ goes high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| ТСК              | I                 | A clock signal for sampling PSDIN input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Port Signals     |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| PA[0:7]          | В                 | Port A, PB0 through PB7. 8-bit bi-directional port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| PA[0:7]          | В                 | Port B, PB0 through PB7. 8-bit bi-directional port. PB0, PB1, PB2, PB4 through PB7 are dual functions as shown below:         Port       Alternate Function         PB0       Timer/Counter0 clock input         PB1       Timer/Counter1 clock input         PB2       (ICP) Input Capture Pin for Timer/Counter1                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                  |                   | PB4(SS#) SPI slave port select inputPB5(MOSI) SPI slave port select inputPB6(MISO) SPI master data in, slave data outPB7(SCK) SPI master clock out, slave clock in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| PC[0:3]          | В                 | Port C, PC0 through PC3. 4-bit output port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| PD[0:7]          | В                 | <ul> <li>Port D, PD0 through PD7. 8-bit bi-directional I/O port. PD0, PD1 also serve as the data lines for the asynchronous serial port as listed below:</li> <li>Port Alternate Function</li> <li>PD0 (SIN) Serial Data In (I): This pin provides the serial receive data input to 16550 UART. The SIN signal will be a logic "1" during reset, idle (no data). During the local loopback mode, the SIN input pin is disabled and SOUT data is internally connected to the UART SIN input.</li> <li>PD1 (SOUT) Serial Data Out (O): This pin provides the serial transmit data from the 16550 UART. The SOUT signal will be a logic "1" during reset, idle (no data).</li> <li>PD6 (INT0) External Interrupt0 source</li> <li>PD7 (INT1) External Interrupt1 source</li> </ul> |  |

| USB Serial Inter | rface             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| DP               | В                 | Upstream Plus USB I/O. DP and DM form the differential signal pin pair connected to the host controller or an upstream hub.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| DM               | В                 | Upstream Minus USB I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| SUSP             | 0                 | Suspend. This output pin is deactivated (high) during normal operation. It is used to signal the host microcontroller that AT76C711 has received USB suspend signaling. This pin will stay asserted while AT76C722 is in the suspend mode. This pin is deactivated whenever a USB resume signaling is detected on DP and DM.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Name           | Туре | Description                                                                                                                                                                                                            |

|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test Signals   |      |                                                                                                                                                                                                                        |

| TEST1          | I    | Test signal for clocks (used in production phase only – normally tied to high)                                                                                                                                         |

| TEST2          | I    | Test signal for monitoring internal signal levels using the four data ports (used in production phase only – normally tied to high)                                                                                    |

| ECK            | I    | Clock pulse for activating various test modes when TEST2 is active                                                                                                                                                     |

| IrDA Interface |      |                                                                                                                                                                                                                        |

| P_ITX          | 0    | Infrared Data Out: This pin provides the serial transmit data from the IrDA codec to external IR Data Transceiver. This function is activated when the IrDA interface is enabled from PERIPHEN I/O Register.           |

| P_IRX          | I    | Infrared Data In: This pin provides the serial receive data input from the external IR Data<br>Transceiver to IrDA codec. This function is activated when the IrDA interface is enabled from<br>PERIPHEN I/O Register. |

| Other Signals  |      |                                                                                                                                                                                                                        |

| GND            | V    | Ground                                                                                                                                                                                                                 |

| VCC            | V    | 3.3V power supply                                                                                                                                                                                                      |

| RST            | I    | Reset. A low on this pin for two machine cycles, while the oscillator is running, resets the device.                                                                                                                   |

| XTAL1          | I    | Oscillator Input. Input to the inverting oscillating amplifier. A 12 MHz clock oscillator should be applied.                                                                                                           |

| XTAL2          | 0    | Oscillator Output. Output of the inverting oscillator amplifier.                                                                                                                                                       |

| LFT            | I    | Master clock PLL LFT pin                                                                                                                                                                                               |

| UXTALI         | I    | UART BRG Oscillator Input. Input to the UART oscillator amplifier.                                                                                                                                                     |

| UXTALO         | 0    | UART BRG Oscillator Output. Output of the UART oscillator amplifier.                                                                                                                                                   |

| LFTU           | I    | UART clock PLL LFT pin<br>es that it is an active low signal                                                                                                                                                           |

Note: Any signal with a # indicates that it is an active low signal.

## **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

#### Europe

Atmel SarL Route des Arsenaux 41 Casa Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

### Japan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

## **Atmel Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

#### Atmel Rousset

Zone Industrielle 13106 Rousset Cedex France TEL (33) 4-4253-6000 FAX (33) 4-4253-6001

### Atmel Smart Card ICs

Scottish Enterprise Technology Park East Kilbride, Scotland G75 0QR TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### Atmel Grenoble

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex France TEL (33) 4-7658-3000 FAX (33) 4-7658-3480

### *Fax-on-Demand* North America: 1-(800) 292-8635 International:

1-(408) 441-0732

*e-mail* literature@atmel.com

Web Site http://www.atmel.com

BBS 1-(408) 436-4309

#### © Atmel Corporation 2000.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Marks bearing <sup>®</sup> and/or <sup>™</sup> are registered trademarks and trademarks of Atmel Corporation.

Printed on recycled paper.

1643AS-10/00/xM