## Hardware Description of the C51 Family Products

## Summary

| 1. Common Features Description                    | I.2.2  |

|---------------------------------------------------|--------|

| 1.1. Introduction                                 | I.2.2  |

| 1.2. Oscillator and Clock Circuit                 | I.2.4  |

| 1.3. CPU Timing                                   | I.2.5  |

| 1.4. Port Structures and Operation                |        |

| 1.5. Accessing External Memory                    | I.2.10 |

| 1.6. Timer/Counters                               |        |

| 1.7. Serial Interface (80C51 and 80C52 only)      | I.2.18 |

| 1.8. Interrupts                                   |        |

| 1.9. Single Step Operation                        | I.2.33 |

| 1.10. Reset                                       | I.2.33 |

| 1.11. Power-Saving Modes of Operation             | I.2.34 |

| 1.12. More about the On-chip Oscillator           | I.2.36 |

| 1.13. Internal Timing                             |        |

| 1.14. C51 Pin Description                         |        |

| 2. More Features for C154 Parts                   | I.2.41 |

| 2.1. I/O Port Impedance                           |        |

| 2.2 Watchdog and 32-bit Timer/Counter Mode        |        |

| 2.3 Power-Reducing Mode                           |        |

| 2.4 Frame and Overrun Error Serial Link Detection |        |

## **1.** Common Features Description

## **1.1. Introduction**

This chapter presents a comprehensive description of the on-chip hardware features of the TEMIC C51 microcontrollers. Included in this description are :

- The port drivers and how they function both as ports and, for Ports 0 and 2, in bus operations

- The Timer/Counters

- The serial Interface

- The Interrupt System

- Reset

- The reduced Power Modes

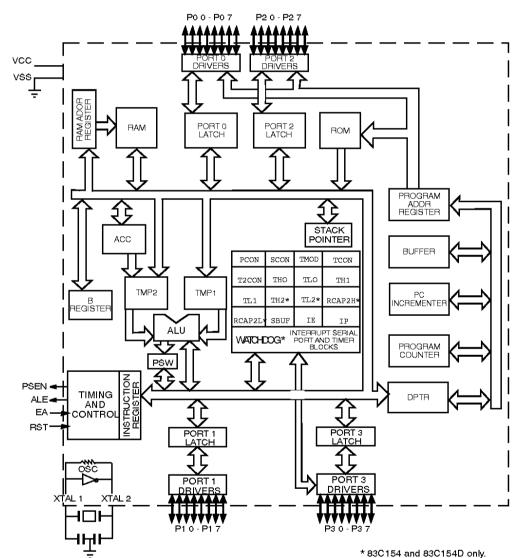

## Figure 1. C51 Architecture Block Diagram.

| DEVICE<br>NAME  | ROMLESS<br>VERSION | ROM<br>BYTES | RAM<br>BYTES | 16–BIT<br>TIMERS | PROCESS<br>TYPE |

|-----------------|--------------------|--------------|--------------|------------------|-----------------|

| 80C51, TSC80C51 | 80C31              | 4K           | 128          | 2                | CMOS            |

| 80C52           | 80C32              | 8K           | 256          | 3                | CMOS            |

| 83C154          | 80C154             | 16K          | 256          | 3*               | CMOS            |

| 83C154D         |                    | 32K          | 256          | 3*               | CMOS            |

Table 1. The TEMIC C51 Family of Microcontrollers.

\* included watchdog and Timer 32 bits.

The devices under consideration are listed in Table 1. As it becomes unwieldy to be constantly referring to each of these devices by their individual names, we will adopt a convention of refering to them generically as 80C51s, 80C52s and 83C154s, unless a specific member of the group is being refered to, in which case it will be specifically named. The 80C51s include the TSC80C51, 80C51 and 80C31. The 80C52s are the 80C52 and 80C32. The 83C154s are the 83C154, the 80C154 and the 83C154D.

Figure 1. shows a functionnal block diagram of the 80C51s, 80C52s and 83C154s.

## **Special Function Registers**

A map of the on-chip memory area called SFR (Special Function Register) space is shown in Figure 2. SFRs marked by parentheses are resident in the 80C52s and 83C154s but not in the 80C51s. IOCON marked by a star is only resident in the 83C154s.

Note that not all of the addresses are occupied. Unoccupied addresses are not implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have no effect.

|            |         |      |          | 8 B      | ytes  |       |      |    |

|------------|---------|------|----------|----------|-------|-------|------|----|

| F8         | *IOCON  |      |          |          |       |       |      | FF |

| F0         | В       |      |          |          |       |       |      | F7 |

| E8         |         |      |          |          |       |       |      | EF |

| E0         | ACC     |      |          |          |       |       |      | E7 |

| D8         |         |      |          |          |       |       |      | DF |

| D0         | PSW     |      |          |          |       |       |      | D7 |

| C8         | (T2CON) |      | (RCAP2L) | (RCAP2H) | (TL2) | (TH2) |      | CF |

| C0         |         |      |          |          |       |       |      | C7 |

| B8         | IP      |      |          |          |       |       |      | BF |

| <b>B</b> 0 | P3      |      |          |          |       |       |      | B7 |

| A8         | IE      |      |          |          |       |       |      | AF |

| A0         | P2      |      |          |          |       |       |      | A7 |

| 98         | SCON    | SBUF |          |          |       |       |      | 9F |

| 90         | P1      |      |          |          |       |       |      | 97 |

| 88         | TCON    | TMOD | TL0      | TL1      | TH0   | TH1   |      | 8F |

| 80         | P0      | SP   | DPL      | DPH      |       |       | PCON | 87 |

| * 020154   | 1       |      |          |          |       |       |      |    |

Figure 2. SFR Map. (...) Indicates Resident in 80C52s and 83C154s, not in 80C51s.

\* 83C154s only.

User software should not write 1s to theses unimplemented locations, since they may be used in future TEMIC C51 products to invoke new features. In that case the reset or inactive values of the new bits will always be 0, and their active values will be 1.

The functions of the SFRs are described as below.

## 1.1.1. Accumulator

ACC is the Accumulator register. The mnemonics for accumulator-specific instructions, however, refer to the accumulator simply as A.

## 1.1.2. B Register

The B register is used during multiply and divide operations. For other instructions it can be treated as another scratch pad register.

## 1.1.3. Program status word

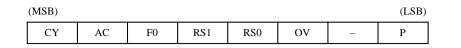

The PSW register contains program status information as detailed in Figure 3.

## 1.1.4. Stack pointer

The Stack Pointer register is 8 bits wide. It is incremented before data is stored during PUSH and CALL executions. While the stack may reside anywhere in on-chip RAM, the Stack Pointer is initialized to 07H after a reset. This causes the stack to begin at location 08H.

## 1.1.5. Data pointer

The Data Pointer (DPTR) consists of a high byte (DPH) and a low byte (DPL). Its intended function is to hold a 16-bit address. It may be manipulated as a 16-bit register or as two independent 8-bit registers.

## 1.1.6. Ports 0 to 3

P0, P1, P2 and P3 are the SFR latches of Ports 0, 1, 2 and 3, respectively.

## 1.1.7. Serial data buffer

The Serial Data Buffer is actually two separate registers, a transmit buffer and a receive buffer register. When data is moved to SBUF, it goes to the transmit buffer where it is held for serial transmission. (Moving a byte to SBUF is what initiates the transmission.) When data is moved from SBUF, it comes from the receive buffer.

## 1.1.8. Timer registers

Register pairs (TH0, TL0), (TH1, TL1), and (TH2, TL2) are the 16-bit counting registers for Timer/Counters 0, 1, and 2, respectively.

## 1.1.9. Capture registers

The register pair (RCAP2H, RCAP2L) are the capture register for the Timer 2 "capture mode." In this mode, in response to a transition at the 80C52's T2EX pin, TH2 and TL2 are copied into RCAP2H and RCAP2L. Timer 2 also has a 16-bit auto-reload mode, and RCAP2H and RCAP2L hold the reload value for this mode. More about Timer 2's features in Section 1.6.

## 1.1.10. Control registers

Special Function Registers IP, IE, TMOD, TCON, T2CON, SCON, and PCON contain control and status bits for the interrupt system, the timer/counters, and the serial port. They are described in later sections.

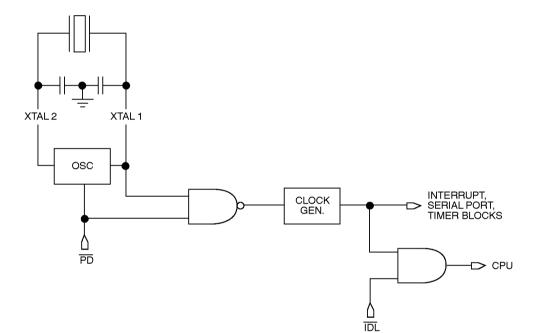

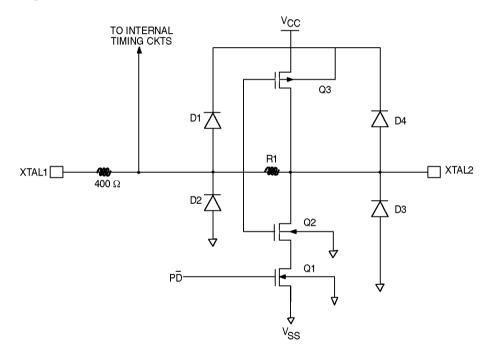

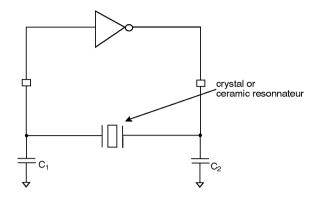

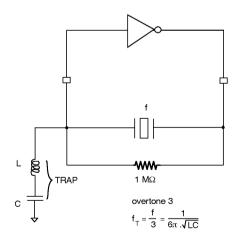

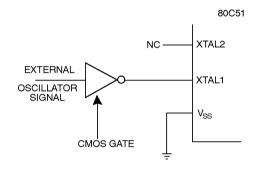

## 1.2. Oscillator and Clock Circuit

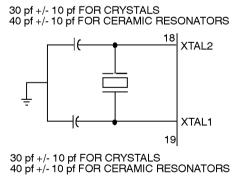

XTAL1 and XTAL2 are the input and output of a single-stage on-chip inverter, which can be configured with off-chip components as a Pierce oscillator, as shown in Figure 4. The on-chip circuitry, and selection of off-chip components to configure the oscillator are discussed in Section 1.12.

## Figure 3. Crystal/Ceramic Resonator Oscillator.

## Figure 4. PSW : Program Status Work Register.

| Symbol | Position | Name and Significance                                               |

|--------|----------|---------------------------------------------------------------------|

| СҮ     | PSW.7    | Carry flag                                                          |

| AC     | PSW.6    | Auxiliary Carry flag.                                               |

|        |          | (For BCD operations.)                                               |

| F0     | PSW.5    | Flag 0                                                              |

|        |          | (Available to the user for general purposes.)                       |

| RS1    | PSW.4    | Register bank Select control bits 1 & 0. Set/cleared by software to |

| RS0    | PSW.3    | determine working register bank (see Note).                         |

| Symbol | Position                | Name and Significance                                                                                                               |

|--------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| OV     | PSW.2                   | Overflow flag.                                                                                                                      |

| -      | PSW.1                   | (reserved)                                                                                                                          |

| Р      | PSW.0                   | Parity flag.                                                                                                                        |

|        |                         | Set/cleared by hardware each instruction cycle to indicate and odd/even number of "one" bits in the accumulator, i.e., even parity. |

| Note : | the contents of (RS1, I | RS0) enable the working register banks as follows                                                                                   |

|        | (0.0)-Bank 0 $(00H)$    | I-07H)                                                                                                                              |

|        | (0.1)–Bank 1 (08H       | I-OFH)                                                                                                                              |

|        | (1.0)–Bank 2 (10H       | I-17H)                                                                                                                              |

|        | (1.1)–Bank 3 (18H       | I-1FH)                                                                                                                              |

The oscillator, in any case, drives the internal clock generator. The clock generator provides the internal clocking signals to the chip. The internal clocking signals are at half the oscillator frequency, and define the internal phases, states, and machine cycles, which are described in the next section.

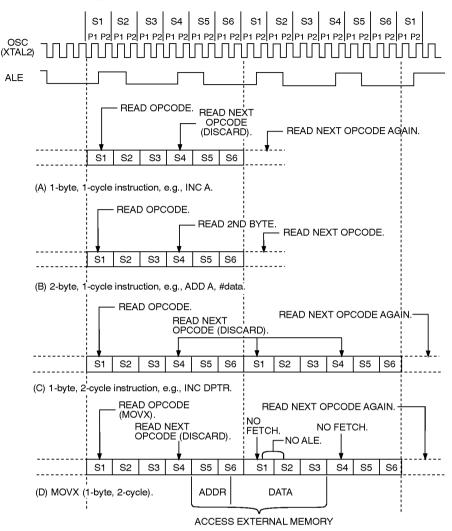

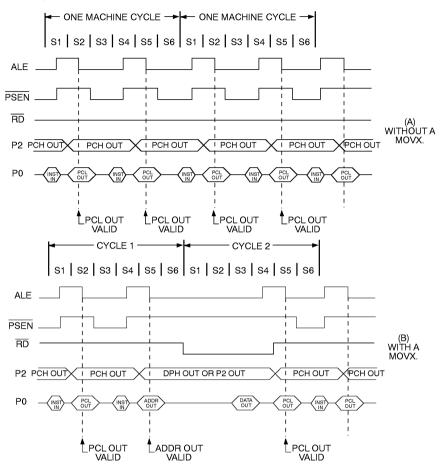

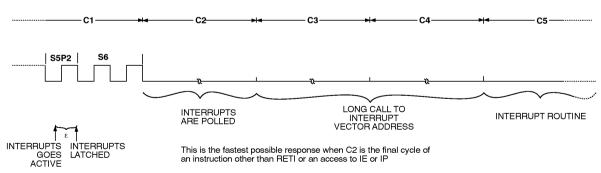

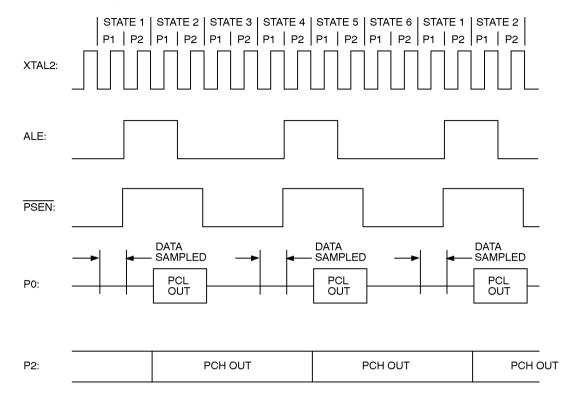

## 1.3. CPU Timing

A machine cycle consists of 6 states (12 oscillator periods). Each state is divided into a Phase 1 half, during which the Phase 1 clock is active, and a Phase 2 half, during which the Phase 2 clock is active. Thus, a machine cycle consists of 12 oscillator periods, numbered S1P1 (State 1, Phase 1), through S6P2 (State 6, Phase 2). Each phase lasts for one oscillator period. Each state lasts for two oscillator periods. Typically, arithmetic and logical operations take place during Phase 1 and internal register-to-register transfers take place during Phase 2.

The diagrams in Figure 5 show the fetch/execute timing referenced to the internal states and phases. Since these internal clock signals are not user accessible, the XTAL2 oscillator signal and the ALE (Address Latch Enable) signal are shown for external reference. ALE is normally activated twice during each machine cycle : once during S1P2 and S2P1, and again during S4P2 and S5P1.

Execution of one-cycle instruction begins at S1P2, when the opcode is latched into the Instruction Register. If it is a two-byte instruction, the second byte is read during S4 of the same machine cycle. If it is one-byte instruction, there is still a fetch at S4, but the byte read (which would be the next opcode), is ignored, and the Program Counter is not incremented. In any case, execution is complete at the end of S6P2. Figures 1-5A and 1-5B show the timing for a 1-byte, 1-cycle instruction and for a 2-byte, 1-cycle instruction.

Most 80C51 instructions execute in one cycle. MUL (multiply) and DIV (divide) are the only instructions that take more than two cycles to complete. They take four cycles.

Normally, two codes bytes are fetched from Program Memory during every machine cycle. The only exception to this is when a MOVX instruction is executed. MOVX is a 1-byte 2-cycle instruction that accesses external Data Memory. During a MOVX, two fetches are skipped while the external Data Memory is being addressed and strobed. Figure 1-5C and 1-5D show the timing for a normal 1-byte, 2-cycle instruction and for a MOVX instruction.

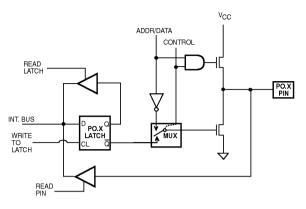

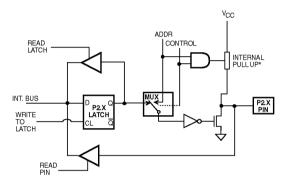

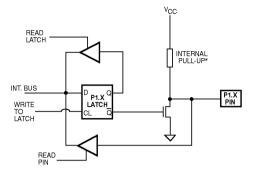

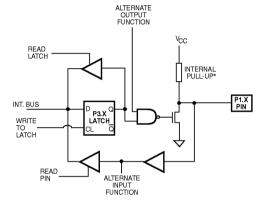

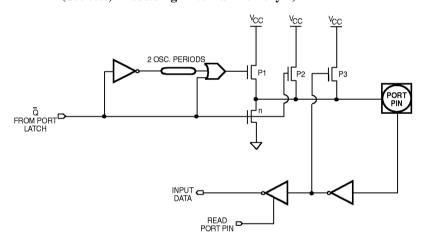

## **1.4.** Port Structures and Operation

All four ports in the 80C51 are bidirectional. Each consists of a latch (Special Function Register P0 through P3), an output driver, and an input buffer.

The output drivers of Ports 0 and 2, and input buffers of Port 0, are used in accesses to external memory. In this application, Port 0 outputs the low byte of the external memory address, time-multiplexed with the byte being written or read. Port 2 outputs the high byte of the external memory address when the address is 16 bits wide. Otherwise the Port 2 pins continue to emit the P2 SFR content.

#### Figure 5. 80C51 fetch/Execute Sequences.

All the Port 3 pins, and (in the 80C52) two Port 1 pins are multifunctional. They are not only port pins, but also serve the functions of various special features as listed below :

| Port Pin | <b>Alternate Function</b>                                 |  |  |  |  |

|----------|-----------------------------------------------------------|--|--|--|--|

| *P1.0    | T2 (Timer/Counter 2 external input)                       |  |  |  |  |

| *P1.1    | T2EX (Timer/Counter 2 capture/reload                      |  |  |  |  |

|          | trigger)                                                  |  |  |  |  |

| P3.0     | RXD (serial input port)                                   |  |  |  |  |

| P3.1     | TXD (serial output port)                                  |  |  |  |  |

| P3.2     | <b>INTO</b> (external interrupt)                          |  |  |  |  |

| P3.3     | <b>INT1</b> (external interrupt)                          |  |  |  |  |

| P3.4     | T0 (Timer/Counter 0 external input)                       |  |  |  |  |

| P3.5     | T1 (Timer/Counter 1 external input)                       |  |  |  |  |

| P3.6     | $\overline{WR}$ (external Data memory write strobe)       |  |  |  |  |

| P3.7     | $\overline{\text{RD}}$ (external Data memory read strobe) |  |  |  |  |

\* P1.0 and P1.1 serve these alternate functions only on the 80C52, 83C154 and 83C154D.

The alternate functions can only be activated if the corresponding bit latch in the port SFR contains a 1. Otherwise the port pin is stuck at 0.

#### 1.4.1. I/O Configurations

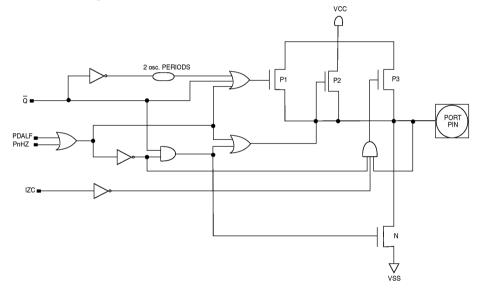

Figure 6. shows a functional diagram of a typical bit latch and I/O buffer in each of the four ports. The bit latch (one bit in the port's SFR) is represented as a Type D flip-flop, which will clock in a value from the internal bus in response to a "write to latch" signal from the CPU. The Q output of the flip-flop is placed on the internal bus in response to a "read latch" signal from the CPU. The level of the port pin itself is placed on the internal bus in response to a "read pin" signal from the CPU. Some instructions that read a port activate the "read latch" signal, and others activate the "read latch" signal.

I

## Figure 6. 80C51 Port Bit Latches and I/O Buffers.

(A) PORT 0 BIT

#### (C) PORT 2 BIT

Semiconductors

(B) PORT 1 BIT

\* See Figure 7. for details of the internal pullup.

As shown in Figure 6., the output drivers of Ports 0 and 2 are switchable to an internal ADDR and ADDR/DATA bus by an internal CONTROL signal for use in external memory accesses. During external memory accesses, the P2 SFR remains unchanged, but the P0 SFR gets 1s written to it.

Also shown in Figure 6., is that if a P3 bit latch contains a 1, then the output level is controlled by the signal labeled "alternate output function." The actual P3.X pin level is always available to the pin's alternate input function, if any.

Ports 1, 2, and 3 have internal pull-ups. Ports 0 has open-drain outputs. Each I/O line can be independently used as an input or an output. (Ports 0 and 2 may not be used as general purpose I/O when being used as the ADDR/DATA BUS). To be used as an input, the port bit latch must contain a 1, which turns off the output driver FET. Then, for Ports 1, 2, and 3, the pin is pulled high by the internal pull-up, but can be pulled low by an external source.

Port 0 differs in not having internal pullups. The pullup FET in the P0 output driver (see Figure 1-6A) is used only when the Port is emitting 1s during external memory accesses. Otherwise the pullup FET is off. Consequently P0 lines that are being used as output port lines are open drain. Writing a 1 to the bit latch leaves both output FETs off, so the pin floats. In that conditions it can be used as a high-impedance input.

Because Ports 1, 2, and 3 have fixed internal pullups they are sometimes called "quasi-bidirectional" ports. When configured as inputs they pull high and will source current (IIL, in the data sheets) when externally pulled low. Port 0, on the other hand, is considered "true" bidirectional, because when configured as an input it floats.

All the port latches in the 80C51 have 1s written to them by the reset function. If a 0 is subsequently written to a port latch, it can be reconfigured as an input by writing a 1 to it.

## 1.4.2. Writing to a Port

In the execution of an instruction that changes the value in a port latch, the new value arrives at the latch during S6P2 of the final cycle of the instruction. However, port latches are in fact sampled by their output buffers only during Phase 1 of any clock period. (During Phase 2 the output buffer holds the value it saw during the previous Phase 1). Consequently, the new value in the port latch won't actually appear at the output pin until the next Phase 1, which be at S1P1 of the next machine cycle.

If the change requires a 0-to-1 transition in Port 1, 2, or 3, an additional pull-up is turned on during S1P1 and S1P2 of the cycle in which the transition occurs. This is done to increase the transition speed. The extra pull-up can source about 100 times the current that the normal pull-up can. It should be noted that the internal pull-ups are field-effect transistors, not linear resistors. The pull-up arrangements are shown in Figure 7.

In the CMOS versions, the pull-up consists of three pFETs. It should be noted that an n-channel FET (nFET) is turned on when a logical 1 is applied to its gate, and is turned off when a logical 0 is applied to its gate. A p-channel FET (pFET) is the opposite : it is on when its gate sees a 0, and off when its gate sees a 1.

pFET 1 in Figure 7. is the transistor that is turned on 2 oscillator periods after a 0-to-1 transition in the port latch. While it's on, it turns on pFET 3 (a weak pull-up), through the inverter. This inverter and pFET form a latch which hold the 1.

Note that if the pin is emitting a 1, a negative glitch on the pin from some external source can turn off pFET 3, causing the pin to go into a float state, pFET 2 is a very weak pull-up which is on whenever the nFET is off, in traditional CMOS style. It's only about 1/10 the strenght of pFET3. Its function is to restore a 1 to the pin in the event the pin *had* a 1 and lost it to a glitch.

#### Figure 7. Ports 1 and 3 CMOS Internal Pull-up Configurations. Port 2 is similar except that it holds the strong pullup on while emitting 1s that are address bits. (See test, "Accessing External Memory".)

CMOS Configuration. pFET 1 is turned on for 2 osc. periods after Q makes a 1-to-0 transition. During this time, pFET 1 also turns on pFET 3 through the inverter to form a latch which holds the 1. pFET 2 is also on.

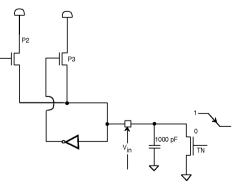

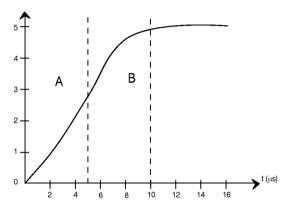

## 1.4.3. Port loading and interfacing

The output buffer of Ports 1, 2 and 3 can each drive 3LS TTL inputs. The pins can be driven by open-collector and open-drain outputs, but note that 0-to-1 transition will not be fast. In the CMOS device, an input 0 turns off pullup P3, leaving only the weak pullup P2 to drive the transistor. The Figure 8. shows an example where the port is driven by an open drain transistor  $t_N$ . The parasitic capacitance is equal to 100pF.

Figure 8. Port Interfacing.

The Figure 9. shows the behaviour of the port during 0-to-1 transition.

In the area A only pullup P2 sinks the capacitor and takes 5  $\mu$ s to switch from 0 volt to 2 volts. In the area B, pullup P2 and P3 feed the capacitor and the time to charge the capacitor is divide roughly by ten. So this figure shows it takes some machine cycles before having a true high level during a 0-to-1 transition.

### Figure 9. Port Behaviour During 0-to-1 Transition.

## 1.4.4. Read-Modify-Write Feature

Some instructions that read a port read the latch and others read the pin. Which ones do which ? The instructions that read the latch rather than the pin are the ones that read a value, possibly change it, and then rewrite it to the latch. These are called "read-modify-write" instructions. The instructions listed below are read-modify-write instructions. When the destination operand is a port, or a port bit, these instructions read the latch rather than the pin :

| ANL        | (logical AND, e.G., ANL P1,A)             |

|------------|-------------------------------------------|

| ORL        | (logical OR, e.g., ORL P2,A)              |

| XRL        | (logical EX-OR, e.g., XRL P3,A)           |

| JBC        | (jump if bit = 1 and clear bit, e.g., JBC |

|            | P1.1, LABEL)                              |

| CPL        | (complement bit, e.g., CPL P3.0)          |

| INC        | (increment, e.g., INC P2)                 |

| DEC        | (decrement, e.g., DEC P2)                 |

| DJNZ       | (decrement and jump if not zero, e.g.,    |

|            | DJNZ P3, LABEL)                           |

| MOV PX.Y,C | (move carry bit to bit Y of Port X)       |

| CLR PX.Y   | (clear bit Y of Port X)                   |

| SETB PX.Y  | (set bit Y of Port X)                     |

|            |                                           |

It is not obvious that the last three instructions in this list are read-modify-write instructions, but they are. They read the port byte, all 8 bits, modify the addressed bit, then write the new byte back to the latch. The reason that read-modify-write instructions are directed to the latch rather than the pin is to avoid a possible misinterpretation of the voltage level at the pin. For example, a port bit might be used to drive the base of a transistor. When a 1 is written to the bit, the transistor is turned on. If the CPU then reads the same port bit at the pin rather than the latch, it will read the base voltage of the transistor and interpret it as a 0. Reading the latch rather than the pin will return the correct value of 1.

Further details are given in the next chapter concerning the powerful functions of the 83C154 I/O PORTS.

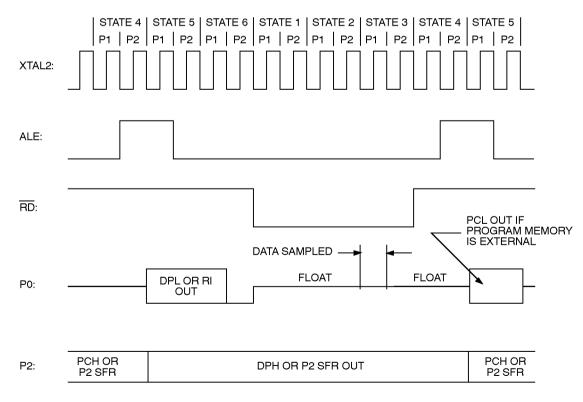

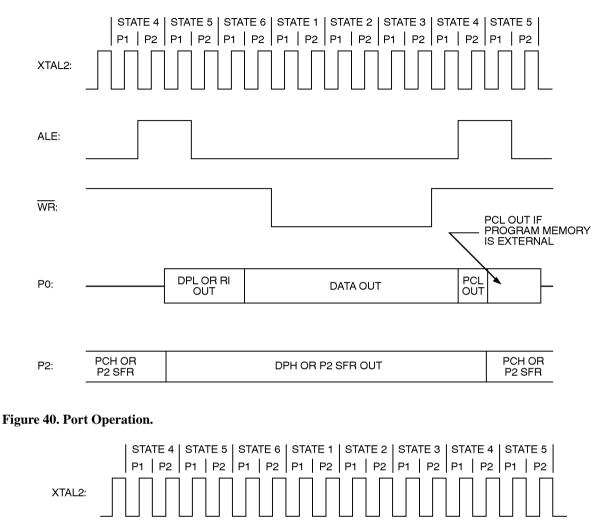

## 1.5. Accessing External Memory

Accesses to external memory are of two types : accesses to external Program Memory and accesses to external Data Memory. Accesses to external Program Memory use signal  $\overrightarrow{PSEN}$  (program store enable) as the read strobe. Accesses to external Data Memory use  $\overrightarrow{RD}$  or  $\overrightarrow{WR}$  (alternate function of P3.7 and P3.6) to strobe the memory.

Fetches from external Program memory always use a 16-bit address. Accesses to external Data Memory can use either a 16-bit address (MOVX @DPTR) or an 8-bit address (MOVX @Ri).

Whenever a 16-bit address is used, the high byte of the address comes out on Port 2, where it is held for the duration of the read or write cycle. Note that the Port 2 drivers use the strong pullups during the entire time that they are emitting address bits that are 1s. This is during the execution of a MOVX @DPTR instruction. During this time the Port 2 latch (the Special Function register) does not have to contain 1s, and the contents of the Port 2 SFR are not modified. If the external memory cycle is not immediately followed by another external memory cycle, the undisturbed contents of the Port 2 SFR will reappear in the next cycle.

If an 8-bit address is being used (MOVX @Ri), the contents of the Port 2 SFR remain at the Port 2 pins throughout the external memory cycle. This will facilitate paging.

In any case, the low byte of the address is time-multiplexed with the data byte on Port 0. The ADDR/DATA signal drives both FETs in the Port 0 output buffers. Thus, in this application the Port 0 pins are not open-drain outputs, and do not require external pull-ups. Signal ALE (address latch enable) should be used to capture the address byte into an external latch. The address byte is valid at the negative transitions of ALE. Then, in a write cycle, the data byte to be written appears on Port 0 just before  $\overline{WR}$  is activated, and remains there until after  $\overline{WR}$  is deactivated. In a read cycle, the incoming byte is accepted at Port 0 just before the read strobe is desactivated.

During any access to external memory, the CPU writes OFFH to the Port 0 latch (the Special Function Register), thus obliterating whatever information the Port 0 SFR may have been holding.

External program Memory is accessed under two conditions :

- 1) Whenever signal  $\overline{EA}$  is active ; or

- 2) Whenever the program counter (PC) contains a number that is larger than 0FFFH (1FFFH for the 80C52, 3FFFH for the 83C154 and 7FFFH for the 83C154D.

This requires that the ROMless versions have  $\overline{EA}$  wired low to enable the lower 4K (8K for the 80C32, 16K for the 80C154 and 32K for the 80C154D) program bytes to be fetched from external memory. When the CPU is executing out of external Program Memory, all 8 bits of Port 2 are dedicated to an output function and may not be used for general purpose I/O. During external program fetches they output the high byte of the PC. During this time the Port 2 drivers use the strong pullups to emit PC bits that are 1s.

## **PSEN**

The read strobe for external fetches is  $\overline{\text{PSEN}}$ .  $\overline{\text{PSEN}}$  is not activated for internal fetches. When the CPU is accessing external Program Memory,  $\overline{\text{PSEN}}$  is activated twice every cycle (except during a MOVX instruction) whether or not the byte fetched is actually needed for the current instruction. When  $\overline{\text{PSEN}}$  is activated its timing is not the same as  $\overline{\text{RD}}$ . A complete  $\overline{\text{RD}}$  cycle, including activation and deactivation of ALE and  $\overline{\text{RD}}$ , takes 12 oscillator periods. A complete  $\overline{\text{PSEN}}$  cycle, including activation and deactivation of ALE and  $\overline{\text{PSEN}}$ , takes 6 oscillator periods. The execution sequence for these two types of read cycles are shown in Figure 10 for comparison.

### Figure 10. External Program Memory Execution.

## ALE

The main function of ALE is to provide a properly timed signal to latch the low byte of an address from P0 to an external latch during fetches from external Program Memory. For that purpose ALE is activated twice every machine cycle. This activation takes place even when the cycle involves no external fetch. The only time an ALE pulse doesn't come out is during an access to external Data Memory. The first ALE of the second cycle of a MOVX instructions is missing (see Figure 10.). Consequently, in any system that does not use external Data Memory, ALE is activated at a constant rate of 1/6 the oscillator frequency, and can be used for external clocking or timing purposes.

## **Overlapping External Program and Data Memory Spaces**

In some applications it is desirable to execute a program from the same physical memory that is being used to store data. In the 80C51, the external Program and Data Memory spaces can be combined by ANDing  $\overrightarrow{PSEN}$  and  $\overrightarrow{RD}$ . A positive-logic AND of these two signals produces an active-low read strobe that can be used for the combined physical memory. Since the  $\overrightarrow{PSEN}$  cycle is faster than the  $\overrightarrow{RD}$  cycle, the external memory needs to be fast enough to accomodate the  $\overrightarrow{PSEN}$  cycle. TEMIC Semiconductors

## **1.6. Timer/Counters**

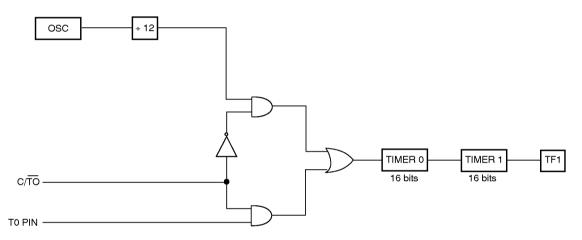

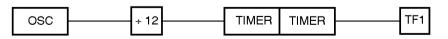

The 80C51 has two 16-bit timer/counter registers : Timer 0 and Timer 1. The 80C52, 83C154 and 83C154D have these two plus one more : Timer 2. All three can be configured to operate either as timers or event counters.

In the "timer" function, the register is incremented every machine cycle. Thus, one can think of it as counting machine cycles. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency.

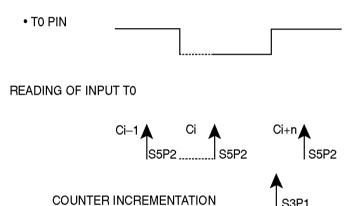

In the "counter" function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T0, T1 or (in the 80C52, 83C154 and 83C154D) T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected. Since it takes 2 machine cycles (24 oscillator periods) to recognize a 1-to-0 transition, the maximum count rate is 1/24 of the oscillator frequency. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be held for at least one full machine cycle.

#### Figure 11. TMOD : Timer/Counter Mode Control Register.

| In addition to the "timer" or "counter" selection, Timer |

|----------------------------------------------------------|

| 0 and Timer 1 have four operating modes from which to    |

| select. Timer 2, in the 80C52, 83C154 and 83C154D has    |

| three modes of operation : "capture," "auto-reload" and  |

| "baud rate generator."                                   |

| (MSB) |                  |      |    |      |                  |      | (LSB) |

|-------|------------------|------|----|------|------------------|------|-------|

| GATE  | $C/\overline{T}$ | M1   | M0 | GATE | $C/\overline{T}$ | M1   | M0    |

|       | TIM              | ER 1 |    |      | TIM              | ER 0 |       |

GATE

Gating control When set. Timer/counter "x" is enabled only while "INTx" pin is high and "TRx" control pin is set. When cleared Timer "x" is enabled whenever "TRx" control bit is set.

C/T

Timer or Counter Selector Cleared for Timer operation (input from internal system clock.) Set for Counter operation (input from "Tx" input pin).

| M1 | M0 | Operatong Mode                                                                                                                                                 |  |  |  |  |

|----|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0  | 0  | MCS-48 Timer "TLx" serves as five-bit prescaler.                                                                                                               |  |  |  |  |

| 0  | 1  | 16 bit Timer/Counter "THx" and "TLx" are cascaded ; there is no prescaler                                                                                      |  |  |  |  |

| 1  | 0  | 8 bit auto-reload timer-counter "THx" holds a value which is to be reloaded into "TLx"<br>each timer it overflows.                                             |  |  |  |  |

| 1  | 1  | (Timer 0) TL0 is an eight bit timer counter-controlled by the standard Timer 0 control bits TH0 is an eight-bit timer only controlled by Timer 1 control bits. |  |  |  |  |

| 1  | 1  | (Timer 1) Timer-counter 1 stopped.                                                                                                                             |  |  |  |  |

## Timer 0 and Timer 1

These timer/counter are present in both the 80C51, the 80C52, the 83C154 and the 83C154D. The "timer" or "counter" function is selected by control bits  $C/\overline{T}$  in the Special Function Register TMOD (Figure 11.). These two timer/counters have four operating modes, which are selected by bit-pairs (M1, M0) in TMOD. Modes 0, 1, and 2 are the same for both timer/counters. Modes 3 is different. The four operating modes are described below.

## Mode 0

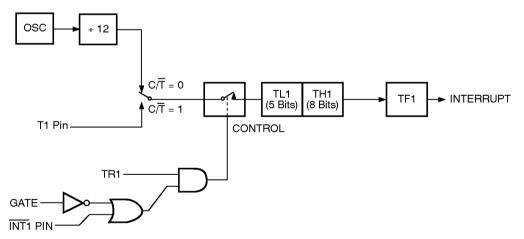

Putting either Timer into mode 0 makes it look like an 8048 Timer, which is an 8-bit counter with a divide-by-32 prescaler. Figure 12. shows the mode 0 operation as it applies to Timer 1.

In this mode, the timer register is configured as a 13-bit register. As the count rolls over from all 1s to all 0s, it sets the timer interrupt flag TF1. The counted input is enabled to the Timer when TR1 = 1 and either GATE = 0 or  $\overline{INTI} = 1$ . (Setting GATE =1 allows the Timer to be controlled by external input  $\overline{INT1}$ , to facilitate pulse width measurements). TR1 is a control bit in the Special Function register TCON (Figure 1-10). GATE is in TMOD.

## Figure 12. Timer/Counter 1 Mode 0 : 13-bit Counter.

The 13-bit register consists of all 8 bits of TH1 and the lower 5 bits of TL1. The upper 3 bits of TL1 are indeterminate and should be ingored. Setting the run flag (TR1) does not clear the registers.

Mode 0 operation is the same for Timer 0 as for Timer 1. Substitute TR0, TF0 and  $\overline{\text{INT0}}$  for the corresponding Timer 1 signals in Figure 12. There are two different GATE bits, one for Timer 1 (TMOD.7) and one for Timer 0 (TMOD.3).

## Mode 1

Mode 1 is the same as Mode 0, except that the Timer register is being run with all 16 bits.

## Mode 2

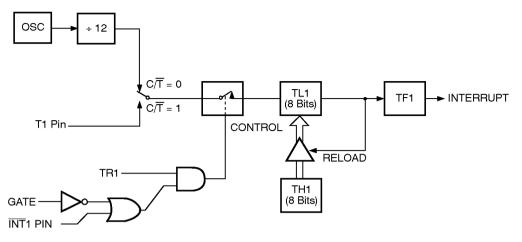

Mode 2 configures the timer register as an 8-bit counter (TL1) with automatic reload, as shown in Figure 14. Overflow from TL1 not only sets TF1, which is preset by sofware. The reload leaves TH1 unchanged.

Mode 2 operation is the same for Timer/Counter 0.

## Mode 3

Timer 1 in Mode 3 simply holds its count. The effect is the same as setting TR1 = 0.

## Figure 13. TCON : Timer/Counter Control Register.

ΊΈΜΙϹ

Semiconductors

| (MSB) |     |     |     |     |     |     | (LSB) |

|-------|-----|-----|-----|-----|-----|-----|-------|

| TF1   | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0   |

| Symbol | Position | Name and Significance                                                                                                                 |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| TF1    | TCON.7   | Timer 1 overflow Flag. Set by hardware on timer/counter overflow.<br>Cleared by hardware when processor vectors to interrupt routine. |

| TR1    | TCON.6   | Timer 1 Run control bit. Set/cleared by software to turn timer/counter on/off.                                                        |

| TF0    | TCON.5   | Timer 0 overflow Flag. Set by hardware on timer/counter overflow.<br>Cleared by hardware when processor vectors to interrupt routine. |

| TR0    | TCON.4   | Timer 0 Run control bit. Set/cleared by software to turn timer/counter on/off.                                                        |

| Symbol | Position | Name and Significance                                                                                                  |

|--------|----------|------------------------------------------------------------------------------------------------------------------------|

| IE1    | TCON.3   | Interrupt 1 Edge flag. Set by hardware when external interrupt edge detected. Cleared when interrupt processed.        |

| IT1    | TCON.2   | Interrupt 1 Type control bit. Set/cleared by software to specify falling edge/low level triggered external interrupts. |

| IEO    | TCON.1   | Interrupt 0 Edge flag. Set by hardware when external interrupt edge detected. Cleared when interrupt processed.        |

| ITO    | TCON.0   | Interrupt 0 Type control bit. Set/cleared by software to specify falling edge/low level triggered external interrupts. |

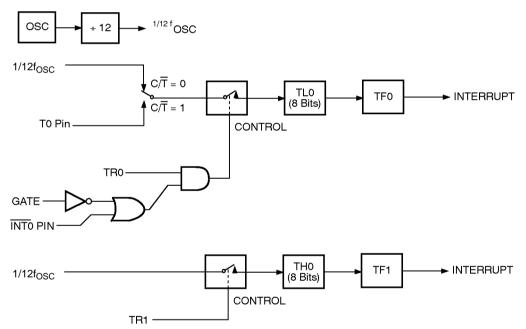

Timer 0 in Mode 3 establishes TL0 and TH0 as two separate counters. The logic for Mode 3 on Timer 0 is shown in Figure 15. TL0 uses the Timer 0 control bits :  $C/\overline{T}$ , GATE, TR0,  $\overline{INT0}$ , and TF0. TH0 is locked into a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from Timer 1. Thus TH0 now controls the "Timer 1" interrupt.

Mode 3 is provided for applications requiring an extra 8-bit timer or counter. With Timer 0 in Mode 3, an 80C51 can look like it has three timer/counters, and an 80C52, an 83C154 and 83C154D, like it has four. When Timer 0 is in Mode 3, Timer 1 can be turned on and off by switching it out of and into its own Mode 3, or can still be used by the serial port as a baud rate generator, or in fact, in any application not requiring an interrupt.

## Timer 2

Timer 2 is a 16-bit timer/counter which is present only in the 80C52, 83C154 and 83C154D. Like Timers 0 and 1, it can operate either as a timer or as an event counter.

Figure 14. Timer/Counter 1 Mode 2 : 8-bit Auto-reload.

## Figure 15. Timer/Counter 0 Mode 3 : Two 8-bit Counters.

## Figure 16. T2CON : Timer/Counter 2 Control Register.

|        | (MSB)   |      |                                                                                                                                                                                                                                                                    |                                                                                                                                           |              |                            |                            | (LSB)                         |                                                                          |

|--------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------|----------------------------|-------------------------------|--------------------------------------------------------------------------|

|        | TF2     | EXF2 | RCLK                                                                                                                                                                                                                                                               | TCLK                                                                                                                                      | EXEN2        | TR2                        | $C/\overline{T2}$          | CP/RL2                        |                                                                          |

| Symbol | Posit   | ion  |                                                                                                                                                                                                                                                                    |                                                                                                                                           | r            | Name and                   | Significa                  | nce                           |                                                                          |

| TF2    |         |      |                                                                                                                                                                                                                                                                    | Timer 2 overflow flag set by a Timer 2 overflow and must be cleared by software. TF2 will not be set when either $RCLK = 1$ or $TCLK = 1$ |              |                            |                            |                               |                                                                          |

| EXF2   | T2CON.6 |      | Timer 2 external flag set when either a capture or reload is caused by a negative transition on T2EX and EXEN2 = 1. When Timer 2 interrupt is enabled, $EXF2 = 1$ will cause the CPU to vector to the Timer 2 interrupt routine. EXF2 must be cleared by software. |                                                                                                                                           |              |                            |                            |                               |                                                                          |

| RCLK   | T2CON.5 |      | Receive clock flag. When set, causes the serial port to use Timer 2 overflow pulses for its receive clock in modes 1 and 3. $RCLK = 0$ causes Timer 1 overflow to be used for the receive clock.                                                                   |                                                                                                                                           |              |                            |                            |                               |                                                                          |

| TCLK   | T2CON.4 |      | Transmit clock flag. When set, causes the serial port to use Timer 2 overflow pulses for its transmit clock in modes 1 and 3. TCLK = 0 causes Timer 1 overflows to be used for the transmit clock.                                                                 |                                                                                                                                           |              |                            |                            |                               |                                                                          |

| EXEN2  | T2CC    | DN.3 | Timer 2 external enable flag. When set, allows a capture or relo<br>negative transition on T2EX if Timer 2 is not being used to cloo<br>causes Timer 2 to ignore events at T2EX.                                                                                   |                                                                                                                                           |              |                            |                            |                               |                                                                          |

| TR2    | T2CC    | N.2  | Start/stop control for Timer 2. A logic 1 starts the timer.                                                                                                                                                                                                        |                                                                                                                                           |              |                            |                            |                               |                                                                          |

| C/T2   | T2CC    | DN.1 | Timer or counter select. (Timer 2) $0 =$ Internal timer (OSC/12) $1 =$ Externa (falling edge triggered).                                                                                                                                                           |                                                                                                                                           |              |                            | External event counter     |                               |                                                                          |

| CP/RL2 | T2CC    | DN.0 | = 1. When transitions                                                                                                                                                                                                                                              | cleared, au<br>at T2EX w                                                                                                                  | to reloads w | ill occur eit<br>= 1. When | her with Tir<br>either RCL | ner 2 overflo<br>K = 1 or TCI | tions at T2EX if EXEN2<br>ows or negative<br>LK = 1, this bit is ignored |

This is selected by bit  $C/\overline{T2}$  in the Special Function Register T2CON (Figure 16). It has three operating modes : "capture," "autoload" and "baud rate generator," which are selected by bits in T2CON as shown in Table 2.

Table 2. Timer 2 Operating Modes.

| RCLK + TCLK | CP/RL2 | TR2 | MODE                |

|-------------|--------|-----|---------------------|

| 0           | 0      | 1   | 16-bit auto-reload  |

| 0           | 1      | 1   | 16-bit capture      |

| 1           | Х      | 1   | baud rate generator |

| X           | Х      | 0   | (off)               |

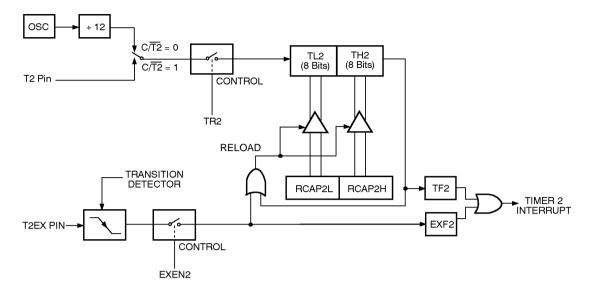

In the capture mode there are two options which are selected by bit EXEN2 in T2CON. If EXEN2 = 0, then Timer 2 is a 16-bit timer or counter which upon overflowing sets bit TF2, the Timer 2 overflow bit, which can be used to generate an interrupt. If EXEN2 = 1, then Timer 2 still does the above, but with the added feature that a 1-to-0 transition at external input T2EX causes the current value in the Timer 2 registers, TL2 and TH2, to be captured into registers RCAP2L and RCAP2H, respectively. (RCAP2L and RCAP2H are new Special Function Registers in the 80C52, 83C154 and 83C154D. In addition, the transition at T2EX causes bit EXF2 in T2CON to be set, and EXF2, like TF2, can generate an interrupt.

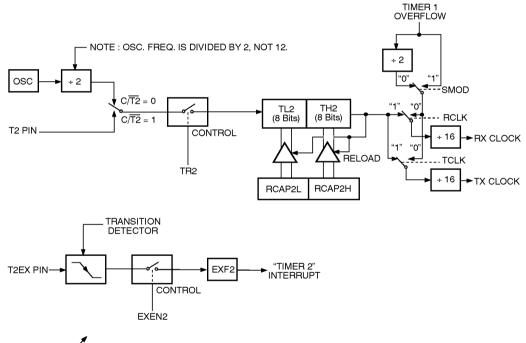

The capture mode is illustrated in Figure 17.

## Figure 17. Timer 2 in Capture Mode.

In the auto-reload mode there are again two options, which are selected by bit EXEN2 in T2CON. If EXEN2 = 0, then when Timer 2 rolls over it not only sets TF2 but also causes the Timer 2 registers to be reloaded with the 16-bit value in registers RCAP2L and RCAP2H, which are preset by software. If EXEN2 = 1, then Timer 2 still does the above, but with the added feature that a 1-to-0 transition at external input T2EX will also trigger the 16-bit reload and set EXF2.

The auto-reload mode is illustrated in Figure 18.

The baud rate generator mode is selected by RCLK = 1 and/or TCLK = 1. It will be described in conjunction with the serial port.

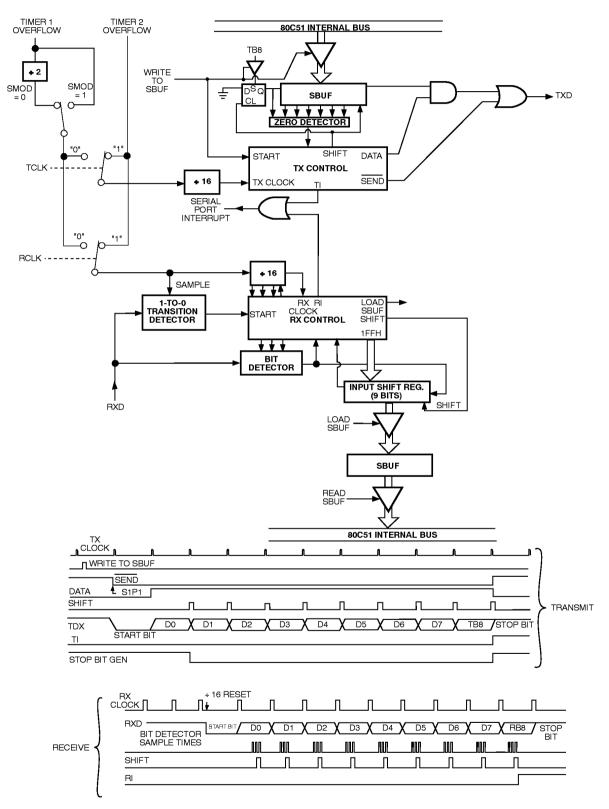

## 1.7. Serial Interface (80C51 and 80C52 only)

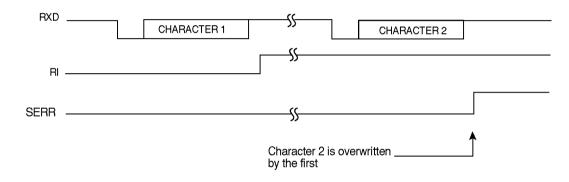

The serial port is full duplex, meaning it can transmit and receive simultaneously. It is also receive-buffered, meaning it can commence reception of a second byte before a previoulsy received byte has been read from the receive register. (However, if the first byte still hasn't been read by the time reception of the second byte is complete, one of the bytes will be lost). The serial port receive and transmit registers are both accessed at Special Function Register SBUF. Writing to SBUF loads the transmit register, and reading SBUF accesses a physically separate receive register.

### Figure 18. Timer 2 in Auto-Reload Mode.

The serial port can operate in 4 modes :

**Mode 0 :** Serial data enters and exits through RXD. TXD outputs the shift clock. 8 bits are transmitted/received : 8 data bits (LSB first). The baud rate is fixed at 1/12 the oscillator frequency.

**Mode 1 :** 10 bits are transmitted (through TXD) or received (through RXD) : a start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive, the stop bit goes into RB8 in Special Function Register SCON. The baud rate is variable.

**Mode 2 :** 11 bits are transmitted (through TXD) or received (through RXD) : a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). On transmit, the 9th data bit (TB8 in SCON) can be assigned the value of 0 or 1. Or, for example, the parity bit (P, in the PSW) could be moved into TB8. On receive, the 9th data bit goes into RB8 in Special Function register SCON, while the stop bit is ignored. The baud rate is programmable to either 1/32 or 1/64 the oscillator frequency.

**Mode 3 :** 11 bits are transmitted (through TXD) or received (through RXD) : a start bit (0), 8 data bits (LSB first), a programmable 9th data bit and a stop bit (1). In fact, Mode 3 is the same as Mode 2 in all respects except the baud rate. The baud rate in Mode 3 is variable.

In all four modes, transmission is initiated in Mode 0 by the condition RI = 0 and REN = 1. Reception is initiated in Mde 0 by the condition RI = 0 and REN = 1. Reception is initiated in the other modes by the incoming start bit if REN = 1.

#### 1.7.1. Multiprocessor Communications

Modes 2 and 3 have a special provision for multiprocessor, communications. In these modes, 9 data bits are received. The 9th one goes into RB8. Then comes a stop bit. The port can be programmed such that when the stop bit is received, the serial port interrupt will be activated only if RB8 = 1. This feature is enabled by setting bit SM2 in SCON. A way to use this feature in multiprocessor systems is as follows.

When the master processor wants to transmit a block of data to one of several slaves, it first sends out an address byte which identifies the target slave. An address byte differs from a data byte in that the 9th bit is 1 in an address byte and 0 in a data byte. With SM2 = 1, no slave will be interrupt by a data byte. An address byte, however, will interrupt all slaves, so that each slave can examine the received byte and see if it is being addressed. The addressed slave will clear its SM2 bit and prepare to receive the data bytes that will be coming. The slaves that weren't being addressed leaved their SM2s set and go on about their business, ignoring the coming data bytes.

SM2 has no effect in Mode 0, and in Mode 1 can be used to check the validity of the stop bit. In a Mode 1 reception, if SM2 = 1, the receive interrupt will not be activated unless a valid stop bit is received.

## Serial port Control Register

The serial port control and status register is the Special Function Register SCON, shown in Figure 19. This register contains not only the mode selection bits, but also the 9th data bit for transmit and receive (TB8 and RB8), and the serial port interrupts bits (TI and RI).

## Figure 19. SCON : Serial Port Control Register.

|                                                           |                                       | (MSB       | )       |           |                                                |                                                                                                       |       |                                                                                                                           |              | (LSB)          |                                                                                   |

|-----------------------------------------------------------|---------------------------------------|------------|---------|-----------|------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------|--------------|----------------|-----------------------------------------------------------------------------------|

|                                                           |                                       | SM         | 10      | SM1       | SM2                                            | REN                                                                                                   | TB8   | RB8                                                                                                                       | TI           | RI             |                                                                                   |

| where SM0, SM1 specify the serial port mode, as follows : |                                       |            |         |           | • TB8                                          | is the 9th data bit that will be transmitted in modes 2 and 3<br>Set or clear by software as desired. |       |                                                                                                                           |              |                |                                                                                   |

| SM0                                                       | SM1                                   | Mode       | Desc    | ription   | Baud Ra                                        | Baud Rate                                                                                             |       |                                                                                                                           |              |                |                                                                                   |

| 0                                                         | 0                                     | 0          | shift   | register  | f <sub>OSC</sub> ./12                          |                                                                                                       | • RB8 | in modes 2 and 3, is the 9th data bit that was received. In mode 1, if $SM2 = 0$ , RB8 is the stop bit that was received. |              |                |                                                                                   |

| 0                                                         | 1                                     | 1          | 8 bit   | UART      | variable                                       |                                                                                                       |       | In mode 0                                                                                                                 | , RB8 is no  | t used.        |                                                                                   |

| 1                                                         | 0                                     | 2          | 9 bit   | UART      | f <sub>OSC</sub> ./64<br>f <sub>OSC</sub> ./32 |                                                                                                       | • TI  | 8th bit tin                                                                                                               | ne in mode ( | ), or at the b | hardware at the end of the<br>beginning of the stop bit in<br>asmission. Must be  |

| 1                                                         | 1                                     | 3          | 9 bit   | UART      | variable                                       |                                                                                                       |       | cleared by                                                                                                                | software.    |                |                                                                                   |

| SM2                                                       | enables the modes 2 and will not be a | d 3. In mo | de 2 or | 3, if SM2 | is set to 1 t                                  | hen RI                                                                                                | • RI  | 8th bit tin                                                                                                               | ne in mode ( | ), or halfwa   | ardware at the end of the<br>y through the stop bit time<br>reception (except see |

• S will not be activated if the received 9th data bit (RB8) is 0. In mode 1, if SM2 = 1 then RI will not be activated if a valid stop bit is not received. In mode 0, SM2 should be 0.

• REN enables serial reception. Set by software to enable reception. Clear by software to disable reception.

#### 1.7.2. Baud Rates

The baud rate in Mode 0 is fixed :

Mode 0 Baud Rate =

$$\frac{\text{Oscillator Frequency}}{12}$$

The baud rate in Mode 2 depends on the value of bit SMOD in Special Function Register PCON. If SMOD = 0 (which is its value on reset), the baud rate is 1/64 the oscillator frequency. If SMOD = 1, the baud rate is 1/32the oscillator frequency.

Mode 2 Baud Rate =  $\frac{2^{\text{SMOD}}}{64} \times (\text{Oscillator Frequency})$

In the 80C51, the baud rates in Modes 1 and 3 are determined by the Timer 1 overflow rate. In the 80C52, 83C154 and 83C154D, these baud rates can be determined by Timer 1, or by Timer 2, or by both (one for transmit and the other for receive).

## 1.7.3. Using Timer 1 to Generate Baud Rates

When Timer 1 is used as the baud rate generator, the baud rates in Modes 1 and 3 are determined by the Timer 1 overflow rate and the value of SMOD as follows :

$\frac{\text{Modes 1, 3}}{\text{Baud rate}} = \frac{2^{\text{SMOD}}}{32} \times \text{(Timer 1 Overflow rate)}$

The Timer 1 interrupt should be disabled in this application. The Timer itself can be configured for either "timer" or "counter" operation, and in any of its 3 running modes. In the most typical applications, it is configured for "timer" operation, in the auto-reload mode (high nibble of TMOD = 0010B). In that case, the baud rate is given by the formula

$$\frac{\text{Modes } 1,3}{\text{Baud rate}} = \frac{2^{\text{SMOD}}}{32} \times \frac{\text{Oscillator Frequency}}{12 \times [256 - (\text{TH1})]}$$

SM2). Must be cleared by software.

One can achieve very low baud rates with Timer 1 by leaving the Timer 1 interrupt enabled, and configuring the Timer to run as a 16-bit timer (high nibble of TMOD = 0001B), and using the Timer 1 interrupt to do a 16-bit software reload.

Figure 20. lists various commonly used baud rates and how they can be obtained from Timer 1.

Figure 20. Timer 1 Generated Commonly Used Baud Rates.

|                   |                  |      | TIMER 1 |      |                 |  |

|-------------------|------------------|------|---------|------|-----------------|--|

| Baud Rate         | f <sub>OSC</sub> | SMOD | C/T     | Mode | Reload<br>Value |  |

| MODE 0 MAX : 1MHZ | 12 MHZ           | x    | х       | x    | х               |  |

| MODE 2 MAX : 375K | 12 MHZ           | 1    | x       | x    | х               |  |

| MODES 1,3 : 62.5K | 12 MHZ           | 1    | 0       | 2    | FFH             |  |

| 19.2K             | 11.059 MHZ       | 1    | 0       | 2    | FDH             |  |

| 9.6K              | 11.059 MHZ       | 0    | 0       | 2    | FDH             |  |

| 4.8K              | 11.059 MHZ       | 0    | 0       | 2    | FAH             |  |

| 2.4K              | 11.059 MHZ       | 0    | 0       | 2    | F4H             |  |

| 1.2K              | 11.059 MHZ       | 0    | 0       | 2    | E8H             |  |

| 137.5             | 11.986 MHZ       | 0    | 0       | 2    | 1DH             |  |

| 110               | 6 MHZ            | 0    | 0       | 2    | 72H             |  |

| 110               | 12 MHZ           | 0    | 0       | 1    | FEEBH           |  |

Figure 21. Timer 2 in Baud Rate Generator Mode.

## 1.7.4. Using Timer 2 to Generate Baud Rates

In the 80C52, 83C154 and 83C154D, Timer 2 is selected as the baud rate generator by setting TCLK and/or RCLK in T2CON (Figure 16.). Note then the baud rates for transmit and receive can be simultaneously different. Setting RCLK and/or TCLK puts Timer 2 into its baud rate generator mode, as shown in Figure 21.

NOTE AVAILABILITY OF ADDITIONNAL EXTERNAL INTERRUPT

The baud rate generator mode is similar to the auto-reload mode, in that a rollower in TH2 causes the Timer 2 registers to be reloaded with the 16-bit value in registes RCAP2H and RCAP2L, which are preset by software.

Now, the baud rates in Modes 1 and 3 are determined by Timer 2's overflow rate as follows :

Modes 1, 3 Baud Rate =

$$\frac{\text{Timer 2 Overflow rate}}{16}$$

The Timer can be configured for either "timer" or "counter" operation. In the most typical applications, it is configured for "timer" operation  $(C/\overline{T2} = 0)$ . "Timer" operation is a little different for Timer 2 when it's being used as a baud rate generator. Normally as a timer it would increment every machine cycle (thus at 1/12 the oscillator frequency). As a baud rate generator, however, it increment every state time (thus at 1/2 the oscillator frequency). In that case the baud rate is given by the formula

$\frac{\text{Modes 1, 3}}{\text{Baud rate}} = \frac{\text{Oscillator Frequency}}{32 \times [65536 - (\text{RCAP2H}, \text{RCAP2L})]}$

where (RCAP2H, RCAP2L) is the content of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

Timer 2 as a baud rate generator is shown in Figure 21. This Figure is valid only if RCLK + TCLK = 1 in T2CON. Note that a rollover in TH2 does not set TF2, and will not generate an interrupt. Therefore, the Timer 2 interrupt does not have to be disabled when Timer 2 is in the baud rate generator mode. Note too, that if EXEN2 is set, a 1-to-0 transition in T2EX will set EXF2 but will not cause a reload from (RCAP2H, RCAP2L) to (TH2, TL2). Thus when Timer 2 is in use as a baud rate generator, T2EX can be used as an extra external interrupt, if desired.

It should be noted that when Timer 2 is running (TR2 = 1) in "timer" function in the baud rate generator mode, one should not try to read or write TH2 or TL2. Under these conditions the Timer is being incremented every state time, and the results of a read or write may not be accurate. The RCAP registers may be read, but shouldn't be written to, because a write might overlap a reload and cause write and/or reload errors. Turn the Timer off (clear TR2) before accessing the Timer 2 or RCAP registers, in this case.

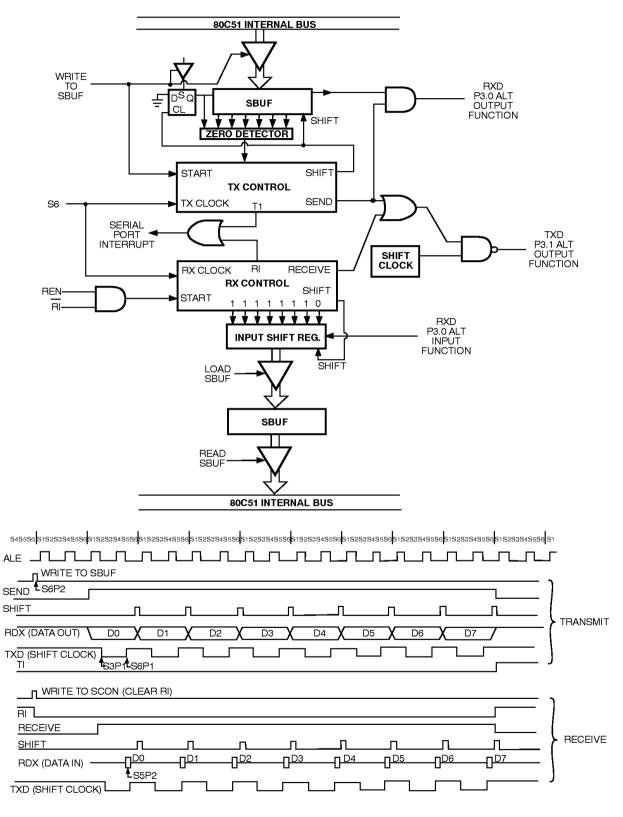

## More About Mode 0

Serial data enters and exits through RXD. TXD outputs the shift clock. 8 bits are transmitted/received : 8 data bits (LSB first). The baud rate is fixed at 1/12 the oscillator frequency.

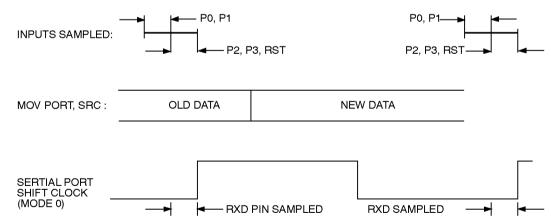

Figure 22. shows a simplified functional diagram of the serial port in mode 0, and associated timing.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "write to SBUF" signal at S6P2 also loads a 1 into the 9th bit position of the transmit shift register and tells the TX Control block to commence a transmission. The internal timing is such that one full machine cycle will elapse between "write to SBUF", and activation of SEND.

SEND enables the output of the shift register to the alternate output function line of P3.0, and also enables SHIFT CLOCK to the alternate output function line of P3.1. SHIFT CLOCK is low during S3, S4, and S5 of every machine cycle, and high during S6, S1 and S2. At S6P2 of every machine cycle in which SEND is active, the contents of the transmit shift register are shifted to the right one position.

As data bits shift out to the right, zeros come in from the left. When the MSB of the data byte is at the output position of the shift register, then the 1 that was initially loaded into the 9th position, is just to the left of the MSB, and all positions to the left of that contain zeros. This condition flags the TX Control block to do one last shift and then deactivate SEND and set T1. Both of these actions occur at S1P1 of the 10th machine cycle after "write to SBUF."

Reception is initiated by the condition REN = 1 and RI = 0. At S6P2 of the next machine cycle, the RX Control unit writes the bits 11111110 to the receive shift register, and in the next clock phase activates RECEIVE.

RECEIVE enables SHIFT CLOCK to the alternate output function line of P3.1. Shift CLOCK makes transitions at S3P1 and S6P1 of every machine cycle. At S6P2 of every cycle in which RECEIVE is active, the contents of the receive shift register are shifted to the left one position. The value that comes in from the right is the value that was sampled at the P3.0 pin at S5P2 of the same machine cycle.

As data bits come in from the right, 1s shift out to the left. When the 0 that was initially loaded into the rightmost position arrives at the leftmost position in the shift and load SBUF. At S1P1 of the 10th machine cycle after the write to SCON that cleared RI, RECEIVE is cleared and RI is set.

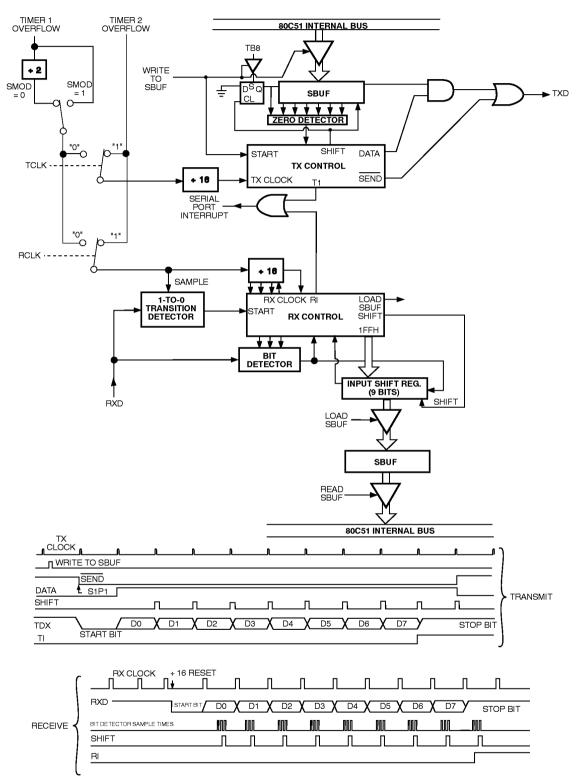

## More About Mode 1

Ten bits are transmitted (through TXD), or received (through RXD) : a start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive, the stop bit goes into RB8 in SCON. In the 80C51 the baud rate is determined by the Timer 1 overflow rate. In the 80C52, 83C154 and 83C154D it is determined either by the Timer 1 overflow rate, or the Timer 2 overflow rate, or both (one for transmit and the other for receive).

Figure 23. shows a simplified functional diagram of the serial port in Mode 1, and associated timings for transmit and receive.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "write to SBUF" signal also loads a 1 into the 9th bit position of the transmit shift register and flags the TX Control unit that a transmission is requested. Transmission actually commences at S1P1 of the machine cycle following the next rollower in the divide-by-16 counter. (Thus, the bit times are synchronized to the divide-by-16 counter, not to the "write to SBUF" signal).

The transmission begins with activation of  $\overline{\text{SEND}}$ , which puts the start bit at TXD. One bit time later, DATA is activated, which enables the output bit of the transmit shift register to TXD. The fisrt shift pulse occurs one bit time after that.

As data bits shift out to the right, zeros are clocked in from the left. When the MSB of the data byte is at the output position of the shift register, then the 1 that was initially loaded into the 9th position is just to the left of the MSB, and all positions to the left of that contain zeroes. This condition flags the TX Control unit to do one last shift and then deactivate  $\overline{\text{SEND}}$  and set TI. This occurs at the 10th divide-by-16 rollower after "write to SBUF". Reception is initiated by a detected 1-to-0 transition at RXD. For this purpose RXD is sampled at a rate of 16 times whatever baud rate has been established. When a transition is detected, the divide-by-16 counter is immediately reset, and 1FFH is written into the input shift register. Resetting the divide-by-16 counter aligns its rollovers with the boundaries of the incoming bit times.

## Figure 22. Serial Port Mode 0.

Figure 23. Serial Port Mode 1. TCLK, RCLK, and Timer 2 are present in the 80C32/80C52, 80C154/83C154 and 83C154D.

The 16 states of the counter divide each bit time into 16ths. At the 7th, 8th, and 9th counter states of each bit time, the bit detector samples the value of RXD. The value accepted is the value that was seen in at least 2 of the 3 samples. This is done for noise rejection. If the value accepted during the first bit time is not 0, the receive circuits are reset and the unit goes back to looking for another 1-to-0 transition. This is to provide rejection of false start bits. If the start bit proves valid, it is shifted into the input shift register, and reception of the rest of the frame will proceed.

As data bits come in from the right, 1s shift out to the left. When the start bit arrives at the leftmost position in the shift register, (which in mode 1 is a 9-bit register), it flags the RX Control block to do one last shift, load SBUFF and RB8, and set RI. Will be generated if, and only if, the following conditions are met at the time the final shift pulse is generated.

1) RI = 0, and

2) Either SM2 = 0, or the received stop bit = 1

If either of these two confitions is not met, the received frame is irretrievably lost. If both conditions are met, the stop bit goes into RB8, the 8 data bits go into SBUF, and RI is activated. At this time, whether the above conditions are met or not, the unit goes back to looking for a 1-to-0 transition in RXD.

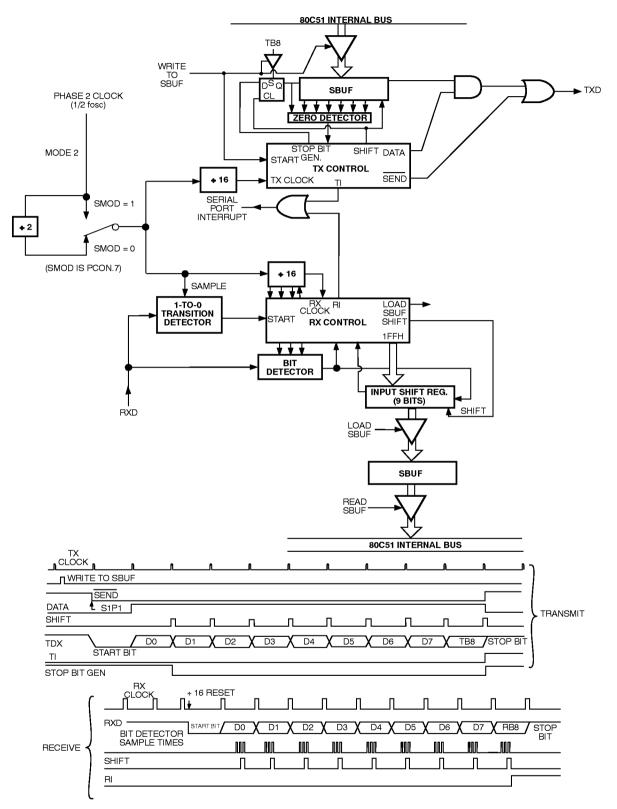

## More About Modes 2 and 3

Eleven bits are transmitted (through TXD), or received (through RXD) : a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). On transmit, the 9th data bit goes into RB8 is SCON. The baud rate is programmable to either 1/32 or 1/64 the oscillator frequency in mode 2. Mode 3 may have a variable baud rate generated from either Timer 1 or 2 depending on the state of TCLK and RCLK.

Figures 1-24 A and B show a functional diagram of the serial port in modes 2 and 3. The receive portion is exactly the same as in mode 1. The transmit portion differs from mode 1 only in the 9th bit of the transmit shift register.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "write to SBUF" signal also loads TB8 into the 9th bit position of the transmit shift register and flags the TX Control unit that a transmission is requested. Transmission commences at S1P1 of the machine cycle following the next rollover in the divide-by-16 counter. (Thus, the bit times are synchronized to the divide-by-16 counter, not to the "write to SBUF" signal.) The transmission begins with activation of SEND, which puts the start bit at TXD. One bit time later, DATA is activated, which enables the output bit of the transmit shift register to TXD. The first shift pulse occurs one bit time after that. The first shift clocks a 1 (the stop bit) into the 9th bit position of the shift register. Thereafter, only zeroes are clocked in. Thus, as data bits shift out to the right, zeroes are clocked in from the left. When TB8 is at the output position of the shift register, then the stop bit is just to the left of TB8, and all positions to the left of that contain zeroes. This condition flags the TX Control unit to do one last shift and then deactivate SEND and set TI. This occurs at the 11th divide-by-16 rollover after "write to SBUF".

Reception is initiated by a detected 1-to-0 transition at RXD. For this purpose RXD is sampled at a rate of 16 times whatever is detected, the divide-by-16 counter is immediately reset, and 1FFH is written to the input shift register.

At the 7th, 8th and 9th counter states of each bit time, the bit detector samples the value of RXD. The value accepted is the value that was seen in at least 2 of the 3 samples. If the value accepted during the first bit time is not 0, the receive circuits are reset and the unit goes back to looking for another 1-to-0 transition. If the start bit proves valid, it is shifted into the input shift register, and reception of the rest of the frame will proceed.

As data bits come in from the right, 1s shift out to the left. When the start bit arrives at the leftmost position in the shift register (which in modes 2 and 3 is a 9-bit register), it flags the RX Control block to do one last shift, load SBUF and RB8, and set RI. The signal to load SBUF and RB8, and to set RI, will be generated if, and only if, the following conditions are met at the time the final shift pulse is generated :

1) RI = 0, and

2) Either SM2 = 0 or the received 9th data bit = 1

If either of these conditions is not met, the received frame is irretrievably lost, and RI is not set. If both conditions are met, the received 9th data bit goes into RB8, and the first 8 data bits go into SBUF. One bit time later, whether the above conditions were met or not, the unit goes back to looking for a 1-to-0 transition at the RXD input.

Note that the value of the received stop bit is irrelevant to SBUF, RB8, or RI.

## TEMIC Semiconductors

## Figure 24. Serial Port Mode 2.

## Figure 25. Serial Port Mode 3. TCLK, RCLK and Timer 2 are present in the 80C32/80C52, 80C154/83C154 and in the 83C154D.

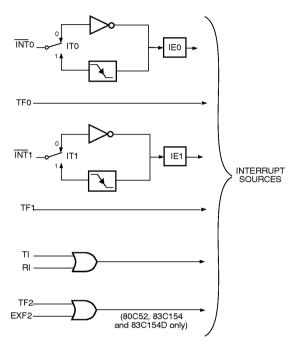

## **1.8. Interrupts**

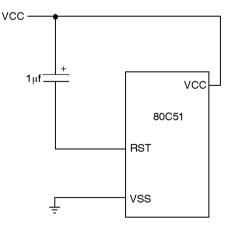

The 80C51 provides 5 interrupt sources. The 80C52 83C154 and 83C154D provide 6. Theses are shown in Figure 25.

## Figure 26. TEMIC C51 Interrupt Sources.

The external interrupts INTO and INTI can each be either level-activated or transition-activated, depending on bits ITO and IT1 in Register TCON. The flags that actually generate these interrupts are bits IEO and IE1 in TCON. When an external interrupt is generated, the flag that generated it is cleared by the hardware when the service routine is vectored to only if the interrupt was transition-activated. If the interrupt was level-activated, then the external requesting source is what controls the request flag, rather than the on-chip hardware. The Timer 0 and Timer 1 Interrupts are generated by TF0 and TF1, which are set by a rollover in their respective timer/counter registers (except see Section 1.6 for Timer 0 in mode 3). When a timer interrupt is generated, the flag that generated it is cleared by the on-chip hardware when the service routine is vectored to.

The Serial Port Interrupt is generated by the logical OR of RI and TI. Neither of these flags is cleared by hardware when the service routine is vectored to. In fact, the service routine will normally have to determine whether it was RI or TI that generated the interrupt, and the bit will have to be cleared in software.

In the 80C52, 83C154 and 83C154D, the Timer 2 Interrupt is generated by the logical OR of TF2 and EXF2. Neither of these flags is cleared by hardware when the service routine is vectored to. In fact, the service routine may have to determine whether it was TF2 or EXF2 that generated the interrupt, and the bit will have to be cleared in software.

All of the bits that generate interrupts can be set or cleared by sofware, with the same result as though it had been set or cleared by hardware. That is, interrupts can be generated or pending interrupts can be canceled in sofware.

Each of these interrupt sources can be individually enabled or disabled by setting or clearing a bit in Special Function Register IE (Figure 26.). Note that IE contains also a global disable bit, EA, which disables all interrupts at once.

## Figure 27. IE : Interrupt Enable Register.

| (MSB)  |         |          |                                                                                                                                                                                           |                      |                     |                       | (LSB)             |  |

|--------|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|-----------------------|-------------------|--|

| EA     | Х       | ET2      | ES                                                                                                                                                                                        | ET1                  | EX1                 | ET0                   | EX0               |  |

| Symbol | Positio | )n       |                                                                                                                                                                                           | J                    | Function            |                       |                   |  |

| EA     | IE.7    |          | disables all interrupts. If $EA = 0$ , no interrupt will be acknowledged. If $EA = 1$ , each interrupt source is individually enabled or disabled by setting or clearing its enables bit. |                      |                     |                       |                   |  |

| _      | IE.6    | reserved | l.                                                                                                                                                                                        |                      |                     |                       |                   |  |

| ET2    | IE.5    |          | enables or disables the Timer 2 overflow or capture interrupt. If $ET2 = 0$ , the Timer 2 is disabled.                                                                                    |                      |                     |                       | er 2 interrupt is |  |

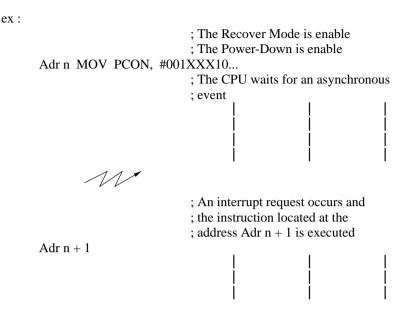

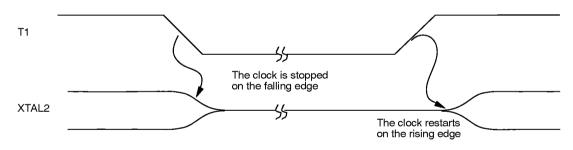

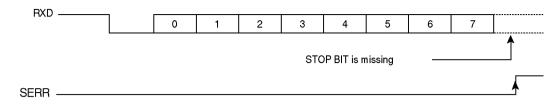

| ES     | IE.4    | enables  | enables or disables the Serial Port interrupt is disabled.                                                                                                                                |                      |                     |                       |                   |  |